Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 48x14b; D/A 2x9b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 56-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 56-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24794-24ltxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

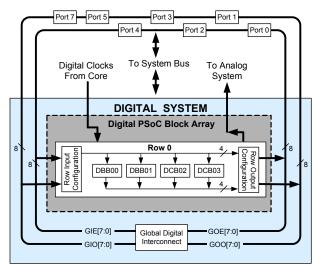

# 5. PSoC Functional Overview

The PSoC family consists of many devices with on-chip controllers. These devices are designed to replace multiple traditional MCU-based system components with one low-cost single-chip programmable component. A PSoC device includes configurable blocks of analog and digital logic, and programmable interconnect. This architecture makes it possible for you to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast central processing unit (CPU), flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts.

The PSoC architecture, shown in "Logic Block Diagram" on page 1, consists of four main areas: the core, the system resources, the digital system, and the analog system. Configurable global bus resources allow combining all of the device resources into a complete custom system. Each CY8C24x94 PSoC device includes four digital blocks and six analog blocks. Depending on the PSoC package, up to 56 GPIOs are also included. The GPIOs provide access to the global digital and analog interconnects.

## 5.1 The PSoC Core

The PSoC core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and internal main oscillator (IMO) and internal low-speed oscillator (ILO). The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a four-million instructions per second (MIPS) 8-bit Harvard-architecture microprocessor.

System resources provide these additional capabilities:

- Digital clocks for increased flexibility

- I<sup>2</sup>C functionality to implement an I<sup>2</sup>C master and slave

- An internal voltage reference, multi-master, that provides an absolute value of 1.3 V to a number of PSoC subsystems

- A switch-mode pump (SMP) that generates normal operating voltages from a single battery cell

- Various system resets supported by the M8C

The digital system consists of an array of digital PSoC blocks that may be configured into any number of digital peripherals. The digital blocks are connected to the GPIOs through a series of global buses. These buses can route any signal to any pin, freeing designs from the constraints of a fixed peripheral controller.

The analog system consists of six analog PSoC blocks, supporting comparators, and analog-to-digital conversion up to 10-bits of precision.

## 5.2 The Digital System

The digital system consists of four digital PSoC blocks. Each block is an 8-bit resource that is used alone or combined with other blocks to form 8-, 16-, 24-, and 32-bit peripherals, which are called user modules. Digital peripheral configurations include:

- PWMs (8- to 32-bit)

- PWMs with dead band (8- to 32-bit)

- Counters (8- to 32-bit)

- Timers (8- to 32-bit)

- UART 8-bit with selectable parity

- SPI master and slave

- I<sup>2</sup>C slave and multi-master

- CRC/generator (8-bit)

- IrDA

- PRS generators (8- to 32-bit)

The digital blocks are connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by PSoC device family. This allows the optimum choice of system resources for your application. Family resources are shown in Table 1 on page 7.

#### Figure 2. Digital System Block Diagram

Pin Type

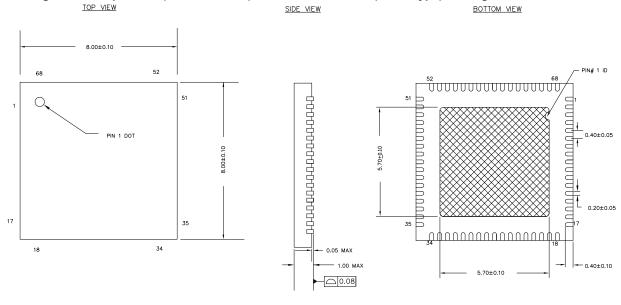

Figure 5 CY8C24894 56-Pin PSoC Device

## 9.2 56-Pin Part Pinout (with XRES)

## Table 3. 56-Pin Part Pinout (QFN<sup>[6]</sup>)

| Pin      | ly         | ре     | Name            | Description                                           |     |        | Fig                      | ure 5.               | CY8C24894 56-Pin PSoC Device                                              |

|----------|------------|--------|-----------------|-------------------------------------------------------|-----|--------|--------------------------|----------------------|---------------------------------------------------------------------------|

| No.      | Digital    | Analog | Name            | Description                                           |     |        |                          |                      |                                                                           |

| 1        | I/O        | I, M   | P2[3]           | Direct switched capacitor block input                 |     |        |                          | 5                    | <u>2 2</u><br>2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                         |

| 2        | I/O        | I, M   | P2[1]           | Direct switched capacitor block input                 |     |        |                          | ∠<br>                | 22                                                                        |

| 3        | I/O        | М      | P4[7]           |                                                       |     |        |                          | ΣΣζ                  |                                                                           |

| 4        | I/O        | М      | P4[5]           |                                                       |     |        |                          | ~2[5<br>~2[7<br>~0[1 | P 0 [3]<br>P 0 [5]<br>V C d d<br>P 0 [6]<br>P 2 [6]<br>P 2 [6]<br>P 2 [6] |

| 5        | I/O        | М      | P4[3]           |                                                       |     |        |                          |                      | 5 5 2 3 3 5 5 2 3 4 4 4 9 4 9 9 9 9 9 9 9 9 9 9 9 9 9 9                   |

| 6        | I/O        | М      | P4[1]           |                                                       |     | A.I.M. | P2[3] = 1                | 55<br>54             | ି ଜି ଜି ଜି ନ ନ ନ ନ ନ ନ ମ ନ ମ ନ ମ ନ ମ ମ ମ ମ ମ ମ ମ                          |

| 7        | I/O        | М      | P3[7]           |                                                       |     |        | P2[1] = 2                |                      | 41 <b>e</b> P2[0], A, I, M                                                |

| 8        | I/O        | М      | P3[5]           |                                                       |     |        | P4[7] = 3                |                      | 40 <b>=</b> P4[6], M                                                      |

| 9        | I/O        | М      | P3[3]           |                                                       |     |        | P4[5] = 4<br>P4[3] = 5   |                      | 39 <b>■</b> P4[4], M<br>38 <b>■</b> P4[2], M                              |

| 10       | I/O        | M      | P3[1]           |                                                       | -   |        | P4[1] 6                  |                      | 38 <b>–</b> [4[2], M<br>37 <b>–</b> P4[0], M                              |

| 11       | I/O        | M      | P5[7]           |                                                       | -   |        | P3[7] <b>-</b> 7         |                      | QFN 36 KRES                                                               |

| 12       | I/O        | M      | P5[5]           |                                                       |     |        | P3[5] = 8<br>P3[3] = 9   |                      | (Top View) 35 P3[4], M                                                    |

| 13       | I/O        | M      | P5[3]           |                                                       | -   |        | P3[1] = 10               | 1                    | 34 ➡ P3[2], M<br>33 ➡ P3[0], M                                            |

| 14       | I/O        | M      | P5[1]           | I <sup>2</sup> C SCL                                  | -   | M, I   | P5[7] 🗖 11               |                      | 32 <b>P</b> 5[6], M                                                       |

| 15<br>16 | I/O<br>I/O | M      |                 | I <sup>2</sup> C SDA                                  |     |        | P5[5] = 12               |                      | 31 <b>P</b> 5[4], M                                                       |

| 10       | 1/0        | M      | P1[5]           | I-C SDA                                               |     |        | P5[3] = 13<br>P5[1] = 14 |                      | 30 ➡ P5[2], M<br>29 ➡ P5[0], M                                            |

| 17       | 1/O        | M      | P1[3]<br>P1[1]  | I <sup>2</sup> C SCL, ISSP SCLK <sup>[7]</sup>        | -   |        |                          | 15<br>16<br>17       | 「 ほ び み お み な る な る な み ま                                                 |

| 19       |            | wer    | V <sub>SS</sub> | Ground connection <sup>[8]</sup>                      |     |        |                          |                      |                                                                           |

| 20       |            | SB     | VSS<br>D+       |                                                       |     |        |                          | P1[5<br>P1[5<br>P1[3 | E12<br>SSV<br>CDV<br>C17<br>C17<br>C17<br>C17<br>C17<br>C17<br>C17<br>C17 |

| 20       |            | SB     | D+              |                                                       |     |        |                          | SCL,<br>SDA,<br>M,   | M. I2C SCL.<br>M. I2C SDA, I<br>EXTCLK, M,<br>M,                          |

| 22       |            | wer    | V <sub>DD</sub> | Supply voltage                                        | -   |        |                          | N N<br>N N           |                                                                           |

| 23       | 1/0        |        | P7[7]           |                                                       |     |        |                          |                      | M, I2C<br>EXTCL                                                           |

| 24       | I/O        |        | P7[0]           |                                                       |     |        |                          | 2 2                  | 2 2 1                                                                     |

| 25       | 1/O        | М      |                 | I <sup>2</sup> C SDA, ISSP SDATA <sup>[7]</sup>       |     |        |                          |                      |                                                                           |

| 26       | I/O        | М      | P1[2]           |                                                       |     |        |                          |                      |                                                                           |

| 27       | I/O        | М      | P1[4]           | Optional EXTCLK                                       |     |        |                          |                      |                                                                           |

| 28       | I/O        | М      | P1[6]           |                                                       |     |        |                          |                      |                                                                           |

| 29       | I/O        | М      | P5[0]           |                                                       | Pin | Tv     | Туре                     |                      |                                                                           |

| 30       | I/O        | М      | P5[2]           |                                                       | No. |        | Analog                   | Name                 | Description                                                               |

| 31       | I/O        | М      | P5[4]           |                                                       | 44  | I/O    | M                        | P2[6]                | External VREF input                                                       |

| 32       | I/O        | М      | P5[6]           |                                                       | 45  | I/O    | I, M                     | P0[0]                | Analog column mux input                                                   |

| 33       | I/O        | М      | P3[0]           |                                                       | 46  | I/O    | I, M                     | P0[2]                | Analog column mux input                                                   |

| 34       | I/O        | М      | P3[2]           |                                                       | 47  | I/O    | I, M                     | P0[4]                | Analog column mux input VREF                                              |

| 35       | I/O        | М      | P3[4]           |                                                       | 48  | I/O    | I, M                     | P0[6]                | Analog column mux input                                                   |

| 36       | Inj        | put    | XRES            | Active high external reset with internal<br>pull-down | 49  | Po     | wer                      | V <sub>DD</sub>      | Supply voltage                                                            |

| 37       | I/O        | М      | P4[0]           |                                                       | 50  | Po     | wer                      | V <sub>SS</sub>      | Ground connection <sup>[8]</sup>                                          |

| 38       | I/O        | М      | P4[2]           |                                                       | 51  | I/O    | I, M                     | P0[7]                | Analog column mux input                                                   |

| 39       | I/O        | М      | P4[4]           |                                                       | 52  | I/O    | I/O, M                   | P0[5]                | Analog column mux input and column output                                 |

| 40       | I/O        | М      | P4[6]           |                                                       | 53  | I/O    | I/O, M                   | P0[3]                | Analog column mux input and column output                                 |

| 41       | I/O        | I, M   | P2[0]           | Direct switched capacitor block input                 | 54  | I/O    | I, M                     | P0[1]                | Analog column mux input                                                   |

| 42       | I/O        | I, M   | P2[2]           | Direct switched capacitor block input                 | 55  | I/O    | М                        | P2[7]                |                                                                           |

| 43       | I/O        | М      | P2[4]           | External AGND input                                   | 56  | I/O    | М                        | P2[5]                |                                                                           |

|          |            | A I I  | L I             | $\Omega = \Omega$ utput, and $M = Analog Mux Input$   |     | I      | I                        | I                    | 1                                                                         |

LEGEND A = Analog, I = Input, O = Output, and M = Analog Mux Input.

#### Notes

The center pad on the QFN package should be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal.

These are the ISSP pins, which are not High Z at POR. See the PSoC Technical Reference Manual for details.

All V<sub>SS</sub> pins should be brought out to one common GND plane.

## 9.4 68-Pin Part Pinout (On-Chip Debug)

The following 68-pin QFN part table and drawing is for the CY8C24094 OCD PSoC device.

Note This part is only used for in-circuit debugging. It is NOT available for production.

| Table 5. | 68-Pin | Part | Pinout | (QFN <sup>[12]</sup> ) |

|----------|--------|------|--------|------------------------|

|----------|--------|------|--------|------------------------|

| No.         Digital         Analog         Description           1         I/O         M         P4[7]                                                                                                                                                                                                                                                          | 8-Pin OCD PSoC Device                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 1 I/O M P4[7]                                                                                                                                                                                                                                                                                                                                                   | ШЯ                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                 | AGND                                                                                 |

| 2 1/0 M P4[5]                                                                                                                                                                                                                                                                                                                                                   |                                                                                      |

| 3 I/O M P4[3] ジェミュニュ                                                                                                                                                                                                                                                                                                                                            | 2 222222                                                                             |

| 4         I/O         M         P4[1]         드 ố:                                                                                                                                                                                                                                                                          | P2[2]                                                                                |

| 5 OCDE OCD even data I/O 입 입 입 입 입 입 입 입 입 입 입 입 입 입 입 입 입 입 입                                                                                                                                                                                                                                                                                                  |                                                                                      |

| 6 OCDO OCD odd data output                                                                                                                                                                                                                                                                                                                                      | 22 33 4 22 23 20 20 20 20 20 20 20 20 20 20 20 20 20                                 |

| 7 Fower V <sub>SS</sub> Ground connection 2                                                                                                                                                                                                                                                                                                                     | 51 = P2[0], M, Al<br>50 = P4[6], M                                                   |

| δ 1/0 M P3[7] M, P4[3] ■ 3                                                                                                                                                                                                                                                                                                                                      | 49 <b>P</b> P4[4], M                                                                 |

| 9 I/O M P3[5] M, P4[1] = 4                                                                                                                                                                                                                                                                                                                                      | 48 🗖 P4[2], M                                                                        |

| 10 I/O M P3[3] OCDE 5<br>11 I/O M P3[1] OCDO 6                                                                                                                                                                                                                                                                                                                  | 47 E P4[0], M                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                 | 46 🗖 XRES<br>45 🗖 CCLK                                                               |

| 12 1/0 M P5(7) M P5(7) 8                                                                                                                                                                                                                                                                                                                                        | 44 HCLK                                                                              |

| 13 I/O M P5[5] M, P3[5] 9                                                                                                                                                                                                                                                                                                                                       | 40 H 1 0[0], M                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                 | 42 = P3[4], M<br>41 = P3[2], M                                                       |

| N, P5[7] ■ 12                                                                                                                                                                                                                                                                                                                                                   | 40 <b>P</b> 3[0], M                                                                  |

| 16 I/O M P1[7] I <sup>2</sup> C SCL M, P5[5] = 13                                                                                                                                                                                                                                                                                                               | 39 🗖 P5[6], M                                                                        |

| 17         I/O         M         P1[5]         I <sup>2</sup> C SDA         M, P5[3]         I           18         I/O         M         P1[3]         M         I         I                                                                                                                                                                                   | 38 <b>–</b> P5[4], M                                                                 |

| 10 1/0 1/0 1/0 1/0 1/0 000 000 000 000 1/0 1/                                                                                                                                                                                                                                                                                                                   | 37 ➡ P5[2], M<br>36 ➡ P5[0], M                                                       |

| 19 1/0 Mi [F1[1] 1 C SCL, ISSF SCLK 2 12C SDA, M, P1[5] 17                                                                                                                                                                                                                                                                                                      | 35 🗖 P1[6] M                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                 | 3 3 3 3 3 8 5 8 5 8 5 8 5 8 5 8 5 8 5 8                                              |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | P7(5)<br>P7(5)<br>P7(13)<br>P7(13)<br>P7(12)<br>P1(13)<br>P1(13)<br>P1(14)<br>P1(14) |

| 23 Power V <sub>DD</sub> Supply voltage                                                                                                                                                                                                                                                                                                                         | 2C SDA, M.<br>M.<br>EXTCLK M.                                                        |

| 24 I/O P7[7]                                                                                                                                                                                                                                                                                                                                                    | SDA                                                                                  |

| 24         I/O         P/[/]                                                                                                                                                                                                                                                                                                                                    | I2C SDA.<br>EXTCLK                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                 | =                                                                                    |

| 27 I/O P7[4]                                                                                                                                                                                                                                                                                                                                                    |                                                                                      |

| 28 I/O P7[3]                                                                                                                                                                                                                                                                                                                                                    |                                                                                      |

| 29         I/O         P7[2]         Pin         Type         Name           30         I/O         P7[1]         No.         Digital         Analog                                                                                                                                                                                                            | Description                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | abod conceitor block input                                                           |

|                                                                                                                                                                                                                                                                                                                                                                 | ched capacitor block input                                                           |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

| 34         I/O         M         P1[4]         Optional EXTCLK         53         I/O         M         P2[4]         External AG           35         I/O         M         P1[6]         54         I/O         M         P2[6]         External VR                                                                                                           | •                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input and column output                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input and column output                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input, integration input #1<br>umn mux input and column output, integration  |

| 43 1/0 1/0, w Poisi Analog cou<br>input #2                                                                                                                                                                                                                                                                                                                      |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input and column output                                                      |

| 44 HCLK OCD high speed clock output 63 I/O I/O, M P0[3] Analog colu                                                                                                                                                                                                                                                                                             |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                 | umn mux input                                                                        |

| 45 CCLK OCD CPU clock output 64 I/O I, M P0[1] Analog colu                                                                                                                                                                                                                                                                                                      | umn mux input                                                                        |

| 45         CCLK         OCD CPU clock output         64         I/O         I, M         P0[1]         Analog colu           46         Input         XRES         Active high pin reset with internal pull-down         65         I/O         M         P2[7]           47         I/O         M         P4[0]         66         I/O         M         P2[5] | umn mux input                                                                        |

**LEGEND** A = Analog, I = Input, O = Output, M = Analog Mux Input, OCD = On-Chip Debugger.

#### Notes

12. The center pad on the QFN package should be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it should be electrically floated and not connected to any other signal.

All V<sub>SS</sub> pins should be brought out to one common GND plane.

These are the ISSP pins, which are not High Z at POR. See the PSoC Technical Reference Manual for details.

## 9.6 100-Ball VFBGA Part Pinout (On-Chip Debug)

The following 100-pin VFBGA part table and drawing is for the CY8C24094 OCD PSoC device.

Note This part is only used for in-circuit debugging. It is NOT available for production.

## Table 7. 100-Ball Part Pinout (VFBGA<sup>[17]</sup>)

| A10Power $V_{SS}$ Ground connectionF10I/OP7[1]B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I²C SCL, ISSB6PowerV_DDSupply voltageG6I/OMP1[6]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG9I/OMP5[6]B10Power $V_{SS}$ Ground connectionG10I/OP7[2]                                                                                                                                                                                                                                                                                                                                                                         | ection<br>ection<br>n reset with internal pull-down<br>a output<br>P SCLK <sup>[18]</sup> |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| A3NCNo connection. Pin must be left floatingF3I/OMP3[5]A4NCNo connection. Pin must be left floatingF4I/OMP5[1]A5NCNo connection. Pin must be left floating.F5Power $V_{SS}$ Ground connectionA6PowerV_DDSupply voltage.F6Power $V_{SS}$ Ground connectionA7NCNo connection. Pin must be left floating.F7I/OMP5[0]A8NCNo connection. Pin must be left floating.F8I/OMP3[6]A9Power $V_{SS}$ Ground connectionF10I/OP7[1]A10Power $V_{SS}$ Ground connectionF10I/OP7[1]B1Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[1]I²C SCLB5I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG10I/OMP3[6]B10PowerV <sub>SS</sub> Ground connectionG10I/OMP3[6]B10PowerV <sub>SS</sub> <td>n reset with internal pull-down a output P SCLK<sup>[18]</sup></td>     | n reset with internal pull-down a output P SCLK <sup>[18]</sup>                           |

| A4NCNo connection. Pin must be left floatingF4I/OMP5[1]A5NCNo connection. Pin must be left floating.F5Power $V_{SS}$ Ground connectionA6Power $V_{DD}$ Supply voltage.F6Power $V_{SS}$ Ground connectionA7NCNo connection. Pin must be left floating.F7I/OMP5[0]A8NCNo connection. Pin must be left floating.F8I/OMP3[0]A9Power $V_{SS}$ Ground connectionF9XRESActive high piA10Power $V_{SS}$ Ground connectionF10I/OP7[1]B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP1[1]I²C SCLB5I/OI, MP0[7]Analog column mux inputG4I/OMP1[0]I²C SCL, ISSB6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I²C SCL, ISSB7I/OI, MP0[2]Direct switched capacitor block inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG10I/OM <td>n reset with internal pull-down a output P SCLK<sup>[18]</sup></td> | n reset with internal pull-down a output P SCLK <sup>[18]</sup>                           |

| A5NCNo connection. Pin must be left floating.F5Power $V_{SS}$ Ground connectionA6Power $V_{DD}$ Supply voltage.F6Power $V_{SS}$ Ground connectionA7NCNo connection. Pin must be left floating.F7I/OMP5[0]A8NCNo connection. Pin must be left floating.F8I/OMP3[0]A9Power $V_{SS}$ Ground connectionF9XRESActive high piA10Power $V_{SS}$ Ground connectionF10I/OP7[1]F11B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[1]I²C SCLB5I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP0[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG9I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG9I/OMP5[6]B10PowerV <sub>SS</sub> Ground connectionG10I/OP7[2]C1NCNo connecti                                                                             | ection n reset with internal pull-down a output P SCLK <sup>[18]</sup>                    |

| A6Power $V_{DD}$ Supply voltage.F6Power $V_{SS}$ Ground connectionA7NCNo connection. Pin must be left floating.F7I/OMP5[0]A8NCNo connection. Pin must be left floating.F8I/OMP3[0]A9Power $V_{SS}$ Ground connectionF9XRESActive high piA10Power $V_{SS}$ Ground connectionF10I/OP7[1]B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[1]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[0]I²C SCL, ISSB6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Direct switched capacitor block inputG8I/OMP3[4]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG10I/OP7[2]C1C1NCNo connection. Pin must be left floatingH1NCNo connection </td <td>ection n reset with internal pull-down a output P SCLK<sup>[18]</sup></td>        | ection n reset with internal pull-down a output P SCLK <sup>[18]</sup>                    |

| A7NCNo connection. Pin must be left floating.F7I/OMP5[0]A8NCNo connection. Pin must be left floating.F8I/OMP3[0]A9Power $V_{SS}$ Ground connectionF9XRESActive high piA10Power $V_{SS}$ Ground connectionF10I/OP7[1]B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[0]I²C SCL, ISSB6PowerV <sub>DD</sub> Supply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP3[4]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG10I/OP7[2]C1C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]                                                                                                                                          | n reset with internal pull-down a output P SCLK <sup>[18]</sup>                           |

| A8NCNo connection. Pin must be left floating.F8I/OMP3(0)A9Power $V_{SS}$ Ground connectionF9XRESActive high piA10Power $V_{SS}$ Ground connectionF10I/OP7[1]B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I²C SCL, ISSB6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP3[4]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG10I/OP7[2]C1C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                        | a output                                                                                  |

| A9Power $V_{SS}$ Ground connectionF9XRESActive high piA10Power $V_{SS}$ Ground connectionF10I/OP7[1]P7[1]B1Power $V_{SS}$ Ground connectionG1OCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I²C SCL, ISSB6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG10I/OMP5[6]B10Power $V_{SS}$ Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                              | a output                                                                                  |

| A10PowerVSSGround connectionF10I/OP7[1]B1PowerVSSGround connectionG1OCDOOCD odd datB2PowerVSSGround connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I²C SCL, ISSB6PowerVDDSupply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerVSSGround connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                                                                                                                                                                           | a output                                                                                  |

| B1Power $V_{SS}$ Ground connectionG1OCDOOCDOOCD odd datB2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I²C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I²C SCL, ISSB6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG9I/OMP5[6]B10Power $V_{SS}$ Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]                                                                                                                                                                                                                                                                                                                        | P SCLK <sup>[18]</sup>                                                                    |

| B2Power $V_{SS}$ Ground connectionG2I/OMP5[5]B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I <sup>2</sup> C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I <sup>2</sup> C SCL, ISSB6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I <sup>2</sup> C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG9I/OMP5[6]B10Power $V_{SS}$ Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                                                                                                                                                    | P SCLK <sup>[18]</sup>                                                                    |

| B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I <sup>2</sup> C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I <sup>2</sup> C SCL, ISSB6PowerV <sub>DD</sub> Supply voltageG6I/OMP1[0]I <sup>2</sup> C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG9I/OMP5[6]B10PowerV <sub>SS</sub> Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

| B3I/OI, MP2[1]Direct switched capacitor block inputG3I/OMP3[3]B4I/OI, MP0[1]Analog column mux inputG4I/OMP1[7]I <sup>2</sup> C SCLB5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1]I <sup>2</sup> C SCL, ISSB6PowerV <sub>DD</sub> Supply voltageG6I/OMP1[0]I <sup>2</sup> C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG9I/OMP5[6]B10PowerV <sub>SS</sub> Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

| B5I/OI, MP0[7]Analog column mux inputG5I/OMP1[1] $I^2C$ SCL, ISSB6PowerV_DDSupply voltageG6I/OMP1[0] $I^2C$ SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9PowerV <sub>SS</sub> Ground connectionG9I/OMP5[6]B10PowerV <sub>SS</sub> Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                           |

| B6Power $V_{DD}$ Supply voltageG6I/OMP1[0]I²C SDA, ISSB7I/OI, MP0[2]Analog column mux inputG7I/OMP1[6]B8I/OI, MP2[2]Direct switched capacitor block inputG8I/OMP3[4]B9Power $V_{SS}$ Ground connectionG9I/OMP5[6]B10Power $V_{SS}$ Ground connectionG10I/OP7[2]C1NCNo connection. Pin must be left floatingH1NCNo connectionC2I/OMP4[1]H2I/OMP5[3]C3I/OMP4[7]H3I/OMP3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P SDATA <sup>[18]</sup>                                                                   |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                           |

| B10         Power         V <sub>SS</sub> Ground connection         G10         I/O         P7[2]           C1         NC         No connection. Pin must be left floating         H1         NC         No connection           C2         I/O         M         P4[1]         H2         I/O         M         P5[3]           C3         I/O         M         P4[7]         H3         I/O         M         P3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                           |

| C1         NC         No connection. Pin must be left floating         H1         NC         No connection           C2         I/O         M         P4[1]         H2         I/O         M         P5[3]           C3         I/O         M         P4[7]         H3         I/O         M         P3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| C2         I/O         M         P4[1]         H2         I/O         M         P5[3]           C3         I/O         M         P4[7]         H3         I/O         M         P3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | n. Pin must be left floating                                                              |

| C3 I/O M P4[7] H3 I/O M P3[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                           |

| C5         I/O         I/O         M         P1[0]         P0[0]         Analog column mux input and column output         H5         I/O         M         P1[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                           |

| C6         I/O         I, M         P0[6]         Analog column mux input         H6         I/O         M         P1[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                           |

| C7         I/O         I, M         P0[0]         Analog column mux input         H7         I/O         M         P1[4]         Optional EXT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CLK                                                                                       |

| C8     I/O     I, M     P2[0]     Direct switched capacitor block input     H8     I/O     M     P3[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GER                                                                                       |

| C9         I/O         M         P4[2]         H9         I/O         M         P5[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                           |

| C10 NC No connection. Pin must be left floating H10 I/O P7[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

| Ç i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | action                                                                                    |

| <b>č</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                           |