Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿХF

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                      |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 56                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 48x14b; D/A 2x9b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

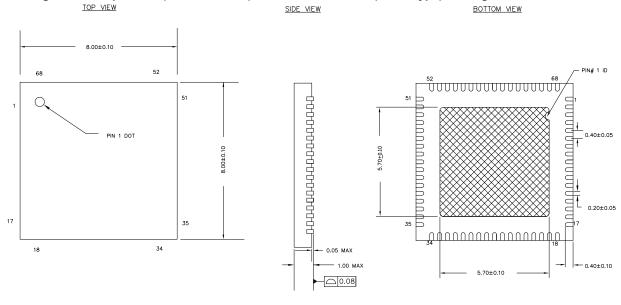

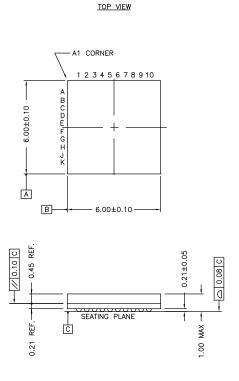

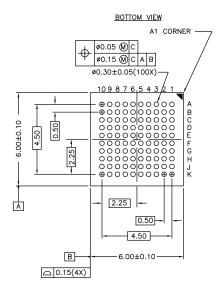

| Package / Case             | 100-VFBGA                                                                   |

| Supplier Device Package    | 100-VFBGA (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24994-24bvxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device Programmers                  |          |                             | 46 |

|-------------------------------------|----------|-----------------------------|----|

| Accessories (Emulation and Programr | ning)    |                             | 47 |

| ORDERING INFORMATION                |          |                             | 48 |

|                                     |          |                             |    |

| PACKAGING DIMENSIONS                |          |                             | 49 |

| ACRONYMS                            |          |                             | 54 |

| Acronyms Used                       |          |                             | 54 |

| DOCUMENT CONVENTIONS                |          |                             | 55 |

|                                     |          |                             |    |

|                                     |          |                             |    |

| GLOSSARY                            |          |                             | 55 |

| ERRATA                              |          |                             | 60 |

| Part Numbers Affected               | 60       | CY8C24x94 Errata Summary    | 60 |

| DOCUMENT HISTORY PAGE               |          |                             | 64 |

| SALES, SOLUTIONS, AND LEGAL INFO    | ORMATION |                             | 67 |

| Worldwide Sales and Design Support  |          | Cypress Developer Community |    |

| Products                            |          | Technical Support           | 67 |

| PSoC® Solutions                     | 67       |                             |    |

# 5. PSoC Functional Overview

The PSoC family consists of many devices with on-chip controllers. These devices are designed to replace multiple traditional MCU-based system components with one low-cost single-chip programmable component. A PSoC device includes configurable blocks of analog and digital logic, and programmable interconnect. This architecture makes it possible for you to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast central processing unit (CPU), flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts.

The PSoC architecture, shown in "Logic Block Diagram" on page 1, consists of four main areas: the core, the system resources, the digital system, and the analog system. Configurable global bus resources allow combining all of the device resources into a complete custom system. Each CY8C24x94 PSoC device includes four digital blocks and six analog blocks. Depending on the PSoC package, up to 56 GPIOs are also included. The GPIOs provide access to the global digital and analog interconnects.

# 5.1 The PSoC Core

The PSoC core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and internal main oscillator (IMO) and internal low-speed oscillator (ILO). The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a four-million instructions per second (MIPS) 8-bit Harvard-architecture microprocessor.

System resources provide these additional capabilities:

- Digital clocks for increased flexibility

- I<sup>2</sup>C functionality to implement an I<sup>2</sup>C master and slave

- An internal voltage reference, multi-master, that provides an absolute value of 1.3 V to a number of PSoC subsystems

- A switch-mode pump (SMP) that generates normal operating voltages from a single battery cell

- Various system resets supported by the M8C

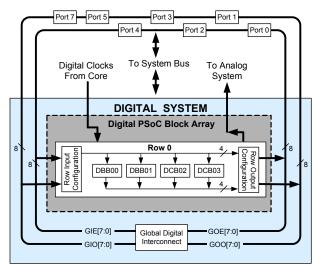

The digital system consists of an array of digital PSoC blocks that may be configured into any number of digital peripherals. The digital blocks are connected to the GPIOs through a series of global buses. These buses can route any signal to any pin, freeing designs from the constraints of a fixed peripheral controller.

The analog system consists of six analog PSoC blocks, supporting comparators, and analog-to-digital conversion up to 10-bits of precision.

### 5.2 The Digital System

The digital system consists of four digital PSoC blocks. Each block is an 8-bit resource that is used alone or combined with other blocks to form 8-, 16-, 24-, and 32-bit peripherals, which are called user modules. Digital peripheral configurations include:

- PWMs (8- to 32-bit)

- PWMs with dead band (8- to 32-bit)

- Counters (8- to 32-bit)

- Timers (8- to 32-bit)

- UART 8-bit with selectable parity

- SPI master and slave

- I<sup>2</sup>C slave and multi-master

- CRC/generator (8-bit)

- IrDA

- PRS generators (8- to 32-bit)

The digital blocks are connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by PSoC device family. This allows the optimum choice of system resources for your application. Family resources are shown in Table 1 on page 7.

#### Figure 2. Digital System Block Diagram

# 6. Getting Started

For in-depth information, along with detailed programming information, see the Technical Reference Manual for this PSoC device.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device datasheets on the web at http://www.cypress.com.

#### 6.1 Application Notes

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs.

#### 6.2 Development Kits

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

## 6.3 Training

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com,

# 7. Development Tools

PSoC Designer<sup>™</sup> is the revolutionary Integrated Design Environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- □ Hardware and software I<sup>2</sup>C slaves and masters

- □ Full speed USB 2.0

- Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

#### 7.1 PSoC Designer Software Subsystems

#### 7.1.1 Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use covers a wide variety of topics and skill levels to assist you in your designs.

### 6.4 CYPros Consultants

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

## 6.5 Solutions Library

Visit our growing library of solution-focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

## 6.6 Technical Support

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this allows you to use more than 100 percent of PSoC's resources for an application.

#### 7.1.2 Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and are linked with other software modules to get absolute addressing.

**C Language Compilers.** C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### 7.1.3 Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and

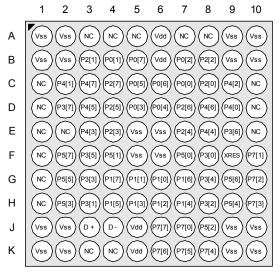

# 9. Pin Information

This section describes, lists, and illustrates the CY8C24x94 PSoC device family pins and pinout configuration.

The CY8C24x94 PSoC devices are available in the following packages, all of which are shown on the following pages. Every port pin (labeled with a "P") is capable of Digital I/O. However,  $V_{SS}$ ,  $V_{DD}$ , and XRES are not capable of Digital I/O.

# 9.1 56-Pin Part Pinout

| Pin                                                                                                | Ту                                                                                                                                                                                                                                                                                                                                                                                                                                      | /pe                                                                   | Name                                                                                                                                         | Description                                                                               |                                                                                                                                                                  |                                                                                             | Figu                                                                                          | ire 4.                                                                                                              | CY8C24794 56-Pin PSoC Device <sup>[3]</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.                                                                                                | Digital                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analog                                                                | Name                                                                                                                                         | Description                                                                               |                                                                                                                                                                  |                                                                                             | •                                                                                             |                                                                                                                     | 52 <u>55</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                                                                                                  | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | I, M                                                                  | P2[3]                                                                                                                                        | Direct switched capacitor block input                                                     |                                                                                                                                                                  |                                                                                             |                                                                                               |                                                                                                                     | P2[4],M<br>P0[1],A,I,M<br>P0[5],A,IO, M<br>P0[5],A,IO, M<br>P0[7],A,I, M<br>Vdd<br>P0[6],A,I, M<br>P0[6],A,I, M<br>P0[2],A,I, M<br>P2[6],M<br>P2[4],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2                                                                                                  | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | I, M                                                                  | P2[1]                                                                                                                                        | Direct switched capacitor block input                                                     |                                                                                                                                                                  |                                                                                             |                                                                                               | M IS                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3                                                                                                  | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | М                                                                     | P4[7]                                                                                                                                        |                                                                                           |                                                                                                                                                                  |                                                                                             |                                                                                               | 0.016                                                                                                               | P 2 [7]<br>P 0 [3]<br>P 0 [6]<br>P 2 [7]<br>P 2 [7 |

| 4                                                                                                  | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | М                                                                     | P4[5]                                                                                                                                        |                                                                                           |                                                                                                                                                                  |                                                                                             |                                                                                               |                                                                                                                     | 38288882888444444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5                                                                                                  | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P4[3]                                                                                                                                        |                                                                                           | _                                                                                                                                                                | А,                                                                                          | I, M, P2[3                                                                                    |                                                                                                                     | 3 ዜ ጜ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6                                                                                                  | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P4[1]                                                                                                                                        |                                                                                           | _                                                                                                                                                                | А,                                                                                          | I, M, P2[1                                                                                    |                                                                                                                     | 41 <b>=</b> P2[0], A,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7<br>8                                                                                             | 1/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P3[7]                                                                                                                                        |                                                                                           | _                                                                                                                                                                |                                                                                             | M,P4[7<br>M,P4[5                                                                              |                                                                                                                     | 40 <b>=</b> P4[6],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0<br>9                                                                                             | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P3[5]<br>P3[3]                                                                                                                               |                                                                                           | -                                                                                                                                                                |                                                                                             | M,P4[3                                                                                        |                                                                                                                     | 39 <b>⊑</b> P4[4],M<br>38 <b>⊑</b> P4[2],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9<br>10                                                                                            | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P3[1]                                                                                                                                        |                                                                                           | _                                                                                                                                                                |                                                                                             | M,P4[1                                                                                        |                                                                                                                     | 37 <b>=</b> P4[0],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10                                                                                                 | 1/0                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P5[7]                                                                                                                                        |                                                                                           | _                                                                                                                                                                |                                                                                             | M,P3[7                                                                                        |                                                                                                                     | QFN 36 P3[6],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12                                                                                                 | 1/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P5[5]                                                                                                                                        |                                                                                           | _                                                                                                                                                                |                                                                                             | M,P3[5<br>M,P3[3                                                                              |                                                                                                                     | (Top View) 35 	P3[4],M<br>34 	P3[2],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13                                                                                                 | 1/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P5[3]                                                                                                                                        |                                                                                           | _                                                                                                                                                                |                                                                                             | M,P3[1                                                                                        | ] = 10                                                                                                              | 33 <b>=</b> P3[0],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 14                                                                                                 | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                     | M                                                                     | P5[1]                                                                                                                                        |                                                                                           |                                                                                                                                                                  |                                                                                             | M,P5[7                                                                                        |                                                                                                                     | 32 <b>=</b> P5[6],M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |