Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART, USB                                  |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 69                                                                              |

| Program Memory Size        | 192KB (192K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 16К х 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x8/12b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LFQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f110phafb-30 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

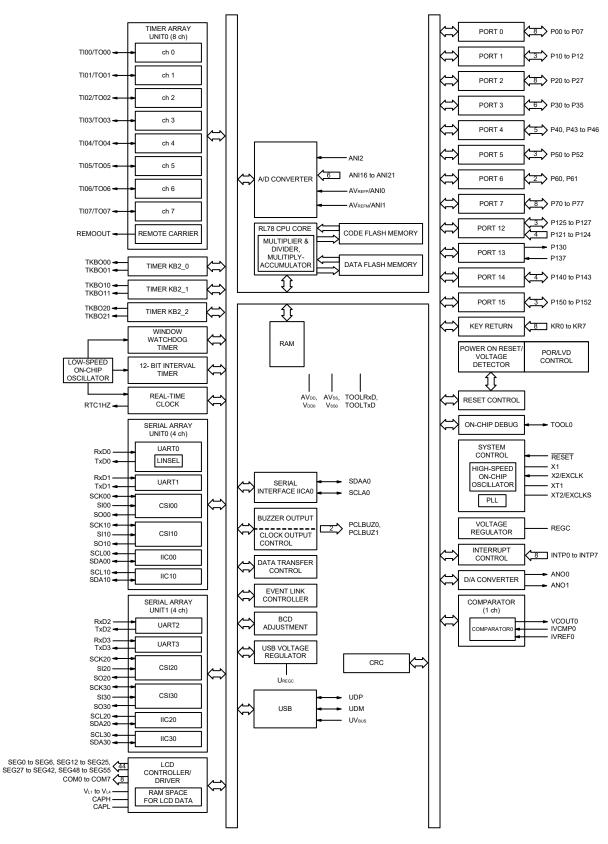

# 1.5 Block Diagram

# 1.5.1 80/85-pin products (with USB)

| Absolute Max | solute Maximum Ratings (TA = 25°C) |                                |                                     |                           |      |  |

|--------------|------------------------------------|--------------------------------|-------------------------------------|---------------------------|------|--|

| Parameter    | Symbols                            |                                | Conditions                          | Ratings                   | Unit |  |

| LCD voltage  | VLI1                               | VL1 input voltage              | Note 1                              | -0.3 to +2.8              | V    |  |

|              | VLI2                               | VL2 input voltage              | Note 1                              | -0.3 to +6.5              | V    |  |

|              | VLI3                               | VL3 input voltage              | Note 1                              | -0.3 to +6.5              | V    |  |

| VLI4         | VLI4                               | VL4 input voltage <sup>I</sup> | Note 1                              | -0.3 to +6.5              | V    |  |

|              | VLI5                               | CAPL, CAPH inpu                | it voltage <sup>Note 1</sup>        | -0.3 to +6.5              | V    |  |

|              | VLO1                               | VL1 output voltage             | •                                   | -0.3 to +2.8              | V    |  |

|              | VLO2                               | VL2 output voltage             | )                                   | -0.3 to +6.5              | V    |  |

|              | VLO3                               | VL3 output voltage             | )                                   | -0.3 to +6.5              | V    |  |

|              | VLO4                               | VL4 output voltage             | )                                   | -0.3 to +6.5              | V    |  |

|              | VLO5                               | CAPL, CAPH outp                | out voltage                         | -0.3 to +6.5              | V    |  |

|              | VLO6                               | COM0 to COM7                   | External resistance division method | -0.3 to VDD + 0.3 Note 2  | V    |  |

|              |                                    | SEG0 to SEG55                  | Capacitor split method              | -0.3 to VDD + 0.3 Note 2  | V    |  |

|              |                                    | output voltage                 | Internal voltage boosting method    | -0.3 to VLI4 + 0.3 Note 2 | V    |  |

Note 1. This value only indicates the absolute maximum ratings when applying voltage to the VL1, VL2, VL3, and VL4 pins; it does not mean that applying voltage to these pins is recommended. When using the internal voltage boosting method or capacitance split method, connect these pins to Vss via a capacitor (0.47 ± 30%) and connect a capacitor (0.47 ± 30%) between the CAPL and CAPH pins.

Note 2. Must be 6.5 V or lower.

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

- Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the LCD controller/driver, A/D converter, D/A converter, comparator, LVD circuit, USB 2.0 function module, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- Note 2. During HALT instruction execution by flash memory.

- **Note 3.** When high-speed on-chip oscillator and subsystem clock are stopped.

- Note 4. When high-speed system clock and subsystem clock are stopped.

- **Note 5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the real-time clock 2 is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- Note 6. Not including the current flowing into the real-time clock 2, 12-bit interval timer, and watchdog timer.

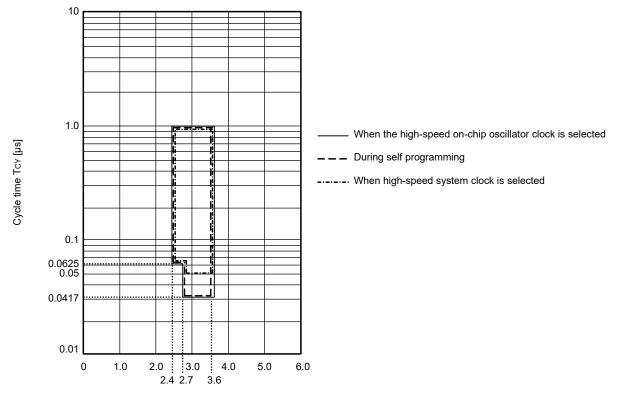

- Note 7. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

- HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}_{@}1 \text{ MHz}$  to 24 MHz

- 2.4 V ≤ VDD ≤ 3.6 V@1 MHz to 16 MHz

- LS (low-speed main) mode:  $1.8 \text{ V} \le \text{VDD} \le 3.6 \text{ V} @1 \text{ MHz}$  to 8 MHz

- LV (low-voltage main) mode 1.6 V ≤ VDD ≤ 3.6 V@1 MHz to 4 MHz

- Note 8. Regarding the value for current to operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- **Remark 2.** fHOCO: High-speed on-chip oscillator clock frequency (48 MHz max.)

- **Remark 3.** file: Main system clock source frequency when the high-speed on-chip oscillator clock divided 1, 2, 4, or 8, or the PLL clock divided by 2, 4, or 8 is selected (24 MHz max.)

- **Remark 4.** fSUB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

| Note 1. | Current flowing to VDD.                                                                                                     |

|---------|-----------------------------------------------------------------------------------------------------------------------------|

| Note 2. | When high speed on-chip oscillator and high-speed system clock are stopped.                                                 |

| Note 3. | Current flowing only to the real-time clock 2 (excluding the operating current of the low-speed on-chip oscillator and the  |

|         | XT1 oscillator). The supply current of the RL78 microcontrollers is the sum of the values of either IDD1 or IDD2, and IRTC, |

|         | when the real-time clock 2 operates in operation mode or HALT mode. When the low-speed on-chip oscillator is selected,      |

|         | IFIL should be added. IDD2 subsystem clock operation includes the operational current of the real-time clock 2.             |

| Note 4. | Current flowing only to the 12-bit interval timer (excluding the operating current of the low-speed on-chip oscillator and  |

- illator and N the XT1 oscillator). The supply current of the RL78 microcontrollers is the sum of the values of either IDD1 or IDD2, and ITMKA, when the 12-bit interval timer operates in operation mode or HALT mode. When the low-speed on-chip oscillator is selected, IFIL should be added. IDD2 subsystem clock operation includes the operational current of the 12-bit interval timer.

- Note 5. Current flowing only to the watchdog timer (including the operating current of the low-speed on-chip oscillator). The current value of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and IWDT when the watchdog timer operates in STOP mode.

- Note 6. Current flowing only to the A/D converter. The supply current of the RL78 microcontrollers is the sum of IDD1 or IDD2 and IADC, IAVREF, IADREF when the A/D converter operates in an operation mode or the HALT mode.

- Note 7. Current flowing to the AVDD.

- Note 8. Current flowing from the reference voltage source of A/D converter.

- Note 9. Operation current flowing to the internal reference voltage.

- Note 10 Current flowing to the AVREFP.

- Current flowing only to the D/A converter. The current value of the RL78 microcontrollers is the sum of IDD1 or IDD2 and Note 11. IDA when the D/A converter operates in an operation mode or the HALT mode.

- Note 12. Current flowing only to the comparator circuit. The current value of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and ICMP when the comparator circuit operates in the Operating, HALT or STOP mode.

- Note 13. Current flowing only to the LVD circuit. The current value of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and ILVI when the LVD circuit operates in the Operating, HALT or STOP mode.

- Note 14. Current flowing only during self-programming.

- Note 15. Current flowing only during data flash rewrite.

- For shift time to the SNOOZE mode, see 23.3.3 SNOOZE mode in the RL78/L1C User's Manual. Note 16.

- Note 17. Current flowing only to the LCD controller/driver (VDD pin). The current value of the RL78 microcontrollers is the sum of the LCD operating current (ILCD1, ILCD2 or ILCD3) to the supply current (IDD1, or IDD2) when the LCD controller/driver operates in an operation mode or HALT mode. Not including the current that flows through the LCD panel.

- Note 18. Not including the current that flows through the external divider resistor divider resistor.

- Note 19. Current flowing to the UVBUS.

- Note 20. Including the operating current when fPLL = 48 MHz.

- Note 21. Including the current supplied from the pull-up resistor of the UDP pin to the pull-down resistor of the host device, in addition to the current consumed by this MCU during the suspended state.

- Remark 1. fil: Low-speed on-chip oscillator clock frequency

- Remark 2. fSUB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 3. fCLK: CPU/peripheral hardware clock frequency

- Remark 4. Temperature condition of the TYP. value is TA = 25°C

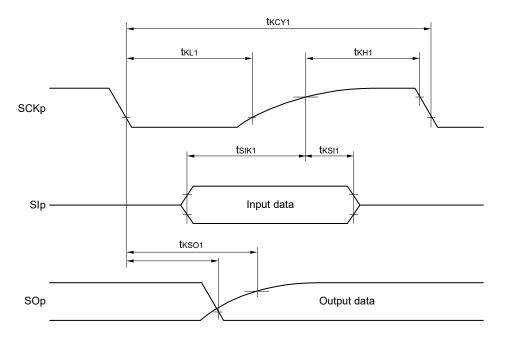

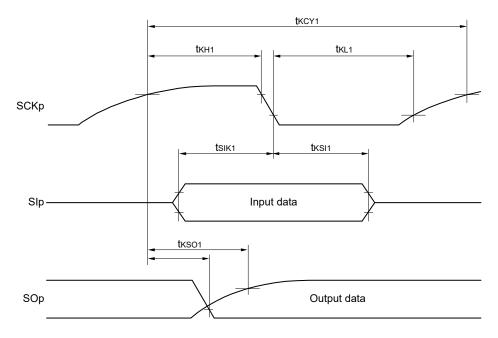

# (2) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output, corresponding CSI00 only)

| Parameter                                                   | Symbol | Symbol Conditions              |                                                                  | HS (high-speed main)<br>Mode |      | LS (low-speed main)<br>Mode |    | LV (low-voltage main)<br>Mode |    | Unit |

|-------------------------------------------------------------|--------|--------------------------------|------------------------------------------------------------------|------------------------------|------|-----------------------------|----|-------------------------------|----|------|

|                                                             |        |                                |                                                                  | MIN.                         | MAX. | MAX. MIN. MAX. MIN. MAX.    |    |                               |    |      |

| SCKp cycle time                                             | tKCY1  | tĸcy1 ≥ fcLĸ/2                 | $2.7~\textrm{V} \leq \textrm{V}_\textrm{DD} \leq 3.6~\textrm{V}$ | 167                          |      | 250                         |    | 500                           |    | ns   |

| SCKp high-/<br>low-level width                              | tKL1   | $2.7 V \leq V_{DD} \leq 3.6 V$ |                                                                  | tксү1/2 - 10                 |      | tксү1/2 - 50                |    | tксү1/2 - 50                  |    | ns   |

| Slp setup time<br>(to SCKp↑) <sup>Note 1</sup>              | tsik1  | 2.7 V ≤ V <sub>DD</sub> ≤      | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$     |                              |      | 110                         |    | 110                           |    | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 2</sup>             | tKSI1  | 2.7 V ≤ V <sub>DD</sub> ≤      | $2.7 V \le V_{DD} \le 3.6 V$                                     |                              |      | 10                          |    | 10                            |    | ns   |

| Delay time from<br>SCKp↓ to SOp<br>output <sup>Note 3</sup> | tKSO1  | C = 20 pF Note 4               | C = 20 pF Note 4                                                 |                              | 10   |                             | 10 |                               | 10 | ns   |

#### $(T_A = -40 \text{ to } +85^{\circ}C, 2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

Note 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The Slp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 4. C is the load capacitance of the SCKp and SOp output lines.

Caution Select the normal input buffer for the SIp pin and the normal output mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

Remark 1. p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0), g: PIM number (g = 2)

Remark 2. fMCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00))

| RL | _78/L | _1C |

|----|-------|-----|

|    |       |     |

| Parameter                      | Sym<br>bol                  | С                                                            | onditions                                                    | HS (high-spee<br>Mode | HS (high-speed main)<br>Mode |              | LS (low-speed main)<br>Mode |               | LV (low-voltage main)<br>Mode |    |

|--------------------------------|-----------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------|------------------------------|--------------|-----------------------------|---------------|-------------------------------|----|

| b                              |                             |                                                              |                                                              | MIN.                  | MAX.                         | MIN.         | MAX.                        | MIN.          | MAX.                          |    |

| SCKp cycle time                | SCKp cycle time tKCY1 tKCY1 | tĸcy1 ≥ fclk/4                                               | $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$           | 167                   |                              | 500          |                             | 1000          |                               | ns |

|                                |                             |                                                              | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$           | 250                   |                              | 500          |                             | 1000          |                               | ns |

|                                |                             |                                                              | 1.8 V ≤ VDD ≤ 3.6 V                                          | -                     |                              | 500          |                             | 1000          |                               | ns |

|                                |                             |                                                              | 1.6 V ≤ VDD ≤ 3.6 V                                          | -                     |                              | —            |                             | 1000          |                               | ns |

| SCKp high-/                    | tĸнı,                       | 2.7 V ≤ VDD ≤ 3                                              | 3.6 V                                                        | tксү1/2 - 18          |                              | tkcy1/2 - 50 |                             | tkcy1/2 - 50  |                               | ns |

| low-level width                | tĸ∟1                        | 2.4 V ≤ VDD ≤ 3                                              | 3.6 V                                                        | tксү1/2 <b>-</b> 38   |                              | tkcy1/2 - 50 |                             | tkcy1/2 - 50  |                               | ns |

|                                |                             | 1.8 V ≤ VDD ≤ 3                                              | -                                                            |                       | tkcy1/2 - 50                 |              | tkcy1/2 - 50                |               | ns                            |    |

|                                |                             | $1.6 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ |                                                              | -                     |                              | —            |                             | tkcy1/2 - 100 |                               | ns |

| SIp setup time                 | tsik1                       | 2.7 V ≤ VDD ≤ 3                                              | 44                                                           |                       | 110                          |              | 110                         |               | ns                            |    |

| (to SCKp↑) <sup>Note 1</sup>   |                             | 2.4 V ≤ VDD ≤ 3                                              | 75                                                           |                       | 110                          |              | 110                         |               | ns                            |    |

|                                |                             | 1.8 V ≤ VDD ≤                                                | 3.6 V                                                        | _                     |                              | 110          |                             | 110           |                               | ns |

|                                |                             | 1.6 V ≤ VDD ≤ 3                                              | 3.6 V                                                        | _                     |                              | —            |                             | 220           |                               | ns |

| SIp hold time                  | tKSI1                       | $2.4 \text{ V} \leq \text{VDD} \leq 3$                       | 3.6 V                                                        | 19                    |                              | 19           |                             | 19            |                               | ns |

| (from SCKp↑) <sup>Note 2</sup> |                             | 1.8 V ≤ VDD ≤ 3                                              | .8 V ≤ VDD ≤ 3.6 V                                           |                       |                              | 19           |                             | 19            |                               | ns |

|                                |                             | 1.6 V ≤ VDD ≤ 3                                              | 3.6 V                                                        | —                     |                              | —            |                             | 19            |                               | ns |

| Delay time from                | tKSO1                       |                                                              | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ |                       | 25                           |              | 50                          |               | 50                            | ns |

| SCKp↓ to SOp output<br>Note 3  |                             | Note 4                                                       | $2.4 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ |                       | 25                           |              | 50                          |               | 50                            | ns |

|                                |                             |                                                              | 1.8 V ≤ VDD ≤ 3.6 V                                          |                       | —                            |              | 50                          |               | 50                            | ns |

|                                |                             |                                                              | 1.6 V ≤ VDD ≤ 3.6 V                                          |                       | _                            |              | _                           |               | 50                            | ns |

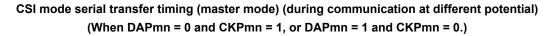

# (3) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output) (TA = -40 to +85°C, 1.6 V $\leq$ VDD $\leq$ 3.6 V, Vss = 0 V)

Note 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

Note 4. C is the load capacitance of the SCKp and SOp output lines.

Caution Select the normal input buffer for the SIp pin and the normal output mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

**Remark 1.** p: CSI number (p = 00, 10, 20, 30), m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), g: PIM number (g = 0 to 3)

Remark 2. fMCK: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13))

### (3) BC option standard

### (TA = -40 to +85°C, 4.35 V $\leq$ UVBUS $\leq$ 5.25 V, 2.4 V $\leq$ VDD $\leq$ 3.6 V, VSS = 0 V, HS (High-speed main) mode only)

| Para                    | meter         |      | Symbol  | Conditions | MIN. | TYP.    | MAX. | Unit    |        |         |        |    |        |

|-------------------------|---------------|------|---------|------------|------|---------|------|---------|--------|---------|--------|----|--------|

| UDP/UDM input reference | VDSELi [3: 0] | 0000 | VDDET0  |            | 27   | 32      | 37   | %UVBUS  |        |         |        |    |        |

| voltage                 | (i = 0, 1)    | 0001 | VDDET1  |            | 29   | 34      | 39   | %UVBUS  |        |         |        |    |        |

| (UVBUS divider ratio)   |               |      | 0010    | VDDET2     |      | 32      | 37   | 42      | %UVBUS |         |        |    |        |

| (Function)              |               | 0011 | VDDET3  |            | 35   | 40      | 45   | %UVBUS  |        |         |        |    |        |

|                         |               | 0100 | VDDET4  |            | 38   | 43      | 48   | %UVBUS  |        |         |        |    |        |

|                         |               | 0101 | VDDET5  |            | 41   | 46      | 51   | %UVBUS  |        |         |        |    |        |

|                         |               | 0110 | VDDET6  |            | 44   | 49      | 54   | %UVBUS  |        |         |        |    |        |

|                         |               | 0111 | VDDET7  |            | 47   | 52      | 57   | %UVBUS  |        |         |        |    |        |

|                         |               |      | 1       |            | 1000 | VDDET8  |      | 51      | 56     | 61      | %UVBUS |    |        |

|                         |               | 1001 | VDDET9  |            | 55   | 60      | 65   | %UVBUS  |        |         |        |    |        |

|                         |               |      | 1010    | VDDET10    |      | 59      | 64   | 69      | %UVBUS |         |        |    |        |

|                         |               |      | 1011    | VDDET11    |      | 63      | 68   | 73      | %UVBUS |         |        |    |        |

|                         |               |      |         |            |      |         | 1100 | VDDET12 |        | 67      | 72     | 73 | %UVBUS |

|                         |               |      |         |            |      |         |      |         | 1101   | VDDET13 |        | 71 | 76     |

|                         |               |      |         |            | 1110 | VDDET14 |      | 75      | 80     | 85      | %UVBUS |    |        |

|                         |               | 1111 | VDDET15 |            | 79   | 84      | 89   | %UVBUS  |        |         |        |    |        |

(3) When reference voltage (+) = AVDD (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI0 to ANI6

# (TA = -40 to +85°C, 1.6 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = 0 V, AVss = 0 V, Reference voltage (+) = AVDD, Reference voltage (-) = AVss = 0 V)

| Parameter                    | Symbol | Con                                               | ditions                                                       | MIN.   | TYP.     | MAX.      | Unit |  |

|------------------------------|--------|---------------------------------------------------|---------------------------------------------------------------|--------|----------|-----------|------|--|

| Resolution                   | Res    |                                                   | $2.4 \text{ V} \leq \text{AV}_{\text{DD}} \leq 3.6 \text{ V}$ | 8      |          | 12        | bit  |  |

|                              |        |                                                   | 1.8 V ≤ AVDD ≤ 3.6 V                                          | 8      |          | 10 Note 1 |      |  |

|                              |        |                                                   | 1.6 V ≤ AVDD ≤ 3.6 V                                          |        | 8 Note 2 |           |      |  |

| Overall error Note 3         | AINL   | 12-bit resolution                                 | 2.4 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±7.5      | LSB  |  |

|                              |        | 10-bit resolution                                 | 1.8 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±5.5      |      |  |

|                              |        | 8-bit resolution                                  | 1.6 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±3.0      |      |  |

| Conversion time              | tCONV  | ADTYP = 0,<br>12-bit resolution                   | $2.4 \text{ V} \leq \text{AVDD} \leq 3.6 \text{ V}$           | 3.375  |          |           | μs   |  |

|                              |        | ADTYP = 0,<br>10-bit resolution <sup>Note 1</sup> | 1.8 V ≤ AVDD ≤ 3.6 V                                          | 6.75   |          |           |      |  |

|                              |        | ADTYP = 0,<br>8-bit resolution <sup>Note 2</sup>  | 1.6 V ≤ AVDD ≤ 3.6 V                                          | 13.5   |          |           |      |  |

|                              |        | ADTYP = 1,                                        | $2.4 \text{ V} \leq \text{AV}_{\text{DD}} \leq 3.6 \text{ V}$ | 2.5625 |          |           |      |  |

|                              |        | 8-bit resolution                                  | 1.8 V ≤ AVDD ≤ 3.6 V                                          | 5.125  |          |           |      |  |

|                              |        |                                                   | 1.6 V ≤ AVDD ≤ 3.6 V                                          | 10.25  |          |           |      |  |

| Zero-scale error Note 3      | Ezs    | 12-bit resolution                                 | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |        |          | ±6.0      | LSB  |  |

|                              |        | 10-bit resolution                                 | 1.8 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±5.0      |      |  |

|                              |        | 8-bit resolution                                  | 1.6 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±2.5      |      |  |

| Full-scale error Note 3      | Efs    | 12-bit resolution                                 | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |        |          | ±6.0      | LSB  |  |

|                              |        | 10-bit resolution                                 | 1.8 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±5.0      |      |  |

|                              |        | 8-bit resolution                                  | 1.6 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±2.5      |      |  |

| Integral linearity error     | ILE    | 12-bit resolution                                 | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |        |          | ±3.0      | LSB  |  |

| Note 3                       |        | 10-bit resolution                                 | 1.8 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±2.0      |      |  |

|                              |        | 8-bit resolution                                  | 1.6 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±1.5      |      |  |

| Differential linearity error | DLE    | 12-bit resolution                                 | $2.4 \text{ V} \leq \text{AV}_{\text{DD}} \leq 3.6 \text{ V}$ |        |          | ±2.0      | LSB  |  |

| Note 3                       |        | 10-bit resolution                                 | 1.8 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±2.0      |      |  |

|                              |        | 8-bit resolution                                  | 1.6 V ≤ AVDD ≤ 3.6 V                                          |        |          | ±1.5      |      |  |

| Analog input voltage         | VAIN   | ANI0 to ANI6                                      | 1                                                             | 0      |          | AVdd      | V    |  |

Note 1. Cannot be used for lower 2 bit of ADCR register

**Note 2.** Cannot be used for lower 4 bit of ADCR register

**Note 3.** Excludes quantization error (±1/2 LSB).

Caution Always use AVDD pin with the same potential as the VDD pin.

# (6) When reference voltage (+) = Internal reference voltage (1.45 V) (ADREFP1 = 1, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI0 to ANI6, ANI16 to ANI21

(TA = -40 to +85°C, 2.4 V  $\leq$  VDD  $\leq$  3.6 V, 1.6 V  $\leq$  VDD, 1.6 V  $\leq$  AVDD = VDD, Vss = 0 V, AVss = 0 V, Reference voltage (+) = internal reference voltage, Reference voltage (-) = AVss = 0 V, HS (high-speed main) mode)

| Parameter                         | Symbol   | Conditions MIN. TYP. MAX.           |      | MAX. | Unit |     |  |

|-----------------------------------|----------|-------------------------------------|------|------|------|-----|--|

| Resolution                        | Res      |                                     |      | 8    |      |     |  |

| Conversion time                   | tCONV    | 8-bit resolution                    | 16   |      |      | μs  |  |

| Zero-scale error Note             | Ezs      | 8-bit resolution                    |      |      | ±4.0 | LSB |  |

| Integral linearity error Note     | ILE      | 8-bit resolution                    |      |      | ±2.0 | LSB |  |

| Differential linearity error Note | DLE      | 8-bit resolution                    |      |      | ±2.5 | LSB |  |

| Reference voltage (+)             | AVREF(+) | = Internal reference voltage (VBGR) | 1.38 | 1.45 | 1.5  | V   |  |

| Analog input voltage              | VAIN     |                                     | 0    |      | Vbgr | V   |  |

**Note** Excludes quantization error (±1/2 LSB).

Caution Always use AVDD pin with the same potential as the VDD pin.

## 2.6.2 Temperature sensor, internal reference voltage output characteristics

| Parameter                         | Symbol         | Conditions                                                        | MIN. | TYP. | MAX. | Unit  |

|-----------------------------------|----------------|-------------------------------------------------------------------|------|------|------|-------|

| Temperature sensor output voltage | VTMPS25        | Setting ADS register = 80H, TA = +25°C                            |      | 1.05 |      | V     |

| Internal reference voltage        | Vbgr           | Setting ADS register = 81H                                        | 1.38 | 1.45 | 1.5  | V     |

| Temperature coefficient           | <b>F</b> VTMPS | Temperature sensor output voltage that depends on the temperature |      | -3.6 |      | mV/°C |

| Operation stabilization wait time | tamp           |                                                                   | 10   |      |      | μs    |

# 2.6.3 D/A converter characteristics

#### $(TA = -40 \text{ to } +85^{\circ}C, 1.6 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter     | Symbol       | Cor           | MIN.                                               | TYP. | MAX. | Unit |     |

|---------------|--------------|---------------|----------------------------------------------------|------|------|------|-----|

| Resolution    | Res          |               |                                                    |      |      | 8    | bit |

| Overall error | AINL         | Rload = 4 MΩ  | $1.8 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |      |      | ±2.5 | LSB |

|               |              | Rload = 8 MΩ  | $1.8 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |      |      | ±2.5 | LSB |

| Settling time | <b>t</b> SET | Cload = 20 pF | $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |      |      | 3    | μs  |

|               |              |               | $1.6 \text{ V} \leq \text{VDD} < 2.7 \text{ V}$    |      |      | 6    | μs  |

- Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or Vss. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the LCD controller/driver, A/D converter, D/A converter, comparator, LVD circuit, USB 2.0 function module, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- Note 2. During HALT instruction execution by flash memory.

- **Note 3.** When high-speed on-chip oscillator and subsystem clock are stopped.

- Note 4. When high-speed system clock and subsystem clock are stopped.

- **Note 5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the real-time clock 2 is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- Note 6. Not including the current flowing into the real-time clock 2, 12-bit interval timer, and watchdog timer.

- Note 7.

Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

HS (high-speed main) mode:

2.7 V ≤ VDD ≤ 3.6 V@1 MHz to 24 MHz

- $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}@1 \text{ MHz}$  to 16 MHz

- Note 8. Regarding the value for current to operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- Remark 2. fHOCO: High-speed on-chip oscillator clock frequency (48 MHz max.)

- Remark 3. fill: Main system clock source frequency when the high-speed on-chip oscillator clock divided 1, 2, 4, or 8, or the PLL clock divided by 2, 4, or 8 is selected (24 MHz max.)

- Remark 4. fSUB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

| Parameter                                            | Symbol                 |                                           | Conditio                                     | ons                      |                                             | MIN. | TYP.         | MAX.         | Unit |

|------------------------------------------------------|------------------------|-------------------------------------------|----------------------------------------------|--------------------------|---------------------------------------------|------|--------------|--------------|------|

| Low-speed<br>on-chip oscillator<br>operating current | FIL Note 1             |                                           |                                              |                          |                                             |      | 0.20         |              | μA   |

| RTC2 operating<br>current                            | IRTC<br>Notes 1, 3     |                                           |                                              |                          |                                             |      |              |              | μA   |

| 12-bit interval<br>timer operating<br>current        | ITMKA<br>Notes 1, 2, 4 |                                           |                                              |                          |                                             |      | 0.02         |              | μA   |

| Watchdog timer operating current                     | IWDT<br>Notes 1, 2, 5  | fi∟ = 15 kHz                              |                                              |                          |                                             |      | 0.22         |              | μA   |

| A/D converter<br>operating current                   | IADC<br>Notes 6, 7     | AVDD = 3.0 V, whe                         | n conversion at maximu                       | ım speed                 |                                             |      | 422          | 720          | μA   |

| AVREF (+) current                                    | IAVREF Note 8          | AVDD = 3.0 V, ADR                         | NDD = 3.0 V, ADREFP1 = 0, ADREFP0 = 0 Note 7 |                          |                                             |      | 14.0         | 25.0         | μA   |

|                                                      |                        | AVREFP = 3.0 V, AI<br>ADREFP1 = 1, AD     | DREFP1 = 0, ADREFP0                          | ) = 1 Note 10            |                                             |      | 14.0<br>14.0 | 25.0<br>25.0 |      |

| A/D converter<br>reference voltage<br>current        | IADREF<br>Notes 1, 9   | VDD = 3.0 V                               |                                              |                          |                                             |      | 75.0         |              | μA   |

| Temperature<br>sensor operating<br>current           | ITMPS Note 1           |                                           |                                              |                          |                                             |      | 78           |              | μA   |

| D/A converter operating current                      | IDAC<br>Notes 1, 11    | Per D/A converter                         | Per D/A converter channel                    |                          |                                             |      | 0.53         | 1.5          | mA   |

| Comparator                                           |                        | VDD = 3.6 V,                              | Window mode                                  |                          |                                             |      | 12.5         |              | μA   |

| operating current                                    | Notes 1, 12            | Regulator output<br>voltage = 2.1 V       | Comparator high-spee                         |                          |                                             |      | 4.5          |              | μA   |

|                                                      |                        |                                           | Comparator low-speed                         | d mode                   |                                             |      | 1.2          |              | μA   |

| LVD operating<br>current                             | ILVD<br>Notes 1, 13    |                                           |                                              |                          |                                             |      | 0.06         |              | μA   |

| Self-programming operating current                   | IFSP<br>Notes 1, 14    |                                           |                                              |                          |                                             |      | 2.50         | 12.20        | mA   |

| BGO operating<br>current                             | IBGO<br>Notes 1, 15    |                                           |                                              |                          |                                             |      | 1.68         | 12.20        | mA   |

| SNOOZE                                               | ISNOZ Note 1           | ADC operation                             | The mode is performe                         | d Note 16                |                                             |      | 0.34         | 1.10         | mA   |

| operating current                                    |                        |                                           | The A/D conversion of<br>mode, AVREFP = VDD  |                          | erformed, Low voltage                       |      | 0.53         | 2.04         |      |

|                                                      |                        | CSI/UART operation                        | on                                           |                          |                                             |      | 0.70         | 1.54         | mA   |

| LCD operating<br>current                             | ILCD1<br>Notes 17, 18  | External<br>resistance<br>division method | fLCD = fSUB<br>LCD clock = 128 Hz            | 1/3 bias<br>4-time slice | VDD = 3.6 V,<br>LV4 = 3.6 V                 |      | 0.14         |              | μA   |

|                                                      | ILCD2<br>Note 17       | Internal voltage<br>boosting method       | fLCD = fSUB<br>LCD clock = 128 Hz            | 1/3 bias<br>4-time slice | VDD = 3.0 V,<br>LV4 = 3.0 V<br>(VLCD = 04H) |      | 0.61         |              | μA   |

|                                                      | ILCD3<br>Note 17       | Capacitor split<br>method                 | fLCD = fSUB<br>LCD clock = 128 Hz            | 1/3 bias<br>4-time slice | VDD = 3.0 V,<br>Lv4 = 3.0 V                 |      | 0.12         |              | μA   |

| 1100                                                 | IUSB Note 20           | Operating current of                      | u<br>during USB communica                    | tion                     | 1                                           |      | 4.88         |              | mA   |

| USB current<br>Note 19                               | 1036                   | 1 0                                       |                                              |                          |                                             |      |              |              |      |

### $(TA = -40 \text{ to } +105^{\circ}C, 2.4 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

(Notes and Remarks are listed on the next page.)

## 3.4 AC Characteristics

## 3.4.1 Basic operation

#### $(TA = -40 \text{ to } +105^{\circ}C, 2.4 \text{ V} \le \text{AVDD} = \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

Symbol Conditions MIN. TYP. MAX. Unit Items Тсү HS (high-speed main) 0.0417 Instruction cycle Main system  $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 1 μs (minimum instruction clock (fMAIN) mode  $2.4 \text{ V} \leq \text{VDD} < 2.7 \text{ V}$ 0.0625 1 μs execution time) operation Subsystem clock (fSUB) operation  $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 28.5 30.5 31.3 μs In the self-HS (high-speed main)  $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 0.0417 1 μs programming mode 0.0625 2.4 V ≤ VDD < 2.7 V 1 μs mode External main system fEX 2.7 V ≤ VDD ≤ 3.6 V 1.0 20.0 MHz clock frequency 2.4 V ≤ Vpp < 2.7 V 1.0 16.0 MHz fext 32 35 kHz External main system texн,  $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 24 ns clock input high-level tEXL 2.4 V ≤ VDD < 2.7 V 30 ns width, low-level width texns, 13.7 μs **t**EXLS TI00 to TI07 input 1/fмск + tтıн. ns high-level width, t⊤ı∟ 10 low-level width

Remark fMCK: Timer array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of timer mode register mn (TMRmn). m: Unit number (m = 0), n: Channel number (n = 0 to 7))

(1/2)

### RL78/L1C

Minimum Instruction Execution Time during Main System Clock Operation

TCY vs VDD (HS (high-speed main) mode)

Supply voltage VDD [V]

### CSI mode serial transfer timing (master mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

**Remark** p: CSI number (p = 00, 10, 20, 30), m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), g: PIM and POM number (g = 0 to 3)

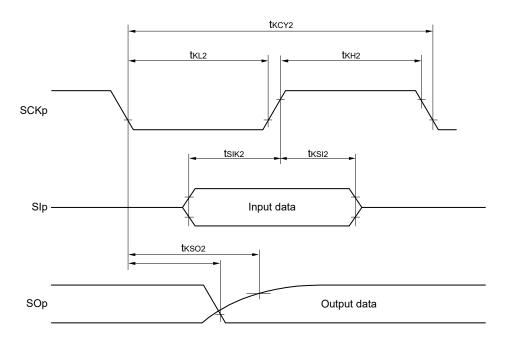

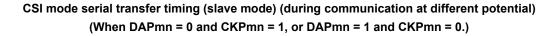

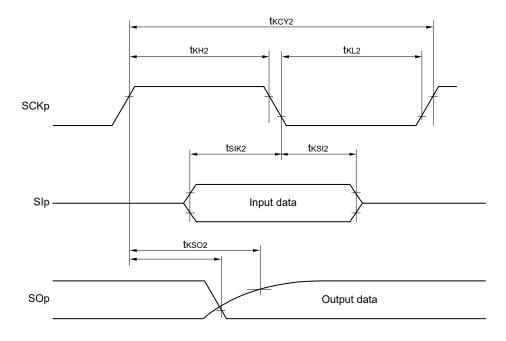

### CSI mode serial transfer timing (slave mode) (during communication at different potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

Remark

p: CSI number (p = 00, 10, 20, 30), m: Unit number (m = 0, 1),

n: Channel number (n = 0 to 3), g: PIM and POM number (g = 0 to 3)

(2) When reference voltage (+) = AVDD (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI0 to ANI6

# (TA = -40 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = 0 V, AVss = 0 V, Reference voltage (+) = AVDD, Reference voltage (-) = AVss = 0 V)

| Parameter                         | Symbol | C                               | Conditions                                                    | MIN.  | TYP. | MAX. | Unit |

|-----------------------------------|--------|---------------------------------|---------------------------------------------------------------|-------|------|------|------|

| Resolution                        | RES    |                                 | $2.4 \text{ V} \leq \text{AV}_{\text{DD}} \leq 3.6 \text{ V}$ | 8     |      | 12   | bit  |

| Overall error Note                | AINL   | 12-bit resolution               | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |       |      | ±7.5 | LSB  |

| Conversion time                   | tCONV  | ADTYP = 0,<br>12-bit resolution | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   | 3.375 |      |      | μs   |

| Zero-scale error Note             | Ezs    | 12-bit resolution               | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |       |      | ±6.0 | LSB  |

| Full-scale error Note             | EFS    | 12-bit resolution               | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |       |      | ±6.0 | LSB  |

| Integral linearity error Note     | ILE    | 12-bit resolution               | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |       |      | ±3.0 | LSB  |

| Differential linearity error Note | DLE    | 12-bit resolution               | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$   |       |      | ±2.0 | LSB  |

| Analog input voltage              | VAIN   |                                 | •                                                             | 0     |      | AVdd | V    |

Note Excludes quantization error (±1/2 LSB).

Caution Always use AVDD pin with the same potential as the VDD pin.

# (5) When reference voltage (+) = Internal reference voltage (1.45 V) (ADREFP1 = 1, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI0 to ANI6, ANI16 to ANI21

# (TA = -40 to +105°C, 2.4 V $\leq$ VDD $\leq$ 3.6 V, 2.4 V $\leq$ VDD, 2.4 V $\leq$ AVDD = VDD, Vss = 0 V, AVss = 0 V, Reference voltage (+) = internal reference voltage, Reference voltage (-) = AVss = 0 V, HS (high-speed main) mode)

| • • • •                           |          | • • • • • •                         |      |      |      | , ,  |

|-----------------------------------|----------|-------------------------------------|------|------|------|------|

| Parameter                         | Symbol   | Conditions                          | MIN. | TYP. | MAX. | Unit |

| Resolution                        | Res      |                                     |      | 8    |      | bit  |

| Conversion time                   | tCONV    | 8-bit resolution                    | 16.0 |      |      | μs   |

| Zero-scale error Note             | Ezs      | 8-bit resolution                    |      |      | ±4.0 | LSB  |

| Integral linearity error Note     | ILE      | 8-bit resolution                    |      |      | ±2.0 | LSB  |

| Differential linearity error Note | DLE      | 8-bit resolution                    |      |      | ±2.5 | LSB  |

| Reference voltage (+)             | AVREF(+) | = Internal reference voltage (VBGR) | 1.38 | 1.45 | 1.5  | V    |

| Analog input voltage              | VAIN     |                                     | 0    |      | Vbgr | V    |

**Note** Excludes quantization error (±1/2 LSB).

Caution Always use AVDD pin with the same potential as the VDD pin.

### 3.6.2 Temperature sensor, internal reference voltage output characteristics

| •                                 |                |                                                                   |      |      |      |       |

|-----------------------------------|----------------|-------------------------------------------------------------------|------|------|------|-------|

| Parameter                         | Symbol         | Conditions                                                        | MIN. | TYP. | MAX. | Unit  |

| Temperature sensor output voltage | VTMPS25        | Setting ADS register = 80H, TA = +25°C                            |      | 1.05 |      | V     |

| Internal reference voltage        | Vbgr           | Setting ADS register = 81H                                        | 1.38 | 1.45 | 1.5  | V     |

| Temperature coefficient           | <b>F</b> VTMPS | Temperature sensor output voltage that depends on the temperature |      | -3.6 |      | mV/°C |

| Operation stabilization wait time | tamp           |                                                                   | 10   |      |      | μs    |

#### (TA = -40 to +105°C, 2.4 V ≤ VDD ≤ 3.6 V, VSS = 0 V (HS (high-speed main) mode))

## 3.6.3 D/A converter characteristics

#### $(TA = -40 \text{ to } +105^{\circ}C, 2.4 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

| Parameter     | Symbol | Conditions    |                                                    | MIN. | TYP. | MAX. | Unit |

|---------------|--------|---------------|----------------------------------------------------|------|------|------|------|

| Resolution    | Res    |               |                                                    |      |      | 8    | bit  |

| Overall error | AINL   | Rload = 4 MΩ  | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |      |      | ±2.5 | LSB  |

|               |        | Rload = 8 MΩ  | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |      |      | ±2.5 | LSB  |

| Settling time | tSET   | Cload = 20 pF | $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |      |      | 3    | μs   |

|               |        |               | $2.4 \text{ V} \leq \text{VDD} \leq 2.7 \text{ V}$ |      |      | 6    | μs   |

## 3.8.3 Capacitor split method

#### (1) 1/3 bias method

#### $(TA = -40 \text{ to } +105^{\circ}C, 2.4 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                        | Symbol | Conditions                                | MIN.           | TYP.    | MAX.           | Unit |

|----------------------------------|--------|-------------------------------------------|----------------|---------|----------------|------|

| V∟4 voltage                      | VL4    | C1 to C4 = 0.47 $\mu$ F <sup>Note 2</sup> |                | Vdd     |                | V    |

| VL2 voltage                      | VL2    | C1 to C4 = 0.47 µF Note 2                 | 2/3 VL4 - 0.07 | 2/3 VL4 | 2/3 VL4 + 0.07 | V    |

| VL1 voltage                      | VL1    | C1 to C4 = 0.47 µF Note 2                 | 1/3 VL4 - 0.08 | 1/3 VL4 | 1/3 VL4 + 0.08 | V    |

| Capacitor split wait time Note 1 | t∨wait |                                           | 100            |         |                | ms   |

Note 1. This is the wait time from when voltage bucking is started (VLCON = 1) until display is enabled (LCDON = 1).

Note 2. This is a capacitor that is connected between voltage pins used to drive the LCD.

C1: A capacitor connected between CAPH and CAPL

C2: A capacitor connected between VL1 and GND

C3: A capacitor connected between VL2 and GND

C4: A capacitor connected between VL4 and GND

C1 = C2 = C3 = C4 = 0.47 µF±30%

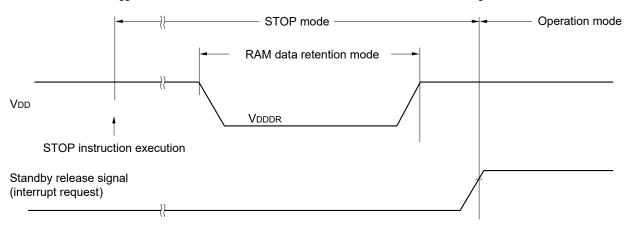

## 3.9 RAM Data Retention Characteristics

#### (TA = -40 to +105°C, Vss = 0 V)

| Parameter                     | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |

|-------------------------------|--------|------------|----------------------|------|------|------|

| Data retention supply voltage | Vdddr  |            | 1.44 <sup>Note</sup> |      | 3.6  | V    |

**Note** This depends on the POR detection voltage. For a falling voltage, data in RAM are retained until the voltage reaches the level that triggers a POR reset but not once it reaches the level at which a POR reset is generated.

# 3.10 Flash Memory Programming Characteristics

| Parameter                                      | Symbol       | Conditions                                                   | MIN.    | TYP.      | MAX. | Unit  |

|------------------------------------------------|--------------|--------------------------------------------------------------|---------|-----------|------|-------|

| CPU/peripheral hardware clock<br>frequency     | <b>f</b> CLK | $2.4 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ | 1       |           | 24   | MHz   |

| Number of code flash rewrites<br>Notes 1, 2, 3 | Cerwr        | Retained for 20 years<br>TA = 85°C <sup>Note 4</sup>         | 1,000   |           |      | Times |

| Number of data flash rewrites<br>Notes 1, 2, 3 |              | Retained for 1 year<br>TA = 25°C                             |         | 1,000,000 |      |       |

|                                                |              | Retained for 5 years<br>TA = 85°C <sup>Note 4</sup>          | 100,000 |           |      |       |

|                                                |              | Retained for 20 years<br>TA = 85°C <sup>Note 4</sup>         | 10,000  |           |      |       |

### $(TA = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

Note 1. 1 erase + 1 write after the erase is regarded as 1 rewrite. The retaining years are until next rewrite after the rewrite.

Note 2. When using flash memory programmer and Renesas Electronics self programming library

**Note 3.** These are the characteristics of the flash memory and the results obtained from reliability testing by Renesas Electronics Corporation.

**Note 4.** This temperature is the average value at which data are retained.

# 3.11 Dedicated Flash Memory Programmer Communication (UART)

#### $(TA = -40 \text{ to } +105^{\circ}C, 2.4 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter     | Symbol | Conditions                | MIN.    | TYP. | MAX.      | Unit |

|---------------|--------|---------------------------|---------|------|-----------|------|

| Transfer rate |        | During serial programming | 115,200 |      | 1,000,000 | bps  |

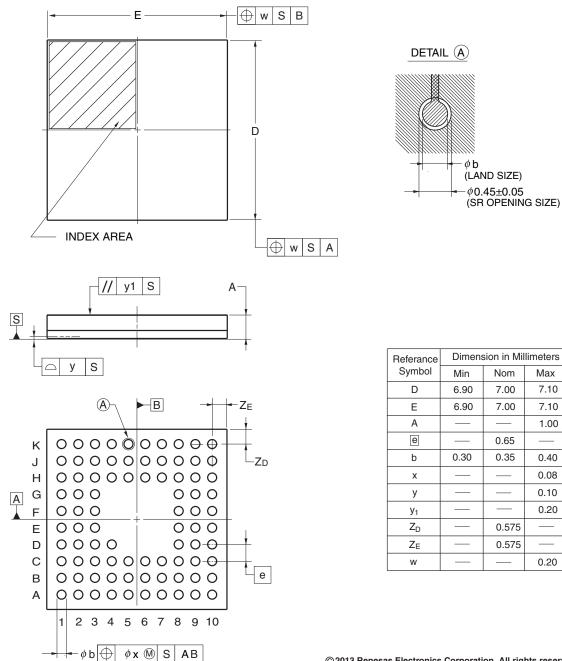

#### 4.2 85-pin products

R5F110NEALA, R5F110NFALA, R5F110NGALA, R5F110NHALA, R5F110NJALA R5F111NEALA, R5F111NFALA, R5F111NGALA, R5F111NHALA, R5F111NJALA R5F110NEGLA, R5F110NFGLA, R5F110NGGLA, R5F110NHGLA, R5F110NJGLA R5F111NEGLA, R5F111NFGLA, R5F111NGGLA, R5F111NHGLA, R5F111NJGLA

| JEITA Package code | RENESAS code | Previous code | MASS(TYP.)[g] |

|--------------------|--------------|---------------|---------------|

| P-VFLGA85-7x7-0.65 | PVLG0085JA-A | P85FC-65-BN4  | 0.1           |

©2013 Renesas Electronics Corporation. All rights reserved.