Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 24MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | LCD, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 55                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 8K x 8                                                                          |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                     |

| Data Converters            | A/D 11x8/12b; D/A 2x8b                                                          |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 80-LQFP                                                                         |

| Supplier Device Package    | 80-LQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f111mjafb-30 |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

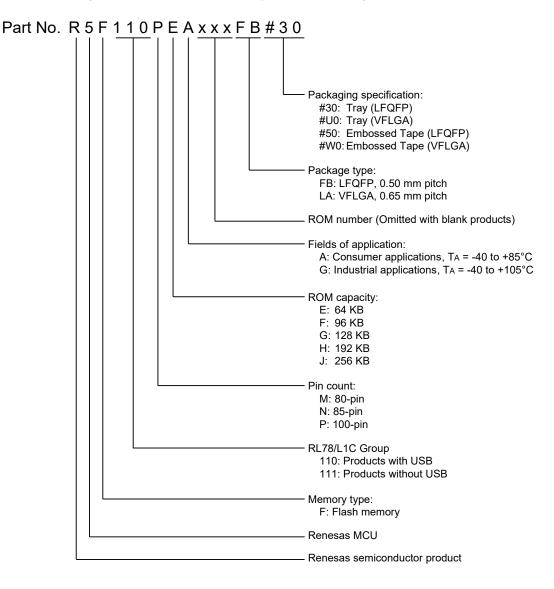

Caution Orderable part numbers are current as of when this manual was published. Please make sure to refer to the relevant product page on the Renesas website for the latest part numbers.

(1/2)

|                                    |                                        | 80/85-pin                                                                                                                                                                                                                                                                                        | 100-pin                                                          |  |  |  |

|------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

|                                    | Item                                   | R5F111Mx/R5F111Nx (x = E to H, J)                                                                                                                                                                                                                                                                | R5F111Px (x = E to H, J)                                         |  |  |  |

| Code flash memory                  | и (КВ)                                 | 64 to 256                                                                                                                                                                                                                                                                                        | 64 to 256                                                        |  |  |  |

| Data flash memory (KB) 8 8         |                                        |                                                                                                                                                                                                                                                                                                  |                                                                  |  |  |  |

| RAM (KB)                           |                                        | 8 to 16 Note 1                                                                                                                                                                                                                                                                                   | 8 to 16 Note 1                                                   |  |  |  |

| Memory space                       |                                        | 1 MB                                                                                                                                                                                                                                                                                             |                                                                  |  |  |  |

| Main system clock                  | High-speed system clock                | X1 (crystal/ceramic) oscillation, external main sys<br>1 to 20 MHz: VDD = 2.7 to 3.6 V, 1 to 8 MHz: VD                                                                                                                                                                                           |                                                                  |  |  |  |

|                                    | High-speed on-chip<br>oscillator clock | HS (high-speed main) operation mode: 1 to 24 Mi<br>HS (high-speed main) operation mode: 1 to 16 Mi<br>LS (low-speed main) operation mode: 1 to 8 MHz<br>LV (low-voltage main) operation mode: 1 to 4 MHz                                                                                         | Hz (VDD = 2.4 to 3.6 V,<br>(VDD = 1.8 to 3.6 V),                 |  |  |  |

| Subsystem clock                    |                                        | XT1 (crystal) oscillation, external subsystem clock<br>32.768 kHz (TYP.): VDD = 1.6 to 3.6 V                                                                                                                                                                                                     | r input (EXCLKS)                                                 |  |  |  |

| Low-speed on-chip                  | oscillator clock                       | 15 kHz (TYP.): VDD = 1.6 to 3.6 V                                                                                                                                                                                                                                                                |                                                                  |  |  |  |

| General-purpose re                 | gister                                 | 8 bits × 32 registers (8 bits × 8 registers × 4 banks)                                                                                                                                                                                                                                           |                                                                  |  |  |  |

| Minimum instruction execution time |                                        | 0.04167 $\mu$ s (High-speed on-chip oscillator clock: fHoco = fiH = 24 MHz operation)                                                                                                                                                                                                            |                                                                  |  |  |  |

|                                    |                                        | 0.05 μs (High-speed system clock: fмx = 20 MHz operation)                                                                                                                                                                                                                                        |                                                                  |  |  |  |

|                                    |                                        | 30.5 μs (Subsystem clock: fsue = 32.768 kHz ope                                                                                                                                                                                                                                                  | eration)                                                         |  |  |  |

| Instruction set                    |                                        | <ul> <li>Data transfer (8/16 bits)</li> <li>Adder and subtractor/logical operation (8/16 bits</li> <li>Multiplication (8 bits × 8 bits, 16 bits × 16 bits), I</li> <li>Multiplication and Accumulation (16 bits × 16 bit</li> <li>Rotate, barrel shift, and bit manipulation (Set, re</li> </ul> | Division (16 bits ÷ 16 bits, 32 bits ÷ 32 bits)<br>is + 32 bits) |  |  |  |

| I/O port                           | Total                                  | 63                                                                                                                                                                                                                                                                                               | 81                                                               |  |  |  |

|                                    | CMOS I/O                               | 55                                                                                                                                                                                                                                                                                               | 73                                                               |  |  |  |

|                                    | CMOS input                             | 5                                                                                                                                                                                                                                                                                                | 5                                                                |  |  |  |

|                                    | CMOS output                            | 1                                                                                                                                                                                                                                                                                                | 1                                                                |  |  |  |

|                                    | N-ch open-drain I/O<br>(6 V tolerance) | 2                                                                                                                                                                                                                                                                                                | 2                                                                |  |  |  |

| Timer                              | 16-bit timer TAU                       | 8 channels (with 1 channel remote control output 1                                                                                                                                                                                                                                               | function) (Timer outputs: 8, PWM outputs: 7 Note 2)              |  |  |  |

|                                    | 16-bit timer KB2                       | 3 channels (PWM outputs: 6)                                                                                                                                                                                                                                                                      |                                                                  |  |  |  |

|                                    | Watchdog timer                         | 1 channel                                                                                                                                                                                                                                                                                        |                                                                  |  |  |  |

|                                    | 12-bit interval timer                  | 1 channel                                                                                                                                                                                                                                                                                        |                                                                  |  |  |  |

|                                    | Real-time clock 2                      | 1 channel                                                                                                                                                                                                                                                                                        |                                                                  |  |  |  |

|                                    | RTC output                             | 1<br>1 Hz (subsystem clock: fs∪в = 32.768 kHz)                                                                                                                                                                                                                                                   |                                                                  |  |  |  |

**Note 1.** In the case of the 16 KB, this is about 15 KB when the self-programming function and data flash function are used (For details, see **CHAPTER 3** in the RL78/L1C User's Manual).

Note 2. The number of outputs varies, depending on the setting of channels in use and the number of the master.

- Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD, or Vss. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the LCD controller/driver, A/D converter, D/A converter, comparator, LVD circuit, USB 2.0 function module, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

Note 2. When high-speed on-chip oscillator and subsystem clock are stopped.

Note 3. When high-speed system clock and subsystem clock are stopped.

- Note 4. When high-speed on-chip oscillator and high-speed system clock are stopped. When AMPHS1 = 1 (Ultra-low power consumption oscillation). However, not including the current flowing into the real-time clock 2, 12-bit interval timer, and watchdog timer.

- **Note 5.** Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

| HS (high-speed main) mode: | $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}_{@}1 \text{ MHz}$ to 24 MHz |

|----------------------------|---------------------------------------------------------------------------------------|

|                            | 2.4 V ≤ VDD ≤ 3.6 V@1 MHz to 16 MHz                                                   |

| LS (low-speed main) mode:  | 1.8 V ≤ VDD ≤ 3.6 V@1 MHz to 8 MHz                                                    |

| LV (low-voltage main) mode | 1.6 V ≤ VDD ≤ 3.6 V@1 MHz to 4 MHz                                                    |

- **Remark 1.** fMX: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- **Remark 2.** fHOCO: High-speed on-chip oscillator clock frequency (48 MHz max.)

- Remark 3. fill: Main system clock source frequency when the high-speed on-chip oscillator clock divided 1, 2, 4, or 8, or the PLL clock divided by 2, 4, or 8 is selected (24 MHz max.)

- Remark 4. fSUB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

- Note 1. Total current flowing into VDD, including the input leakage current flowing when the level of the input pin is fixed to VDD or VSS. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the LCD controller/driver, A/D converter, D/A converter, comparator, LVD circuit, USB 2.0 function module, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- Note 2. During HALT instruction execution by flash memory.

- **Note 3.** When high-speed on-chip oscillator and subsystem clock are stopped.

- Note 4. When high-speed system clock and subsystem clock are stopped.

- **Note 5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the real-time clock 2 is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- Note 6. Not including the current flowing into the real-time clock 2, 12-bit interval timer, and watchdog timer.

- Note 7. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

- HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}_{@}1 \text{ MHz}$  to 24 MHz

- 2.4 V ≤ VDD ≤ 3.6 V@1 MHz to 16 MHz

- LS (low-speed main) mode:  $1.8 \text{ V} \le \text{VDD} \le 3.6 \text{ V} @1 \text{ MHz}$  to 8 MHz

- LV (low-voltage main) mode 1.6 V ≤ VDD ≤ 3.6 V@1 MHz to 4 MHz

- Note 8. Regarding the value for current to operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remark 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- **Remark 2.** fHOCO: High-speed on-chip oscillator clock frequency (48 MHz max.)

- **Remark 3.** file: Main system clock source frequency when the high-speed on-chip oscillator clock divided 1, 2, 4, or 8, or the PLL clock divided by 2, 4, or 8 is selected (24 MHz max.)

- **Remark 4.** fSUB: Subsystem clock frequency (XT1 clock oscillation frequency)

- Remark 5. Except subsystem clock operation, temperature condition of the TYP. value is TA = 25°C

AC Timing Test Points Vin/Von Vін/Vон Test points VIL/VOL VIL/VOL External System Clock Timing 1/fex 1/fexs **t**EXL tехн **t**EXLS **t**EXHS EXCLK/EXCLKS TI/TO Timing t⊤ı∟ ttiH-TI00 to TI07, TI10 to TI17 1/fто TO00 to TO07, TO10 to TO17, TKBO00, TKBO01, TKBO10, TKBO11, TKBO20, TKBO21 Interrupt Request Input Timing tintl tinth-INTP0 to INTP7

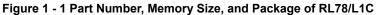

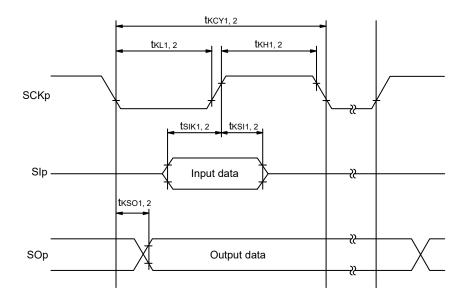

# CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

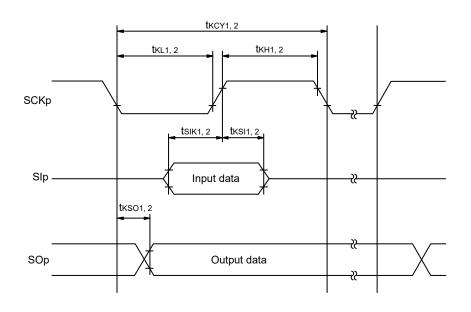

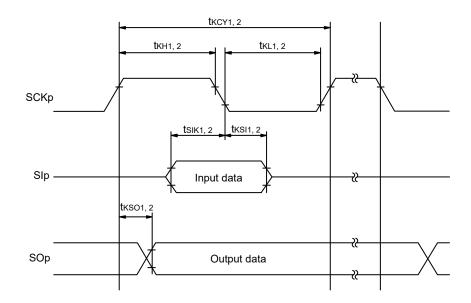

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

Remark 1. p: CSI number (p = 00, 10, 20, 30) Remark 2. m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13)

# (3) BC option standard

# (TA = -40 to +85°C, 4.35 V $\leq$ UVBUS $\leq$ 5.25 V, 2.4 V $\leq$ VDD $\leq$ 3.6 V, VSS = 0 V, HS (High-speed main) mode only)

| Parameter               |               | Symbol | Conditions | MIN.    | TYP.    | MAX. | Unit |        |        |        |

|-------------------------|---------------|--------|------------|---------|---------|------|------|--------|--------|--------|

| UDP/UDM input reference | VDSELi [3: 0] | 0000   | VDDET0     |         | 27      | 32   | 37   | %UVBUS |        |        |

| voltage                 | (i = 0, 1)    | 0001   | VDDET1     |         | 29      | 34   | 39   | %UVBUS |        |        |

| (UVBUS divider ratio)   |               | 0010   | VDDET2     |         | 32      | 37   | 42   | %UVBUS |        |        |

| (Function)              |               | 0011   | VDDET3     |         | 35      | 40   | 45   | %UVBUS |        |        |

|                         |               |        |            | 0100    | VDDET4  |      | 38   | 43     | 48     | %UVBUS |

|                         |               | 0101   | VDDET5     |         | 41      | 46   | 51   | %UVBUS |        |        |

|                         |               | 0110   | VDDET6     |         | 44      | 49   | 54   | %UVBUS |        |        |

|                         |               | 0111   | VDDET7     |         | 47      | 52   | 57   | %UVBUS |        |        |

|                         |               | 1000   | VDDET8     |         | 51      | 56   | 61   | %UVBUS |        |        |

|                         |               | 1001   | VDDET9     |         | 55      | 60   | 65   | %UVBUS |        |        |

|                         |               |        |            | 1010    | VDDET10 |      | 59   | 64     | 69     | %UVBUS |

|                         |               |        | 1011       | VDDET11 |         | 63   | 68   | 73     | %UVBUS |        |

|                         |               | 1100   | VDDET12    |         | 67      | 72   | 73   | %UVBUS |        |        |

|                         |               | 1101   | VDDET13    |         | 71      | 76   | 81   | %UVBUS |        |        |

|                         |               | 1110   | VDDET14    |         | 75      | 80   | 85   | %UVBUS |        |        |

|                         |               | 1111   | VDDET15    |         | 79      | 84   | 89   | %UVBUS |        |        |

# 2.6.4 Comparator

| Parameter                                     | Symbol                                            | Co                        | nditions                                  | MIN. | TYP.     | MAX.      | Unit |

|-----------------------------------------------|---------------------------------------------------|---------------------------|-------------------------------------------|------|----------|-----------|------|

| Input voltage range                           | lvref                                             |                           |                                           | 0    |          | Vdd - 1.4 | V    |

|                                               | lvcmp                                             |                           |                                           | -0.3 |          | VDD + 0.3 | V    |

| Output delay                                  | elay td VDD = 3.0 V<br>Input slew rate > 50 mV/µs |                           | High-speed comparator mode, standard mode |      |          | 1.2       | μs   |

|                                               |                                                   |                           | High-speed comparator mode, window mode   |      |          | 2.0       | μs   |

|                                               |                                                   |                           | Low-speed comparator mode, standard mode  |      | 3        | 5.0       | μs   |

| High-electric-potential judgment voltage      | VTW+                                              | High-speed comparator mod | de, window mode                           |      | 0.76 Vdd |           | V    |

| Low-electric-potential judgment voltage       | VTW-                                              | High-speed comparator mod | de, window mode                           |      | 0.24 Vdd |           | V    |

| Operation stabilization wait time             | tCMP                                              |                           |                                           | 100  |          |           | μs   |

| Internal reference<br>voltage <sup>Note</sup> | Vbgr                                              |                           |                                           | 1.38 | 1.45     | 1.50      | V    |

### $(TA = -40 \text{ to } +85^{\circ}C, 1.6 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

Note Not usable in LS (low-speed main) mode, LV (low-voltage main) mode, sub-clock operation, or STOP mode.

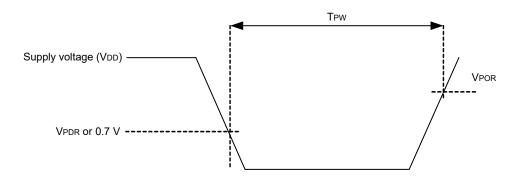

# 2.6.5 POR circuit characteristics

## (TA = -40 to +85°C, Vss = 0 V)

| Parameter           | Symbol | Conditions                             | MIN. | TYP. | MAX. | Unit |

|---------------------|--------|----------------------------------------|------|------|------|------|

| Detection voltage   | VPOR   | Power supply rise time                 | 1.47 | 1.51 | 1.55 | V    |

|                     | VPDR   | Power supply fall time <sup>Note</sup> | 1.46 | 1.50 | 1.54 | V    |

| Minimum pulse width | TPW    |                                        | 300  |      |      | μs   |

Note Minimum time required for a POR reset when VDD exceeds below VPDR. This is also the minimum time required for a POR reset from when VDD exceeds below 0.7 V to when VDD exceeds VPOR while STOP mode is entered or the main system clock is stopped through setting bit 0 (HIOSTOP) and bit 7 (MSTOP) in the clock operation status control register (CSC).

# (2) 1/4 bias method

### $(TA = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                           | Symbol  | Conc              | litions    | MIN.         | TYP.  | MAX.  | Unit |

|-------------------------------------|---------|-------------------|------------|--------------|-------|-------|------|

| LCD output voltage variation range  | VL1     | C1 to C4 Note 1   | VLCD = 04H | 0.90         | 1.00  | 1.08  | V    |

|                                     |         | = 0.47 µF Note 2  | VLCD = 05H | 0.95         | 1.05  | 1.13  | V    |

|                                     |         |                   | VLCD = 06H | 1.00         | 1.10  | 1.18  | V    |

|                                     |         |                   | VLCD = 07H | 1.05         | 1.15  | 1.23  | V    |

|                                     |         |                   | VLCD = 08H | 1.10         | 1.20  | 1.28  | V    |

|                                     |         |                   | VLCD = 09H | 1.15         | 1.25  | 1.33  | V    |

|                                     |         |                   | VLCD = 0AH | 1.20         | 1.30  | 1.38  | V    |

| Doubler output voltage              | VL2     | C1 to C4 Note 1 = | 0.47 μF    | 2 VL1 - 0.08 | 2 VL1 | 2 VL1 | V    |

| Tripler output voltage              | VL3     | C1 to C4 Note 1 = | = 0.47 μF  | 3 VL1 - 0.12 | 3 VL1 | 3 VL1 | V    |

| Quadruply output voltage            | VL4     | C1 to C5 Note 1 = | = 0.47 μF  | 4 VL1 - 0.16 | 4 VL1 | 4 VL1 | V    |

| Reference voltage setup time Note 2 | tvwait1 |                   |            | 5            |       |       | ms   |

| Voltage boost wait time Note 3      | tvwait2 | C1 to C5 Note 1 = | = 0.47μF   | 500          |       |       | ms   |

Note 1. This is a capacitor that is connected between voltage pins used to drive the LCD.

C1: A capacitor connected between CAPH and CAPL

C2: A capacitor connected between VL1 and GND

C3: A capacitor connected between VL2 and GND

C4: A capacitor connected between VL3 and GND

C5: A capacitor connected between VL4 and GND

C1 = C2 = C3 = C4 = 0.47 µF±30%

**Note 2.** This is the time required to wait from when the reference voltage is specified by using the VLCD register (or when the internal voltage boosting method is selected (by setting the MDSET1 and MDSET0 bits of the LCDM0 register to 01B) if the default value reference voltage is used) until voltage boosting starts (VLCON = 1).

Note 3. This is the wait time from when voltage boosting is started (VLCON = 1) until display is enabled (LCDON = 1).

# 2.8.3 Capacitor split method

## (1) 1/3 bias method

### (TA = -40 to +85°C, 2.2 V $\leq$ VDD $\leq$ 3.6 V, Vss = 0 V)

| Parameter                        | Symbol | Conditions                | MIN.          | TYP.    | MAX.          | Unit |

|----------------------------------|--------|---------------------------|---------------|---------|---------------|------|

| VL4 voltage                      | VL4    | C1 to C4 = 0.47 µF Note 2 |               | Vdd     |               | V    |

| VL2 voltage                      | VL2    | C1 to C4 = 0.47 µF Note 2 | 2/3 VL4 - 0.1 | 2/3 VL4 | 2/3 VL4 + 0.1 | V    |

| VL1 voltage                      | VL1    | C1 to C4 = 0.47 µF Note 2 | 1/3 Vl4 - 0.1 | 1/3 VL4 | 1/3 VL4 + 0.1 | V    |

| Capacitor split wait time Note 1 | t∨wait |                           | 100           |         |               | ms   |

Note 1. This is the wait time from when voltage bucking is started (VLCON = 1) until display is enabled (LCDON = 1).

Note 2. This is a capacitor that is connected between voltage pins used to drive the LCD.

C1: A capacitor connected between CAPH and CAPL

C2: A capacitor connected between VL1 and GND

C3: A capacitor connected between VL2 and GND

C4: A capacitor connected between VL4 and GND

$C1 = C2 = C3 = C4 = 0.47 \ \mu F \pm 30\%$

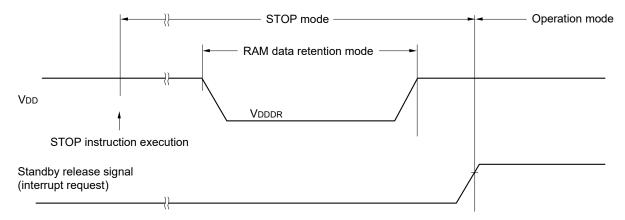

#### 2.9 **RAM Data Retention Characteristics**

| F                     | Parameter    | Symbol | Conditions | MIN.                 | TYP. | MAX. | Unit |  |  |

|-----------------------|--------------|--------|------------|----------------------|------|------|------|--|--|

| Data reter<br>voltage | ntion supply | Vdddr  |            | 1.46 <sup>Note</sup> |      | 3.6  | V    |  |  |

| Note                  | <b>°</b>     |        |            |                      |      |      |      |  |  |

(TA = -40 to +85°C, Vss = 0 V)

level that triggers a POR reset but not once it reaches the level at which a POR reset is generated.

#### **Flash Memory Programming Characteristics** 2.10

| Parameter                                      | Symbol       | Conditions                                         | MIN.    | TYP.      | MAX. | Unit  |

|------------------------------------------------|--------------|----------------------------------------------------|---------|-----------|------|-------|

| CPU/peripheral hardware clock frequency        | <b>f</b> CLK | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ | 1       |           | 24   | MHz   |

| Number of code flash rewrites<br>Notes 1, 2, 3 | Cerwr        | Retained for 20 years<br>TA = 85°C                 | 1,000   |           |      | Times |

| Number of data flash rewrites<br>Notes 1, 2, 3 |              | Retained for 1 year<br>TA = 25°C                   |         | 1,000,000 | 000  |       |

|                                                |              | Retained for 5 years<br>TA = 85°C                  | 100,000 |           |      |       |

|                                                |              | Retained for 20 years<br>TA = 85°C                 | 10,000  |           |      |       |

$(T_A = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{V}_{SS} = 0 \text{ V})$

Note 1. 1 erase + 1 write after the erase is regarded as 1 rewrite. The retaining years are until next rewrite after the rewrite.

When using flash memory programmer and Renesas Electronics self programming library Note 2.

Note 3. These are the characteristics of the flash memory and the results obtained from reliability testing by Renesas Electronics Corporation.

#### 2.11 **Dedicated Flash Memory Programmer Communication (UART)**

## $(TA = -40 \text{ to } +85^{\circ}C, 1.8 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter     | Symbol | Conditions                | MIN.    | TYP. | MAX.      | Unit |

|---------------|--------|---------------------------|---------|------|-----------|------|

| Transfer rate |        | During serial programming | 115,200 |      | 1,000,000 | bps  |

<R>

## (TA = -40 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = 0 V)

| Items                                    | Symbol | Conditions                                                                                                                                                                              |                                                              | MIN. | TYP. | MAX.           | Unit |

|------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|----------------|------|

| Output current,<br>low <sup>Note 1</sup> | IOL1   | Per pin for P00 to P07, P10 to P17, P20 to P27,<br>P30 to P37, P40 to P46, P50 to P57,<br>P70 to P77, P80 to P83,<br>P125 to P127, P130, P140 to P143                                   |                                                              |      |      | 8.5<br>Note 2  | mA   |

|                                          |        | Per pin for P60 and P61                                                                                                                                                                 |                                                              |      |      | 15.0<br>Note 2 | mA   |

|                                          |        | Total of P40 to P46, P130<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                                                                                       | 2.7 V ≤ VDD ≤ 3.6 V                                          |      |      | 15.0           | mA   |

|                                          |        |                                                                                                                                                                                         | 2.4 V ≤ VDD < 2.7 V                                          |      |      | 9.0            | mA   |

|                                          |        | Total of P00 to P07, P10 to P17, P20 to P27,<br>P30 to P37, P50 to P57, P60, P61,<br>P70 to P77, P80 to P83, P125 to P127,<br>P140 to P143<br>(When duty $\leq$ 70% <sup>Note 3</sup> ) | $2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ |      |      | 35.0           | mA   |

|                                          |        |                                                                                                                                                                                         | 2.4 V ≤ VDD < 2.7 V                                          |      |      | 20.0           | mA   |

|                                          |        | Total of all pins<br>(When duty ≤ 70% <sup>Note 3</sup> )                                                                                                                               |                                                              |      |      | 50.0           | mA   |

|                                          | IOL2   | Per pin for P150 to P156                                                                                                                                                                |                                                              |      |      | 0.4<br>Note 2  | mA   |

|                                          |        | Total of all pins                                                                                                                                                                       | $2.4 \text{ V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V}$ |      |      | 2.8            | mA   |

Note 1. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

**Note 2.** However, do not exceed the total current value.

<R>

**Note 3.** Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression

(when changing the duty factor from 70% to n%).

• Total output current of pins =  $(IOL \times 0.7)/(n \times 0.01)$

<Example> Where n = 80% and IOL = 10.0 mA

Total output current of pins = (10.0 × 0.7)/(80 × 0.01) ≈ 8.7 mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

Remark Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

| Items                          | Symbol | Conditions                                                                                                                                                    |           | MIN.                                               | TYP. | MAX. | Unit |    |

|--------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------|------|------|------|----|

| Input leakage<br>current, high | ILIH1  | P00 to P07, P10 to P17, P20 to P27,<br>P30 to P37, P40 to P46, P50 to P57,<br>P60, P61, P70 to P77, P80 to P83,<br>P125 to P127, P137,<br>P140 to P143, RESET | VI = VDD  |                                                    |      |      | 1    | μΑ |

|                                | ILIH2  | P20, P21, P140 to P143                                                                                                                                        | VI = VDD  |                                                    |      |      | 1    | μA |

|                                | Ілнз   | P121 to P124 (X1, X2, EXCLK, XT1, XT2, EXCLKS)                                                                                                                | VI = VDD  | In input port or external clock input              |      |      | 1    | μA |

|                                |        |                                                                                                                                                               |           | In resonator connection                            |      |      | 10   | μA |

|                                | ILIH4  | P150 to P156                                                                                                                                                  | VI = AVDI |                                                    |      | 1    | μA   |    |

| Input leakage<br>current, low  | ILIL1  | P00 to P07, P10 to P17, P20 to P27,<br>P30 to P37, P40 to P46, P50 to P57,<br>P60, P61, P70 to P77, P80 to P83,<br>P125 to P127, P137,<br>P140 to P143, RESET | VI = VSS  |                                                    |      |      | -1   | μA |

|                                | ILIL2  | P20, P21, P140 to P143                                                                                                                                        | VI = Vss  |                                                    |      | -1   | μA   |    |

|                                | Ilil3  | P121 to P124 (X1, X2, EXCLK, XT1, XT2, EXCLKS)                                                                                                                | VI = Vss  | In input port or external clock input              |      |      | -1   | μA |

|                                |        |                                                                                                                                                               |           | In resonator connection                            |      |      | -10  | μA |

|                                | ILIL4  | P150 to P156                                                                                                                                                  | VI = AVss |                                                    |      |      | -1   | μA |

| On-chip pull-up<br>resistance  | Ru1    | P00 to P07, P10 to P17, P20 to P27,<br>P30 to P37, P50 to P57, P70 to P77,<br>P140 to P143, P125 to P127                                                      | VI = VSS  | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ | 10   | 20   | 100  | kΩ |

|                                | RU2    | P40 to P46, P80 to P83                                                                                                                                        | VI = VSS  |                                                    | 10   | 20   | 100  | kΩ |

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

# 3.4 AC Characteristics

# 3.4.1 Basic operation

### $(TA = -40 \text{ to } +105^{\circ}C, 2.4 \text{ V} \le \text{AVDD} = \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V})$

Symbol Conditions MIN. TYP. MAX. Unit Items Тсү HS (high-speed main) 0.0417 Instruction cycle Main system  $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 1 μs (minimum instruction clock (fMAIN) mode  $2.4 \text{ V} \le \text{VDD} < 2.7 \text{ V}$ 0.0625 1 μs execution time) operation Subsystem clock (fSUB) operation  $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 28.5 30.5 31.3 μs In the self-HS (high-speed main)  $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 0.0417 1 μs programming mode 0.0625 2.4 V ≤ VDD < 2.7 V 1 μs mode External main system fEX 2.7 V ≤ VDD ≤ 3.6 V 1.0 20.0 MHz clock frequency 2.4 V ≤ Vpp < 2.7 V 1.0 16.0 MHz fext 32 35 kHz External main system texн,  $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ 24 ns clock input high-level tEXL 2.4 V ≤ VDD < 2.7 V 30 ns width, low-level width texns, 13.7 μs **t**EXLS TI00 to TI07 input 1/fмск + tтıн. ns high-level width, t⊤ı∟ 10 low-level width

Remark fMCK: Timer array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of timer mode register mn (TMRmn). m: Unit number (m = 0), n: Channel number (n = 0 to 7))

(1/2)

# (TA = -40 to +105°C, 2.4 V $\leq$ AVDD = VDD $\leq$ 3.6 V, Vss = 0 V)

(2/2)

| ,                                                             |                 | , ,                                                |                                                          |      |      | -    | ( )  |

|---------------------------------------------------------------|-----------------|----------------------------------------------------|----------------------------------------------------------|------|------|------|------|

| Items                                                         | Symbol          | Conditio                                           | ns                                                       | MIN. | TYP. | MAX. | Unit |

| TO00 to TO07, TKBO00,                                         | fто             | HS (high-speed main) mode                          | $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$       |      |      | 8    | MHz  |

| TKBO01, TKBO10, TKBO11,<br>TKBO20, TKBO21<br>output frequency |                 |                                                    | $2.4 \text{ V} \le \text{V}_{\text{DD}} < 2.7 \text{ V}$ |      |      | 8    | MHz  |

| PCLBUZ0, PCLBUZ1 output                                       | fPCL            | HS (high-speed main) mode                          | $2.7 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$       |      |      | 8    | MHz  |

| frequency                                                     |                 |                                                    | $2.4 \text{ V} \leq \text{VDD} < 2.7 \text{ V}$          |      |      | 8    | MHz  |

| Interrupt input high-level width,<br>low-level width          | tinth,<br>tintl | INTP0 to INTP7                                     | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$       | 1    |      |      | μs   |

| Key interrupt input low-level width                           | tkr             | $2.4 \text{ V} \leq \text{VDD} \leq 3.6 \text{ V}$ |                                                          | 250  |      |      | ns   |

| TMKB2 forced output stop input                                | tihr            | INTP0 to INTP7                                     | fclk > 16 MHz                                            | 125  |      |      | ns   |

| high-level width                                              |                 |                                                    | fclk ≤ 16 MHz                                            | 2    |      |      | fclk |

| RESET low-level width                                         | trsl            |                                                    | •                                                        | 10   |      |      | μs   |

# CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

**Remark 1.** p: CSI number (p = 00, 10, 20, 30) **Remark 2.** m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13)

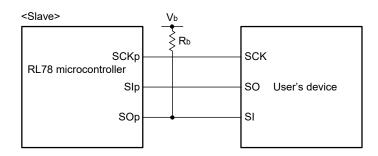

## CSI mode connection diagram (during communication at different potential)

**Remark 1.** Rb[Ω]: Communication line (SOp) pull-up resistance, Cb[F]: Communication line (SOp) load capacitance, Vb[V]: Communication line voltage

**Remark 2.** p: CSI number (p = 00, 10, 20, 30), m: Unit number (m = 0, 1), n: Channel number (n = 0 to 3), g: PIM and POM number (g = 0 to 3)

Remark 3. fMCK: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00, 02, 10, 12))

# (4) When reference voltage (+) = AVDD (ADREFP1 = 0, ADREFP0 = 0), reference voltage (-) = AVss (ADREFM = 0), conversion target: ANI16 to ANI21, internal reference voltage, temperature sensor output voltage

$(TA = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{VDD} \le 3.6 \text{ V}, 2.4 \text{ V} \le \text{AVDD} = \text{VDD} \le 3.6 \text{ V}, \text{Vss} = 0 \text{ V}, \text{AVss} = 0 \text{ V}, \text{Reference voltage (+)} = \text{AVDD}, \text{Reference voltage (-)} = \text{AVss} = 0)$

| Parameter                              | Symbol | Conditions                                                                                      |                                                             | MIN.          | TYP.      | MAX. | Unit |

|----------------------------------------|--------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|-----------|------|------|

| Resolution                             | Res    |                                                                                                 | $2.4 \text{ V} \le \text{AV}_{\text{DD}} \le 3.6 \text{ V}$ | 8             |           | 12   | bit  |

| Overall error Note 1                   | AINL   | 12-bit resolution                                                                               | $2.4 \text{ V} \leq \text{AVDD} \leq 3.6 \text{ V}$         |               |           | ±8.5 | LSB  |

| Conversion time                        | tCONV  | ADTYP = 0,<br>12-bit resolution                                                                 | 2.4 V ≤ AVDD ≤ 3.6 V                                        | 4.125         |           |      | μs   |

| Zero-scale error Note 1                | Ezs    | 12-bit resolution                                                                               | $2.4 \text{ V} \le \text{AV}\text{DD} \le 3.6 \text{ V}$    |               |           | ±8.0 | LSB  |

| Full-scale error Note 1                | Efs    | 12-bit resolution                                                                               | $2.4 \text{ V} \leq \text{AVDD} \leq 3.6 \text{ V}$         |               |           | ±8.0 | LSB  |

| Integral linearity error Note 1        | ILE    | 12-bit resolution                                                                               | $2.4 \text{ V} \le \text{AV}\text{DD} \le 3.6 \text{ V}$    |               |           | ±3.5 | LSB  |

| Differential linearity error<br>Note 1 | DLE    | 12-bit resolution                                                                               | 2.4 V ≤ AVDD ≤ 3.6 V                                        |               |           | ±2.5 | LSB  |

| Analog input voltage                   | VAIN   |                                                                                                 | l                                                           | 0             |           | AVdd | V    |

|                                        |        | Internal reference voltage (2.4 V $\leq$ VDD $\leq$ 3.6 V, HS                                   | e<br>(high-speed main) mode)                                | ١             | /BGR Note | 2    |      |

|                                        |        | Temperature sensor output voltage<br>(2.4 V $\leq$ VDD $\leq$ 3.6 V, HS (high-speed main) mode) |                                                             | VTMP25 Note 2 |           |      |      |

**Note 1.** Excludes quantization error (±1/2 LSB).

Note 2. Refer to 3.6.2 Temperature sensor, internal reference voltage output characteristics.

Caution Always use AVDD pin with the same potential as the VDD pin.

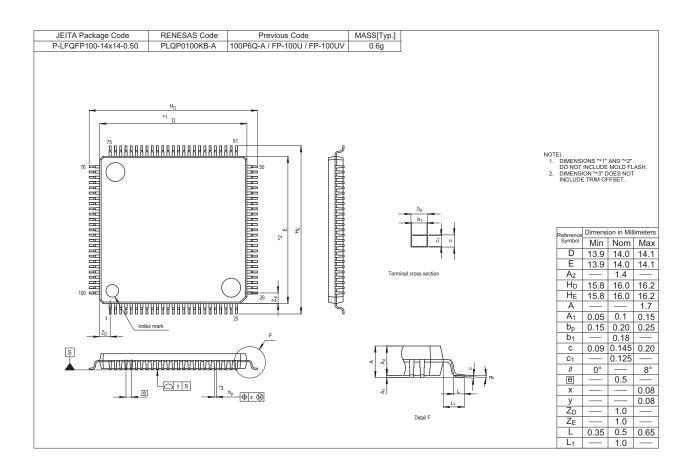

# 4.3 100-pin products

R5F110PEAFB, R5F110PFAFB, R5F110PGAFB, R5F110PHAFB, R5F110PJAFB R5F111PEAFB, R5F111PFAFB, R5F111PGAFB, R5F111PHAFB, R5F111PJAFB R5F110PEGFB, R5F110PFGFB, R5F110PGGFB, R5F110PHGFB, R5F110PJGFB R5F111PEGFB, R5F111PFGFB, R5F111PGGFB, R5F111PHGFB, R5F111PJGFB

**REVISION HISTORY**

# RL78/L1C Datasheet

| Day               | Dete         |                                                                    | Description                                                                                                                              |  |  |

|-------------------|--------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Rev.              | Date         | Page                                                               | Summary                                                                                                                                  |  |  |

| 0.01              | Oct 15, 2012 | _                                                                  | First Edition issued                                                                                                                     |  |  |

| 1.00 Nov 18, 2013 |              | 1, 2                                                               | Modification of 1.1 Features                                                                                                             |  |  |

|                   |              | 3, 4                                                               | Modification of 1.2 Ordering Information                                                                                                 |  |  |

|                   |              | 5 to 8                                                             | Modification of package type in 1.3 Pin Configuration (Top View)                                                                         |  |  |

|                   |              | 14 to 17                                                           | Modification of vectored interrupt sources in 1.6 Outline of Functions                                                                   |  |  |

|                   |              | 14 to 17                                                           | Modification of operating ambient temperature in 1.6 Outline of Functions                                                                |  |  |

|                   |              | 19 to 21                                                           | Modification of description in tables in 2.1 Absolute Maximum Ratings                                                                    |  |  |

|                   |              | 22, 23                                                             | Modification of description in 2.2 Oscillator Characteristics                                                                            |  |  |

|                   |              | 25 Modification of low-level output current in 2.3.1 Pin character |                                                                                                                                          |  |  |

|                   |              | 26                                                                 | Modification of error of high-level input voltage conditions in 2.3.1 Pin characteristics                                                |  |  |

|                   |              | 26                                                                 | Modification of error of low-level input voltage conditions in 2.3.1 Pin characteristics                                                 |  |  |

|                   |              | 27                                                                 | Modification of low-level output voltage in 2.3.1 Pin characteristics                                                                    |  |  |

|                   |              | 28                                                                 | Modification of error of internal pull-up resistor conditions in 2.3.1 Pin characteristics                                               |  |  |

|                   |              | 29 to 34                                                           | Modification of 2.3.2 Supply current characteristics                                                                                     |  |  |

|                   |              | 35, 36                                                             | Modification of 2.4 AC Characteristics                                                                                                   |  |  |

|                   |              | 37, 38                                                             | Addition of minimum instruction execution time during main system clock operation                                                        |  |  |

|                   |              | 41 to 63                                                           | Addition of LS mode and LV mode characteristics in 2.5.1 Serial array unit                                                               |  |  |

|                   |              | 64 to 66                                                           | Addition of LS mode and LV mode characteristics in 2.5.2 Serial interface IICA                                                           |  |  |

|                   |              | 67, 68                                                             | Modification of conditions in 2.5.3 USB                                                                                                  |  |  |

|                   |              | 69                                                                 | Addition of (3) BC option standard in 2.5.3 USB                                                                                          |  |  |

|                   |              | 70 to 75                                                           | Addition of characteristics about conversion of internal reference voltage and temperature sensor in 2.6.1 A/D converter characteristics |  |  |

|                   |              | 76                                                                 | Addition of characteristic in 2.6.4 Comparator                                                                                           |  |  |

|                   |              | 76                                                                 | Deletion of detection delay in 2.6.5 POR circuit characteristics                                                                         |  |  |

|                   |              | 78                                                                 | Modification of 2.7 Power supply voltage rising slope characteristics                                                                    |  |  |

|                   |              | 79 to 82                                                           | Modification of 2.8 LCD Characteristics                                                                                                  |  |  |

|                   |              | 83                                                                 | Modification of 2.9 Data Memory STOP Mode Low Supply Voltage Data<br>Retention Characteristics                                           |  |  |

|                   |              | 83                                                                 | Modification of 2.10 Flash Memory Programming Characteristics                                                                            |  |  |

|                   |              | 84                                                                 | Addition of 2.12 Timing Specs for Switching Modes                                                                                        |  |  |

|                   |              | 85 to 144                                                          | Addition of 3. ELECTRICAL SPECIFICATIONS (G: TA = -40 to +105°C)                                                                         |  |  |

| 2.00              | Feb 21, 2014 | All                                                                | Addition of 85-pin product information                                                                                                   |  |  |

|                   |              | All                                                                | Modification from 80-pin to 80/85-pin                                                                                                    |  |  |

|                   |              | All                                                                | Modification from x = M, P to x = M, N, P                                                                                                |  |  |

|                   |              | All                                                                | Modification from high-accuracy real-time clock to real-time clock 2                                                                     |  |  |

|                   |              | All                                                                | Modification from RTC to RTC2                                                                                                            |  |  |

|                   |              | 1                                                                  | Modification of 1.1 Features                                                                                                             |  |  |

|                   |              | 3                                                                  | Modification of 1.2 Ordering Information                                                                                                 |  |  |