Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M4                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 50MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                               |

| Peripherals                | DMA, I²S, LVD, POR, PWM, WDT                                          |

| Number of I/O              | 60                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 4K x 8                                                                |

| RAM Size                   | 32K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |

| Data Converters            | A/D 24x16b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 80-LQFP                                                               |

| Supplier Device Package    | 80-FQFP (12x12)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk12dx256vlk5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1 Ordering parts

#### 1.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to freescale.com and perform a part number search for the following device numbers: PK12 and MK12.

#### 2 Part identification

#### 2.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

#### 2.2 Format

Part numbers for this device have the following format:

Q K## A M FFF R T PP CC N

#### 2.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description          | Values                                                                                     |

|-------|----------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| K##   | Kinetis family       | • K12                                                                                      |

| А     | Key attribute        | <ul> <li>D = Cortex-M4 w/ DSP</li> <li>F = Cortex-M4 w/ DSP and FPU</li> </ul>             |

| М     | Flash memory type    | <ul> <li>N = Program flash only</li> <li>X = Program flash and FlexMemory</li> </ul>       |

#### rarı identification

| Field | Description                 | Values                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FFF   | Program flash memory size   | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> <li>256 = 256 KB</li> <li>512 = 512 KB</li> <li>1M0 = 1 MB</li> <li>2M0 = 2 MB</li> </ul>                                                                                                                                                                                                                                         |

| R     | Silicon revision            | <ul> <li>Z = Initial</li> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                                                                                                                                                                                                                                                                             |

| Т     | Temperature range (°C)      | <ul> <li>V = -40 to 105</li> <li>C = -40 to 85</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LF = 48 LQFP (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> <li>MP = 64 MAPBGA (5 mm x 5 mm)</li> <li>LK = 80 LQFP (12 mm x 12 mm)</li> <li>LL = 100 LQFP (14 mm x 14 mm)</li> <li>MC = 121 MAPBGA (8 mm x 8 mm)</li> <li>LQ = 144 LQFP (20 mm x 20 mm)</li> <li>MD = 144 MAPBGA (13 mm x 13 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | <ul> <li>5 = 50 MHz</li> <li>7 = 72 MHz</li> <li>10 = 100 MHz</li> <li>12 = 120 MHz</li> <li>15 = 150 MHz</li> <li>18 = 180 MHz</li> </ul>                                                                                                                                                                                                                                                           |

| N     | Packaging type              | <ul><li>R = Tape and reel</li><li>(Blank) = Trays</li></ul>                                                                                                                                                                                                                                                                                                                                          |

## 2.4 Example

This is an example part number:

MK12DX128VLK5

### 2.5 Small package marking

In an effort to save space, small package devices use special marking on the chip. These markings have the following format:

Q##CFTPP

This table lists the possible values for each field in the part number for small packages (not all combinations are valid):

| Field | Description                | Values                                                                                     |

|-------|----------------------------|--------------------------------------------------------------------------------------------|

| Q     | Qualification status       | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul> |

| С     | Speed                      | • G = 50 MHz                                                                               |

| F     | Flash memory configuration | <ul> <li>G = 128 KB + Flex</li> <li>H = 256 KB + Flex</li> <li>9 = 512 KB</li> </ul>       |

| Т     | Temperature range (°C)     | • V = -40 to 105                                                                           |

| PP    | Package identifier         | • MC = 121 MAPBGA                                                                          |

This tables lists some examples of small package marking along with the original part numbers:

| Original part number | Alternate part number |

|----------------------|-----------------------|

| MK12DX256VLF5        | M12GHVLF              |

| MK12DN512VLH5        | M12G9VLH              |

## 3 Terminology and guidelines

### 3.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

#### **3.1.1 Example**

This is an example of an operating requirement:

| Symbol   | Description               | Min. | Max. | Unit |

|----------|---------------------------|------|------|------|

| $V_{DD}$ | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

#### Genera

Table 1. Voltage and current operating requirements (continued)

| Symbol              | Description                                                                                                                                                                                                              | Min.                  | Max.    | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|---------|------|-------|

| I <sub>ICcont</sub> | Contiguous pin DC injection current —regional limit, includes sum of negative injection currents or sum of positive injection currents of 16 contiguous pins  • Negative current injection  • Positive current injection | -25<br>—              | <br>+25 | mA   |       |

| V <sub>RAM</sub>    | V <sub>DD</sub> voltage required to retain RAM                                                                                                                                                                           | 1.2                   | _       | V    |       |

| V <sub>RFVBAT</sub> | V <sub>BAT</sub> voltage required to retain the VBAT register file                                                                                                                                                       | V <sub>POR_VBAT</sub> | _       | V    |       |

<sup>1.</sup> All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is less than V<sub>AIO\_MIN</sub> or greater than V<sub>AIO\_MAX</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICAIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>IN</sub>-V<sub>AIO\_MAX</sub>)/II<sub>ICAIO</sub>I. Select the larger of these two calculated resistances if the pin is exposed to positive and negative injection currents.

#### 5.2.2 LVD and POR operating requirements

Table 2. V<sub>DD</sub> supply LVD and POR operating requirements

| Symbol            | Description                                                 | Min. | Тур. | Max. | Unit | Notes |

|-------------------|-------------------------------------------------------------|------|------|------|------|-------|

| V <sub>POR</sub>  | Falling VDD POR detect voltage                              | 0.8  | 1.1  | 1.5  | V    |       |

| $V_{LVDH}$        | Falling low-voltage detect threshold — high range (LVDV=01) | 2.48 | 2.56 | 2.64 | V    |       |

|                   | Low-voltage warning thresholds — high range                 |      |      |      |      | 1     |

| $V_{LVW1H}$       | Level 1 falling (LVWV=00)                                   | 2.62 | 2.70 | 2.78 | V    |       |

| $V_{LVW2H}$       | Level 2 falling (LVWV=01)                                   | 2.72 | 2.80 | 2.88 | V    |       |

| $V_{LVW3H}$       | Level 3 falling (LVWV=10)                                   | 2.82 | 2.90 | 2.98 | V    |       |

| $V_{LVW4H}$       | Level 4 falling (LVWV=11)                                   | 2.92 | 3.00 | 3.08 | V    |       |

| V <sub>HYSH</sub> | Low-voltage inhibit reset/recover hysteresis — high range   | _    | 80   | _    | mV   |       |

| $V_{LVDL}$        | Falling low-voltage detect threshold — low range (LVDV=00)  | 1.54 | 1.60 | 1.66 | V    |       |

|                   | Low-voltage warning thresholds — low range                  |      |      |      |      | 1     |

| $V_{LVW1L}$       | Level 1 falling (LVWV=00)                                   | 1.74 | 1.80 | 1.86 | V    |       |

| $V_{LVW2L}$       | Level 2 falling (LVWV=01)                                   | 1.84 | 1.90 | 1.96 | V    |       |

| $V_{LVW3L}$       | Level 3 falling (LVWV=10)                                   | 1.94 | 2.00 | 2.06 | V    |       |

| $V_{LVW4L}$       | Level 4 falling (LVWV=11)                                   | 2.04 | 2.10 | 2.16 | V    |       |

| $V_{HYSL}$        | Low-voltage inhibit reset/recover hysteresis — low range    | _    | 60   | _    | mV   |       |

| $V_{BG}$          | Bandgap voltage reference                                   | 0.97 | 1.00 | 1.03 | V    |       |

| t <sub>LPO</sub>  | Internal low power oscillator period — factory trimmed      | 900  | 1000 | 1100 | μs   |       |

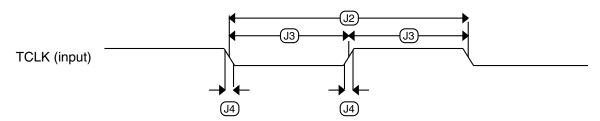

### Table 13. JTAG full voltage range electricals

| Symbol | Description                                        | Min.         | Max. | Unit |

|--------|----------------------------------------------------|--------------|------|------|

|        | Operating voltage                                  | 1.71         | 3.6  | V    |

| J1     | TCLK frequency of operation                        |              |      | MHz  |

|        | Boundary Scan                                      | 0            | 10   |      |

|        | JTAG and CJTAG                                     | 0            | 20   |      |

|        | Serial Wire Debug                                  | 0            | 40   |      |

| J2     | TCLK cycle period                                  | 1/J1         | _    | ns   |

| J3     | TCLK clock pulse width                             |              |      |      |

|        | Boundary Scan                                      | 50           | _    | ns   |

|        | JTAG and CJTAG                                     | 25           | _    | ns   |

|        | Serial Wire Debug                                  | 12.5         | _    | ns   |

| J4     | TCLK rise and fall times                           | _            | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20           | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 0            | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _            | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | _            | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8            | _    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1.4          | _    | ns   |

| J11    | TCLK low to TDO data valid                         | <del>-</del> | 22.1 | ns   |

| J12    | TCLK low to TDO high-Z                             | <del>-</del> | 22.1 | ns   |

| J13    | TRST assert time                                   | 100          | _    | ns   |

| J14    | TRST setup time (negation) to TCLK high            | 8            | _    | ns   |

Figure 4. Test clock input timing

#### Table 14. MCG specifications (continued)

| Symbol                | Description                  | Min. | Тур. | Max.                                | Unit | Notes |

|-----------------------|------------------------------|------|------|-------------------------------------|------|-------|

| t <sub>pll_lock</sub> | Lock detector detection time | _    | _    | 150 × 10 <sup>-6</sup><br>+ 1075(1/ | s    | 10    |

|                       |                              |      |      | f <sub>pll_ref</sub> )              |      |       |

- This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. 2 V <= VDD <= 3.6 V.

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=0.

- The resulting system clock frequencies should not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco t</sub>) over voltage and temperature should be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32=1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 7. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 8. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 9. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- 10. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

#### 6.3.2 Oscillator electrical specifications

## 6.3.2.1 Oscillator DC electrical specifications Table 15. Oscillator DC electrical specifications

| Symbol             | Description                             | Min. | Тур. | Max. | Unit | Notes |

|--------------------|-----------------------------------------|------|------|------|------|-------|

| $V_{DD}$           | Supply voltage                          | 1.71 | _    | 3.6  | V    |       |

| I <sub>DDOSC</sub> | Supply current — low-power mode (HGO=0) |      |      |      |      | 1     |

|                    | • 32 kHz                                | _    | 500  | _    | nA   |       |

|                    | • 4 MHz                                 | _    | 200  | _    | μΑ   |       |

|                    | • 8 MHz (RANGE=01)                      | _    | 300  | _    | μΑ   |       |

|                    | • 16 MHz                                | _    | 950  | _    | μΑ   |       |

|                    | • 24 MHz                                | _    | 1.2  | _    | mA   |       |

|                    | • 32 MHz                                | _    | 1.5  | _    | mA   |       |

|                    |                                         |      |      |      |      |       |

#### Table 15. Oscillator DC electrical specifications (continued)

| Symbol                       | Description                                                                                      | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

| I <sub>DDOSC</sub>           | Supply current — high-gain mode (HGO=1)                                                          |      |                 |      |      | 1     |

|                              | • 32 kHz                                                                                         | _    | 25              | _    | μΑ   |       |

|                              | • 4 MHz                                                                                          | _    | 400             | _    | μΑ   |       |

|                              | • 8 MHz (RANGE=01)                                                                               | _    | 500             | _    | μΑ   |       |

|                              | • 16 MHz                                                                                         | _    | 2.5             | _    | mA   |       |

|                              | • 24 MHz                                                                                         | _    | 3               | _    | mA   |       |

|                              | • 32 MHz                                                                                         | _    | 4               | _    | mA   |       |

| C <sub>x</sub>               | EXTAL load capacitance                                                                           | _    | _               | _    |      | 2, 3  |

| C <sub>y</sub>               | XTAL load capacitance                                                                            | _    | _               | _    |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                        | _    | _               | _    | ΜΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                        | _    | 10              | _    | ΜΩ   |       |

|                              | Feedback resistor — high-frequency, low-power mode (HGO=0)                                       | _    | _               | _    | ΜΩ   |       |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                       | _    | 1               | _    | ΜΩ   |       |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power mode (HGO=0)                                          | _    | _               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain mode (HGO=1)                                          | _    | 200             | _    | kΩ   |       |

|                              | Series resistor — high-frequency, low-power mode (HGO=0)                                         | _    | _               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain mode (HGO=1)                                         |      |                 |      |      |       |

|                              |                                                                                                  | _    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator mode) — low-frequency, low-power mode (HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator mode) — low-frequency, high-gain mode (HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator mode) — high-frequency, low-power mode (HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator mode) — high-frequency, high-gain mode (HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

- 1.  $V_{DD}$ =3.3 V, Temperature =25 °C

- 2. See crystal or resonator manufacturer's recommendation

- 3.  $C_x$  and  $C_y$  can be provided by using either integrated capacitors or external components.

- 4. When low-power mode is selected, R<sub>F</sub> is integrated and must not be attached externally.

- 5. The EXTAL and XTAL pins should only be connected to required oscillator components and must not be connected to any other device.

## 6.3.2.2 Oscillator frequency specifications Table 16. Oscillator frequency specifications

| Symbol                | Description                                                                                     | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-frequency mode (MCG_C2[RANGE]=00)               | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high-frequency mode (low range) (MCG_C2[RANGE]=01)  | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high frequency mode (high range) (MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                     | _    | _    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                    | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency, low-power mode (HGO=0)                             | _    | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency, high-gain mode (HGO=1)                             | _    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency (MCG_C2[RANGE]=01), low-power mode (HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency (MCG_C2[RANGE]=01), high-gain mode (HGO=1)          | _    | 1    | _    | ms   |       |

- 1. Other frequency limits may apply when external clock is being used as a reference for FLL or PLL.

- 2. When transitioning from FBE to FEI mode, restrict the frequency of the input clock so that—it remains within the limits of DCO input clock frequency when divided by FRDIV.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

- Crystal startup time is defined as the time between oscillator being enabled and OSCINIT bit in the MCG\_S register being set.

#### NOTE

The 32 kHz oscillator works in low power mode by default and cannot be moved into high power/gain mode.

#### 6.3.3 32 kHz oscillator electrical characteristics

## 6.3.3.1 32 kHz oscillator DC electrical specifications Table 17. 32kHz oscillator DC electrical specifications

| Symbol            | Description                                   | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------|------|------|------|------|

| $V_{BAT}$         | Supply voltage                                | 1.71 | _    | 3.6  | V    |

| R <sub>F</sub>    | Internal feedback resistor                    | _    | 100  | _    | ΜΩ   |

| C <sub>para</sub> | Parasitical capacitance of EXTAL32 and XTAL32 | _    | 5    | 7    | pF   |

Table 17. 32kHz oscillator DC electrical specifications (continued)

| Symbol                       | Description                           | Min. | Тур. | Max. | Unit |

|------------------------------|---------------------------------------|------|------|------|------|

| V <sub>pp</sub> <sup>1</sup> | Peak-to-peak amplitude of oscillation | _    | 0.6  | _    | V    |

<sup>1.</sup> When a crystal is being used with the 32 kHz oscillator, the EXTAL32 and XTAL32 pins should only be connected to required oscillator components and must not be connected to any other devices.

## 6.3.3.2 32 kHz oscillator frequency specifications Table 18. 32 kHz oscillator frequency specifications

| Symbol                  | Description                               | Min. | Тур.   | Max.      | Unit | Notes |

|-------------------------|-------------------------------------------|------|--------|-----------|------|-------|

| f <sub>osc_lo</sub>     | Oscillator crystal                        | _    | 32.768 | _         | kHz  |       |

| t <sub>start</sub>      | Crystal start-up time                     | _    | 1000   | _         | ms   | 1     |

| V <sub>ec_extal32</sub> | Externally provided input clock amplitude | 700  | _      | $V_{BAT}$ | mV   | 2, 3  |

- 1. Proper PC board layout procedures must be followed to achieve specifications.

- 2. This specification is for an externally supplied clock driven to EXTAL32 and does not apply to any other clock input. The oscillator remains enabled and XTAL32 must be left unconnected.

- 3. The parameter specified is a peak-to-peak value and  $V_{IH}$  and  $V_{IL}$  specifications do not apply. The voltage of the applied clock must be within the range of  $V_{SS}$  to  $V_{BAT}$ .

#### 6.4 Memories and memory interfaces

#### 6.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

#### 6.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

Table 19. NVM program/erase timing specifications

| Symbol                    | Description                              | Min. | Тур. | Max. | Unit | Notes |

|---------------------------|------------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub>       | Longword Program high-voltage time       | _    | 7.5  | 18   | μs   |       |

| t <sub>hversscr</sub>     | Sector Erase high-voltage time           | _    | 13   | 113  | ms   | 1     |

| t <sub>hversblk256k</sub> | Erase Block high-voltage time for 256 KB | 1    | 104  | 904  | ms   | 1     |

1. Maximum time based on expectations at cycling end-of-life.

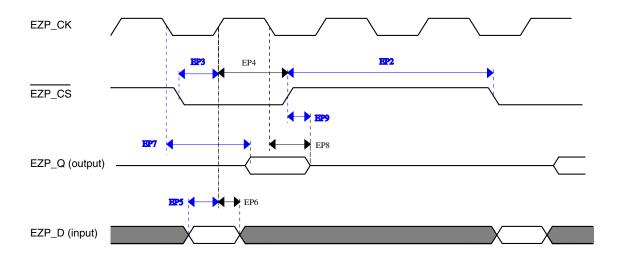

Figure 8. EzPort Timing Diagram

### 6.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

#### 6.6 Analog

#### 6.6.1 ADC electrical specifications

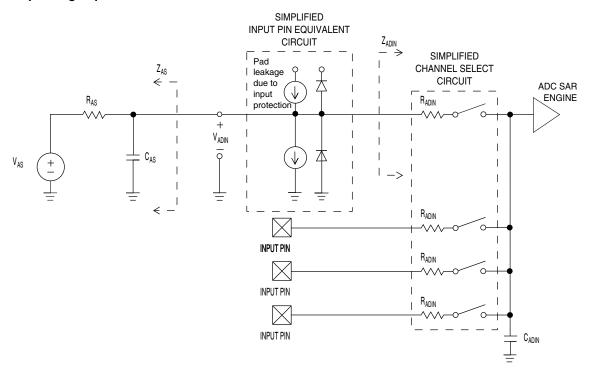

The 16-bit accuracy specifications listed in Table 24 and Table 25 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

## 6.6.1.1 16-bit ADC operating conditions Table 24. 16-bit ADC operating conditions

| Symbol           | Description    | Conditions                                                     | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |

|------------------|----------------|----------------------------------------------------------------|------|-------------------|------|------|-------|

| $V_{DDA}$        | Supply voltage | Absolute                                                       | 1.71 | _                 | 3.6  | V    |       |

| $\Delta V_{DDA}$ | Supply voltage | Delta to V <sub>DD</sub> (V <sub>DD</sub> – V <sub>DDA</sub> ) | -100 | 0                 | +100 | mV   | 2     |

| $\Delta V_{SSA}$ | Ground voltage | Delta to V <sub>SS</sub> (V <sub>SS</sub> – V <sub>SSA</sub> ) | -100 | 0                 | +100 | mV   | 2     |

Figure 9. ADC input impedance equivalency diagram

#### 6.6.1.2 16-bit ADC electrical characteristics Table 25. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ , $V_{REFL} = V_{SSA}$ )

| Symbol               | Description               | Conditions <sup>1</sup> .    | Min.         | Typ. <sup>2</sup> | Max.         | Unit             | Notes                   |

|----------------------|---------------------------|------------------------------|--------------|-------------------|--------------|------------------|-------------------------|

| I <sub>DDA_ADC</sub> | Supply current            |                              | 0.215        | _                 | 1.7          | mA               | 3                       |

|                      | ADC                       | • ADLPC = 1, ADHSC = 0       | 1.2          | 2.4               | 3.9          | MHz              | t <sub>ADACK</sub> = 1/ |

| f <sub>ADACK</sub>   | asynchronous clock source | • ADLPC = 1, ADHSC = 1       | 2.4          | 4.0               | 6.1          | MHz              | f <sub>ADACK</sub>      |

|                      |                           | • ADLPC = 0, ADHSC = 0       | 3.0          | 5.2               | 7.3          | MHz              |                         |

|                      |                           | • ADLPC = 0, ADHSC = 1       | 4.4          | 6.2               | 9.5          | MHz              |                         |

|                      | Sample Time               | See Reference Manual chapter | for sample t | imes              |              |                  |                         |

| TUE                  | Total unadjusted          | 12-bit modes                 | _            | ±4                | ±6.8         | LSB <sup>4</sup> | 5                       |

|                      | error                     | • <12-bit modes              | _            | ±1.4              | ±2.1         |                  |                         |

| DNL                  | Differential non-         | 12-bit modes                 | _            | ±0.7              | -1.1 to +1.9 | LSB <sup>4</sup> | 5                       |

|                      | linearity                 |                              |              |                   | -0.3 to 0.5  |                  |                         |

|                      |                           | • <12-bit modes              | _            | ±0.2              |              |                  |                         |

| INL                  | Integral non-             | 12-bit modes                 | _            | ±1.0              | -2.7 to +1.9 | LSB <sup>4</sup> | 5                       |

|                      | linearity                 |                              |              |                   | -0.7 to +0.5 |                  |                         |

|                      |                           | • <12-bit modes              | _            | ±0.5              |              |                  |                         |

| E <sub>FS</sub>      | Full-scale error          | 12-bit modes                 | _            | -4                | -5.4         | LSB <sup>4</sup> | V <sub>ADIN</sub> =     |

|                      |                           | • <12-bit modes              | _            | -1.4              | -1.8         |                  | $V_{DDA}$               |

|                      |                           |                              |              |                   |              |                  | 5                       |

## 6.6.3.2 12-bit DAC operating behaviors Table 28. 12-bit DAC operating behaviors

| Symbol                | Description                                                                       | Min.                      | Тур.     | Max.       | Unit   | Notes |

|-----------------------|-----------------------------------------------------------------------------------|---------------------------|----------|------------|--------|-------|

| I <sub>DDA_DACL</sub> | Supply current — low-power mode                                                   | _                         | _        | 330        | μΑ     |       |

| I <sub>DDA_DACH</sub> | Supply current — high-speed mode                                                  | _                         | _        | 1200       | μΑ     |       |

| t <sub>DACLP</sub>    | Full-scale settling time (0x080 to 0xF7F) — low-power mode                        | _                         | 100      | 200        | μs     | 1     |

| t <sub>DACHP</sub>    | Full-scale settling time (0x080 to 0xF7F) — high-power mode                       | _                         | 15       | 30         | μs     | 1     |

| t <sub>CCDACLP</sub>  | Code-to-code settling time (0xBF8 to 0xC08)  — low-power mode and high-speed mode | _                         | 0.7      | 1          | μs     | 1     |

| V <sub>dacoutl</sub>  | DAC output voltage range low — high-speed mode, no load, DAC set to 0x000         | _                         | _        | 100        | mV     |       |

| V <sub>dacouth</sub>  | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF    | V <sub>DACR</sub><br>-100 | _        | $V_{DACR}$ | mV     |       |

| INL                   | Integral non-linearity error — high speed mode                                    | _                         | _        | ±8         | LSB    | 2     |

| DNL                   | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                     | _                         | _        | ±1         | LSB    | 3     |

| DNL                   | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                   | _                         | _        | ±1         | LSB    | 4     |

| V <sub>OFFSET</sub>   | Offset error                                                                      | _                         | ±0.4     | ±0.8       | %FSR   | 5     |

| E <sub>G</sub>        | Gain error                                                                        | _                         | ±0.1     | ±0.6       | %FSR   | 5     |

| PSRR                  | Power supply rejection ratio, V <sub>DDA</sub> ≥ 2.4 V                            | 60                        | _        | 90         | dB     |       |

| T <sub>CO</sub>       | Temperature coefficient offset voltage                                            | _                         | 3.7      | _          | μV/C   | 6     |

| T <sub>GE</sub>       | Temperature coefficient gain error                                                | _                         | 0.000421 | _          | %FSR/C |       |

| Rop                   | Output resistance (load = $3 \text{ k}\Omega$ )                                   | _                         | _        | 250        | Ω      |       |

| SR                    | Slew rate -80h→ F7Fh→ 80h                                                         |                           |          |            | V/µs   |       |

|                       | High power (SP <sub>HP</sub> )                                                    | 1.2                       | 1.7      | _          |        |       |

|                       | Low power (SP <sub>LP</sub> )                                                     | 0.05                      | 0.12     | _          |        |       |

| СТ                    | Channel to channel cross talk                                                     | _                         | _        | -80        | dB     |       |

| BW                    | 3dB bandwidth                                                                     |                           |          |            | kHz    |       |

|                       | High power (SP <sub>HP</sub> )                                                    | 550                       | _        | _          |        |       |

|                       | Low power (SP <sub>LP</sub> )                                                     | 40                        | _        | _          |        |       |

- 1. Settling within ±1 LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V

- 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  100 mV

- 6. V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

#### Table 30. VREF full-range operating behaviors

| Symbol              | Description                                                                                | Min.   | Тур.  | Max.   | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------|--------|-------|--------|------|-------|

| V <sub>out</sub>    | Voltage reference output with factory trim at nominal V <sub>DDA</sub> and temperature=25C | 1.1915 | 1.195 | 1.1977 | V    | 1     |

| V <sub>out</sub>    | Voltage reference output — factory trim                                                    | 1.1584 | _     | 1.2376 | V    | 1     |

| V <sub>out</sub>    | Voltage reference output — user trim                                                       | 1.193  | _     | 1.197  | V    | 1     |

| V <sub>step</sub>   | Voltage reference trim step                                                                | _      | 0.5   | _      | mV   | 1     |

| V <sub>tdrift</sub> | Temperature drift (Vmax -Vmin across the full temperature range)                           | _      | _     | 80     | mV   | 1     |

| I <sub>bg</sub>     | Bandgap only current                                                                       | _      | _     | 80     | μA   | 1     |

| $\Delta V_{LOAD}$   | Load regulation                                                                            |        |       |        | μV   | 1, 2  |

|                     | • current = ± 1.0 mA                                                                       | _      | 200   | _      |      |       |

| T <sub>stup</sub>   | Buffer startup time                                                                        | _      | _     | 100    | μs   |       |

| $V_{vdrift}$        | Voltage drift (Vmax -Vmin across the full voltage range)                                   | _      | 2     | _      | mV   | 1     |

- 1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

- 2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

Table 31. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   |       |

Table 32. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    |       |

#### 6.7 Timers

See General switching specifications.

### 6.8 Communication interfaces

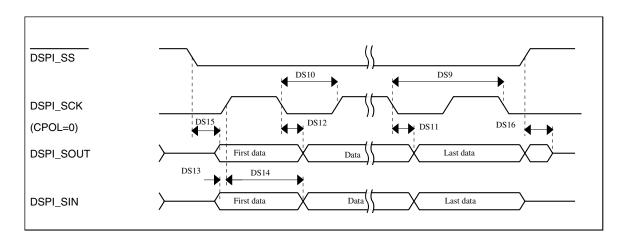

14

14

ns

ns

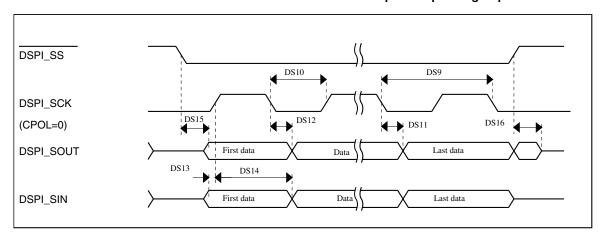

**DS15**

**DS16**

DSPI\_SS active to DSPI\_SOUT driven

DSPI\_SS inactive to DSPI\_SOUT not driven

| Num  | Description                      | Min.                      | Max.                      | Unit |

|------|----------------------------------|---------------------------|---------------------------|------|

| DS10 | DSPI_SCK input high/low time     | (t <sub>SCK</sub> /2) - 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid      | _                         | 10                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid    | 0                         | _                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup | 2                         | _                         | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold  | 7                         | _                         | ns   |

Table 34. Slave mode DSPI timing (limited voltage range) (continued)

Figure 17. DSPI classic SPI timing — slave mode

#### 6.8.2 DSPI switching specifications (full voltage range)

The DMA Serial Peripheral Interface (DSPI) provides a synchronous serial bus with master and slave operations. Many of the transfer attributes are programmable. The tables below provides DSPI timing characteristics for classic SPI timing modes. Refer to the DSPI chapter of the Reference Manual for information on the modified transfer formats used for communicating with slower peripheral devices.

Num Description Min. Max. Unit **Notes** 1.71 3.6 ٧ Operating voltage Frequency of operation 12.5 MHz DS<sub>1</sub> DSPI\_SCK output cycle time 4 x t<sub>BUS</sub> ns DS2 DSPI\_SCK output high/low time  $(t_{SCK}/2) - 4$  $(t_{SCK/2}) + 4$ ns DS3 DSPI\_PCSn valid to DSPI\_SCK delay 2  $(t_{BUS} \times 2)$ ns

Table 35. Master mode DSPI timing (full voltage range)

Figure 19. DSPI classic SPI timing — slave mode

### 6.8.3 I<sup>2</sup>C switching specifications

See General switching specifications.

#### 6.8.4 UART switching specifications

See General switching specifications.

#### Normal Run, Wait and Stop mode performance over the full 6.8.5 operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

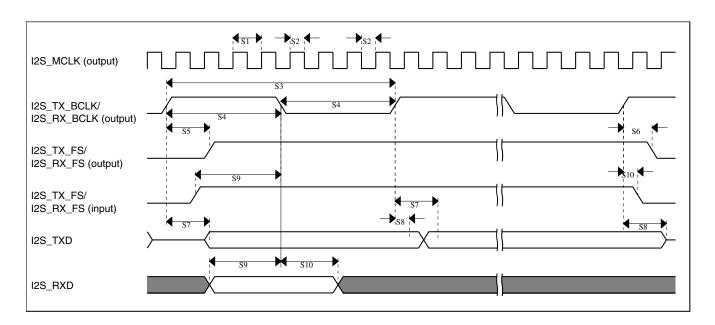

Num. Characteristic Min. Max. Unit 1.71 Operating voltage 3.6 S1 40 I2S\_MCLK cycle time S2 I2S\_MCLK (as an input) pulse width high/low 45% 55% MCLK period S3 I2S\_TX\_BCLK/I2S\_RX\_BCLK cycle time (output) 80 S4 I2S\_TX\_BCLK/I2S\_RX\_BCLK pulse width high/low BCLK period 45% 55% S5 I2S\_TX\_BCLK/I2S\_RX\_BCLK to I2S\_TX\_FS/ 15 I2S\_RX\_FS output valid S6 I2S\_TX\_BCLK/I2S\_RX\_BCLK to I2S\_TX\_FS/ I2S\_RX\_FS output invalid S7 I2S\_TX\_BCLK to I2S\_TXD valid

Table 37. I2S/SAI master mode timing

Table continues on the next page...

15

Table 37. I2S/SAI master mode timing (continued)

| Num. | Characteristic                                   | Min. | Max. | Unit |

|------|--------------------------------------------------|------|------|------|

| S8   | I2S_TX_BCLK to I2S_TXD invalid                   | 0    | _    | ns   |

|      | I2S_RXD/I2S_RX_FS input setup before I2S_RX_BCLK | 25   | _    | ns   |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK   | 0    | _    | ns   |

Figure 20. I2S/SAI timing — master modes

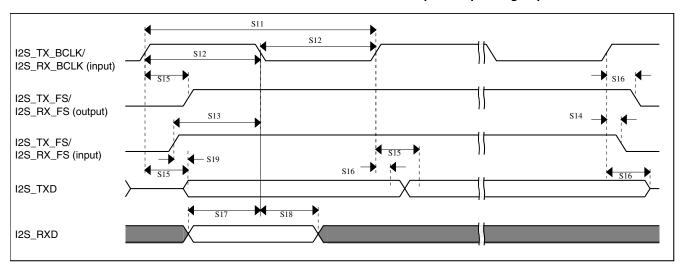

Table 38. I2S/SAI slave mode timing

| Num. | Characteristic                                                 | Min. | Max. | Unit        |

|------|----------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                              | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                     | 80   | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)           | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before I2S_TX_BCLK/I2S_RX_BCLK | 10   | _    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after I2S_TX_BCLK/I2S_RX_BCLK   | 2    | _    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                  | _    | 29   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                | 0    | _    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                               | 10   | _    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                 | 2    | _    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup> | _    | 21   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 21. I2S/SAI timing — slave modes

# 6.8.6 VLPR, VLPW, and VLPS mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in VLPR, VLPW, and VLPS modes.

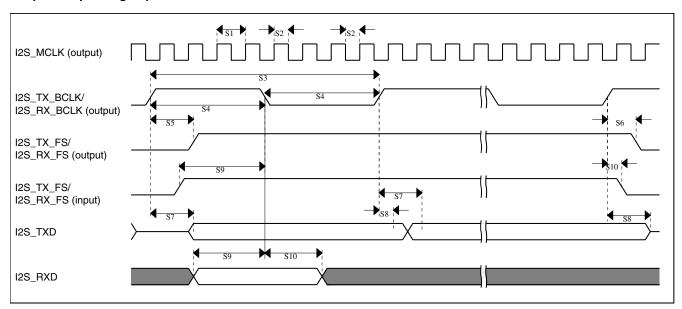

Table 39. I2S/SAI master mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                               | 62.5 | _    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 250  | _    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | _    | 45   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | 0    | _    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | _    | 45   | ns          |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | _    | ns          |

| S9   | I2S_RXD/I2S_RX_FS input setup before I2S_RX_BCLK                  | 75   | _    | ns          |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | _    | ns          |

Figure 22. I2S/SAI timing — master modes

Table 40. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                 | Min. | Max. | Unit        |

|------|----------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                              | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                     | 250  | _    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)           | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before I2S_TX_BCLK/I2S_RX_BCLK | 30   | _    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after I2S_TX_BCLK/I2S_RX_BCLK   | 2    | _    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                  | _    | 87   | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                | 0    | _    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                               | 30   | _    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                 | 2    | _    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup> | _    | 72   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

#### 8.2 K12 Pinouts

The below figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

How to Reach Us:

Home Page: freescale.com

Web Support:

freescale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, Energy Efficient Solutions logo, and Kinetis are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM and Cortex are the registered trademarks of ARM Limited. © 2012-2013 Freescale Semiconductor, Inc.

Document Number: K12P80M50SF4

Rev. 4.1 08/2013