Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Product Status                 | Obsolete                                                                  |

|--------------------------------|---------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells |                                                                           |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 83                                                                        |

| Number of Gates                | 24000                                                                     |

| Voltage - Supply               | 3V ~ 3.6V, 4.5V ~ 5.5V                                                    |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                         |

| Package / Case                 | 100-BQFP                                                                  |

| Supplier Device Package        | 100-PQFP (20x14)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx16-2pq100i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

| Figure 51 | BG272 |

|-----------|-------|

| Figure 52 | PG132 |

| Figure 53 | CQ172 |

- The Transient Current, page 13 is new (SAR 36930).

- Package names were revised according to standards established in *Package Mechanical Drawings* (SAR 34774)

## 1.7 Revision 9.0

The following is a summary of the changes in revision 9.0 of this document

In Table 20, page 23, the limits in VI were changed from -0.5 to VCCI + 0.5 to -0.5 to VCCA + 0.5

In Table 22, page 25, V<sub>OH</sub> was changed from 3.7 to 2.4 for the min in industrial and military. V<sub>IH</sub> had V<sub>CCI</sub> and that was changed to VCCA

## 1.8 Revision 6.0

The following is a summary of the changes in revision 6.0 of this document.

- The Ease of Integration, page 1 was updated

- The Temperature Grade Offerings, page 5 is new

- The Speed Grade Offerings, page 5 is new

- The General Description, page 6 was updated

- The MultiPlex I/O Modules, page 11 was updated

- The User Security, page 12 was updated

- Table 6, page 13 was updated

- The Power Dissipation, page 14 was updated.

- The Static Power Component, page 14 was updated

- The Equivalent Capacitance, page 15 was updated

- Figure 13, page 17 was updated

- Table 10, page 18 was updated.

- Figure 14, page 18 was updated.

- Table 11, page 19 was updated.

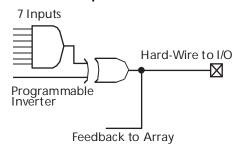

#### Figure 5 • A42MX24 and A42MX36 D-Module Implementation

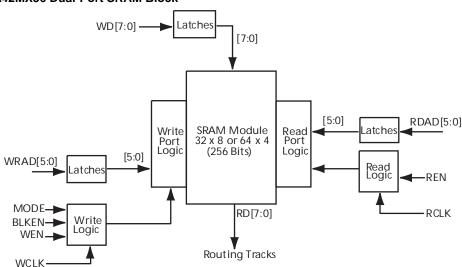

#### Figure 6 • A42MX36 Dual-Port SRAM Block

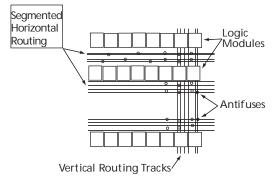

## 3.2.3 Routing Structure

The MX architecture uses vertical and horizontal routing tracks to interconnect the various logic and I/O modules. These routing tracks are metal interconnects that may be continuous or split into segments. Varying segment lengths allow the interconnect of over 90% of design tracks to occur with only two antifuse connections. Segments can be joined together at the ends using antifuses to increase their lengths up to the full length of the track. All interconnects can be accomplished with a maximum of four antifuses.

### 3.2.3.1 Horizontal Routing

Horizontal routing tracks span the whole row length or are divided into multiple segments and are located in between the rows of modules. Any segment that spans more than one-third of the row length is considered a long horizontal segment. A typical channel is shown in Figure 7, page 10. Within horizontal routing, dedicated routing tracks are used for global clock networks and for power and ground tie-off tracks. Non-dedicated tracks are used for signal nets.

### 3.2.3.2 Vertical Routing

Another set of routing tracks run vertically through the module. There are three types of vertical tracks: input, output, and long. Long tracks span the column length of the module, and can be divided into multiple segments. Each segment in an input track is dedicated to the input of a particular module; each segment in an output track is dedicated to the output of a particular module. Long segments are uncommitted and can be assigned during routing.

Each output segment spans four channels (two above and two below), except near the top and bottom of the array, where edge effects occur. Long vertical tracks contain either one or two segments. An example of vertical routing tracks and segments is shown in Figure 7, page 10.

## 3.2.3.3 Antifuse Structures

An antifuse is a "normally open" structure. The use of antifuses to implement a programmable logic device results in highly testable structures as well as efficient programming algorithms. There are no pre-existing connections; temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed and individual circuit structures to be tested, which can be done before and after programming. For instance, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

#### Figure 7 • MX Routing Structure

## 3.2.4 Clock Networks

The 40MX devices have one global clock distribution network (CLK). A signal can be put on the CLK network by being routed through the CLKBUF buffer.

In 42MX devices, there are two low-skew, high-fanout clock distribution networks, referred to as CLKA and CLKB. Each network has a clock module (CLKMOD) that can select the source of the clock signal from any of the following (Figure 8, page 11):

- Externally from the CLKA pad, using CLKBUF buffer

- Externally from the CLKB pad, using CLKBUF buffer

- Internally from the CLKINTA input, using CLKINT buffer

- Internally from the CLKINTB input, using CLKINT buffer

The clock modules are located in the top row of I/O modules. Clock drivers and a dedicated horizontal clock track are located in each horizontal routing channel.

Clock input pads in both 40MX and 42MX devices can also be used as normal I/Os, bypassing the clock networks.

The A42MX36 device has four additional register control resources, called quadrant clock networks (Figure 9, page 11). Each quadrant clock provides a local, high-fanout resource to the contiguous logic modules within its quadrant of the device. Quadrant clock signals can originate from specific I/O pins or from the internal array and can be used as a secondary register clock, register clear, or output enable.

$f_{\alpha 2}$  = Average second routed array clock rate in MHz)

| Device Type | r1 routed_Clk1 | r2 routed_Clk2 |  |  |  |

|-------------|----------------|----------------|--|--|--|

| A40MX02     | 41.4           | N/A            |  |  |  |

| A40MX04     | 68.6           | N/A            |  |  |  |

| A42MX09     | 118            | 118            |  |  |  |

| A42MX16     | 165            | 165            |  |  |  |

| A42MX24     | 185            | 185            |  |  |  |

| A42MX36     | 220            | 220            |  |  |  |

Table 7 •

Fixed Capacitance Values for MX FPGAs (pF)

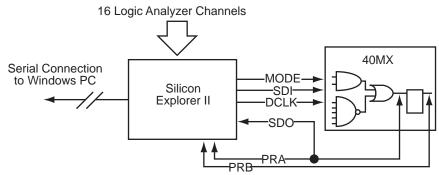

## 3.4.6 Test Circuitry and Silicon Explorer II Probe

MX devices contain probing circuitry that provides built-in access to every node in a design, via the use of Silicon Explorer II. Silicon Explorer II is an integrated hardware and software solution that, in conjunction with the Designer software, allow users to examine any of the internal nets of the device while it is operating in a prototyping or a production system. The user can probe into an MX device without changing the placement and routing of the design and without using any additional resources. Silicon Explorer II's noninvasive method does not alter timing or loading effects, thus shortening the debug cycle and providing a true representation of the device under actual functional situations.

Silicon Explorer II samples data at 100 MHz (asynchronous) or 66 MHz (synchronous). Silicon Explorer II attaches to a PC's standard COM port, turning the PC into a fully functional 18-channel logic analyzer. Silicon Explorer II allows designers to complete the design verification process at their desks and reduces verification time from several hours per cycle to a few seconds.

Silicon Explorer II is used to control the MODE, DCLK, SDI and SDO pins in MX devices to select the desired nets for debugging. The user simply assigns the selected internal nets in the Silicon Explorer II software to the PRA/PRB output pins for observation. Probing functionality is activated when the MODE pin is held HIGH.

Figure 12, page 16 illustrates the interconnection between Silicon Explorer II and 40MX devices, while Figure 13, page 17 illustrates the interconnection between Silicon Explorer II and 42MX devices

To allow for probing capabilities, the security fuses must not be programmed. (See User Security, page 12 for the security fuses of 40MX and 42MX devices). Table 8, page 17 summarizes the possible device configurations for probing.

PRA and PRB pins are dual-purpose pins. When the "Reserve Probe Pin" is checked in the Designer software, PRA and PRB pins are reserved as dedicated outputs for probing. If PRA and PRB pins are required as user I/Os to achieve successful layout and "Reserve Probe Pin" is checked, the layout tool will override the option and place user I/Os on PRA and PRB pins.

#### Figure 12 • Silicon Explorer II Setup with 40MX

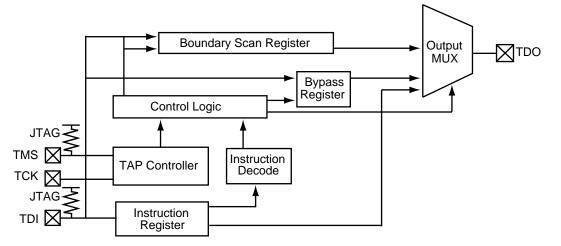

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a device into a boundary-scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic tile and the input, output and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

#### Figure 14 • 42MX IEEE 1149.1 Boundary Scan Circuitry

#### Table 9 • Test Access Port Descriptions

| Port                      | Description                                                                                                                                                                                                                                               |  |  |  |  |  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TMS<br>(Test Mode Select) | Serial input for the test logic control bits. Data is captured on the rising edge of the test logic clock (TCK).                                                                                                                                          |  |  |  |  |  |

| TCK<br>(Test Clock Input) | Dedicated test logic clock used serially to shift test instruction, test data, and control inputs on the rising edge of the clock, and serially to shift the output data on the falling edge of the clock. The maximum clock frequency for TCK is 20 MHz. |  |  |  |  |  |

| TDI<br>(Test Data Input)  | Serial input for instruction and test data. Data is captured on the rising edge of the test logic clock.                                                                                                                                                  |  |  |  |  |  |

| TDO<br>(Test Data Output) | Serial output for test instruction and data from the test logic. TDO is set to an Inactive Drive state (high impedance) when data scanning is not in progress.                                                                                            |  |  |  |  |  |

#### Table 10 • Supported BST Public Instructions

| Instruction    | IR Code<br>(IR2.IR0) | Instruction<br>Type | Description                                                                                                                                                                  |

|----------------|----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000                  | Mandatory           | Allows the external circuitry and board-level interconnections to be<br>tested by forcing a test pattern at the output pins and capturing test<br>results at the input pins. |

| SAMPLE/PRELOAD | 001                  | Mandatory           | Allows a snapshot of the signals at the device pins to be captured and examined during operation                                                                             |

| HIGH Z         | 101                  | Optional            | Tristates all I/Os to allow external signals to drive pins. See the IEEE Standard 1149.1 specification.                                                                      |

| CLAMP          | 110                  | Optional            | Allows state of signals driven from component pins to be determined<br>from the Boundary-Scan Register. See the IEEE Standard 1149.1<br>specification for details.           |

| BYPASS         | 111                  | Mandatory           | Enables the bypass register between the TDI and TDO pins. The test data passes through the selected device to adjacent devices in the test chain.                            |

#### **3.3 V LVTTL Electrical Specifications** 3.8.1

#### Table 19 • 3.3V LVTTL Electrical Specifications

|                                        |                      | Commercial |             | Com      | nercial -F   | Indus  | trial        | Military |                |       |

|----------------------------------------|----------------------|------------|-------------|----------|--------------|--------|--------------|----------|----------------|-------|

| Symbol                                 | Parameter            | Min.       | Max.        | Min.     | Max.         | Min.   | Max.         | Min.     | Max.           | Units |

| VOH <sup>1</sup>                       | IOH = -4 mA          | 2.15       |             | 2.15     |              | 2.4    |              | 2.4      |                | V     |

| VOL <sup>1</sup>                       | IOL = 6 mA           |            | 0.4         |          | 0.4          |        | 0.48         |          | 0.48           | V     |

| VIL                                    |                      | -0.3       | 0.8         | -0.3     | 0.8          | -0.3   | 0.8          | -0.3     | 0.8            | V     |

| VIH (40MX)                             |                      | 2.0        | VCC + 0.3   | 2.0      | VCC + 0.3    | 2.0    | VCC + 0.3    | 2.0      | VCC + 0.3      | V     |

| VIH (42MX)                             |                      | 2.0        | VCCI + 0.3  | 2.0      | VCCI + 0.3   | 2.0    | VCCI + 0.3   | 2.0      | VCCI + 0.3     | V     |

| IIL                                    |                      |            | -10         |          | -10          |        | -10          |          | -10            | μA    |

| IIH                                    |                      |            | -10         |          | -10          |        | -10          |          | -10            | μA    |

| Input Transition Time, $T_R$ and $T_F$ |                      |            | 500         |          | 500          |        | 500          |          | 500            | ns    |

| C <sub>IO</sub> I/O<br>Capacitance     |                      |            | 10          |          | 10           |        | 10           |          | 10             | pF    |

| Standby<br>Current, ICC <sup>2</sup>   | A40MX02,<br>A40MX04  |            | 3           |          | 25           |        | 10           |          | 25             | mA    |

|                                        | A42MX09              |            | 5           |          | 25           |        | 25           |          | 25             | mA    |

|                                        | A42MX16              |            | 6           |          | 25           |        | 25           |          | 25             | mA    |

|                                        | A42MX24,<br>A42MX36  |            | 15          |          | 25           |        | 25           |          | 25             | mA    |

| Low-Power<br>Mode Standby<br>Current   | 42MX<br>devices only |            | 0.5         |          | ICC - 5.0    |        | ICC - 5.0    |          | ICC - 5.0      | mA    |

| IIO, I/O source                        | Can be derive        | ed from    | the IBIS mo | del (htt | p://www.micr | osemi. | com/soc/tech | ndocs/n  | nodels/ibis.ht | ml)   |

sink current

Only one output tested at a time. VCC/VCCI = min. 1.

All outputs unloaded. All inputs = VCC/VCCI or GND. 2.

### Mixed 5.0 V / 3.3 V Operating Conditions (for 42MX 3.9 **Devices Only)**

#### Table 20 • Absolute Maximum Ratings\*

| Symbol           | Parameter                   | Limits             | Units |

|------------------|-----------------------------|--------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | –0.5 to +7.0       | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0       | V     |

| VI               | Input Voltage               | -0.5 to VCCA +0.5  | V     |

| VO               | Output Voltage              | -0.5 to VCCI + 0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150        | °C    |

Note: \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device

Note: Values are shown for A42MX36 –3 at 5.0 V worst-case commercial conditions.

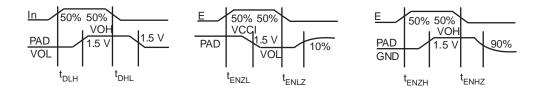

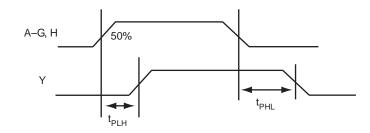

## 3.10.1 Parameter Measurement

The following figures show parameter measurement details.

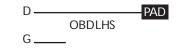

#### Figure 21 • Output Buffer Delays

#### Figure 27 • Output Buffer Latches

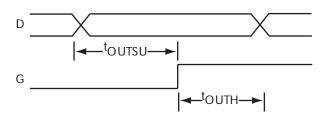

## 3.10.4 Decode Module Timing

The following figure shows decode module timing.

#### Figure 28 • Decode Module Timing

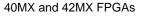

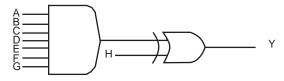

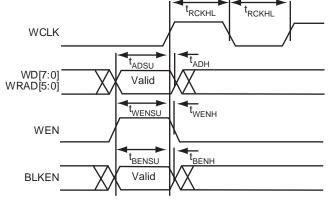

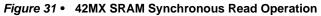

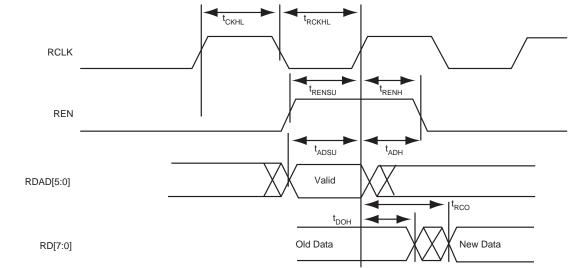

## 3.10.5 SRAM Timing Characteristics

The following figure shows SRAM timing characteristics.

#### Figure 29 • SRAM Timing Characteristics

| Write Port                                         |                                         | Read Port                                    |  |  |  |  |  |

|----------------------------------------------------|-----------------------------------------|----------------------------------------------|--|--|--|--|--|

| <br>WRAD [5:0]<br>BLKEN<br>WEN<br>WCLK<br>WD [7:0] | RAM Array<br>32x8 or 64x4<br>(256 Bits) | RDAD [5:0]<br>LEW<br>REN<br>RCLK<br>RD [7:0] |  |  |  |  |  |

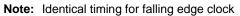

## 3.10.6 Dual-Port SRAM Timing Waveforms

The following figures show dual-port SRAM timing waveforms.

#### Figure 30 • 42MX SRAM Write Operation

**Note:** Identical timing for falling edge clock

### Figure 32 • 42MX SRAM Asynchronous Read Operation—Type 1 (Read Address Controlled)

# Table 36 •A40MX04 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                                    |                     | –3 Sj          | beed       | –2 Sp      | beed       | –1 S        | peed       | Std S      | Speed      | –F S         | peed         |       |

|--------------------|----------------------------------------------------|---------------------|----------------|------------|------------|------------|-------------|------------|------------|------------|--------------|--------------|-------|

| Parame             | ter / Description                                  |                     | Min.           | Max.       | Min.       | Max.       | Min.        | Max.       | Min.       | Max.       | Min.         | Max.         | Units |

| t <sub>HENA</sub>  | Flip-Flop (Latch)<br>Enable Hold                   |                     | 0.0            |            | 0.0        |            | 0.0         |            | 0.0        |            | 0.0          |              | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse \          | Vidth               | 3.3            |            | 3.8        |            | 4.3         |            | 5.0        |            | 7.0          |              | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse            | e Width             | 3.3            |            | 3.8        |            | 4.3         |            | 5.0        |            | 7.0          |              | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Inpu                               | t Period            | 4.8            |            | 5.6        |            | 6.3         |            | 7.5        |            | 10.4         |              | ns    |

| f <sub>MAX</sub>   | Flip-Flop (Latch)<br>Clock Frequency<br>(FO = 128) |                     |                | 181        |            | 167        |             | 154        |            | 134        |              | 80           | MHz   |

| Input M            | odule Propagation D                                | )elays              |                |            |            |            |             |            |            |            |              |              |       |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                      |                     |                | 0.7        |            | 0.8        |             | 0.9        |            | 1.1        |              | 1.5          | ns    |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                       |                     |                | 0.6        |            | 0.7        |             | 0.8        |            | 1.0        |              | 1.3          | ns    |

| Input M            | odule Predicted Rou                                | ting Delays         | s <sup>1</sup> |            |            |            |             |            |            |            |              |              |       |

| t <sub>IRD1</sub>  | FO = 1 Routing Dela                                | ау                  |                | 2.1        |            | 2.4        |             | 2.2        |            | 3.2        |              | 4.5          | ns    |

| t <sub>IRD2</sub>  | FO = 2 Routing Dela                                | ау                  |                | 2.6        |            | 3.0        |             | 3.4        |            | 4.0        |              | 5.6          | ns    |

| t <sub>IRD3</sub>  | FO = 3 Routing Dela                                | ау                  |                | 3.1        |            | 3.6        |             | 4.1        |            | 4.8        |              | 6.7          | ns    |

| t <sub>IRD4</sub>  | FO = 4 Routing Dela                                | ау                  |                | 3.6        |            | 4.2        |             | 4.8        |            | 5.6        |              | 7.8          | ns    |

| t <sub>IRD8</sub>  | FO = 8 Routing Dela                                | ау                  |                | 5.7        |            | 6.6        |             | 7.5        |            | 8.8        |              | 12.4         | ns    |

| Global             | Clock Network                                      |                     |                |            |            |            |             |            |            |            |              |              |       |

| t <sub>CKH</sub>   | Input Low to HIGH                                  | FO = 16<br>FO = 128 |                | 4.6<br>4.6 |            | 5.3<br>5.3 |             | 6.0<br>6.0 |            | 7.0<br>7.0 |              | 9.8<br>9.8   | ns    |

| t <sub>CKL</sub>   | Input High to LOW                                  | FO = 16<br>FO = 128 |                | 4.8<br>4.8 |            | 5.6<br>5.6 |             | 6.3<br>6.3 |            | 7.4<br>7.4 |              | 10.4<br>10.4 | ns    |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH                        | FO = 16<br>FO = 128 | 2.2<br>2.4     |            | 2.6<br>2.7 |            | 2.9<br>3.1  |            | 3.4<br>3.6 |            | 4.8<br>5.1   |              | ns    |

| t <sub>PWL</sub>   | Minimum Pulse<br>Width LOW                         | FO = 16<br>FO = 128 | 2.2<br>2.4     |            | 2.6<br>2.7 |            | 2.9<br>3.01 |            | 3.4<br>3.6 |            | 4.8<br>5.1   |              | ns    |

| t <sub>CKSW</sub>  | Maximum Skew                                       | FO = 16<br>FO = 128 |                | 0.4<br>0.5 |            | 0.5<br>0.6 |             | 0.5<br>0.7 |            | 0.6<br>0.8 |              | 0.8<br>1.2   | ns    |

| t <sub>P</sub>     | Minimum Period                                     | FO = 16<br>FO = 128 | 4.7<br>4.8     |            | 5.4<br>5.6 |            | 6.1<br>6.3  |            | 7.2<br>7.5 |            | 10.0<br>10.4 |              | ns    |

| f <sub>MAX</sub>   | Maximum<br>Frequency                               | FO = 16<br>FO = 128 |                | 188<br>181 |            | 175<br>168 |             | 160<br>154 |            | 139<br>134 |              | 83<br>80     | MHz   |

| TTL Out            | tput Module Timing <sup>4</sup>                    |                     |                |            |            |            |             |            |            |            |              |              |       |

| t <sub>DLH</sub>   | Data-to-Pad HIGH                                   |                     |                | 3.3        |            | 3.8        |             | 4.3        |            | 5.1        |              | 7.2          | ns    |

| t <sub>DHL</sub>   | Data-to-Pad LOW                                    |                     |                | 4.0        |            | 4.6        |             | 5.2        |            | 6.1        |              | 8.6          | ns    |

| t <sub>ENZH</sub>  | Enable Pad Z to HIC                                | ЭH                  |                | 3.7        |            | 4.3        |             | 4.9        |            | 5.8        |              | 8.0          | ns    |

| t <sub>ENZL</sub>  | Enable Pad Z to LO                                 | W                   |                | 4.7        |            | 5.4        |             | 6.1        |            | 7.2        |              | 10.1         | ns    |

| t <sub>ENHZ</sub>  | Enable Pad HIGH to                                 | Σ                   |                | 7.9        |            | 9.1        |             | 10.4       |            | 12.2       |              | 17.1         | ns    |

# Table 40 •A42MX16 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                         |                                |                     | –3 S       | peed       | –2 Sj       | beed       | –1 Sp      | beed       | Std S      | peed       | –F Sp       | beed       |            |

|-------------------------|--------------------------------|---------------------|------------|------------|-------------|------------|------------|------------|------------|------------|-------------|------------|------------|

| Parameter / Description |                                |                     |            | Max.       | Min.        | Max.       | Min.       | Max.       | Min.       | Max.       | Min.        | Max.       | Units      |

| t <sub>PWL</sub>        | Minimum Pulse Width<br>LOW     | FO = 32<br>FO = 384 | 3.2<br>3.7 |            | 3.5<br>4.1  |            | 4.0<br>4.6 |            | 4.7<br>5.4 |            | 6.6<br>7.6  |            | ns<br>ns   |

| t <sub>CKSW</sub>       | Maximum Skew                   | FO = 32<br>FO = 384 |            | 0.3<br>0.3 |             | 0.4<br>0.4 |            | 0.4<br>0.4 |            | 0.5<br>0.5 |             | 0.7<br>0.7 | ns<br>ns   |

| t <sub>SUEXT</sub>      | Input Latch External<br>Set-Up | FO = 32<br>FO = 384 | 0.0<br>0.0 |            | 0.0<br>0.0  |            | 0.0<br>0.0 |            | 0.0<br>0.0 |            | 0.0<br>0.0  |            | ns<br>ns   |

| t <sub>HEXT</sub>       | Input Latch External<br>Hold   | FO = 32<br>FO = 384 | 2.8<br>3.2 |            | 3.1<br>3.5  |            | 5.5<br>4.0 |            | 4.1<br>4.7 |            | 5.7<br>6.6  |            | ns<br>ns   |

| t <sub>P</sub>          | Minimum Period                 | FO = 32<br>FO = 384 | 4.2<br>4.6 |            | 4.67<br>5.1 |            | 5.1<br>5.6 |            | 5.8<br>6.4 |            | 9.7<br>10.7 |            | ns<br>ns   |

| f <sub>MAX</sub>        | Maximum Frequency              | FO = 32<br>FO = 384 |            | 237<br>215 |             | 215<br>195 |            | 198<br>179 |            | 172<br>156 |             | 103<br>94  | MHz<br>MHz |

# Table 41 • A42MX16 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                            |                       | –3 S       | peed       | –2 Sp      | beed       | –1 Sj      | beed       | Std S      | Std Speed -F Sp |              | beed         |          |

|--------------------|--------------------------------------------|-----------------------|------------|------------|------------|------------|------------|------------|------------|-----------------|--------------|--------------|----------|

| Paramet            | er / Description                           |                       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.            | Min.         | Max.         | Units    |

| Logic Mo           | odule Sequential Timin                     | g <sup>3, 4</sup>     |            |            |            |            |            |            |            |                 |              |              |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up     |                       | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |                 | 0.9          |              | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data                     | Input Hold            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |                 | 0.0          |              | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enat                     | ole Set-Up            | 1.0        |            | 1.1        |            | 1.2        |            | 1.4        |                 | 2.0          |              | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enat                     | ole Hold              | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |                 | 0.0          |              | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Wi | dth                   | 4.8        |            | 5.3        |            | 6.0        |            | 7.1        |                 | 9.9          |              | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse    | Nidth                 | 6.2        |            | 6.9        |            | 7.9        |            | 9.2        |                 | 12.9         |              | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input                      | Period                | 9.5        |            | 10.6       |            | 12.0       |            | 14.1       |                 | 19.8         |              | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Hol                     | d                     | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |                 | 0.0          |              | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Set                     | -Up                   | 0.7        |            | 0.8        |            | 0.9        |            | 1.01       |                 | 1.4          |              | ns       |

| t <sub>OUTH</sub>  | Output Buffer Latch H                      | old                   | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |                 | 0.0          |              | ns       |

| t <sub>outsu</sub> | Output Buffer Latch S                      | et-Up                 | 0.7        |            | 0.8        |            | 0.89       |            | 1.01       |                 | 1.4          |              | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Cloc<br>Frequency        | k                     |            | 129        |            | 117        |            | 108        |            | 94              |              | 56           | MHz      |

| Input Mo           | dule Propagation Dela                      | iys                   |            |            |            |            |            |            |            |                 |              |              |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                              |                       |            | 1.5        |            | 1.6        |            | 1.9        |            | 2.2             |              | 3.1          | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                               |                       |            | 1.1        |            | 1.3        |            | 1.4        |            | 1.7             |              | 2.4          | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                                |                       |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9             |              | 4.1          | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                 |                       |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9             |              | 4.1          | ns       |

| Input Mo           | dule Predicted Routin                      | g Delays <sup>2</sup> |            |            |            |            |            |            |            |                 |              |              |          |

| t <sub>IRD1</sub>  | FO = 1 Routing<br>Delay                    |                       |            | 2.6        |            | 2.9        |            | 3.2        |            | 3.8             |              | 5.3          | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing<br>Delay                    |                       |            | 2.9        |            | 3.2        |            | 3.7        |            | 4.3             |              | 6.1          | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing<br>Delay                    |                       |            | 3.3        |            | 3.6        |            | 4.1        |            | 4.9             |              | 6.8          | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing<br>Delay                    |                       |            | 3.6        |            | 4.0        |            | 4.6        |            | 5.4             |              | 7.6          | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing<br>Delay                    |                       |            | 5.1        |            | 5.6        |            | 6.4        |            | 7.5             |              | 10.5         | ns       |

| Global C           | lock Network                               |                       |            |            |            |            |            |            |            |                 |              |              |          |

| t <sub>CKH</sub>   | Input LOW to HIGH                          | FO = 32<br>FO = 384   |            | 4.4<br>4.8 |            | 4.8<br>5.3 |            | 5.5<br>6.0 |            | 6.5<br>7.1      |              | 9.0<br>9.9   | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW                          | FO = 32<br>FO = 384   |            | 5.3<br>6.2 |            | 5.9<br>6.9 |            | 6.7<br>7.9 |            | 7.8<br>9.2      |              | 11.0<br>12.9 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH                | FO = 32<br>FO = 384   | 5.7<br>6.6 |            | 6.3<br>7.4 |            | 7.1<br>8.3 |            | 8.4<br>9.8 |                 | 11.8<br>13.7 |              | ns<br>ns |

| 7 | able | 54        | • | PQ240 |

|---|------|-----------|---|-------|

|   | abic | <b>UT</b> |   | IQLIU |

| PQ240      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 237        | GND              |

| 238        | MODE             |

| 239        | VCCA             |

| 240        | GND              |

#### Figure 46 • VQ80

*Table 55* • VQ80

| VQ80       |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A40MX02<br>Function | A40MX04<br>Function |

| 1          | I/O                 | I/O                 |

| 2          | NC                  | I/O                 |

| 3          | NC                  | I/O                 |

| 4          | NC                  | I/O                 |

| 5          | I/O                 | I/O                 |

| 6          | I/O                 | I/O                 |

| 7          | GND                 | GND                 |

| 3          | I/O                 | I/O                 |

| Э          | I/O                 | I/O                 |

| 10         | I/O                 | I/O                 |

| 11         | I/O                 | I/O                 |

| 12         | I/O                 | I/O                 |

|            |                     |                     |

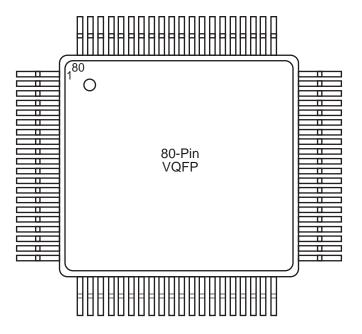

#### Figure 47 • VQ100

#### Table 56 • VQ100

| VQ100      |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A42MX09<br>Function | A42MX16<br>Function |

| 1          | I/O                 | I/O                 |

| 2          | MODE                | MODE                |

| 3          | I/O                 | I/O                 |

| 4          | I/O                 | I/O                 |

| 5          | I/O                 | I/O                 |

| 6          | I/O                 | I/O                 |

| 7          | GND                 | GND                 |

| 8          | I/O                 | I/O                 |

| 9          | I/O                 | I/O                 |

| 10         | I/O                 | I/O                 |

| 11         | I/O                 | I/O                 |

| 12         | I/O                 | I/O                 |

| 13         | I/O                 | I/O                 |

| 14         | VCCA                | NC                  |

| 15         | VCCI                | VCCI                |

| 16         | I/O                 | I/O                 |

| 17         | I/O                 | I/O                 |

| 18         | I/O                 | I/O                 |

| 19         | I/O                 | I/O                 |

| 20         | GND                 | GND                 |

#### Table 57 • TQ176

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 158        | CLKB, I/O        | CLKB, I/O        | CLKB, I/O        |

| 159        | I/O              | I/O              | I/O              |

| 160        | PRB, I/O         | PRB, I/O         | PRB, I/O         |

| 161        | NC               | I/O              | WD, I/O          |

| 162        | I/O              | I/O              | WD, I/O          |

| 163        | I/O              | I/O              | I/O              |

| 164        | I/O              | I/O              | I/O              |

| 165        | NC               | NC               | WD, I/O          |

| 166        | NC               | I/O              | WD, I/O          |

| 167        | I/O              | I/O              | I/O              |

| 168        | NC               | I/O              | I/O              |

| 169        | I/O              | I/O              | I/O              |

| 170        | NC               | VCCI             | VCCI             |

| 171        | I/O              | I/O              | WD, I/O          |

| 172        | I/O              | I/O              | WD, I/O          |

| 173        | NC               | I/O              | I/O              |

| 174        | I/O              | I/O              | I/O              |

| 175        | DCLK, I/O        | DCLK, I/O        | DCLK, I/O        |

| 176        | I/O              | I/O              | I/O              |

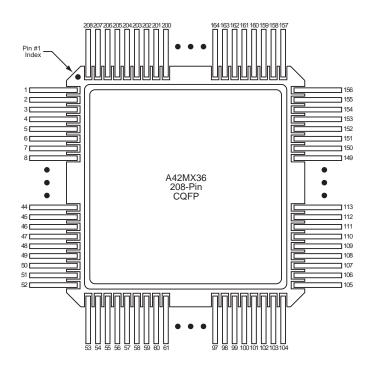

Figure 49 • CQ208

| CQ256      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 96         | VCCA             |

| 97         | GND              |

| 98         | GND              |

| 99         | I/O              |

| 100        | I/O              |

| 101        | I/O              |

| 102        | I/O              |

| 103        | I/O              |

| 104        | I/O              |

| 105        | WD, I/O          |

| 106        | WD, I/O          |

| 107        | I/O              |

| 108        | I/O              |

| 109        | WD, I/O          |

| 110        | WD, I/O          |

| 111        | I/O              |

| 112        | QCLKA, I/O       |

| 113        | I/O              |

| 114        | GND              |

| 115        | I/O              |

| 116        | I/O              |

| 117        | I/O              |

| 118        | I/O              |

| 119        | VCCI             |

| 120        | I/O              |

| 121        | WD, I/O          |

| 122        | WD, I/O          |

| 123        | I/O              |

| 124        | I/O              |

| 125        | I/O              |

| 126        | I/O              |

| 127        | GND              |

| 128        | NC               |

| 129        | NC               |

| 130        | NC               |

| 131        | GND              |

| 132        | I/O              |

| <i>Table 61</i> • PG132 |                  |

|-------------------------|------------------|

| PG132                   |                  |

| Pin Number              | A42MX09 Function |

| G12                     | VSV              |

| F13                     | I/O              |

| F12                     | I/O              |

| F11                     | I/O              |

| F10                     | I/O              |

| E13                     | I/O              |

| D13                     | I/O              |

| D12                     | I/O              |

| C13                     | I/O              |

| B13                     | I/O              |

| D11                     | I/O              |

| C12                     | I/O              |

| A13                     | I/O              |

| C11                     | I/O              |

| B12                     | SDI              |

| B11                     | I/O              |

| C10                     | I/O              |

| A12                     | I/O              |

| A11                     | I/O              |

| B10                     | I/O              |

| D8                      | I/O              |

| A10                     | I/O              |

| C8                      | I/O              |

| A9                      | I/O              |

| B8                      | PRBA             |

| A8                      | I/O              |

| B7                      | CLKA             |

| A7                      | I/O              |

| B6                      | CLKB             |

| A6                      | I/O              |

| C6                      | PRBB             |

| A5                      | I/O              |

| D6                      | I/O              |

| A4                      | I/O              |

| B4                      | I/O              |

| A3                      | I/O              |

| C4                      | I/O              |

|                         | <b>1/</b> 0      |

| <i>Table 62</i> • CQ172 |       |

|-------------------------|-------|

| 138                     | I/O   |

| 139                     | I/O   |

| 140                     | I/O   |

| 141                     | GND   |

| 142                     | I/O   |

| 143                     | I/O   |

| 144                     | I/O   |

| 145                     | I/O   |

| 146                     | I/O   |

| 147                     | I/O   |

| 148                     | PROBA |

| 149                     | I/O   |

| 150                     | CLKA  |

| 151                     | VCC   |

| 152                     | GND   |

| 153                     | I/O   |

| 154                     | CLKB  |

| 155                     | I/O   |

| 156                     | PROBB |

| 157                     | I/O   |

| 158                     | I/O   |

| 159                     | I/O   |

| 160                     | I/O   |

| 161                     | GND   |

| 162                     | I/O   |

| 163                     | I/O   |

| 164                     | I/O   |

| 165                     | I/O   |

| 166                     | VCCI  |

| 167                     | I/O   |

| 168                     | I/O   |

| 169                     | I/O   |

| 170                     | I/O   |

| 171                     | DCLK  |

|                         |       |