Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | -                                                             |

| Number of Logic Elements/Cells | -                                                             |

| Total RAM Bits                 | -                                                             |

| Number of I/O                  | 140                                                           |

| Number of Gates                | 24000                                                         |

| Voltage - Supply               | 3V ~ 3.6V, 4.75V ~ 5.25V                                      |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 70°C (TA)                                               |

| Package / Case                 | 176-LQFP                                                      |

| Supplier Device Package        | 176-TQFP (24x24)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a42mx16-2tq176 |

|                                |                                                               |

Email: info@E-XFL.COM

E·XF

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 Revision 15.0

The following is a summary of the changes in revision 15.0 of this document.

- Table 15, page 21 is edited to add the footnote, VIH(Min) is 2.4V for A42MX36 family. This applies only to VCCI of 5V and is not applicable to VCCI of 3.3V

- Table 22, page 25 is edited to add the footnote, VIH(Min) is 2.4V for A42MX36 family. This applies only to VCCI of 5V and is not applicable to VCCI of 3.3V

- Table 23, page 25 is edited to add the footnote, VIH(Min) is 2.4V for A42MX36 family. This applies only to VCCI of 5V and is not applicable to VCCI of 3.3V

# 1.2 Revision 14.0

The following is a summary of the changes in revision 14.0 of this document.

- Added CQFP package information for A42MX16 device in Product Profile, page 1 and Ceramic Device Resources, page 4 (SAR 79522).

- Added Military (M) and MIL-STD-883 Class B (B) grades for CPGA 132 Package and added Commercial (C), Military (M), and MIL-STD-883 Class B (B) grades for CQFP 172 Package in Temperature Grade Offerings, page 5 (SAR 79519)

- Changed Silicon Sculptor II to Silicon Sculptor in Programming, page 12 (SAR 38754)

- Added Figure 53, page 158 CQ172 package (SAR 79522).

## 1.3 **Revision 13.0**

The following is a summary of the changes in revision 13.0 of this document.

- Added Figure 42, page 97 PQ144 Package for A42MX09 device (SAR 69776)

- Added Figure 52, page 153 PQ132 Package for A42MX09 device (SAR 69776)

## 1.4 **Revision 12.0**

The following is a summary of the changes in revision 12.0 of this document.

- Added information on power-up behavior for A42MX24 and A42MX36 devices to the Power Supply, page 13 (SAR 42096

- Corrected the inadvertent mistake in the naming of the PL68 pin assignment table (SARs 48999, 49793)

# 1.5 Revision 11.0

The following is a summary of the changes in revision 11.0 of this document.

- The FuseLock logo and accompanying text was removed from the User Security, page 12. This marking is no longer used on Microsemi devices (PCN 0915)

- The Development Tool Support, page 19 was updated (SAR 38512)

# 1.6 Revision 10.0

The following is a summary of the changes in revision 10.0 of this document.

- Ordering Information, page 3 was updated to include lead-free package ordering codes (SAR 21968)

- The User Security, page 12 was revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 34673)

# 2 40MX and 42MX FPGA Families

## 2.1 Features

The following sections list out various features of the 40MX and 42MX FPGA family devices.

## 2.1.1 High Capacity

- Single-Chip ASIC Alternative

- 3,000 to 54,000 System Gates

- Up to 2.5 kbits Configurable Dual-Port SRAM

- Fast Wide-Decode Circuitry

- Up to 202 User-Programmable I/O Pins

### 2.1.2 High Performance

- 5.6 ns Clock-to-Out

- 250 MHz Performance

- 5 ns Dual-Port SRAM Access

- 100 MHz FIFOs

- 7.5 ns 35-Bit Address Decode

## 2.1.3 HiRel Features

- Commercial, Industrial, Automotive, and Military Temperature Plastic Packages

- Commercial, Military Temperature, and MIL-STD-883 Ceramic Packages

- QML Certification

- Ceramic Devices Available to DSCC SMD

## 2.1.4 Ease of Integration

- Mixed-Voltage Operation (5.0 V or 3.3 V for core and I/Os), with PCI-Compliant I/Os

- Up to 100% Resource Utilization and 100% Pin Locking

- Deterministic, User-Controllable Timing

- Unique In-System Diagnostic and Verification Capability with Silicon Explorer II

# Low Power Consumption IEEE Standard 1149.1 (JTAG) Boundary Scan Testing

## 2.2 Product Profile

The following table gives the features of the products.

### Table 1 • Product profile

| Device               | A40MX02 | A40MX04 | A42MX09 | A42MX16 | A42MX24 | A42MX36 |

|----------------------|---------|---------|---------|---------|---------|---------|

| Capacity             |         |         |         |         |         |         |

| System Gates         | 3,000   | 6,000   | 14,000  | 24,000  | 36,000  | 54,000  |

| SRAM Bits            | _       | -       | -       | -       | -       | 2,560   |

| Logic Modules        |         |         |         |         |         |         |

| Sequential           | _       | _       | 348     | 624     | 954     | 1,230   |

| Combinatorial        | 295     | 547     | 336     | 608     | 912     | 1,184   |

| Decode               | _       | -       | -       | -       | 24      | 24      |

| Clock-to-Out         | 9.5 ns  | 9.5 ns  | 5.6 ns  | 6.1 ns  | 6.1 ns  | 6.3 ns  |

| SRAM Modules         |         |         |         |         |         |         |

| (64x4 or 32x8)       | _       | _       | -       | _       | _       | 10      |

| Dedicated Flip-Flops | _       | _       | 348     | 624     | 954     | 1,230   |

# 3 40MX and 42MX FPGAs

# 3.1 General Description

Microsemi's 40MX and 42MX families offer a cost-effective design solution at 5V. The MX devices are single-chip solutions and provide high performance while shortening the system design and development cycle. MX devices can integrate and consolidate logic implemented in multiple PALs, CPLDs, and FPGAs. Example applications include high-speed controllers and address decoding, peripheral bus interfaces, DSP, and co-processor functions.

The MX device architecture is based on Microsemi's patented antifuse technology implemented in a 0.45µm triple-metal CMOS process. With capacities ranging from 3,000 to 54,000 system gates, the MX devices provide performance up to 250 MHz, are live on power-up and have one-fifth the standby power consumption of comparable FPGAs. MX FPGAs provide up to 202 user I/Os and are available in a wide variety of packages and speed grades.

A42MX24 and A42MX36 devices also feature multiPlex I/Os, which support mixed-voltage systems, enable programmable PCI, deliver high-performance operation at both 5.0V and 3.3V, and provide a low-power mode. The devices are fully compliant with the PCI local bus specification (version 2.1). They deliver 200 MHz on-chip operation and 6.1 ns clock-to-output performance.

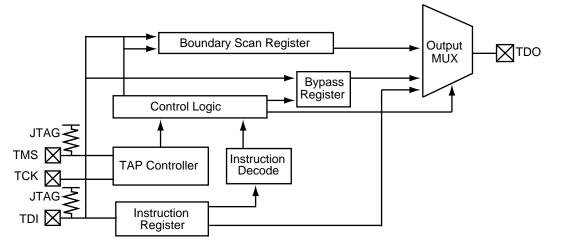

The 42MX24 and 42MX36 devices include system-level features such as IEEE Standard 1149.1 (JTAG) Boundary Scan Testing and fast wide-decode modules. In addition, the A42MX36 device offers dual-port SRAM for implementing fast FIFOs, LIFOs, and temporary data storage. The storage elements can efficiently address applications requiring wide data path manipulation and can perform transformation functions such as those required for telecommunications, networking, and DSP.

All MX devices are fully tested over automotive and military temperature ranges. In addition, the largest member of the family, the A42MX36, is available in both CQ208 and CQ256 ceramic packages screened to MIL-STD-883 levels. For easy prototyping and conversion from plastic to ceramic, the CQ208 and PQ208 devices are pin-compatible.

# 3.2 MX Architectural Overview

The MX devices are composed of fine-grained building blocks that enable fast, efficient logic designs. All devices within these families are composed of logic modules, I/O modules, routing resources and clock networks, which are the building blocks for fast logic designs. In addition, the A42MX36 device contains embedded dual-port SRAM modules, which are optimized for high-speed data path functions such as FIFOs, LIFOs and scratch pad memory. A42MX24 and A42MX36 also contain wide-decode modules.

## 3.2.1 Logic Modules

The 40MX logic module is an eight-input, one-output logic circuit designed to implement a wide range of logic functions with efficient use of interconnect routing resources.(see the following figure).

The logic module can implement the four basic logic functions (NAND, AND, OR and NOR) in gates of two, three, or four inputs. The logic module can also implement a variety of D-latches, exclusivity functions, AND-ORs and OR-ANDs. No dedicated hard-wired latches or flip-flops are required in the array; latches and flip-flops can be constructed from logic modules whenever required in the application.

### 3.2.3.3 Antifuse Structures

An antifuse is a "normally open" structure. The use of antifuses to implement a programmable logic device results in highly testable structures as well as efficient programming algorithms. There are no pre-existing connections; temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed and individual circuit structures to be tested, which can be done before and after programming. For instance, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

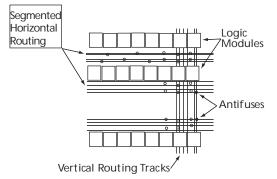

#### Figure 7 • MX Routing Structure

## 3.2.4 Clock Networks

The 40MX devices have one global clock distribution network (CLK). A signal can be put on the CLK network by being routed through the CLKBUF buffer.

In 42MX devices, there are two low-skew, high-fanout clock distribution networks, referred to as CLKA and CLKB. Each network has a clock module (CLKMOD) that can select the source of the clock signal from any of the following (Figure 8, page 11):

- Externally from the CLKA pad, using CLKBUF buffer

- Externally from the CLKB pad, using CLKBUF buffer

- Internally from the CLKINTA input, using CLKINT buffer

- Internally from the CLKINTB input, using CLKINT buffer

The clock modules are located in the top row of I/O modules. Clock drivers and a dedicated horizontal clock track are located in each horizontal routing channel.

Clock input pads in both 40MX and 42MX devices can also be used as normal I/Os, bypassing the clock networks.

The A42MX36 device has four additional register control resources, called quadrant clock networks (Figure 9, page 11). Each quadrant clock provides a local, high-fanout resource to the contiguous logic modules within its quadrant of the device. Quadrant clock signals can originate from specific I/O pins or from the internal array and can be used as a secondary register clock, register clear, or output enable.

Designer software development tools provide a design library of I/O macro functions that can implement all I/O configurations supported by the MX FPGAs.

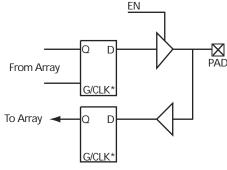

#### Figure 10 • 42MX I/O Module

Note: \*Can be configured as a Latch or D Flip-Flop (Using C-Module)

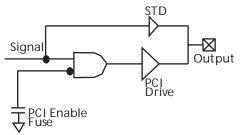

### Figure 11 • PCI Output Structure of A42MX24 and A42MX36 Devices

# 3.3 Other Architectural Features

The following sections cover other architectural features of 40MX and 42MX FPGAs.

## 3.3.1 Performance

MX devices can operate with internal clock frequencies of 250 MHz, enabling fast execution of complex logic functions. MX devices are live on power-up and do not require auxiliary configuration devices and thus are an optimal platform to integrate the functionality contained in multiple programmable logic devices. In addition, designs that previously would have required a gate array to meet performance can be integrated into an MX device with improvements in cost and time-to-market. Using timing-driven place-and-route (TDPR) tools, designers can achieve highly deterministic device performance.

## 3.3.2 User Security

Microsemi FuseLock provides robust security against design theft. Special security fuses are hidden in the fabric of the device and protect against unauthorized users attempting to access the programming and/or probe interfaces. It is virtually impossible to identify or bypass these fuses without damaging the device, making Microsemi antifuse FPGAs protected with the highest level of security available from both invasive and noninvasive attacks.

Special security fuses in 40MX devices include the Probe Fuse and Program Fuse. The former disables the probing circuitry while the latter prohibits further programming of all fuses, including the Probe Fuse. In 42MX devices, there is the Security Fuse which, when programmed, both disables the probing circuitry and prohibits further programming of the device.

## 3.3.3 Programming

Device programming is supported through the Silicon Sculptor series of programmers. Silicon Sculptor is a compact, robust, single-site and multi-site device programmer for the PC. With standalone software, Silicon Sculptor is designed to allow concurrent programming of multiple units from the same PC.

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a device into a boundary-scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic tile and the input, output and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

#### Figure 14 • 42MX IEEE 1149.1 Boundary Scan Circuitry

#### Table 9 • Test Access Port Descriptions

| Port                      | Description                                                                                                                                                                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS<br>(Test Mode Select) | Serial input for the test logic control bits. Data is captured on the rising edge of the test logic clock (TCK).                                                                                                                                          |

| TCK<br>(Test Clock Input) | Dedicated test logic clock used serially to shift test instruction, test data, and control inputs on the rising edge of the clock, and serially to shift the output data on the falling edge of the clock. The maximum clock frequency for TCK is 20 MHz. |

| TDI<br>(Test Data Input)  | Serial input for instruction and test data. Data is captured on the rising edge of the test logic clock.                                                                                                                                                  |

| TDO<br>(Test Data Output) | Serial output for test instruction and data from the test logic. TDO is set to an Inactive Drive state (high impedance) when data scanning is not in progress.                                                                                            |

#### Table 10 • Supported BST Public Instructions

| Instruction    | IR Code<br>(IR2.IR0) | Instruction<br>Type | Description                                                                                                                                                                  |

|----------------|----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000                  | Mandatory           | Allows the external circuitry and board-level interconnections to be<br>tested by forcing a test pattern at the output pins and capturing test<br>results at the input pins. |

| SAMPLE/PRELOAD | 001                  | Mandatory           | Allows a snapshot of the signals at the device pins to be captured and examined during operation                                                                             |

| HIGH Z         | 101                  | Optional            | Tristates all I/Os to allow external signals to drive pins. See the IEEE Standard 1149.1 specification.                                                                      |

| CLAMP          | 110                  | Optional            | Allows state of signals driven from component pins to be determined<br>from the Boundary-Scan Register. See the IEEE Standard 1149.1<br>specification for details.           |

| BYPASS         | 111                  | Mandatory           | Enables the bypass register between the TDI and TDO pins. The test data passes through the selected device to adjacent devices in the test chain.                            |

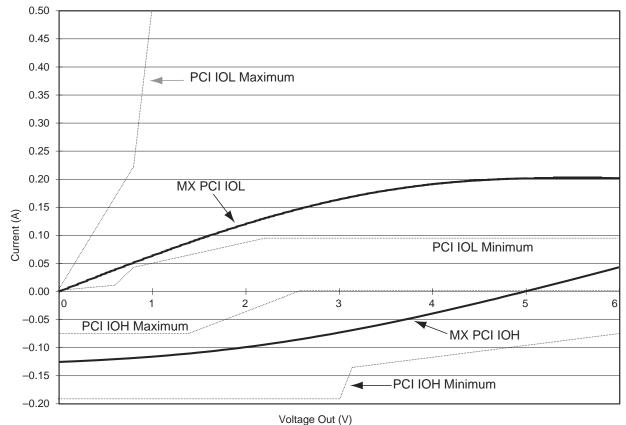

Figure 16 • Typical Output Drive Characteristics (Based Upon Measured Data)

## 3.9.4 Junction Temperature (T<sub>J</sub>)

The temperature variable in the Designer software refers to the junction temperature, not the ambient temperature. This is an important distinction because the heat generated from dynamic power consumption is usually hotter than the ambient temperature. The following equation can be used to calculate junction temperature.

Junction Temperature =  $\Delta T + T_a(1)$

EQ 4

where:

- T<sub>a</sub> = Ambient Temperature

- $\Delta T$  = Temperature gradient between junction (silicon) and ambient

- $\Delta T = \theta_{ia} * P(2)$

- P = Power

- $\theta_{ia}$  = Junction to ambient of package.  $\theta_{ia}$  numbers are located in Table 27, page 29.

## 3.9.5 Package Thermal Characteristics

The device junction-to-case thermal characteristic is  $\theta_{jc}$ , and the junction-to-ambient air characteristic is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown with two different air flow rates.

The maximum junction temperature is 150°C.

Maximum power dissipation for commercial- and industrial-grade devices is a function of  $\theta_{ia}$ .

|                    |                                           |                        | –3 S       | peed       | –2 Sp      | eed        | –1 Sj      | beed       | Std S      | Speed      | –F Sp        | beed         |          |

|--------------------|-------------------------------------------|------------------------|------------|------------|------------|------------|------------|------------|------------|------------|--------------|--------------|----------|

| Paramete           | er / Description                          |                        | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.         | Max.         | Units    |

| Logic Mo           | odule Sequential Timi                     | ng <sup>3, 4</sup>     |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up    |                        | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 0.9          |              | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data                    | a Input Hold           | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Ena                     | ble Set-Up             | 1.0        |            | 1.1        |            | 1.2        |            | 1.4        |            | 2.0          |              | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Ena                     | ble Hold               | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse W | /idth                  | 4.8        |            | 5.3        |            | 6.0        |            | 7.1        |            | 9.9          |              | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse   | Width                  | 6.2        |            | 6.9        |            | 7.9        |            | 9.2        |            | 12.9         |              | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input                     | Period                 | 9.5        |            | 10.6       |            | 12.0       |            | 14.1       |            | 19.8         |              | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Ho                     | old                    | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Se                     | et-Up                  | 0.7        |            | 0.8        |            | 0.9        |            | 1.01       |            | 1.4          |              | ns       |

| t <sub>оитн</sub>  | Output Buffer Latch H                     | Hold                   | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>outsu</sub> | Output Buffer Latch S                     | Set-Up                 | 0.7        |            | 0.8        |            | 0.89       |            | 1.01       |            | 1.4          |              | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Cloo<br>Frequency       | ck                     |            | 129        |            | 117        |            | 108        |            | 94         |              | 56           | MHz      |

| Input Mo           | dule Propagation Del                      | ays                    |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                             |                        |            | 1.5        |            | 1.6        |            | 1.9        |            | 2.2        |              | 3.1          | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                              |                        |            | 1.1        |            | 1.3        |            | 1.4        |            | 1.7        |              | 2.4          | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                               |                        |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9        |              | 4.1          | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                |                        |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9        |              | 4.1          | ns       |

| Input Mo           | dule Predicted Routir                     | ng Delays <sup>2</sup> |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>IRD1</sub>  | FO = 1 Routing<br>Delay                   |                        |            | 2.6        |            | 2.9        |            | 3.2        |            | 3.8        |              | 5.3          | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing<br>Delay                   |                        |            | 2.9        |            | 3.2        |            | 3.7        |            | 4.3        |              | 6.1          | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing<br>Delay                   |                        |            | 3.3        |            | 3.6        |            | 4.1        |            | 4.9        |              | 6.8          | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing<br>Delay                   |                        |            | 3.6        |            | 4.0        |            | 4.6        |            | 5.4        |              | 7.6          | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing<br>Delay                   |                        |            | 5.1        |            | 5.6        |            | 6.4        |            | 7.5        |              | 10.5         | ns       |

| Global C           | lock Network                              |                        |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>CKH</sub>   | Input LOW to HIGH                         | FO = 32<br>FO = 384    |            | 4.4<br>4.8 |            | 4.8<br>5.3 |            | 5.5<br>6.0 |            | 6.5<br>7.1 |              | 9.0<br>9.9   | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW                         | FO = 32<br>FO = 384    |            | 5.3<br>6.2 |            | 5.9<br>6.9 |            | 6.7<br>7.9 |            | 7.8<br>9.2 |              | 11.0<br>12.9 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH               | FO = 32<br>FO = 384    | 5.7<br>6.6 |            | 6.3<br>7.4 |            | 7.1<br>8.3 |            | 8.4<br>9.8 |            | 11.8<br>13.7 |              | ns<br>ns |

# Table 41 • A42MX16 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                               | –3 S | peed | –2 Sp | beed | –1 S | peed | Std S | peed | –F S | peed |       |

|--------------------|-----------------------------------------------|------|------|-------|------|------|------|-------|------|------|------|-------|

| Paramete           | er / Description                              | Min. | Max. | Min.  | Max. | Min. | Max. | Min.  | Max. | Min. | Max. | Units |

| Logic Mo           | odule Sequential Timing <sup>3, 4</sup>       |      |      |       |      |      |      |       |      |      |      |       |

| t <sub>CO</sub>    | Flip-Flop Clock-to-Output                     |      | 2.1  |       | 2.0  |      | 2.3  |       | 2.7  |      | 3.7  | ns    |

| t <sub>GO</sub>    | Latch Gate-to-Output                          |      | 3.4  |       | 1.9  |      | 2.1  |       | 2.5  |      | 3.4  | ns    |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Set-Up Time                 | 0.4  |      | 0.5   |      | 0.6  |      | 0.7   |      | 0.9  |      | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Hold Time                   | 0.0  |      | 0.0   |      | 0.0  |      | 0.0   |      | 0.0  |      | ns    |

| t <sub>RO</sub>    | Flip-Flop (Latch) Reset-to-Output             |      | 2.0  |       | 2.2  |      | 2.5  |       | 2.9  |      | 4.1  | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.6  |      | 0.6   |      | 0.7  |      | 0.8   |      | 1.2  |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0  |      | 0.0   |      | 0.0  |      | 0.0   |      | 0.0  |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width | 4.6  |      | 5.2   |      | 5.8  |      | 6.9   |      | 9.6  |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 6.1  |      | 6.8   |      | 7.7  |      | 9.0   |      | 12.6 |      | ns    |

| Input Mo           | dule Propagation Delays                       |      |      |       |      |      |      |       |      |      |      |       |

| t <sub>INPY</sub>  | Input Data Pad-to-Y                           |      | 1.4  |       | 1.6  |      | 1.8  |       | 2.2  |      | 3.0  | ns    |

| t <sub>INGO</sub>  | Input Latch Gate-to-Output                    |      | 1.8  |       | 1.9  |      | 2.2  |       | 2.6  |      | 3.6  | ns    |

| t <sub>INH</sub>   | Input Latch Hold                              | 0.0  |      | 0.0   |      | 0.0  |      | 0.0   |      | 0.0  |      | ns    |

| t <sub>INSU</sub>  | Input Latch Set-Up                            | 0.7  |      | 0.7   |      | 0.8  |      | 1.0   |      | 1.4  |      | ns    |

| t <sub>ILA</sub>   | Latch Active Pulse Width                      | 6.5  |      | 7.3   |      | 8.2  |      | 9.7   |      | 13.5 |      | ns    |

# Table 43 •A42MX24 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                               | –3 S | peed | –2 S | beed | –1 Sp | beed | Std S | peed | –F Sp | beed |       |

|--------------------|-----------------------------------------------|------|------|------|------|-------|------|-------|------|-------|------|-------|

| Paramet            | er / Description                              | Min. | Max. | Min. | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| Logic M            | odule Combinatorial Functions <sup>1</sup>    |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>PD</sub>    | Internal Array Module Delay                   |      | 1.3  |      | 1.5  |       | 1.7  |       | 2.0  |       | 2.7  | ns    |

| t <sub>PDD</sub>   | Internal Decode Module Delay                  |      | 1.6  |      | 1.8  |       | 2.0  |       | 2.4  |       | 3.3  | ns    |

| Logic M            | odule Predicted Routing Delays <sup>2</sup>   |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                          |      | 0.9  |      | 1.0  |       | 1.2  |       | 1.4  |       | 2.0  | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                          |      | 1.3  |      | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>RD3</sub>   | FO =3 Routing Delay                           |      | 1.6  |      | 1.8  |       | 2.0  |       | 2.4  |       | 3.4  | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |      | 2.0  |      | 2.2  |       | 2.5  |       | 2.9  |       | 4.1  | ns    |

| t <sub>RD5</sub>   | FO = 8 Routing Delay                          |      | 3.3  |      | 3.7  |       | 4.2  |       | 4.9  |       | 6.9  | ns    |

| t <sub>RDD</sub>   | Decode-to-Output Routing Delay                |      | 0.3  |      | 0.4  |       | 0.4  |       | 0.5  |       | 0.7  | ns    |

| Logic M            | odule Sequential Timing <sup>3, 4</sup>       |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>CO</sub>    | Flip-Flop Clock-to-Output                     |      | 1.3  |      | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>GO</sub>    | Latch Gate-to-Output                          |      | 1.3  |      | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Set-Up Time                 | 0.3  |      | 0.3  |      | 0.4   |      | 0.5   |      | 0.7   |      | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Hold Time                   | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>RO</sub>    | Flip-Flop (Latch) Reset-to-Output             |      | 1.6  |      | 1.7  |       | 2.0  |       | 2.3  |       | 3.2  | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.7  |      | 0.8  |      | 0.9   |      | 1.0   |      | 1.4   |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active<br>Pulse Width | 3.3  |      | 3.7  |      | 4.2   |      | 4.9   |      | 6.9   |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchronous<br>Pulse Width | 4.4  |      | 4.8  |      | 5.5   |      | 6.4   |      | 9.0   |      | ns    |

| Synchro            | nous SRAM Operations                          |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>RC</sub>    | Read Cycle Time                               | 6.8  |      | 7.5  |      | 8.5   |      | 10.0  |      | 14.0  |      | ns    |

| t <sub>WC</sub>    | Write Cycle Time                              | 6.8  |      | 7.5  |      | 8.5   |      | 10.0  |      | 14.0  |      | ns    |

| t <sub>RCKHL</sub> | Clock HIGH/LOW Time                           | 3.4  |      | 3.8  |      | 4.3   |      | 5.0   |      | 7.0   |      | ns    |

| t <sub>RCO</sub>   | Data Valid After Clock<br>HIGH/LOW            |      | 3.4  |      | 3.8  |       | 4.3  |       | 5.0  |       | 7.0  | ns    |

| t <sub>ADSU</sub>  | Address/Data Set-Up Time                      | 1.6  |      | 1.8  |      | 2.0   |      | 2.4   |      | 3.4   |      | ns    |

| Synchro            | nous SRAM Operations (continu                 | ied) |      |      |      |       |      |       |      |       |      |       |

| t <sub>ADH</sub>   | Address/Data Hold Time                        | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>RENSU</sub> | Read Enable Set-Up                            | 0.6  |      | 0.7  |      | 0.8   |      | 0.9   |      | 1.3   |      | ns    |

| t <sub>RENH</sub>  | Read Enable Hold                              | 3.4  |      | 3.8  |      | 4.3   |      | 5.0   |      | 7.0   |      | ns    |

| t <sub>WENSU</sub> | Write Enable Set-Up                           | 2.7  |      | 3.0  |      | 3.4   |      | 4.0   |      | 5.6   |      | ns    |

| t <sub>WENH</sub>  | Write Enable Hold                             | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

|                    | Block Enable Set-Up                           | 2.8  |      | 3.1  |      | 3.5   |      | 4.1   |      | 5.7   |      | ns    |

| t <sub>BENS</sub>  | Diotit Litable Oct Op                         |      |      |      |      |       |      |       |      |       |      |       |

# Table 44 •A42MX36 Timing Characteristics (Nominal 5.0 V Operation)(Worst-Case Commercial Conditions,<br/>VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                   |                                                 | –3 S | peed | –2 S | peed | –1 S | peed | Std S | Speed | –F S | peed |       |

|-------------------|-------------------------------------------------|------|------|------|------|------|------|-------|-------|------|------|-------|

| Parame            | eter / Description                              | Min. | Max. | Min. | Max. | Min. | Max. | Min.  | Max.  | Min. | Max. | Units |

| t <sub>ACO</sub>  | Array Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O |      | 10.9 |      | 12.1 |      | 13.7 |       | 16.1  |      | 22.5 | ns    |

| d <sub>TLH</sub>  | Capacitive Loading, LOW to HIGH                 |      | 0.10 |      | 0.11 |      | 0.12 |       | 0.14  |      | 0.20 | ns/pF |

| d <sub>THL</sub>  | Capacitive Loading, HIGH to LOW                 |      | 0.10 |      | 0.11 |      | 0.12 |       | 0.14  |      | 0.20 | ns/pF |

| CMOS              | Output Module Timing <sup>5</sup>               |      |      |      |      |      |      |       |       |      |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                                |      | 4.9  |      | 5.5  |      | 6.2  |       | 7.3   |      | 10.3 | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                                 |      | 3.4  |      | 3.8  |      | 4.3  |       | 5.1   |      | 7.1  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH                            |      | 3.7  |      | 4.1  |      | 4.7  |       | 5.5   |      | 7.7  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW                             |      | 4.1  |      | 4.6  |      | 5.2  |       | 6.1   |      | 8.5  | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z                            |      | 7.4  |      | 8.2  |      | 9.3  |       | 10.9  |      | 15.3 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                             |      | 6.9  |      | 7.6  |      | 8.7  |       | 10.2  |      | 14.3 | ns    |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                   |      | 7.0  |      | 7.8  |      | 8.9  |       | 10.4  |      | 14.6 | ns    |

| t <sub>GHL</sub>  | G-to-Pad LOW                                    |      | 7.0  |      | 7.8  |      | 8.9  |       | 10.4  |      | 14.6 | ns    |

| t <sub>LSU</sub>  | I/O Latch Set-Up                                | 0.7  |      | 0.7  |      | 0.8  |      | 1.0   |       | 1.4  |      | ns    |

| t <sub>LH</sub>   | I/O Latch Hold                                  | 0.0  |      | 0.0  |      | 0.0  |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O   |      | 7.9  |      | 8.8  |      | 10.0 |       | 11.8  |      | 16.5 | ns    |

# Table 45 • A42MX36 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

1. For dual-module macros, use  $t_{PD1} + t_{RD1} + t_{PDn}$ ,  $t_{CO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

4. Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

# 3.12 Pin Descriptions

This section lists the pin descriptions for 40MX and 42MX series FPGAs.

#### CLK/A/B, I/O Global Clock

Clock inputs for clock distribution networks. CLK is for 40MX while CLKA and CLKB are for 42MX devices. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

### DCLK, I/ODiagnostic Clock

Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### **GND**, Ground

Input LOW supply voltage.

#### I/O, Input/Output

| PQ144      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX09 Function |  |

| 80         | GNDI             |  |

| 81         | NC               |  |

| 82         | I/O              |  |

| 83         | I/O              |  |

| 84         | I/O              |  |

| 85         | I/O              |  |

| 86         | I/O              |  |

| 87         | I/O              |  |

| 88         | VKS              |  |

| 89         | VPP              |  |

| 90         | VCC              |  |

| 91         | VCCI             |  |

| 92         | NC               |  |

| 93         | VSV              |  |

| 94         | I/O              |  |

| 95         | I/O              |  |

| 96         | I/O              |  |

| 97         | I/O              |  |

| 98         | I/O              |  |

| 99         | I/O              |  |

| 100        | GND              |  |

| 101        | GNDI             |  |

| 102        | NC               |  |

| 103        | I/O              |  |

| 104        | I/O              |  |

| 105        | I/O              |  |

| 106        | I/O              |  |

| 107        | I/O              |  |

| 108        | I/O              |  |

| 109        | I/O              |  |

| 110        | SDI              |  |

| 111        | I/O              |  |

| 112        | I/O              |  |

| 113        | I/O              |  |

| 114        | I/O              |  |

| 115        | I/O              |  |

| 116        | GNDQ             |  |

#### Table 51 • PQ144

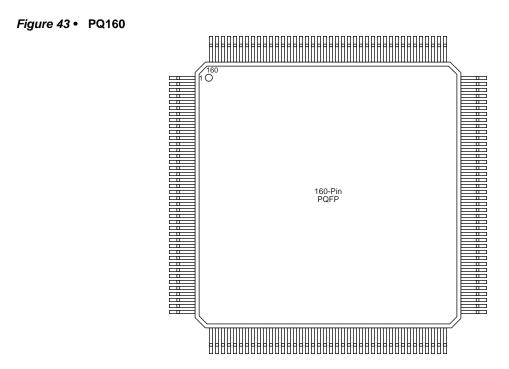

### Table 52 • PQ160

| PQ160      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 1          | I/O              | I/O              | I/O              |

| 2          | DCLK, I/O        | DCLK, I/O        | DCLK, I/O        |

| 3          | NC               | I/O              | I/O              |

| 4          | I/O              | I/O              | WD, I/O          |

| 5          | I/O              | I/O              | WD, I/O          |

| 6          | NC               | VCCI             | VCCI             |

| 7          | I/O              | I/O              | I/O              |

| 8          | I/O              | I/O              | I/O              |

| 9          | I/O              | I/O              | I/O              |

| 10         | NC               | I/O              | I/O              |

| 11         | GND              | GND              | GND              |

| 12         | NC               | I/O              | I/O              |

| 13         | I/O              | I/O              | WD, I/O          |

| 14         | I/O              | I/O              | WD, I/O          |

| 15         | I/O              | I/O              | I/O              |

| 16         | PRB, I/O         | PRB, I/O         | PRB, I/O         |

| 17         | I/O              | I/O              | I/O              |

| 18         | CLKB, I/O        | CLKB, I/O        | CLKB, I/O        |

| 19         | I/O              | I/O              | I/O              |

| 20         | VCCA             | VCCA             | VCCA             |

#### Table 52 • PQ160

| PQ160      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 58         | VCCI             | VCCI             | VCCI             |

| 59         | GND              | GND              | GND              |

| 60         | VCCA             | VCCA             | VCCA             |

| 61         | LP               | LP               | LP               |

| 62         | I/O              | I/O              | TCK, I/O         |

| 63         | I/O              | I/O              | I/O              |

| 64         | GND              | GND              | GND              |

| 65         | I/O              | I/O              | I/O              |

| 66         | I/O              | I/O              | I/O              |

| 67         | I/O              | I/O              | I/O              |

| 68         | I/O              | I/O              | I/O              |

| 69         | GND              | GND              | GND              |

| 70         | NC               | I/O              | I/O              |

| 71         | I/O              | I/O              | I/O              |

| 72         | I/O              | I/O              | I/O              |

| 73         | I/O              | I/O              | I/O              |

| 74         | I/O              | I/O              | I/O              |

| 75         | NC               | I/O              | I/O              |

| 76         | I/O              | I/O              | I/O              |

| 77         | NC               | I/O              | I/O              |

| 78         | I/O              | I/O              | I/O              |

| 79         | NC               | I/O              | I/O              |

| 30         | GND              | GND              | GND              |

| 31         | I/O              | I/O              | I/O              |

| 32         | SDO, I/O         | SDO, I/O         | SDO, TDO, I/O    |

| 33         | I/O              | I/O              | WD, I/O          |

| 34         | I/O              | I/O              | WD, I/O          |

| 35         | I/O              | I/O              | I/O              |

| 36         | NC               | VCCI             | VCCI             |

| 37         | I/O              | I/O              | I/O              |

| 38         | I/O              | I/O              | WD, I/O          |

| 39         | GND              | GND              | GND              |

| 90         | NC               | I/O              | I/O              |

| 91         | I/O              | I/O              | I/O              |

| 92         | I/O              | I/O              | I/O              |

| 93         | I/O              | I/O              | I/O              |

| 94         | I/O              | I/O              | I/O              |

### Table 57 • TQ176

| TQ176      |                  |                  |                  |  |

|------------|------------------|------------------|------------------|--|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |  |

| 47         | I/O              | I/O              | TDI, I/O         |  |

| 48         | I/O              | I/O              | I/O              |  |

| 49         | I/O              | I/O              | WD, I/O          |  |

| 50         | I/O              | I/O              | WD, I/O          |  |

| 51         | I/O              | I/O              | I/O              |  |

| 52         | NC               | VCCI             | VCCI             |  |

| 53         | I/O              | I/O              | I/O              |  |

| 54         | NC               | I/O              | I/O              |  |

| 55         | NC               | I/O              | WD, I/O          |  |

| 56         | I/O              | I/O              | WD, I/O          |  |

| 57         | NC               | NC               | I/O              |  |

| 58         | I/O              | I/O              | I/O              |  |

| 59         | I/O              | I/O              | WD, I/O          |  |

| 60         | I/O              | I/O              | WD, I/O          |  |

| 61         | NC               | I/O              | I/O              |  |

| 62         | I/O              | I/O              | I/O              |  |

| 63         | I/O              | I/O              | I/O              |  |

| 64         | NC               | I/O              | I/O              |  |

| 65         | I/O              | I/O              | I/O              |  |

| 66         | NC               | I/O              | I/O              |  |

| 67         | GND              | GND              | GND              |  |

| 68         | VCCA             | VCCA             | VCCA             |  |

| 69         | I/O              | I/O              | WD, I/O          |  |

| 70         | I/O              | I/O              | WD, I/O          |  |

| 71         | I/O              | I/O              | I/O              |  |

| 72         | I/O              | I/O              | I/O              |  |

| 73         | I/O              | I/O              | I/O              |  |

| 74         | NC               | I/O              | I/O              |  |

| 75         | I/O              | I/O              | I/O              |  |

| 76         | I/O              | I/O              | I/O              |  |

| 77         | NC               | NC               | WD, I/O          |  |

| 78         | NC               | I/O              | WD, I/O          |  |

| 79         | I/O              | I/O              | I/O              |  |

| 80         | NC               | I/O              | I/O              |  |

| 81         | I/O              | I/O              | I/O              |  |

| 82         | NC               | VCCI             | VCCI             |  |

| 83         | I/O              | I/O              | I/O              |  |

### Table 57 • TQ176

| TQ176      |                  |                  |                  |  |

|------------|------------------|------------------|------------------|--|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |  |

| 84         | I/O              | I/O              | WD, I/O          |  |

| 85         | I/O              | I/O              | WD, I/O          |  |

| 86         | NC               | I/O              | I/O              |  |

| 87         | SDO, I/O         | SDO, I/O         | SDO, TDO, I/O    |  |

| 88         | I/O              | I/O              | I/O              |  |

| 39         | GND              | GND              | GND              |  |

| 90         | I/O              | I/O              | I/O              |  |

| 91         | I/O              | I/O              | I/O              |  |

| 92         | I/O              | I/O              | I/O              |  |

| 93         | I/O              | I/O              | I/O              |  |

| 94         | I/O              | I/O              | I/O              |  |

| 95         | I/O              | I/O              | I/O              |  |

| 96         | NC               | I/O              | I/O              |  |

| 97         | NC               | I/O              | I/O              |  |

| 98         | I/O              | I/O              | I/O              |  |

| 99         | I/O              | I/O              | I/O              |  |

| 100        | I/O              | I/O              | I/O              |  |

| 101        | NC               | NC               | I/O              |  |

| 102        | I/O              | I/O              | I/O              |  |

| 103        | NC               | I/O              | I/O              |  |

| 104        | I/O              | I/O              | I/O              |  |

| 105        | I/O              | I/O              | I/O              |  |

| 106        | GND              | GND              | GND              |  |

| 107        | NC               | I/O              | I/O              |  |

| 108        | NC               | I/O              | TCK, I/O         |  |

| 109        | LP               | LP               | LP               |  |

| 110        | VCCA             | VCCA             | VCCA             |  |

| 111        | GND              | GND              | GND              |  |

| 112        | VCCI             | VCCI             | VCCI             |  |

| 113        | VCCA             | VCCA             | VCCA             |  |

| 114        | NC               | I/O              | I/O              |  |

| 115        | NC               | I/O              | I/O              |  |

| 116        | NC               | VCCA             | VCCA             |  |

| 117        | I/O              | I/O              | I/O              |  |

| 118        | I/O              | I/O              | I/O              |  |

| 119        | I/O              | I/O              | I/O              |  |

| 120        | I/O              | I/O              | I/O              |  |

| Table | 57• | TQ176 |

|-------|-----|-------|

|       |     |       |

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 158        | CLKB, I/O        | CLKB, I/O        | CLKB, I/O        |

| 159        | I/O              | I/O              | I/O              |

| 160        | PRB, I/O         | PRB, I/O         | PRB, I/O         |

| 161        | NC               | I/O              | WD, I/O          |

| 162        | I/O              | I/O              | WD, I/O          |

| 163        | I/O              | I/O              | I/O              |

| 164        | I/O              | I/O              | I/O              |

| 165        | NC               | NC               | WD, I/O          |

| 166        | NC               | I/O              | WD, I/O          |

| 167        | I/O              | I/O              | I/O              |

| 168        | NC               | I/O              | I/O              |

| 169        | I/O              | I/O              | I/O              |

| 170        | NC               | VCCI             | VCCI             |

| 171        | I/O              | I/O              | WD, I/O          |

| 172        | I/O              | I/O              | WD, I/O          |

| 173        | NC               | I/O              | I/O              |

| 174        | I/O              | I/O              | I/O              |

| 175        | DCLK, I/O        | DCLK, I/O        | DCLK, I/O        |

| 176        | I/O              | I/O              | I/O              |

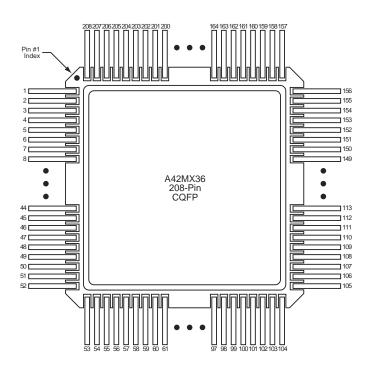

Figure 49 • CQ208

| CQ208      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 185        | I/O              |

| 186        | CLKB, I/O        |

| 187        | I/O              |

| 188        | PRB, I/O         |

| 189        | I/O              |

| 190        | WD, I/O          |

| 191        | WD, I/O          |

| 192        | I/O              |

| 193        | I/O              |

| 194        | WD, I/O          |

| 195        | WD, I/O          |

| 196        | QCLKC, I/O       |

| 197        | I/O              |

| 198        | I/O              |

| 199        | I/O              |

| 200        | I/O              |

| 201        | I/O              |

| 202        | VCCI             |

| 203        | WD, I/O          |

| 204        | WD, I/O          |

| 205        | I/O              |

| 206        | I/O              |

| 207        | DCLK, I/O        |

| 208        | I/O              |

|            |                  |

| Table 60 • BG272 |                  |  |

|------------------|------------------|--|

| BG272            |                  |  |

| Pin Number       | A42MX36 Function |  |

| A6               | I/O              |  |

| A7               | WD, I/O          |  |

| A8               | WD, I/O          |  |

| A9               | I/O              |  |

| A10              | I/O              |  |

| A11              | CLKA             |  |

| A12              | I/O              |  |

| A13              | I/O              |  |

| A14              | I/O              |  |

| A15              | I/O              |  |

| A16              | WD, I/O          |  |

| A17              | I/O              |  |

| A18              | I/O              |  |

| A19              | GND              |  |

| A20              | GND              |  |

| B1               | GND              |  |

| B2               | GND              |  |

| B3               | DCLK, I/O        |  |

| B4               | I/O              |  |

| B5               | I/O              |  |

| B6               | I/O              |  |

| B7               | WD, I/O          |  |

| B8               | I/O              |  |

| B9               | PRB, I/O         |  |

| B10              | I/O              |  |

| B11              | I/O              |  |

| B12              | WD, I/O          |  |

| B13              | I/O              |  |

| B14              | I/O              |  |

| B15              | WD, I/O          |  |

| B16              | I/O              |  |

| B17              | WD, I/O          |  |

| B18              | I/O              |  |

| B19              | GND              |  |

| B20              | GND              |  |

| C1               | I/O              |  |

| C2               | MODE             |  |

| Table 60 • BG272 |                    |  |  |  |

|------------------|--------------------|--|--|--|

| BG272            |                    |  |  |  |

| Pin Numbe        | r A42MX36 Function |  |  |  |

| J9               | GND                |  |  |  |

| J10              | GND                |  |  |  |

| J11              | GND                |  |  |  |

| J12              | GND                |  |  |  |

| J17              | VCCA               |  |  |  |

| J18              | I/O                |  |  |  |

| J19              | I/O                |  |  |  |

| J20              | I/O                |  |  |  |

| K1               | I/O                |  |  |  |

| K2               | I/O                |  |  |  |

| K3               | I/O                |  |  |  |

| K4               | VCCI               |  |  |  |

| K9               | GND                |  |  |  |

| K10              | GND                |  |  |  |

| K11              | GND                |  |  |  |

| K12              | GND                |  |  |  |

| K17              | I/O                |  |  |  |

| K18              | VCCA               |  |  |  |

| K19              | VCCA               |  |  |  |

| K20              | LP                 |  |  |  |

| L1               | I/O                |  |  |  |

| L2               | I/O                |  |  |  |

| L3               | VCCA               |  |  |  |

| L4               | VCCA               |  |  |  |

| L9               | GND                |  |  |  |

| L10              | GND                |  |  |  |

| L11              | GND                |  |  |  |

| L12              | GND                |  |  |  |

| L17              | VCCI               |  |  |  |

| L18              | I/O                |  |  |  |

| L19              | I/O                |  |  |  |

| L20              | TCK, I/O           |  |  |  |

| M1               | I/O                |  |  |  |

| M2               | I/O                |  |  |  |

| M3               | I/O                |  |  |  |

| M4               | VCCI               |  |  |  |

| M9               | GND                |  |  |  |