Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

E·XFI

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Obsolete                                                                  |

| Number of LABs/CLBs            | ·                                                                         |

| Number of Logic Elements/Cells | · ·                                                                       |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 125                                                                       |

| Number of Gates                | 24000                                                                     |

| Voltage - Supply               | 3V ~ 3.6V, 4.5V ~ 5.5V                                                    |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                         |

| Package / Case                 | 160-BQFP                                                                  |

| Supplier Device Package        | 160-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx16-3pq160i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

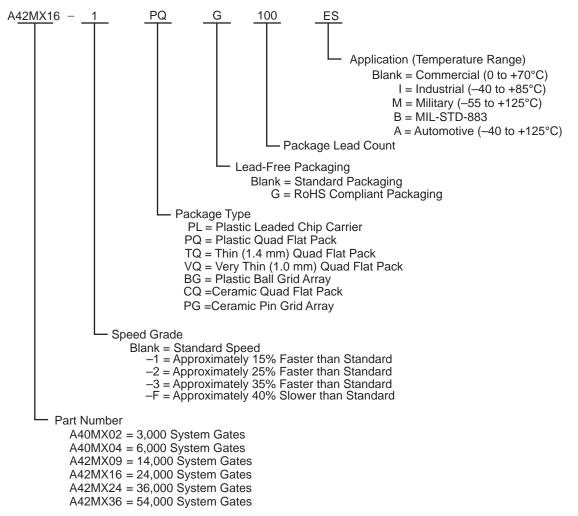

## 2.3 Ordering Information

The following figure shows ordering information.All the following tables show plastic and ceramic device resources, temperature and speed grade offerings.

#### Figure 1 • Ordering Information

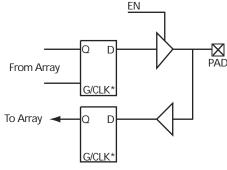

Designer software development tools provide a design library of I/O macro functions that can implement all I/O configurations supported by the MX FPGAs.

#### Figure 10 • 42MX I/O Module

Note: \*Can be configured as a Latch or D Flip-Flop (Using C-Module)

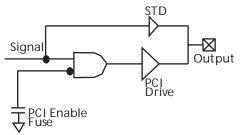

#### Figure 11 • PCI Output Structure of A42MX24 and A42MX36 Devices

## 3.3 Other Architectural Features

The following sections cover other architectural features of 40MX and 42MX FPGAs.

### 3.3.1 Performance

MX devices can operate with internal clock frequencies of 250 MHz, enabling fast execution of complex logic functions. MX devices are live on power-up and do not require auxiliary configuration devices and thus are an optimal platform to integrate the functionality contained in multiple programmable logic devices. In addition, designs that previously would have required a gate array to meet performance can be integrated into an MX device with improvements in cost and time-to-market. Using timing-driven place-and-route (TDPR) tools, designers can achieve highly deterministic device performance.

### 3.3.2 User Security

Microsemi FuseLock provides robust security against design theft. Special security fuses are hidden in the fabric of the device and protect against unauthorized users attempting to access the programming and/or probe interfaces. It is virtually impossible to identify or bypass these fuses without damaging the device, making Microsemi antifuse FPGAs protected with the highest level of security available from both invasive and noninvasive attacks.

Special security fuses in 40MX devices include the Probe Fuse and Program Fuse. The former disables the probing circuitry while the latter prohibits further programming of all fuses, including the Probe Fuse. In 42MX devices, there is the Security Fuse which, when programmed, both disables the probing circuitry and prohibits further programming of the device.

### 3.3.3 Programming

Device programming is supported through the Silicon Sculptor series of programmers. Silicon Sculptor is a compact, robust, single-site and multi-site device programmer for the PC. With standalone software, Silicon Sculptor is designed to allow concurrent programming of multiple units from the same PC.

| Device Type | r1 routed_Clk1 | r2 routed_Clk2 |

|-------------|----------------|----------------|

| A40MX02     | 41.4           | N/A            |

| A40MX04     | 68.6           | N/A            |

| A42MX09     | 118            | 118            |

| A42MX16     | 165            | 165            |

| A42MX24     | 185            | 185            |

| A42MX36     | 220            | 220            |

Fixed Capacitance Values for MX FPGAs (pF)

$f_{a2}$  = Average second routed array clock rate in MHz)

Table 7 •

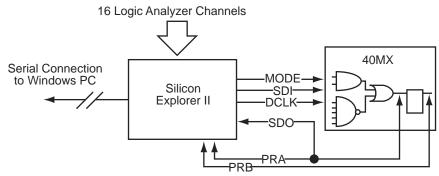

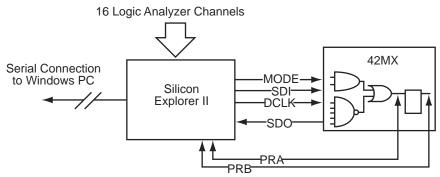

## 3.4.6 Test Circuitry and Silicon Explorer II Probe

MX devices contain probing circuitry that provides built-in access to every node in a design, via the use of Silicon Explorer II. Silicon Explorer II is an integrated hardware and software solution that, in conjunction with the Designer software, allow users to examine any of the internal nets of the device while it is operating in a prototyping or a production system. The user can probe into an MX device without changing the placement and routing of the design and without using any additional resources. Silicon Explorer II's noninvasive method does not alter timing or loading effects, thus shortening the debug cycle and providing a true representation of the device under actual functional situations.

Silicon Explorer II samples data at 100 MHz (asynchronous) or 66 MHz (synchronous). Silicon Explorer II attaches to a PC's standard COM port, turning the PC into a fully functional 18-channel logic analyzer. Silicon Explorer II allows designers to complete the design verification process at their desks and reduces verification time from several hours per cycle to a few seconds.

Silicon Explorer II is used to control the MODE, DCLK, SDI and SDO pins in MX devices to select the desired nets for debugging. The user simply assigns the selected internal nets in the Silicon Explorer II software to the PRA/PRB output pins for observation. Probing functionality is activated when the MODE pin is held HIGH.

Figure 12, page 16 illustrates the interconnection between Silicon Explorer II and 40MX devices, while Figure 13, page 17 illustrates the interconnection between Silicon Explorer II and 42MX devices

To allow for probing capabilities, the security fuses must not be programmed. (See User Security, page 12 for the security fuses of 40MX and 42MX devices). Table 8, page 17 summarizes the possible device configurations for probing.

PRA and PRB pins are dual-purpose pins. When the "Reserve Probe Pin" is checked in the Designer software, PRA and PRB pins are reserved as dedicated outputs for probing. If PRA and PRB pins are required as user I/Os to achieve successful layout and "Reserve Probe Pin" is checked, the layout tool will override the option and place user I/Os on PRA and PRB pins.

#### Figure 12 • Silicon Explorer II Setup with 40MX

#### Figure 13 • Silicon Explorer II Setup with 42MX

#### Table 8 • Device Configuration Options for Probe Capability

| Security Fuse(s) Programmed | Mode | PRA, PRB <sup>1</sup>  | SDI, SDO, DCLK <sup>1</sup> |

|-----------------------------|------|------------------------|-----------------------------|

| No                          | LOW  | User I/Os <sup>2</sup> | User I/Os <sup>2</sup>      |

| No                          | HIGH | Probe Circuit Outputs  | Probe Circuit Inputs        |

| Yes                         | _    | Probe Circuit Secured  | Probe Circuit Secured       |

1. Avoid using SDI, SDO, DCLK, PRA and PRB pins as input or bidirectional ports. Since these pins are active during probing, input signals will not pass through these pins and may cause contention.

2. If no user signal is assigned to these pins, they will behave as unused I/Os in this mode. See the Pin Descriptions, page 83 for information on unused I/O pins

## 3.4.7 Design Consideration

It is recommended to use a series  $70\Omega$  termination resistor on every probe connector (SDI, SDO, MODE, DCLK, PRA and PRB). The 70  $\Omega$  series termination is used to prevent data transmission corruption during probing and reading back the checksum.

## 3.4.8 IEEE Standard 1149.1 Boundary Scan Test (BST) Circuitry

42MX24 and 42MX36 devices are compatible with IEEE Standard 1149.1 (informally known as Joint Testing Action Group Standard or JTAG), which defines a set of hardware architecture and mechanisms for cost-effective board-level testing. The basic MX boundary-scan logic circuit is composed of the TAP (test access port), TAP controller, test data registers and instruction register (Figure 14, page 18). This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD and BYPASS) and some optional instructions. Table 9, page 18 describes the ports that control JTAG testing, while Table 10, page 18 describes the test instructions supported by these MX devices.

Each test section is accessed through the TAP, which has four associated pins: TCK (test clock input), TDI and TDO (test data input and output), and TMS (test mode selector).

The TAP controller is a four-bit state machine. The '1's and '0's represent the values that must be present at TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain high for five TCK cycles.

42MX24 and 42MX36 devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register with four fields (lowest significant byte (LSB), ID number, part number and version). The boundary-scan register observes and controls the state of each I/O pin.

#### Table 23 • DC Specification (5.0 V PCI Signaling)<sup>1</sup>

|                  |                       |           | PCI  |      | MX   |                     |       |

|------------------|-----------------------|-----------|------|------|------|---------------------|-------|

| Symbol           | Parameter             | Condition | Min. | Max. | Min. | Max.                | Units |

| C <sub>IN</sub>  | Input Pin Capacitance |           |      | 10   | —    | 10                  | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance   |           | 5    | 12   | —    | 10                  | pF    |

| L <sub>PIN</sub> | Pin Inductance        |           |      | 20   | —    | < 8 nH <sup>4</sup> | nH    |

1. PCI Local Bus Specification, Version 2.1, Section 4.2.1.1.

2. Maximum rating for VCCI –0.5 V to 7.0 V  $\,$

3. VIH(Min) is 2.4V for A42MX36 family. This applies only to VCCI of 5V and is not applicable to VCCI of 3.3V.

4. Dependent upon the chosen package. PCI recommends QFP and BGA packaging to reduce pin inductance and capacitance.

#### Table 24 • AC Specifications (5.0V PCI Signaling)\*

| -        |                       |                     | PCI                   |      | MX   | МХ   |       |  |

|----------|-----------------------|---------------------|-----------------------|------|------|------|-------|--|

| Symbol   | Parameter             | Condition           | Min.                  | Max. | Min. | Max. | Units |  |

| ICL      | Low Clamp Current     | $-5 < VIN \le -1$   | -25 + (VIN +1) /0.015 |      | -60  | -10  | mA    |  |

| Slew (r) | Output Rise Slew Rate | 0.4 V to 2.4 V load | 1                     | 5    | 1.8  | 2.8  | V/ns  |  |

| Slew (f) | Output Fall Slew Rate | 2.4 V to 0.4 V load | 1                     | 5    | 2.8  | 4.3  | V/ns  |  |

Note: \*PCI Local Bus Specification, Version 2.1, Section 4.2.1.2.

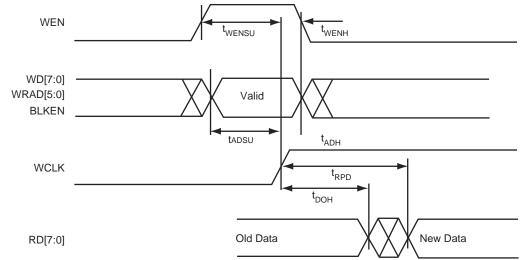

#### Figure 33 • 42MX SRAM Asynchronous Read Operation—Type 2 (Write Address Controlled)

## 3.10.7 Predictable Performance: Tight Delay Distributions

Propagation delay between logic modules depends on the resistive and capacitive loading of the routing tracks, the interconnect elements, and the module inputs being driven. Propagation delay increases as the length of routing tracks, the number of interconnect elements, or the number of inputs increases.

From a design perspective, the propagation delay can be statistically correlated or modeled by the fanout (number of loads) driven by a module. Higher fanout usually requires some paths to have longer routing tracks.

The MX FPGAs deliver a tight fanout delay distribution, which is achieved in two ways: by decreasing the delay of the interconnect elements and by decreasing the number of interconnect elements per path.

Microsemi's patented antifuse offers a very low resistive/capacitive interconnect. The antifuses, fabricated in 0.45  $\mu$ m lithography, offer nominal levels of 100  $\Omega$  resistance and 7.0 fF capacitance per antifuse.

MX fanout distribution is also tight due to the low number of antifuses required for each interconnect path. The proprietary architecture limits the number of antifuses per path to a maximum of four, with 90 percent of interconnects using only two antifuses.

## 3.11 Timing Characteristics

Device timing characteristics fall into three categories: family-dependent, device-dependent, and designdependent. The input and output buffer characteristics are common to all MX devices. Internal routing delays are device-dependent; actual delays are not determined until after place-and-route of the user's design is complete. Delay values may then be determined by using the Designer software utility or by performing simulation with post-layout delays.

## 3.11.1 Critical Nets and Typical Nets

Propagation delays are expressed only for typical nets, which are used for initial design performance evaluation. Critical net delays can then be applied to the most timing critical paths. Critical nets are determined by net property assignment in Microsemi's Designer software prior to placement and routing. Up to 6% of the nets in a design may be designated as critical.

## 3.11.2 Long Tracks

Some nets in the design use long tracks, which are special routing resources that span multiple rows, columns, or modules. Long tracks employ three and sometimes four antifuse connections, which increase capacitance and resistance, resulting in longer net delays for macros connected to long tracks. Typically, up to 6 percent of nets in a fully utilized device require long tracks. Long tracks add

|                   |                     | –3 Sp | -3 Speed |      | -2 Speed -1 S |      | -1 Speed |      | Std Speed |      | beed |       |

|-------------------|---------------------|-------|----------|------|---------------|------|----------|------|-----------|------|------|-------|

| Param             | eter / Description  | Min.  | Max.     | Min. | Max.          | Min. | Max.     | Min. | Max.      | Min. | Max. | Units |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z |       | 5.9      |      | 6.8           |      | 7.7      |      | 9.0       |      | 12.6 | ns    |

| d <sub>TLH</sub>  | Delta LOW to HIGH   |       | 0.02     |      | 0.02          |      | 0.03     |      | 0.03      |      | 0.04 | ns/pF |

| d <sub>THL</sub>  | Delta HIGH to LOW   |       | 0.03     |      | 0.03          |      | 0.03     |      | 0.04      |      | 0.06 | ns/pF |

# Table 36 •A40MX04 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C)

|                   |                                   | –3 Sp | eed  | –2 Sp | beed | –1 S | peed | Std S | Speed | –F S | peed |       |

|-------------------|-----------------------------------|-------|------|-------|------|------|------|-------|-------|------|------|-------|

| Parame            | eter / Description                | Min.  | Max. | Min.  | Max. | Min. | Max. | Min.  | Max.  | Min. | Max. | Units |

| CMOS              | Output Module Timing <sup>1</sup> |       |      |       |      |      |      |       |       |      |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                  |       | 3.9  |       | 4.5  |      | 5.1  |       | 6.05  |      | 8.5  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                   |       | 3.4  |       | 3.9  |      | 4.4  |       | 5.2   |      | 7.3  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH              |       | 3.4  |       | 3.9  |      | 4.4  |       | 5.2   |      | 7.3  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW               |       | 4.9  |       | 5.6  |      | 6.4  |       | 7.5   |      | 10.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z              |       | 7.9  |       | 9.1  |      | 10.4 |       | 12.2  |      | 17.0 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z               |       | 5.9  |       | 6.8  |      | 7.7  |       | 9.0   |      | 12.6 | ns    |

| d <sub>TLH</sub>  | Delta LOW to HIGH                 |       | 0.03 |       | 0.04 |      | 0.04 |       | 0.05  |      | 0.07 | ns/pF |

| $d_{THL}$         | Delta HIGH to LOW                 |       | 0.02 |       | 0.02 |      | 0.03 |       | 0.03  |      | 0.04 | ns/pF |

## Table 36 • A40MX04 Timing Characteristics (Nominal 5.0 V Operation) (continued)(Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C)

1. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

2. Set-up times assume fanout of 3. Further testing information can be obtained from the Timer utility

3. The hold time for the DFME1A macro may be greater than 0 ns. Use the Timer utility from the Designer software to check the hold time for this macro.

4. Delays based on 35 pF loading

## Table 37 •A40MX04 Timing Characteristics (Nominal 3.3 V Operation) (Worst-Case Commercial Conditions,<br/>VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                              |                                             | –3 S | peed | –2 S | peed | –1 Sp | beed | Std S | Speed | –F S | peed |       |

|------------------------------|---------------------------------------------|------|------|------|------|-------|------|-------|-------|------|------|-------|

| Paramet                      | er / Description                            | Min. | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| Logic Mo                     | odule Propagation Delays                    |      |      |      |      |       |      |       |       |      |      |       |

| t <sub>PD1</sub>             | Single Module                               |      | 1.7  |      | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>PD2</sub>             | Dual-Module Macros                          |      | 3.7  |      | 4.3  |       | 4.9  |       | 5.7   |      | 8.0  | ns    |

| t <sub>CO</sub>              | Sequential Clock-to-Q                       |      | 1.7  |      | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>GO</sub>              | Latch G-to-Q                                |      | 1.7  |      | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>RS</sub>              | Flip-Flop (Latch) Reset-to-Q                |      | 1.7  |      | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| Logic Mo                     | odule Predicted Routing Delays <sup>1</sup> |      |      |      |      |       |      |       |       |      |      |       |

| t <sub>RD1</sub>             | FO = 1 Routing Delay                        |      | 1.9  |      | 2.2  |       | 2.5  |       | 3.0   |      | 4.2  | ns    |

| t <sub>RD2</sub>             | FO = 2 Routing Delay                        |      | 2.7  |      | 3.1  |       | 3.5  |       | 4.1   |      | 5.7  | ns    |

| t <sub>RD3</sub>             | FO = 3 Routing Delay                        |      | 3.4  |      | 3.9  |       | 4.4  |       | 5.2   |      | 7.3  | ns    |

| t <sub>RD4</sub>             | FO = 4 Routing Delay                        |      | 4.1  |      | 4.8  |       | 5.4  |       | 6.3   |      | 8.9  | ns    |

| t <sub>RD8</sub>             | FO = 8 Routing Delay                        |      | 7.1  |      | 8.1  |       | 9.2  |       | 10.9  |      | 15.2 | ns    |

| Logic Mo                     | odule Sequential Timing <sup>2</sup>        |      |      |      |      |       |      |       |       |      |      |       |

| t <sub>SUD</sub>             | Flip-Flop (Latch)<br>Data Input Set-Up      | 4.3  |      | 5.0  |      | 5.6   |      | 6.6   |       | 9.2  |      | ns    |

| t <sub>HD</sub> <sup>3</sup> | Flip-Flop (Latch) Data Input Hold           | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>SUENA</sub>           | Flip-Flop (Latch) Enable Set-Up             | 4.3  |      | 5.0  |      | 5.6   |      | 6.6   |       | 9.2  |      | ns    |

| t <sub>HENA</sub>            | Flip-Flop (Latch) Enable Hold               | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

|                    |                                           |                        | –3 S       | peed       | –2 Sp      | eed        | –1 Sj      | beed       | Std S      | Speed      | –F Sp        | beed         |          |

|--------------------|-------------------------------------------|------------------------|------------|------------|------------|------------|------------|------------|------------|------------|--------------|--------------|----------|

| Paramete           | er / Description                          |                        | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.         | Max.         | Units    |

| Logic Mo           | odule Sequential Timi                     | ng <sup>3, 4</sup>     |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up    |                        | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 0.9          |              | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data                    | a Input Hold           | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Ena                     | ble Set-Up             | 1.0        |            | 1.1        |            | 1.2        |            | 1.4        |            | 2.0          |              | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Ena                     | ble Hold               | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse W | /idth                  | 4.8        |            | 5.3        |            | 6.0        |            | 7.1        |            | 9.9          |              | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse   | Width                  | 6.2        |            | 6.9        |            | 7.9        |            | 9.2        |            | 12.9         |              | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input                     | Period                 | 9.5        |            | 10.6       |            | 12.0       |            | 14.1       |            | 19.8         |              | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Ho                     | old                    | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Se                     | et-Up                  | 0.7        |            | 0.8        |            | 0.9        |            | 1.01       |            | 1.4          |              | ns       |

| t <sub>оитн</sub>  | Output Buffer Latch H                     | Hold                   | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>outsu</sub> | Output Buffer Latch S                     | Set-Up                 | 0.7        |            | 0.8        |            | 0.89       |            | 1.01       |            | 1.4          |              | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Cloo<br>Frequency       | ck                     |            | 129        |            | 117        |            | 108        |            | 94         |              | 56           | MHz      |

| Input Mo           | dule Propagation Del                      | ays                    |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                             |                        |            | 1.5        |            | 1.6        |            | 1.9        |            | 2.2        |              | 3.1          | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                              |                        |            | 1.1        |            | 1.3        |            | 1.4        |            | 1.7        |              | 2.4          | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                               |                        |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9        |              | 4.1          | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                |                        |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9        |              | 4.1          | ns       |

| Input Mo           | dule Predicted Routir                     | ng Delays <sup>2</sup> |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>IRD1</sub>  | FO = 1 Routing<br>Delay                   |                        |            | 2.6        |            | 2.9        |            | 3.2        |            | 3.8        |              | 5.3          | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing<br>Delay                   |                        |            | 2.9        |            | 3.2        |            | 3.7        |            | 4.3        |              | 6.1          | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing<br>Delay                   |                        |            | 3.3        |            | 3.6        |            | 4.1        |            | 4.9        |              | 6.8          | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing<br>Delay                   |                        |            | 3.6        |            | 4.0        |            | 4.6        |            | 5.4        |              | 7.6          | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing<br>Delay                   |                        |            | 5.1        |            | 5.6        |            | 6.4        |            | 7.5        |              | 10.5         | ns       |

| Global C           | lock Network                              |                        |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>CKH</sub>   | Input LOW to HIGH                         | FO = 32<br>FO = 384    |            | 4.4<br>4.8 |            | 4.8<br>5.3 |            | 5.5<br>6.0 |            | 6.5<br>7.1 |              | 9.0<br>9.9   | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW                         | FO = 32<br>FO = 384    |            | 5.3<br>6.2 |            | 5.9<br>6.9 |            | 6.7<br>7.9 |            | 7.8<br>9.2 |              | 11.0<br>12.9 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH               | FO = 32<br>FO = 384    | 5.7<br>6.6 |            | 6.3<br>7.4 |            | 7.1<br>8.3 |            | 8.4<br>9.8 |            | 11.8<br>13.7 |              | ns<br>ns |

# Table 41 • A42MX16 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

## Table 41 • A42MX16 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                  |                                                     | –3 S | peed | –2 Sp | beed | –1 S | peed | Std S | Speed | –F Sp | beed |       |

|------------------|-----------------------------------------------------|------|------|-------|------|------|------|-------|-------|-------|------|-------|

| Parame           | eter / Description                                  | Min. | Max. | Min.  | Max. | Min. | Max. | Min.  | Max.  | Min.  | Max. | Units |

| t <sub>ACO</sub> | Array Clock-to-Out<br>(Pad-to-Pad),64 Clock Loading |      | 11.3 |       | 12.5 |      | 14.2 |       | 16.7  |       | 23.3 | ns    |

| $d_{TLH}$        | Capacitive Loading, LOW to<br>HIGH                  |      | 0.04 |       | 0.04 |      | 0.05 |       | 0.06  |       | 0.08 | ns/pF |

| $d_{THL}$        | Capacitive Loading, HIGH to LOW                     |      | 0.05 |       | 0.05 |      | 0.06 |       | 0.07  |       | 0.10 | ns/pF |

1. For dual-module macros use tPD1 + tRD1 + taped, to + tRD1 + taped, or tPD1 + tRD1 + tusk, whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing ansalysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

4. Set-up and hold timing parameters for the input buffer latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G inputs subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

## Table 42 •A42MX24 Timing Characteristics (Nominal 5.0 V Operation) (Worst-Case Commercial Conditions,<br/>VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                               | –3 S | peed | –2 Sp | beed | –1 S | peed | Std S | Speed | –F S | peed |       |

|--------------------|-----------------------------------------------|------|------|-------|------|------|------|-------|-------|------|------|-------|

| Paramete           | er / Description                              | Min. | Max. | Min.  | Max. | Min. | Max. | Min.  | Max.  | Min. | Max. | Units |

| Logic Mo           | odule Combinatorial Functions <sup>1</sup>    |      |      |       |      |      |      |       |       |      |      |       |

| t <sub>PD</sub>    | Internal Array Module Delay                   |      | 1.2  |       | 1.3  |      | 1.5  |       | 1.8   |      | 2.5  | ns    |

| t <sub>PDD</sub>   | Internal Decode Module Delay                  |      | 1.4  |       | 1.6  |      | 1.8  |       | 2.1   |      | 3.0  | ns    |

| Logic Mo           | odule Predicted Routing Delays <sup>2</sup>   |      |      |       |      |      |      |       |       |      |      |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                          |      | 0.8  |       | 0.9  |      | 1.0  |       | 1.2   |      | 1.7  | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                          |      | 1.0  |       | 1.2  |      | 1.3  |       | 1.5   |      | 2.1  | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                          |      | 1.3  |       | 1.4  |      | 1.6  |       | 1.9   |      | 2.6  | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |      | 1.5  |       | 1.7  |      | 1.9  |       | 2.2   |      | 3.1  | ns    |

| t <sub>RD5</sub>   | FO = 8 Routing Delay                          |      | 2.4  |       | 2.7  |      | 3.0  |       | 3.6   |      | 5.0  | ns    |

| Logic Mo           | odule Sequential Timing <sup>3, 4</sup>       |      |      |       |      |      |      |       |       |      |      |       |

| t <sub>CO</sub>    | Flip-Flop Clock-to-Output                     |      | 1.3  |       | 1.4  |      | 1.6  |       | 1.9   |      | 2.7  | ns    |

| t <sub>GO</sub>    | Latch Gate-to-Output                          |      | 1.2  |       | 1.3  |      | 1.5  |       | 1.8   |      | 2.5  | ns    |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Set-Up Time                 | 0.3  |      | 0.4   |      | 0.4  |      | 0.5   |       | 0.7  |      | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Hold Time                   | 0.0  |      | 0.0   |      | 0.0  |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>RO</sub>    | Flip-Flop (Latch) Reset-to-Output             |      | 1.4  |       | 1.6  |      | 1.8  |       | 2.1   |      | 2.9  | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.4  |      | 0.5   |      | 0.5  |      | 0.6   |       | 0.8  |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0  |      | 0.0   |      | 0.0  |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width | 3.3  |      | 3.7   |      | 4.2  |      | 4.9   |       | 6.9  |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 4.4  |      | 4.8   |      | 5.3  |      | 6.5   |       | 9.0  |      | ns    |

|                    |                                               | –3 S | peed | –2 S | beed | –1 Sp | beed | Std S | peed | –F Sp | beed |       |

|--------------------|-----------------------------------------------|------|------|------|------|-------|------|-------|------|-------|------|-------|

| Paramet            | er / Description                              | Min. | Max. | Min. | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| Logic M            | odule Combinatorial Functions <sup>1</sup>    |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>PD</sub>    | Internal Array Module Delay                   |      | 1.3  |      | 1.5  |       | 1.7  |       | 2.0  |       | 2.7  | ns    |

| t <sub>PDD</sub>   | Internal Decode Module Delay                  |      | 1.6  |      | 1.8  |       | 2.0  |       | 2.4  |       | 3.3  | ns    |

| Logic M            | odule Predicted Routing Delays <sup>2</sup>   |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                          |      | 0.9  |      | 1.0  |       | 1.2  |       | 1.4  |       | 2.0  | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                          |      | 1.3  |      | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>RD3</sub>   | FO =3 Routing Delay                           |      | 1.6  |      | 1.8  |       | 2.0  |       | 2.4  |       | 3.4  | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |      | 2.0  |      | 2.2  |       | 2.5  |       | 2.9  |       | 4.1  | ns    |

| t <sub>RD5</sub>   | FO = 8 Routing Delay                          |      | 3.3  |      | 3.7  |       | 4.2  |       | 4.9  |       | 6.9  | ns    |

| t <sub>RDD</sub>   | Decode-to-Output Routing Delay                |      | 0.3  |      | 0.4  |       | 0.4  |       | 0.5  |       | 0.7  | ns    |

| Logic M            | odule Sequential Timing <sup>3, 4</sup>       |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>CO</sub>    | Flip-Flop Clock-to-Output                     |      | 1.3  |      | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>GO</sub>    | Latch Gate-to-Output                          |      | 1.3  |      | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Set-Up Time                 | 0.3  |      | 0.3  |      | 0.4   |      | 0.5   |      | 0.7   |      | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Hold Time                   | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>RO</sub>    | Flip-Flop (Latch) Reset-to-Output             |      | 1.6  |      | 1.7  |       | 2.0  |       | 2.3  |       | 3.2  | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.7  |      | 0.8  |      | 0.9   |      | 1.0   |      | 1.4   |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch) Clock Active<br>Pulse Width | 3.3  |      | 3.7  |      | 4.2   |      | 4.9   |      | 6.9   |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch) Asynchronous<br>Pulse Width | 4.4  |      | 4.8  |      | 5.5   |      | 6.4   |      | 9.0   |      | ns    |

| Synchro            | nous SRAM Operations                          |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>RC</sub>    | Read Cycle Time                               | 6.8  |      | 7.5  |      | 8.5   |      | 10.0  |      | 14.0  |      | ns    |

| t <sub>WC</sub>    | Write Cycle Time                              | 6.8  |      | 7.5  |      | 8.5   |      | 10.0  |      | 14.0  |      | ns    |

| t <sub>RCKHL</sub> | Clock HIGH/LOW Time                           | 3.4  |      | 3.8  |      | 4.3   |      | 5.0   |      | 7.0   |      | ns    |

| t <sub>RCO</sub>   | Data Valid After Clock<br>HIGH/LOW            |      | 3.4  |      | 3.8  |       | 4.3  |       | 5.0  |       | 7.0  | ns    |

| t <sub>ADSU</sub>  | Address/Data Set-Up Time                      | 1.6  |      | 1.8  |      | 2.0   |      | 2.4   |      | 3.4   |      | ns    |

| Synchro            | nous SRAM Operations (continu                 | ied) |      |      |      |       |      |       |      |       |      |       |

| t <sub>ADH</sub>   | Address/Data Hold Time                        | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>RENSU</sub> | Read Enable Set-Up                            | 0.6  |      | 0.7  |      | 0.8   |      | 0.9   |      | 1.3   |      | ns    |

| t <sub>RENH</sub>  | Read Enable Hold                              | 3.4  |      | 3.8  |      | 4.3   |      | 5.0   |      | 7.0   |      | ns    |

| t <sub>WENSU</sub> | Write Enable Set-Up                           | 2.7  |      | 3.0  |      | 3.4   |      | 4.0   |      | 5.6   |      | ns    |

| t <sub>WENH</sub>  | Write Enable Hold                             | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

|                    | Block Enable Set-Up                           | 2.8  |      | 3.1  |      | 3.5   |      | 4.1   |      | 5.7   |      | ns    |

| t <sub>BENS</sub>  | Diotit Litable Oct Op                         |      |      |      |      |       |      |       |      |       |      |       |

# Table 44 •A42MX36 Timing Characteristics (Nominal 5.0 V Operation)(Worst-Case Commercial Conditions,<br/>VCCA = 4.75 V, T<sub>J</sub> = 70°C)

#### Table 52 • PQ160

| PQ160      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 58         | VCCI             | VCCI             | VCCI             |

| 59         | GND              | GND              | GND              |

| 60         | VCCA             | VCCA             | VCCA             |

| 61         | LP               | LP               | LP               |

| 62         | I/O              | I/O              | TCK, I/O         |

| 63         | I/O              | I/O              | I/O              |

| 64         | GND              | GND              | GND              |

| 65         | I/O              | I/O              | I/O              |

| 66         | I/O              | I/O              | I/O              |

| 67         | I/O              | I/O              | I/O              |

| 68         | I/O              | I/O              | I/O              |

| 69         | GND              | GND              | GND              |

| 70         | NC               | I/O              | I/O              |

| 71         | I/O              | I/O              | I/O              |

| 72         | I/O              | I/O              | I/O              |

| 73         | I/O              | I/O              | I/O              |

| 74         | I/O              | I/O              | I/O              |

| 75         | NC               | I/O              | I/O              |

| 76         | I/O              | I/O              | I/O              |

| 77         | NC               | I/O              | I/O              |

| 78         | I/O              | I/O              | I/O              |

| 79         | NC               | I/O              | I/O              |

| 30         | GND              | GND              | GND              |

| 31         | I/O              | I/O              | I/O              |

| 32         | SDO, I/O         | SDO, I/O         | SDO, TDO, I/O    |

| 33         | I/O              | I/O              | WD, I/O          |

| 34         | I/O              | I/O              | WD, I/O          |

| 35         | I/O              | I/O              | I/O              |

| 36         | NC               | VCCI             | VCCI             |

| 37         | I/O              | I/O              | I/O              |

| 38         | I/O              | I/O              | WD, I/O          |

| 39         | GND              | GND              | GND              |

| 90         | NC               | I/O              | I/O              |

| 91         | I/O              | I/O              | I/O              |

| 92         | I/O              | I/O              | I/O              |

| 93         | I/O              | I/O              | I/O              |

| 94         | I/O              | I/O              | I/O              |

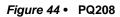

#### Table 53 • PQ208

| PQ208      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX16 Function | A42MX24 Function | A42MX36 Function |

| 1          | GND              | GND              | GND              |

| 2          | NC               | VCCA             | VCCA             |

| 3          | MODE             | MODE             | MODE             |

| 4          | I/O              | I/O              | I/O              |

| 5          | I/O              | I/O              | I/O              |

| 6          | I/O              | I/O              | I/O              |

| 7          | I/O              | I/O              | I/O              |

| 8          | I/O              | I/O              | I/O              |

| 9          | NC               | I/O              | I/O              |

| 10         | NC               | I/O              | I/O              |

| 11         | NC               | I/O              | I/O              |

| 12         | I/O              | I/O              | I/O              |

| 13         | I/O              | I/O              | I/O              |

| 14         | I/O              | I/O              | I/O              |

| 15         | I/O              | I/O              | I/O              |

| 16         | NC               | I/O              | I/O              |

| 17         | VCCA             | VCCA             | VCCA             |

| 18         | I/O              | I/O              | I/O              |

| 19         | I/O              | I/O              | I/O              |

| 20         | I/O              | I/O              | I/O              |

#### Table 53 • PQ208

| PQ208      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX16 Function | A42MX24 Function | A42MX36 Function |

| 58         | I/O              | WD, I/O          | WD, I/O          |

| 59         | I/O              | I/O              | I/O              |

| 60         | VCCI             | VCCI             | VCCI             |

| 61         | NC               | I/O              | I/O              |

| 62         | NC               | I/O              | I/O              |

| 63         | I/O              | I/O              | I/O              |

| 64         | I/O              | I/O              | I/O              |

| 65         | I/O              | I/O              | QCLKA, I/O       |

| 66         | I/O              | WD, I/O          | WD, I/O          |

| 67         | NC               | WD, I/O          | WD, I/O          |

| 68         | NC               | I/O              | I/O              |

| 69         | I/O              | I/O              | I/O              |

| 70         | I/O              | WD, I/O          | WD, I/O          |

| 71         | I/O              | WD, I/O          | WD, I/O          |

| 72         | I/O              | I/O              | I/O              |

| 73         | I/O              | I/O              | I/O              |

| 74         | I/O              | I/O              | I/O              |

| 75         | I/O              | I/O              | I/O              |

| 76         | I/O              | I/O              | I/O              |

| 77         | I/O              | I/O              | I/O              |

| 78         | GND              | GND              | GND              |

| 79         | VCCA             | VCCA             | VCCA             |

| 30         | NC               | VCCI             | VCCI             |

| 31         | I/O              | I/O              | I/O              |

| 32         | I/O              | I/O              | I/O              |

| 83         | I/O              | I/O              | I/O              |

| 34         | I/O              | I/O              | I/O              |

| 35         | I/O              | WD, I/O          | WD, I/O          |

| 36         | I/O              | WD, I/O          | WD, I/O          |

| 37         | I/O              | I/O              | I/O              |

| 38         | I/O              | I/O              | I/O              |

| 39         | NC               | I/O              | I/O              |

| 90         | NC               | I/O              | I/O              |

| 91         | I/O              | I/O              | QCLKB, I/O       |

| 92         | I/O              | I/O              | I/O              |

| 93         | I/O              | WD, I/O          | WD, I/O          |

| 94         | I/O              | WD, I/O          | WD, I/O          |

| PQ240      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 52         | VCCI             |

| 53         | I/O              |

| 54         | WD, I/O          |

| 55         | WD, I/O          |

| 56         | I/O              |

| 57         | SDI, I/O         |

| 58         | I/O              |

| 59         | VCCA             |

| 60         | GND              |

| 61         | GND              |

| 62         | I/O              |

| 63         | I/O              |

| 64         | I/O              |

| 65         | I/O              |

| 66         | I/O              |

| 67         | I/O              |

| 68         | I/O              |

| 69         | I/O              |

| 70         | I/O              |

| '1         | VCCI             |

| /2         | I/O              |

| 73         | I/O              |

| 74         | I/O              |

| 75         | I/O              |

| 76         | I/O              |

| 77         | I/O              |

| 78         | I/O              |

| 79         | I/O              |

| 30         | I/O              |

| 81         | I/O              |

| 82         | I/O              |

| 83         | I/O              |

| 84         | I/O              |

| 85         | VCCA             |

| 36         | I/O              |

| 87         | I/O              |

| 38         | VCCA             |

| PQ240      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 89         | VCCI             |

| 90         | VCCA             |

| 91         | LP               |

| 92         | TCK, I/O         |

| 93         | I/O              |

| 94         | GND              |

| 95         | I/O              |

| 96         | I/O              |

| 97         | I/O              |

| 98         | I/O              |

| 99         | I/O              |

| 100        | I/O              |

| 101        | I/O              |

| 102        | I/O              |

| 103        | I/O              |

| 104        | I/O              |

| 105        | I/O              |

| 106        | I/O              |

| 107        | I/O              |

| 108        | VCCI             |

| 109        | I/O              |

| 110        | I/O              |

| 111        | I/O              |

| 112        | I/O              |

| 113        | I/O              |

| 114        | I/O              |

| 115        | I/O              |

| 116        | I/O              |

| 117        | I/O              |

| 118        | VCCA             |

| 119        | GND              |

| 120        | GND              |

| 121        | GND              |

| 122        | I/O              |

| 123        | SDO, TDO, I/O    |

| 124        | I/O              |

| 125        | WD, I/O          |

| VQ80       |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A40MX02<br>Function | A40MX04<br>Function |

| 13         | VCC                 | VCC                 |

| 4          | I/O                 | I/O                 |

| 5          | I/O                 | I/O                 |

| 16         | I/O                 | I/O                 |

| 17         | NC                  | I/O                 |

| 18         | NC                  | I/O                 |

| 19         | NC                  | I/O                 |

| 20         | VCC                 | VCC                 |

| 21         | I/O                 | I/O                 |

| 22         | I/O                 | I/O                 |

| 23         | I/O                 | I/O                 |

| 24         | I/O                 | I/O                 |

| 25         | I/O                 | I/O                 |

| 26         | I/O                 | I/O                 |

| 27         | GND                 | GND                 |

| 28         | I/O                 | I/O                 |

| 29         | I/O                 | I/O                 |

| 30         | I/O                 | I/O                 |

| 31         | I/O                 | I/O                 |

| 2          | I/O                 | I/O                 |

| 3          | VCC                 | VCC                 |

| 34         | I/O                 | I/O                 |

| 35         | I/O                 | I/O                 |

| 36         | I/O                 | I/O                 |

| 37         | I/O                 | I/O                 |

| 38         | I/O                 | I/O                 |

| 39         | I/O                 | I/O                 |

| 10         | I/O                 | I/O                 |

| 11         | NC                  | I/O                 |

| 12         | NC                  | I/O                 |

| 13         | NC                  | I/O                 |

| 14         | I/O                 | I/O                 |

| 15         | I/O                 | I/O                 |

| 16         | I/O                 | I/O                 |

| 47         | GND                 | GND                 |

|            |                     |                     |

| VQ100      |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A42MX09<br>Function | A42MX16<br>Function |

| 57         | I/O                 | I/O                 |

| 58         | I/O                 | I/O                 |

| 59         | I/O                 | I/O                 |

| 60         | I/O                 | I/O                 |

| 61         | I/O                 | I/O                 |

| 62         | LP                  | LP                  |

| 63         | VCCA                | VCCA                |

| 64         | VCCI                | VCCI                |

| 65         | VCCA                | VCCA                |

| 66         | I/O                 | I/O                 |

| 67         | I/O                 | I/O                 |

| 68         | I/O                 | I/O                 |

| 69         | I/O                 | I/O                 |

| 70         | GND                 | GND                 |

| 71         | I/O                 | I/O                 |

| 72         | I/O                 | I/O                 |

| 73         | I/O                 | I/O                 |

| 74         | I/O                 | I/O                 |

| 75         | I/O                 | I/O                 |

| 76         | I/O                 | I/O                 |

| 77         | SDI, I/O            | SDI, I/O            |

| 78         | I/O                 | I/O                 |

| 79         | I/O                 | I/O                 |

| 80         | I/O                 | I/O                 |

| 81         | I/O                 | I/O                 |

| 82         | GND                 | GND                 |

| 83         | I/O                 | I/O                 |

| 84         | I/O                 | I/O                 |

| 85         | PRA, I/O            | PRA, I/O            |

| 86         | I/O                 | I/O                 |

| 87         | CLKA, I/O           | CLKA, I/O           |

| 88         | VCCA                | VCCA                |

| 89         | I/O                 | I/O                 |

| 90         | CLKB, I/O           | CLKB, I/O           |

| 91         | I/O                 | I/O                 |

| 92         | PRB, I/O            | PRB, I/O            |

| VQ100      |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A42MX09<br>Function | A42MX16<br>Function |

| 93         | I/O                 | I/O                 |

| 94         | GND                 | GND                 |

| 5          | I/O                 | I/O                 |

| 96         | I/O                 | I/O                 |

| )7         | I/O                 | I/O                 |

| 98         | I/O                 | I/O                 |

| 99         | I/O                 | I/O                 |

| 100        | DCLK, I/O           | DCLK, I/O           |

#### Figure 48 • TQ176

#### Table 57 • TQ176

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 1          | GND              | GND              | GND              |

| 2          | MODE             | MODE             | MODE             |

| 3          | I/O              | I/O              | I/O              |

| 4          | I/O              | I/O              | I/O              |

| 5          | I/O              | I/O              | I/O              |

| 6          | I/O              | I/O              | I/O              |

| 7          | I/O              | I/O              | I/O              |

| 8          | NC               | NC               | I/O              |

| 9          | I/O              | I/O              | I/O              |

|            |                  |                  |                  |

| Table 60 • BG | 272              |

|---------------|------------------|

| BG272         |                  |

| Pin Number    | A42MX36 Function |

| T19           | I/O              |

| T20           | I/O              |

| U1            | I/O              |

| U2            | I/O              |

| U3            | I/O              |

| U4            | I/O              |

| U5            | VCCI             |

| U6            | WD, I/O          |

| U7            | I/O              |

| U8            | I/O              |

| U9            | WD, I/O          |

| U10           | VCCA             |

| U11           | VCCI             |

| U12           | I/O              |

| U13           | I/O              |

| U14           | QCLKB, I/O       |

| U15           | I/O              |

| U16           | VCCI             |

| U17           | I/O              |

| U18           | GND              |

| U19           | I/O              |

| U20           | I/O              |

| V1            | I/O              |

| V2            | I/O              |

| V3            | GND              |

| V4            | GND              |

| V5            | I/O              |

| V6            | I/O              |

| V7            | I/O              |

| V8            | WD, I/O          |

| V9            | I/O              |

| V10           | I/O              |

| V11           | I/O              |

| V12           | I/O              |

| V13           | WD, I/O          |

| V14           | I/O              |

| V15           | WD, I/O          |