Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                          |

|--------------------------------|--------------------------------------------------------------------------|

| Product Status                 | Discontinued at Digi-Key                                                 |

| Number of LABs/CLBs            | -                                                                        |

| Number of Logic Elements/Cells | -                                                                        |

| Total RAM Bits                 | -                                                                        |

| Number of I/O                  | 131                                                                      |

| Number of Gates                | 24000                                                                    |

| Voltage - Supply               | 3V ~ 3.6V, 4.5V ~ 5.5V                                                   |

| Mounting Type                  | -                                                                        |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                       |

| Package / Case                 | -                                                                        |

| Supplier Device Package        | -                                                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx16-cq172m |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3 40MX and 42MX FPGAs

## 3.1 General Description

Microsemi's 40MX and 42MX families offer a cost-effective design solution at 5V. The MX devices are single-chip solutions and provide high performance while shortening the system design and development cycle. MX devices can integrate and consolidate logic implemented in multiple PALs, CPLDs, and FPGAs. Example applications include high-speed controllers and address decoding, peripheral bus interfaces, DSP, and co-processor functions.

The MX device architecture is based on Microsemi's patented antifuse technology implemented in a 0.45µm triple-metal CMOS process. With capacities ranging from 3,000 to 54,000 system gates, the MX devices provide performance up to 250 MHz, are live on power-up and have one-fifth the standby power consumption of comparable FPGAs. MX FPGAs provide up to 202 user I/Os and are available in a wide variety of packages and speed grades.

A42MX24 and A42MX36 devices also feature multiPlex I/Os, which support mixed-voltage systems, enable programmable PCI, deliver high-performance operation at both 5.0V and 3.3V, and provide a low-power mode. The devices are fully compliant with the PCI local bus specification (version 2.1). They deliver 200 MHz on-chip operation and 6.1 ns clock-to-output performance.

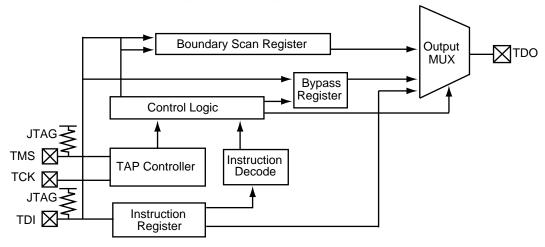

The 42MX24 and 42MX36 devices include system-level features such as IEEE Standard 1149.1 (JTAG) Boundary Scan Testing and fast wide-decode modules. In addition, the A42MX36 device offers dual-port SRAM for implementing fast FIFOs, LIFOs, and temporary data storage. The storage elements can efficiently address applications requiring wide data path manipulation and can perform transformation functions such as those required for telecommunications, networking, and DSP.

All MX devices are fully tested over automotive and military temperature ranges. In addition, the largest member of the family, the A42MX36, is available in both CQ208 and CQ256 ceramic packages screened to MIL-STD-883 levels. For easy prototyping and conversion from plastic to ceramic, the CQ208 and PQ208 devices are pin-compatible.

### 3.2 MX Architectural Overview

The MX devices are composed of fine-grained building blocks that enable fast, efficient logic designs. All devices within these families are composed of logic modules, I/O modules, routing resources and clock networks, which are the building blocks for fast logic designs. In addition, the A42MX36 device contains embedded dual-port SRAM modules, which are optimized for high-speed data path functions such as FIFOs, LIFOs and scratch pad memory. A42MX24 and A42MX36 also contain wide-decode modules.

## 3.2.1 Logic Modules

The 40MX logic module is an eight-input, one-output logic circuit designed to implement a wide range of logic functions with efficient use of interconnect routing resources.(see the following figure).

The logic module can implement the four basic logic functions (NAND, AND, OR and NOR) in gates of two, three, or four inputs. The logic module can also implement a variety of D-latches, exclusivity functions, AND-ORs and OR-ANDs. No dedicated hard-wired latches or flip-flops are required in the array; latches and flip-flops can be constructed from logic modules whenever required in the application.

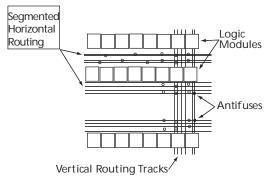

#### 3.2.3.3 Antifuse Structures

An antifuse is a "normally open" structure. The use of antifuses to implement a programmable logic device results in highly testable structures as well as efficient programming algorithms. There are no pre-existing connections; temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed and individual circuit structures to be tested, which can be done before and after programming. For instance, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

Figure 7 • MX Routing Structure

#### 3.2.4 Clock Networks

The 40MX devices have one global clock distribution network (CLK). A signal can be put on the CLK network by being routed through the CLKBUF buffer.

In 42MX devices, there are two low-skew, high-fanout clock distribution networks, referred to as CLKA and CLKB. Each network has a clock module (CLKMOD) that can select the source of the clock signal from any of the following (Figure 8, page 11):

- Externally from the CLKA pad, using CLKBUF buffer

- · Externally from the CLKB pad, using CLKBUF buffer

- Internally from the CLKINTA input, using CLKINT buffer

- Internally from the CLKINTB input, using CLKINT buffer

The clock modules are located in the top row of I/O modules. Clock drivers and a dedicated horizontal clock track are located in each horizontal routing channel.

Clock input pads in both 40MX and 42MX devices can also be used as normal I/Os, bypassing the clock networks.

The A42MX36 device has four additional register control resources, called quadrant clock networks (Figure 9, page 11). Each quadrant clock provides a local, high-fanout resource to the contiguous logic modules within its quadrant of the device. Quadrant clock signals can originate from specific I/O pins or from the internal array and can be used as a secondary register clock, register clear, or output enable.

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a device into a boundary-scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic tile and the input, output and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

Figure 14 • 42MX IEEE 1149.1 Boundary Scan Circuitry

Table 9 • Test Access Port Descriptions

| Port                      | Description                                                                                                                                                                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS<br>(Test Mode Select) | Serial input for the test logic control bits. Data is captured on the rising edge of the test logic clock (TCK).                                                                                                                                          |

| TCK<br>(Test Clock Input) | Dedicated test logic clock used serially to shift test instruction, test data, and control inputs on the rising edge of the clock, and serially to shift the output data on the falling edge of the clock. The maximum clock frequency for TCK is 20 MHz. |

| TDI<br>(Test Data Input)  | Serial input for instruction and test data. Data is captured on the rising edge of the test logic clock.                                                                                                                                                  |

| TDO<br>(Test Data Output) | Serial output for test instruction and data from the test logic. TDO is set to an Inactive Drive state (high impedance) when data scanning is not in progress.                                                                                            |

Table 10 • Supported BST Public Instructions

| Instruction    | IR Code<br>(IR2.IR0) | Instruction<br>Type | Description                                                                                                                                                            |

|----------------|----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000                  | Mandatory           | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins. |

| SAMPLE/PRELOAD | 001                  | Mandatory           | Allows a snapshot of the signals at the device pins to be captured and examined during operation                                                                       |

| HIGH Z         | 101                  | Optional            | Tristates all I/Os to allow external signals to drive pins. See the IEEE Standard 1149.1 specification.                                                                |

| CLAMP          | 110                  | Optional            | Allows state of signals driven from component pins to be determined from the Boundary-Scan Register. See the IEEE Standard 1149.1 specification for details.           |

| BYPASS         | 111                  | Mandatory           | Enables the bypass register between the TDI and TDO pins. The test data passes through the selected device to adjacent devices in the test chain.                      |

## 3.8.1 3.3 V LVTTL Electrical Specifications

Table 19 • 3.3V LVTTL Electrical Specifications

|                                                             |                      | Com     | mercial     | Com      | mercial -F   | Indus  | trial        | Milita  | ry             |       |

|-------------------------------------------------------------|----------------------|---------|-------------|----------|--------------|--------|--------------|---------|----------------|-------|

| Symbol                                                      | Parameter            | Min.    | Max.        | Min.     | Max.         | Min.   | Max.         | Min.    | Max.           | Units |

| VOH <sup>1</sup>                                            | IOH = -4 mA          | 2.15    |             | 2.15     |              | 2.4    |              | 2.4     |                | V     |

| VOL <sup>1</sup>                                            | IOL = 6 mA           |         | 0.4         |          | 0.4          |        | 0.48         |         | 0.48           | V     |

| VIL                                                         |                      | -0.3    | 0.8         | -0.3     | 0.8          | -0.3   | 0.8          | -0.3    | 0.8            | V     |

| VIH (40MX)                                                  |                      | 2.0     | VCC + 0.3   | 2.0      | VCC + 0.3    | 2.0    | VCC + 0.3    | 2.0     | VCC + 0.3      | V     |

| VIH (42MX)                                                  |                      | 2.0     | VCCI + 0.3  | 2.0      | VCCI + 0.3   | 2.0    | VCCI + 0.3   | 2.0     | VCCI + 0.3     | V     |

| IIL                                                         |                      |         | -10         |          | -10          |        | -10          |         | -10            | μΑ    |

| IIH                                                         |                      |         | -10         |          | -10          |        | -10          |         | -10            | μΑ    |

| Input Transition<br>Time, T <sub>R</sub> and T <sub>F</sub> |                      |         | 500         |          | 500          |        | 500          |         | 500            | ns    |

| C <sub>IO</sub> I/O<br>Capacitance                          |                      |         | 10          |          | 10           |        | 10           |         | 10             | pF    |

| Standby<br>Current, ICC <sup>2</sup>                        | A40MX02,<br>A40MX04  |         | 3           |          | 25           |        | 10           |         | 25             | mA    |

|                                                             | A42MX09              |         | 5           |          | 25           |        | 25           |         | 25             | mA    |

|                                                             | A42MX16              |         | 6           |          | 25           |        | 25           |         | 25             | mA    |

|                                                             | A42MX24,<br>A42MX36  |         | 15          |          | 25           |        | 25           |         | 25             | mA    |

| Low-Power<br>Mode Standby<br>Current                        | 42MX<br>devices only |         | 0.5         |          | ICC - 5.0    |        | ICC - 5.0    |         | ICC - 5.0      | mA    |

| IIO, I/O source                                             | Can be derive        | ed from | the IBIS mo | del (htt | p://www.micr | osemi. | com/soc/tech | idocs/r | nodels/ibis.ht | ml)   |

<sup>1.</sup> Only one output tested at a time. VCC/VCCI = min.

# 3.9 Mixed 5.0 V / 3.3 V Operating Conditions (for 42MX Devices Only)

Table 20 • Absolute Maximum Ratings\*

| Symbol           | Parameter                   | Limits             | Units |

|------------------|-----------------------------|--------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | -0.5 to +7.0       | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0       | V     |

| VI               | Input Voltage               | -0.5 to VCCA +0.5  | V     |

| VO               | Output Voltage              | -0.5 to VCCI + 0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150        | °C    |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device

<sup>2.</sup> All outputs unloaded. All inputs = VCC/VCCI or GND.

## 3.10 Timing Models

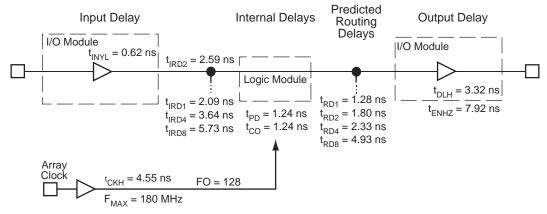

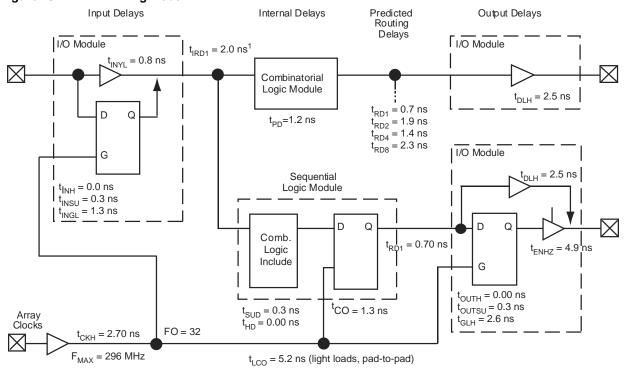

The following figures show various timing models.

Figure 17 • 40MX Timing Model\*

Note: Values are shown for 40MX –3 speed devices at 5.0 V worst-case commercial conditions.

Figure 18 • 42MX Timing Model

Note: 1. Input module predicted routing delay

Note: 2. Values are shown for A42MX09 –3 at 5.0 V worst-case commercial conditions.

Table 34 • A40MX02 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C)

|                   |                                   | -3 Sp | peed | –2 Sp | eed  | -1 Sp | eed  | Std S | peed | −F Sp | eed  |       |

|-------------------|-----------------------------------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Parame            | eter / Description                | Min.  | Max. | Units |

| TTL O             | utput Module Timing <sup>4</sup>  |       |      |       |      |       |      |       |      |       |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                  |       | 3.3  |       | 3.8  |       | 4.3  |       | 5.1  |       | 7.2  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                   |       | 4.0  |       | 4.6  |       | 5.2  |       | 6.1  |       | 8.6  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH              |       | 3.7  |       | 4.3  |       | 4.9  |       | 5.8  |       | 8.0  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW               |       | 4.7  |       | 5.4  |       | 6.1  |       | 7.2  |       | 10.1 | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z              |       | 7.9  |       | 9.1  |       | 10.4 |       | 12.2 |       | 17.1 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z               |       | 5.9  |       | 6.8  |       | 7.7  |       | 9.0  |       | 12.6 | ns    |

| d <sub>TLH</sub>  | Delta LOW to<br>HIGH              |       | 0.02 |       | 0.02 |       | 0.03 |       | 0.03 |       | 0.04 | ns/pF |

| d <sub>THL</sub>  | Delta HIGH to<br>LOW              |       | 0.03 |       | 0.03 |       | 0.03 |       | 0.04 |       | 0.06 | ns/pF |

| CMOS              | Output Module Timing <sup>4</sup> |       |      |       |      |       |      |       |      |       |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                  |       | 3.9  |       | 4.5  |       | 5.1  |       | 6.05 |       | 8.5  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                   |       | 3.4  |       | 3.9  |       | 4.4  |       | 5.2  |       | 7.3  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH              |       | 3.4  |       | 3.9  |       | 4.4  |       | 5.2  |       | 7.3  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW               |       | 4.9  |       | 5.6  |       | 6.4  |       | 7.5  |       | 10.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z              |       | 7.9  |       | 9.1  |       | 10.4 |       | 12.2 |       | 17.0 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z               |       | 5.9  |       | 6.8  |       | 7.7  |       | 9.0  |       | 12.6 | ns    |

| d <sub>TLH</sub>  | Delta LOW to<br>HIGH              |       | 0.03 |       | 0.04 |       | 0.04 |       | 0.05 |       | 0.07 | ns/pF |

| d <sub>THL</sub>  | Delta HIGH to<br>LOW              |       | 0.02 |       | 0.02 |       | 0.03 |       | 0.03 |       | 0.04 | ns/pF |

<sup>1.</sup> Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance

Table 35 • A40MX02 Timing Characteristics (Nominal 3.3 V Operation) (Worst-Case Commercial Conditions, VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                  |                                 | -3 Sp          | peed | -2 Sp | peed | -1 Sp | peed | Std S | Speed | −F S | peed |       |

|------------------|---------------------------------|----------------|------|-------|------|-------|------|-------|-------|------|------|-------|

| Parame           | eter / Description              | Min.           | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| Logic N          | Module Propagation Delays       |                |      |       |      |       |      |       |       |      |      |       |

| t <sub>PD1</sub> | Single Module                   |                | 1.7  |       | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>PD2</sub> | Dual-Module Macros              |                | 3.7  |       | 4.3  |       | 4.9  |       | 5.7   |      | 8.0  | ns    |

| t <sub>CO</sub>  | Sequential Clock-to-Q           |                | 1.7  |       | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>GO</sub>  | Latch G-to-Q                    |                | 1.7  |       | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>RS</sub>  | Flip-Flop (Latch) Reset-to-Q    |                | 1.7  |       | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| Logic N          | Module Predicted Routing Delays | s <sup>1</sup> |      |       |      |       |      |       |       |      |      |       |

<sup>2.</sup> Set-up times assume fanout of 3. Further testing information can be obtained from the Timer utility

<sup>3.</sup> The hold time for the DFME1A macro may be greater than 0 ns. Use the Timer tool from the Designer software to check the hold time for this macro.

<sup>4.</sup> Delays based on 35pF loading

Table 38 • A42MX09 Timing Characteristics (Nominal 5.0 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                   |                                                          | -3 Sp | eed  | -2 S | peed | –1 Sp | peed | Std S | Speed | −F S | peed |       |

|-------------------|----------------------------------------------------------|-------|------|------|------|-------|------|-------|-------|------|------|-------|

| Parame            | eter / Description                                       | Min.  | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| TTL Ou            | tput Module Timing <sup>5</sup>                          |       |      |      |      |       |      |       |       |      |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                                         |       | 2.5  |      | 2.7  |       | 3.1  |       | 3.6   |      | 5.1  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                                          |       | 2.9  |      | 3.2  |       | 3.6  |       | 4.3   |      | 6.0  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH                                     |       | 2.6  |      | 2.9  |       | 3.3  |       | 3.9   |      | 5.5  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW                                      |       | 2.9  |      | 3.2  |       | 3.7  |       | 4.3   |      | 6.1  | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z                                     |       | 4.9  |      | 5.4  |       | 6.2  |       | 7.3   |      | 10.2 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                                      |       | 5.3  |      | 5.9  |       | 6.7  |       | 7.9   |      | 11.1 | ns    |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                            |       | 2.6  |      | 2.9  |       | 3.3  |       | 3.8   |      | 5.3  | ns    |

| t <sub>GHL</sub>  | G-to-Pad LOW                                             |       | 2.6  |      | 2.9  |       | 3.3  |       | 3.8   |      | 5.3  | ns    |

| t <sub>LSU</sub>  | I/O Latch Set-Up                                         | 0.5   |      | 0.5  |      | 0.6   |      | 0.7   |       | 1.0  |      | ns    |

| t <sub>LH</sub>   | I/O Latch Hold                                           | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad), 64 Clock Loading |       | 5.2  |      | 5.8  |       | 6.6  |       | 7.7   |      | 10.8 | ns    |

| t <sub>ACO</sub>  | Array Clock-to-Out<br>(Pad-to-Pad), 64 Clock Loading     |       | 7.4  |      | 8.2  |       | 9.3  |       | 10.9  |      | 15.3 | ns    |

| d <sub>TLH</sub>  | Capacity Loading, LOW to HIGH                            |       | 0.03 |      | 0.03 |       | 0.03 |       | 0.04  |      | 0.06 | ns/pF |

| d <sub>THL</sub>  | Capacity Loading, HIGH to LOW                            |       | 0.04 |      | 0.04 |       | 0.04 |       | 0.05  |      | 0.07 | ns/pF |

Table 44 • A42MX36 Timing Characteristics (Nominal 5.0 V Operation)(Worst-Case Commercial Conditions,  $VCCA = 4.75 \text{ V}, T_J = 70^{\circ}\text{C}$

| -                 |                                               | −3 S | peed | -2 Sp | peed | –1 Sp | peed | Std S | peed | –F Sp | eed  |       |

|-------------------|-----------------------------------------------|------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Parame            | eter / Description                            | Min. | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| CMOS              | Output Module Timing <sup>5</sup>             |      |      |       |      |       |      |       |      |       |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                              |      | 3.5  |       | 3.9  |       | 4.5  |       | 5.2  |       | 7.3  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                               |      | 2.5  |       | 2.7  |       | 3.1  |       | 3.6  |       | 5.1  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH                          |      | 2.7  |       | 3.0  |       | 3.3  |       | 3.9  |       | 5.5  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW                           |      | 2.9  |       | 3.3  |       | 3.7  |       | 4.3  |       | 6.1  | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z                          |      | 5.3  |       | 5.8  |       | 6.6  |       | 7.8  |       | 10.9 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                           |      | 4.9  |       | 5.5  |       | 6.2  |       | 7.3  |       | 10.2 | ns    |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                 |      | 5.0  |       | 5.6  |       | 6.3  |       | 7.5  |       | 10.4 | ns    |

| t <sub>GHL</sub>  | G-to-Pad LOW                                  |      | 5.0  |       | 5.6  |       | 6.3  |       | 7.5  |       | 10.4 | ns    |

| t <sub>LSU</sub>  | I/O Latch Set-Up                              | 0.5  |      | 0.5   |      | 0.6   |      | 0.7   |      | 1.0   |      | ns    |

| t <sub>LH</sub>   | I/O Latch Hold                                | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O |      | 5.7  |       | 6.3  |       | 7.1  |       | 8.4  |       | 11.8 | ns    |

| t <sub>ACO</sub>  | Array Latch Clock-to-Out (Pad-to-Pad) 32 I/O  |      | 7.8  |       | 8.6  |       | 9.8  |       | 11.5 |       | 16.1 | ns    |

| d <sub>TLH</sub>  | Capacitive Loading,<br>LOW to HIGH            |      | 0.07 |       | 0.08 |       | 0.09 |       | 0.10 |       | 0.14 | ns/pF |

| d <sub>THL</sub>  | Capacitive Loading,<br>HIGH to LOW            |      | 0.07 |       | 0.08 |       | 0.09 |       | 0.10 |       | 0.14 | ns/pF |

Table 45 • A42MX36 Timing Characteristics (Nominal 3.3 V Operation) (Worst-Case Commercial Conditions,  $VCCA = 3.0 \text{ V}, T_{.1} = 70^{\circ}\text{C}$

|                  |                                              | −3 S <sub>I</sub> | peed | -2 S | peed | –1 Sp | peed | Std S | Speed | -F S | peed |       |

|------------------|----------------------------------------------|-------------------|------|------|------|-------|------|-------|-------|------|------|-------|

| Parame           | eter / Description                           | Min.              | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| Logic N          | Module Combinatorial Functions <sup>1</sup>  |                   |      |      |      |       |      |       |       |      |      |       |

| t <sub>PD</sub>  | Internal Array Module Delay                  |                   | 1.9  |      | 2.1  |       | 2.3  |       | 2.7   |      | 3.8  | ns    |

| t <sub>PDD</sub> | Internal Decode Module Delay                 |                   | 2.2  |      | 2.5  |       | 2.8  |       | 3.3   |      | 4.7  | ns    |

| Logic N          | Module Predicted Routing Delays <sup>2</sup> |                   |      |      |      |       |      |       |       |      |      |       |

| t <sub>RD1</sub> | FO = 1 Routing Delay                         |                   | 1.3  |      | 1.5  |       | 1.7  |       | 2.0   |      | 2.7  | ns    |

| t <sub>RD2</sub> | FO = 2 Routing Delay                         |                   | 1.8  |      | 2.0  |       | 2.3  |       | 2.7   |      | 3.7  | ns    |

| t <sub>RD3</sub> | FO = 3 Routing Delay                         |                   | 2.3  |      | 2.5  |       | 2.8  |       | 3.4   |      | 4.7  | ns    |

| t <sub>RD4</sub> | FO = 4 Routing Delay                         |                   | 2.8  |      | 3.1  |       | 3.5  |       | 4.1   |      | 5.7  | ns    |

For dual-module macros, use  $t_{PD1} + t_{RD1} + t_{PDn}$ ,  $t_{CO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

Delays based on 35 pF loading.

Table 45 • A42MX36 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                   |                                                 | -3 S | peed | -2 S | peed | -1 Sp | peed | Std S | peed | −F S <sub>I</sub> | peed |       |

|-------------------|-------------------------------------------------|------|------|------|------|-------|------|-------|------|-------------------|------|-------|

| Parame            | ter / Description                               | Min. | Max. | Min. | Max. | Min.  | Max. | Min.  | Max. | Min.              | Max. | Units |

| t <sub>ACO</sub>  | Array Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O |      | 10.9 |      | 12.1 |       | 13.7 |       | 16.1 |                   | 22.5 | ns    |

| d <sub>TLH</sub>  | Capacitive Loading, LOW to HIGH                 |      | 0.10 |      | 0.11 |       | 0.12 |       | 0.14 |                   | 0.20 | ns/pF |

| d <sub>THL</sub>  | Capacitive Loading, HIGH to LOW                 |      | 0.10 |      | 0.11 |       | 0.12 |       | 0.14 |                   | 0.20 | ns/pF |

| CMOS              | Dutput Module Timing <sup>5</sup>               |      |      |      |      |       |      |       |      |                   |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                                |      | 4.9  |      | 5.5  |       | 6.2  |       | 7.3  |                   | 10.3 | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                                 |      | 3.4  |      | 3.8  |       | 4.3  |       | 5.1  |                   | 7.1  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH                            |      | 3.7  |      | 4.1  |       | 4.7  |       | 5.5  |                   | 7.7  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW                             |      | 4.1  |      | 4.6  |       | 5.2  |       | 6.1  |                   | 8.5  | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z                            |      | 7.4  |      | 8.2  |       | 9.3  |       | 10.9 |                   | 15.3 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                             |      | 6.9  |      | 7.6  |       | 8.7  |       | 10.2 |                   | 14.3 | ns    |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                   |      | 7.0  |      | 7.8  |       | 8.9  |       | 10.4 |                   | 14.6 | ns    |

| t <sub>GHL</sub>  | G-to-Pad LOW                                    |      | 7.0  |      | 7.8  |       | 8.9  |       | 10.4 |                   | 14.6 | ns    |

| t <sub>LSU</sub>  | I/O Latch Set-Up                                | 0.7  |      | 0.7  |      | 0.8   |      | 1.0   |      | 1.4               |      | ns    |

| t <sub>LH</sub>   | I/O Latch Hold                                  | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0               |      | ns    |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O   |      | 7.9  |      | 8.8  |       | 10.0 |       | 11.8 |                   | 16.5 | ns    |

For dual-module macros, use t<sub>PD1</sub> + t<sub>RD1</sub> + t<sub>PDn</sub>, t<sub>CO</sub> + t<sub>RD1</sub> + t<sub>PDn</sub>, or t<sub>PD1</sub> + t<sub>RD1</sub> + t<sub>SUD</sub>, whichever is appropriate.

## 3.12 Pin Descriptions

This section lists the pin descriptions for 40MX and 42MX series FPGAs.

#### CLK/A/B, I/O Global Clock

Clock inputs for clock distribution networks. CLK is for 40MX while CLKA and CLKB are for 42MX devices. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O

#### DCLK, I/ODiagnostic Clock

Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### **GND**, Ground

Input LOW supply voltage.

#### I/O, Input/Output

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

<sup>3.</sup> Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

<sup>4.</sup> Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

<sup>5.</sup> Delays based on 35 pF loading.

Clock signal to shift the Boundary Scan Test (BST) data into the device. This pin functions as an I/O when "Reserve JTAG" is not checked in the Designer Software. BST pins are only available in A42MX24 and A42MX36 devices.

#### TDI, I/OTest Data In

Serial data input for BST instructions and data. Data is shifted in on the rising edge of TCK. This pin functions as an I/O when "Reserve JTAG" is not checked in the Designer Software. BST pins are only available in A42MX24 and A42MX36 devices.

#### TDO, I/OTest Data Out

Serial data output for BST instructions and test data. This pin functions as an I/O when "Reserve JTAG" is not checked in the Designer Software. BST pins are only available in A42MX24 and A42MX36 devices.

#### TMS, I/OTest Mode Select

The TMS pin controls the use of the IEEE 1149.1 Boundary Scan pins (TCK, TDI, TDO). In flexible mode when the TMS pin is set LOW, the TCK, TDI and TDO pins are boundary scan pins. Once the boundary scan pins are in test mode, they will remain in that mode until the internal boundary scan state machine reaches the "logic reset" state. At this point, the boundary scan pins will be released and will function as regular I/O pins. The "logic reset" state is reached 5 TCK cycles after the TMS pin is set HIGH. In dedicated test mode, TMS functions as specified in the IEEE 1149.1 specifications. IEEE JTAG specification recommends a  $10k\Omega$  pull-up resistor on the pin. BST pins are only available in A42MX24 and A42MX36 devices.

#### VCC, Supply Voltage

Input supply voltage for 40MX devices

#### VCCA, Supply Voltage

Supply voltage for array in 42MX devices

#### **VCCI, Supply Voltage**

Supply voltage for I/Os in 42MX devices

#### WD, I/OWide Decode Output

When a wide decode module is used in a 42MX device this pin can be used as a dedicated output from the wide decode module. This direct connection eliminates additional interconnect delays associated with regular logic modules. To implement the direct I/O connection, connect an output buffer of any type to the output of the wide decode macro and place this output on one of the reserved WD pins.

# 4 Package Pin Assignments

The following figures and tables give the details of the package pin assignments.

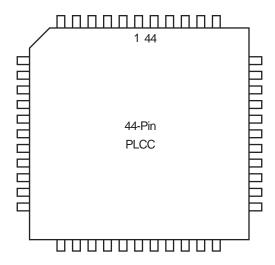

Figure 38 • PL44

Table 47 • PL44

| PL44       |                  |                  |

|------------|------------------|------------------|

| Pin Number | A40MX02 Function | A40MX04 Function |

| 1          | I/O              | I/O              |

| 2          | I/O              | I/O              |

| 3          | VCC              | VCC              |

| 4          | I/O              | I/O              |

| 5          | I/O              | I/O              |

| 6          | I/O              | I/O              |

| 7          | I/O              | I/O              |

| 8          | I/O              | I/O              |

| 9          | I/O              | I/O              |

| 10         | GND              | GND              |

| 11         | I/O              | I/O              |

| 12         | I/O              | I/O              |

| 13         | I/O              | I/O              |

| 14         | VCC              | VCC              |

| 15         | I/O              | I/O              |

| 16         | VCC              | VCC              |

| 17         | I/O              | I/O              |

| 18         | I/O              | I/O              |

| 19         | I/O              | I/O              |

| 20         | I/O              | I/O              |

|            |                  |                  |

Table 48 • PL68

| PL68       |                  |                  |

|------------|------------------|------------------|

| Pin Number | A40MX02 Function | A40MX04 Function |

| 24         | I/O              | I/O              |

| 25         | VCC              | VCC              |

| 26         | I/O              | I/O              |

| 27         | I/O              | I/O              |

| 28         | I/O              | I/O              |

| 29         | I/O              | I/O              |

| 30         | I/O              | I/O              |

| 31         | I/O              | I/O              |

| 32         | GND              | GND              |

| 33         | I/O              | I/O              |

| 34         | I/O              | I/O              |

| 35         | I/O              | I/O              |

| 36         | I/O              | I/O              |

| 37         | I/O              | I/O              |

| 38         | VCC              | VCC              |

| 39         | I/O              | I/O              |

| 40         | I/O              | I/O              |

| 41         | I/O              | I/O              |

| 42         | I/O              | I/O              |

| 43         | I/O              | I/O              |

| 44         | I/O              | I/O              |

| 45         | I/O              | I/O              |

| 46         | I/O              | I/O              |

| 47         | I/O              | I/O              |

| 48         | I/O              | I/O              |

| 49         | GND              | GND              |

| 50         | I/O              | I/O              |

| 51         | I/O              | I/O              |

| 52         | CLK, I/O         | CLK, I/O         |

| 53         | I/O              | I/O              |

| 54         | MODE             | MODE             |

| 55         | VCC              | VCC              |

| 56         | SDI, I/O         | SDI, I/O         |

| 57         | DCLK, I/O        | DCLK, I/O        |

| 58         | PRA, I/O         | PRA, I/O         |

| 59         | PRB, I/O         | PRB, I/O         |

| 60         | I/O              | I/O              |

Table 50 • PQ 100

| PQ100      |                  |                  |                  |                  |

|------------|------------------|------------------|------------------|------------------|

| Pin Number | A40MX02 Function | A40MX04 Function | A42MX09 Function | A42MX16 Function |

| 93         | VCC              | VCC              | I/O              | I/O              |

| 94         | VCC              | VCC              | PRB, I/O         | PRB, I/O         |

| 95         | NC               | I/O              | I/O              | I/O              |

| 96         | NC               | I/O              | GND              | GND              |

| 97         | NC               | I/O              | I/O              | I/O              |

| 98         | SDI, I/O         | SDI, I/O         | I/O              | I/O              |

| 99         | DCLK, I/O        | DCLK, I/O        | I/O              | I/O              |

| 100        | PRA, I/O         | PRA, I/O         | I/O              | I/O              |

Table 51 • PQ144

| PQ144      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX09 Function |  |

| 6          | I/O              |  |

| 7          | I/O              |  |

| 8          | I/O              |  |

| 9          | GNDQ             |  |

| 10         | GNDI             |  |

| 11         | NC               |  |

| 12         | I/O              |  |

| 13         | I/O              |  |

| 14         | I/O              |  |

| 15         | I/O              |  |

| 16         | I/O              |  |

| 17         | I/O              |  |

| 18         | VSV              |  |

| 19         | VCC              |  |

| 20         | VCCI             |  |

| 21         | NC               |  |

| 22         | I/O              |  |

| 23         | I/O              |  |

| 24         | I/O              |  |

| 25         | I/O              |  |

| 26         | I/O              |  |

| 27         | I/O              |  |

| 28         | GND              |  |

| 29         | GNDI             |  |

| 30         | NC               |  |

| 31         | I/O              |  |

| 32         | I/O              |  |

| 33         | I/O              |  |

| 34         | I/O              |  |

| 35         | I/O              |  |

| 36         | I/O              |  |

| 37         | BININ            |  |

| 38         | BINOUT           |  |

| 39         | I/O              |  |

| 40         | I/O              |  |

| 41         | I/O              |  |

| 42         | I/O              |  |

|            |                  |  |

Table 54 • PQ240

| PQ240      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX36 Function |  |

| 52         | VCCI             |  |

| 53         | I/O              |  |

| 54         | WD, I/O          |  |

| 55         | WD, I/O          |  |

| 56         | I/O              |  |

| 57         | SDI, I/O         |  |

| 58         | I/O              |  |

| 59         | VCCA             |  |

| 60         | GND              |  |

| 61         | GND              |  |

| 62         | I/O              |  |

| 63         | I/O              |  |

| 64         | I/O              |  |

| 65         | I/O              |  |

| 66         | I/O              |  |

| 67         | I/O              |  |

| 68         | I/O              |  |

| 69         | I/O              |  |

| 70         | I/O              |  |

| 71         | VCCI             |  |

| 72         | I/O              |  |

| 73         | I/O              |  |

| 74         | I/O              |  |

| 75         | I/O              |  |

| 76         | I/O              |  |

| 77         | I/O              |  |

| 78         | I/O              |  |

| 79         | I/O              |  |

| 80         | I/O              |  |

| 81         | I/O              |  |

| 82         | I/O              |  |

| 83         | I/O              |  |

| 84         | I/O              |  |

| 85         | VCCA             |  |

| 86         | I/O              |  |

| 87         | I/O              |  |

| 88         | VCCA             |  |

Table 54 • PQ240

| PQ240      |                  |   |

|------------|------------------|---|

| Pin Number | A42MX36 Function |   |

| 126        | WD, I/O          |   |

| 127        | I/O              |   |

| 128        | VCCI             |   |

| 129        | I/O              |   |

| 130        | I/O              |   |

| 131        | I/O              |   |

| 132        | WD, I/O          |   |

| 133        | WD, I/O          |   |

| 134        | I/O              |   |

| 135        | QCLKB, I/O       |   |

| 136        | I/O              |   |

| 137        | I/O              |   |

| 138        | I/O              |   |

| 139        | I/O              |   |

| 140        | I/O              |   |

| 141        | I/O              |   |

| 142        | WD, I/O          |   |

| 143        | WD, I/O          |   |

| 144        | I/O              |   |

| 145        | I/O              |   |

| 146        | I/O              |   |

| 147        | I/O              |   |

| 148        | I/O              |   |

| 149        | I/O              |   |

| 150        | VCCI             |   |

| 151        | VCCA             |   |

| 152        | GND              |   |

| 153        | I/O              |   |

| 154        | I/O              |   |

| 155        | I/O              |   |

| 156        | I/O              |   |

| 157        | I/O              |   |

| 158        | I/O              |   |

| 159        | WD, I/O          |   |

| 160        | WD, I/O          |   |

| 161        | I/O              |   |

| 162        | I/O              |   |

|            |                  | _ |

Table 54 • PQ240

| PQ240      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX36 Function |  |

| 200        | I/O              |  |

| 201        | I/O              |  |

| 202        | I/O              |  |

| 203        | I/O              |  |

| 204        | I/O              |  |

| 205        | I/O              |  |

| 206        | VCCA             |  |

| 207        | I/O              |  |

| 208        | I/O              |  |

| 209        | VCCA             |  |

| 210        | VCCI             |  |

| 211        | I/O              |  |

| 212        | I/O              |  |

| 213        | I/O              |  |

| 214        | I/O              |  |

| 215        | I/O              |  |

| 216        | I/O              |  |

| 217        | I/O              |  |

| 218        | I/O              |  |

| 219        | VCCA             |  |

| 220        | I/O              |  |

| 221        | I/O              |  |

| 222        | I/O              |  |

| 223        | I/O              |  |

| 224        | I/O              |  |

| 225        | I/O              |  |

| 226        | I/O              |  |

| 227        | VCCI             |  |

| 228        | I/O              |  |

| 229        | I/O              |  |

| 230        | I/O              |  |

| 231        | I/O              |  |

| 232        | I/O              |  |

| 233        | I/O              |  |

| 234        | I/O              |  |

| 235        | I/O              |  |

| 236        | I/O              |  |

Table 57 • TQ176

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 158        | CLKB, I/O        | CLKB, I/O        | CLKB, I/O        |

| 159        | I/O              | I/O              | I/O              |

| 160        | PRB, I/O         | PRB, I/O         | PRB, I/O         |

| 161        | NC               | I/O              | WD, I/O          |

| 162        | I/O              | I/O              | WD, I/O          |

| 163        | I/O              | I/O              | I/O              |

| 164        | I/O              | I/O              | I/O              |

| 165        | NC               | NC               | WD, I/O          |

| 166        | NC               | I/O              | WD, I/O          |

| 167        | I/O              | I/O              | I/O              |

| 168        | NC               | I/O              | I/O              |

| 169        | I/O              | I/O              | I/O              |

| 170        | NC               | VCCI             | VCCI             |

| 171        | I/O              | I/O              | WD, I/O          |

| 172        | I/O              | I/O              | WD, I/O          |

| 173        | NC               | I/O              | I/O              |

| 174        | I/O              | I/O              | I/O              |

| 175        | DCLK, I/O        | DCLK, I/O        | DCLK, I/O        |

| 176        | I/O              | I/O              | I/O              |

|            |                  |                  |                  |

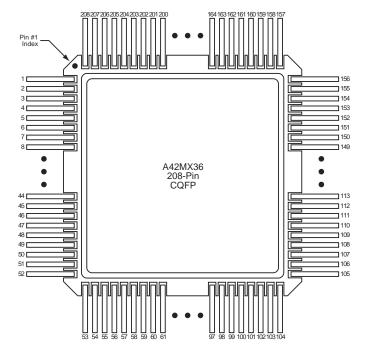

Figure 49 • CQ208

Table 61 • PG132

| PG132      |                  |

|------------|------------------|

| Pin Number | A42MX09 Function |

| G12        | VSV              |

| F13        | I/O              |

| F12        | I/O              |

| F11        | I/O              |

| F10        | I/O              |

| E13        | I/O              |

| D13        | I/O              |

| D12        | I/O              |

| C13        | I/O              |

| B13        | I/O              |

| D11        | I/O              |

| C12        | I/O              |

| A13        | I/O              |

| C11        | I/O              |

| B12        | SDI              |

| B11        | I/O              |

| C10        | I/O              |

| A12        | I/O              |

| A11        | I/O              |

| B10        | I/O              |

| D8         | I/O              |

| A10        | I/O              |

| C8         | I/O              |

| A9         | I/O              |

| B8         | PRBA             |

| A8         | I/O              |

| B7         | CLKA             |

| A7         | I/O              |

| B6         | CLKB             |

| A6         | I/O              |

| C6         | PRBB             |

| A5         | I/O              |

| D6         | I/O              |

| A4         | I/O              |

| B4         | I/O              |

| A3         | I/O              |

| C4         | I/O              |

|            |                  |

Table 62 • CQ172

| 60 | I/O  |

|----|------|

| 61 | I/O  |

| 62 | I/O  |

| 63 | I/O  |

| 64 | I/O  |

| 65 | GND  |

| 66 | VCC  |

| 67 | I/O  |

| 68 | I/O  |

| 69 | I/O  |

| 70 | I/O  |

| 71 | I/O  |

| 72 | I/O  |

| 73 | I/O  |

| 74 | I/O  |

| 75 | GND  |

| 76 | I/O  |

| 77 | I/O  |

| 78 | I/O  |

| 79 | I/O  |

| 80 | VCCI |

| 81 | I/O  |

| 82 | I/O  |

| 83 | I/O  |

| 84 | I/O  |

| 85 | SDO  |

| 86 | I/O  |

| 87 | I/O  |

| 88 | I/O  |

| 89 | I/O  |

| 90 | I/O  |

| 91 | I/O  |

| 92 | I/O  |

| 93 | I/O  |

| 94 | I/O  |

| 95 | I/O  |

| 96 | I/O  |

| 97 | I/O  |

| 98 | GND  |

|    |      |