Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

E·XF

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | - ·                                                                       |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 125                                                                       |

| Number of Gates                | 24000                                                                     |

| Voltage - Supply               | 3V ~ 3.6V, 4.75V ~ 5.25V                                                  |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                           |

| Package / Case                 | 160-BQFP                                                                  |

| Supplier Device Package        | 160-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx16-fpqg160 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 40MX and 42MX FPGAs

# 3.1 General Description

Microsemi's 40MX and 42MX families offer a cost-effective design solution at 5V. The MX devices are single-chip solutions and provide high performance while shortening the system design and development cycle. MX devices can integrate and consolidate logic implemented in multiple PALs, CPLDs, and FPGAs. Example applications include high-speed controllers and address decoding, peripheral bus interfaces, DSP, and co-processor functions.

The MX device architecture is based on Microsemi's patented antifuse technology implemented in a 0.45µm triple-metal CMOS process. With capacities ranging from 3,000 to 54,000 system gates, the MX devices provide performance up to 250 MHz, are live on power-up and have one-fifth the standby power consumption of comparable FPGAs. MX FPGAs provide up to 202 user I/Os and are available in a wide variety of packages and speed grades.

A42MX24 and A42MX36 devices also feature multiPlex I/Os, which support mixed-voltage systems, enable programmable PCI, deliver high-performance operation at both 5.0V and 3.3V, and provide a low-power mode. The devices are fully compliant with the PCI local bus specification (version 2.1). They deliver 200 MHz on-chip operation and 6.1 ns clock-to-output performance.

The 42MX24 and 42MX36 devices include system-level features such as IEEE Standard 1149.1 (JTAG) Boundary Scan Testing and fast wide-decode modules. In addition, the A42MX36 device offers dual-port SRAM for implementing fast FIFOs, LIFOs, and temporary data storage. The storage elements can efficiently address applications requiring wide data path manipulation and can perform transformation functions such as those required for telecommunications, networking, and DSP.

All MX devices are fully tested over automotive and military temperature ranges. In addition, the largest member of the family, the A42MX36, is available in both CQ208 and CQ256 ceramic packages screened to MIL-STD-883 levels. For easy prototyping and conversion from plastic to ceramic, the CQ208 and PQ208 devices are pin-compatible.

# 3.2 MX Architectural Overview

The MX devices are composed of fine-grained building blocks that enable fast, efficient logic designs. All devices within these families are composed of logic modules, I/O modules, routing resources and clock networks, which are the building blocks for fast logic designs. In addition, the A42MX36 device contains embedded dual-port SRAM modules, which are optimized for high-speed data path functions such as FIFOs, LIFOs and scratch pad memory. A42MX24 and A42MX36 also contain wide-decode modules.

## 3.2.1 Logic Modules

The 40MX logic module is an eight-input, one-output logic circuit designed to implement a wide range of logic functions with efficient use of interconnect routing resources.(see the following figure).

The logic module can implement the four basic logic functions (NAND, AND, OR and NOR) in gates of two, three, or four inputs. The logic module can also implement a variety of D-latches, exclusivity functions, AND-ORs and OR-ANDs. No dedicated hard-wired latches or flip-flops are required in the array; latches and flip-flops can be constructed from logic modules whenever required in the application.

### 3.2.3.3 Antifuse Structures

An antifuse is a "normally open" structure. The use of antifuses to implement a programmable logic device results in highly testable structures as well as efficient programming algorithms. There are no pre-existing connections; temporary connections can be made using pass transistors. These temporary connections can isolate individual antifuses to be programmed and individual circuit structures to be tested, which can be done before and after programming. For instance, all metal tracks can be tested for continuity and shorts between adjacent tracks, and the functionality of all logic modules can be verified.

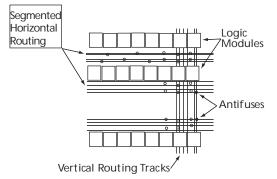

### Figure 7 • MX Routing Structure

### 3.2.4 Clock Networks

The 40MX devices have one global clock distribution network (CLK). A signal can be put on the CLK network by being routed through the CLKBUF buffer.

In 42MX devices, there are two low-skew, high-fanout clock distribution networks, referred to as CLKA and CLKB. Each network has a clock module (CLKMOD) that can select the source of the clock signal from any of the following (Figure 8, page 11):

- Externally from the CLKA pad, using CLKBUF buffer

- Externally from the CLKB pad, using CLKBUF buffer

- Internally from the CLKINTA input, using CLKINT buffer

- Internally from the CLKINTB input, using CLKINT buffer

The clock modules are located in the top row of I/O modules. Clock drivers and a dedicated horizontal clock track are located in each horizontal routing channel.

Clock input pads in both 40MX and 42MX devices can also be used as normal I/Os, bypassing the clock networks.

The A42MX36 device has four additional register control resources, called quadrant clock networks (Figure 9, page 11). Each quadrant clock provides a local, high-fanout resource to the contiguous logic modules within its quadrant of the device. Quadrant clock signals can originate from specific I/O pins or from the internal array and can be used as a secondary register clock, register clear, or output enable.

## 3.3.7 Low Power Mode

42MX devices have been designed with a Low Power Mode. This feature, activated with setting the special LP pin to HIGH for a period longer than 800 ns, is particularly useful for battery-operated systems where battery life is a primary concern. In this mode, the core of the device is turned off and the device consumes minimal power with low standby current. In addition, all input buffers are turned off, and all outputs and bidirectional buffers are tristated. Since the core of the device is turned off, the states of the registers are lost. The device must be re-initialized when exiting Low Power Mode. I/Os can be driven during LP mode, and clock pins should be driven HIGH or LOW and should not float to avoid drawing current. To exit LP mode, the LP pin must be pulled LOW for over 200 µs to allow for charge pumps to power up, and device initialization will begin.

# 3.4 **Power Dissipation**

The general power consumption of MX devices is made up of static and dynamic power and can be expressed with the following equation.

## 3.4.1 General Power Equation

P = [ICCstandby + ICCactive]\*VCCI + IOL\*VOL\*N + IOH\*(VCCI - VOH)\*M

EQ 1

#### where:

- ICCstandby is the current flowing when no inputs or outputs are changing.

- ICCactive is the current flowing due to CMOS switching.

- IOL, IOH are TTL sink/source currents.

- VOL, VOH are TTL level output voltages.

- N equals the number of outputs driving TTL loads to VOL.

- M equals the number of outputs driving TTL loads to VOH.

Accurate values for N and M are difficult to determine because they depend on the family type, on design details, and on the system I/O. The power can be divided into two components: static and active.

### 3.4.2 Static Power Component

The static power due to standby current is typically a small component of the overall power consumption. Standby power is calculated for commercial, worst-case conditions. The static power dissipation by TTL loads depends on the number of outputs driving, and on the DC load current. For instance, a 32-bit bus sinking 4mA at 0.33V will generate 42mW with all outputs driving LOW, and 140mW with all outputs driving HIGH. The actual dissipation will average somewhere in between, as I/Os switch states with time.

## 3.4.3 Active Power Component

Power dissipation in CMOS devices is usually dominated by the dynamic power dissipation. Dynamic power consumption is frequency-dependent and is a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitances due to PC board traces and load device inputs. An additional component of the active power dissipation is the totem pole current in the CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

The power dissipated by a CMOS circuit can be expressed by the equation:

$$Power(\mu W) = C_{EO}^* VCCA2^* F(1)$$

where:

C<sub>EQ</sub> = Equivalent capacitance expressed in picofarads (pF)

EQ 2

3. All outputs unloaded. All inputs = VCC/VCCI or GND

# 3.8 3.3 V Operating Conditions

The following table shows 3.3 V operating conditions.

### Table 16 • Absolute Maximum Ratings for 40MX Devices\*

| Symbol           | Parameter           | Limits            | Units |

|------------------|---------------------|-------------------|-------|

| VCC              | DC Supply Voltage   | -0.5 to +7.0      | V     |

| VI               | Input Voltage       | -0.5 to VCC + 0.5 | V     |

| VO               | Output Voltage      | -0.5 to VCC + 0.5 | V     |

| t <sub>STG</sub> | Storage Temperature | -65 to + 150      | °C    |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

#### Table 17 • Absolute Maximum Ratings for 42MX Devices\*

| Symbol           | Parameter                   | Limits           | Units |

|------------------|-----------------------------|------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | -0.5 to +7.0     | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0     | V     |

| VI               | Input Voltage               | -0.5 to VCCI+0.5 | V     |

| VO               | Output Voltage              | -0.5 to VCCI+0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150      | °C    |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

#### Table 18 • Recommended Operating Conditions

| Parameter          | Commercial | Industrial | Military    | Units |

|--------------------|------------|------------|-------------|-------|

| Temperature Range* | 0 to +70   | -40 to +85 | -55 to +125 | °C    |

| VCC (40MX)         | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

| VCCA (42MX)        | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

| VCCI (42MX)        | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

**Note:** \*Ambient temperature (T<sub>A</sub>) is used for commercial and industrial grades; case temperature (T<sub>C</sub>) is used for military grades.

All the following tables show various specifications and operating conditions of 40MX and 42MX FPGAs.

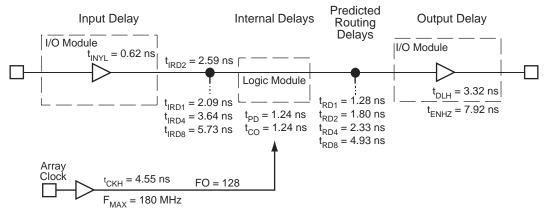

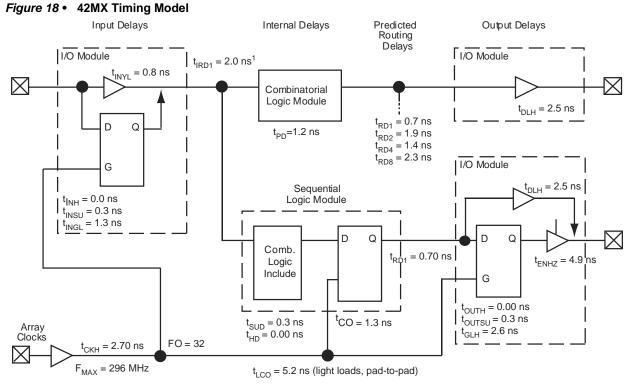

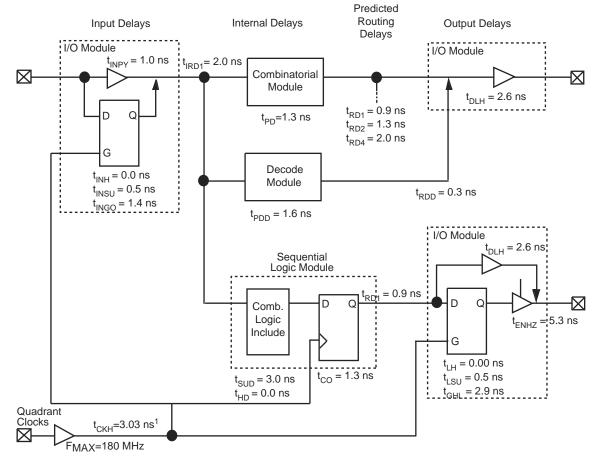

# 3.10 Timing Models

The following figures show various timing models.

### Figure 17 • 40MX Timing Model\*

Note: Values are shown for 40MX –3 speed devices at 5.0 V worst-case commercial conditions.

Note: 1. Input module predicted routing delay

Note: 2. Values are shown for A42MX09 -3 at 5.0 V worst-case commercial conditions.

Figure 19 • 42MX Timing Model (Logic Functions Using Quadrant Clocks)

Note: 1. Load-dependent

Note: 2. Values are shown for A42MX36 -3 at 5.0 V worst-case commercial conditions

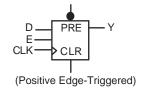

# 3.10.2 Sequential Module Timing Characteristics

The following figure shows sequential module timing characteristics.

### Figure 25 • Flip-Flops and Latches

Note: \*D represents all data functions involving A, B, and S for multiplexed flip-flops.

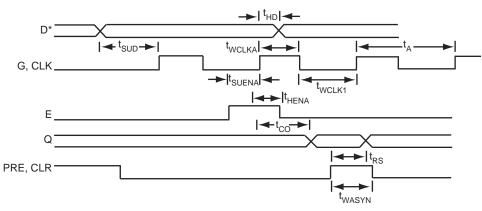

## 3.10.3 Sequential Timing Characteristics

The following figures show sequential timing characteristics.

### Figure 26 • Input Buffer Latches

|              | Temperat | ure   |      |      |      |      |       |

|--------------|----------|-------|------|------|------|------|-------|

| 40MX Voltage | –55°C    | –40°C | 0°C  | 25°C | 70°C | 85°C | 125°C |

| 3.60         | 0.83     | 0.85  | 0.92 | 0.96 | 1.14 | 1.25 | 1.53  |

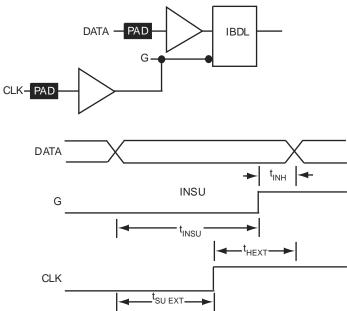

### Table 31 • 40MX Temperature and Voltage Derating Factors (Normalized to TJ = 25°C, VCC = 3.3 V)

### *Figure 37* • 40MX Junction Temperature and Voltage Derating Curves (Normalized to T<sub>J</sub> = 25°C, VCC = 3.3 V)

Voltage (V)

Note: This derating factor applies to all routing and propagation delays

### 3.11.5 PCI System Timing Specification

The following tables list the critical PCI timing parameters and the corresponding timing parameters for the MX PCI-compliant devices.

### 3.11.6 PCI Models

Microsemi provides synthesizable VHDL and Verilog-HDL models for a PCI Target interface, a PCI Target and Target+DMA Master interface. Contact the Microsemi sales representative for more details.

### Table 32 • Clock Specification for 33 MHz PCI

|                   |                | PCI  | A42MX | 24   | A42MX |      |      |       |

|-------------------|----------------|------|-------|------|-------|------|------|-------|

| Symbol            | Parameter      | Min. | Max.  | Min. | Max.  | Min. | Max. | Units |

| t <sub>CYC</sub>  | CLK Cycle Time | 30   | -     | 4.0  | -     | 4.0  | -    | ns    |

| t <sub>HIGH</sub> | CLK High Time  | 11   | -     | 1.9  | -     | 1.9  | -    | ns    |

| t <sub>LOW</sub>  | CLK Low Time   | 11   | -     | 1.9  | -     | 1.9  | -    | ns    |

### Table 33 • Timing Parameters for 33 MHz PCI

|                       |                                        | PCI            | A42N | IX24 | A42N             |      |                  |       |

|-----------------------|----------------------------------------|----------------|------|------|------------------|------|------------------|-------|

| Symbol                | Parameter                              | Min.           | Max. | Min. | Max.             | Min. | Max.             | Units |

| t <sub>VAL</sub>      | CLK to Signal Valid—Bused Signals      | 2              | 11   | 2.0  | 9.0              | 2.0  | 9.0              | ns    |

| t <sub>VAL(PTP)</sub> | CLK to Signal Valid—Point-to-Point     | 2 <sup>2</sup> | 12   | 2.0  | 9.0              | 2.0  | 9.0              | ns    |

| t <sub>ON</sub>       | Float to Active                        | 2              | _    | 2.0  | 4.0              | 2.0  | 4.0              | ns    |

| t <sub>OFF</sub>      | Active to Float                        | _              | 28   | -    | 8.3 <sup>1</sup> | _    | 8.3 <sup>1</sup> | ns    |

| t <sub>SU</sub>       | Input Set-Up Time to CLK—Bused Signals | 7              | _    | 1.5  | -                | 1.5  | -                | ns    |

|                   |                                   | –3 SI | beed | –2 Sp | beed | –1 Sp | eed  | Std S | peed | –F Sp | beed |       |

|-------------------|-----------------------------------|-------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Param             | eter / Description                | Min.  | Max. | Units |

| TTL Ou            | utput Module Timing <sup>4</sup>  |       |      |       |      |       |      |       |      |       |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                  |       | 3.3  |       | 3.8  |       | 4.3  |       | 5.1  |       | 7.2  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                   |       | 4.0  |       | 4.6  |       | 5.2  |       | 6.1  |       | 8.6  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH              |       | 3.7  |       | 4.3  |       | 4.9  |       | 5.8  |       | 8.0  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW               |       | 4.7  |       | 5.4  |       | 6.1  |       | 7.2  |       | 10.1 | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z              |       | 7.9  |       | 9.1  |       | 10.4 |       | 12.2 |       | 17.1 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z               |       | 5.9  |       | 6.8  |       | 7.7  |       | 9.0  |       | 12.6 | ns    |

| d <sub>TLH</sub>  | Delta LOW to<br>HIGH              |       | 0.02 |       | 0.02 |       | 0.03 |       | 0.03 |       | 0.04 | ns/pF |

| d <sub>THL</sub>  | Delta HIGH to<br>LOW              |       | 0.03 |       | 0.03 |       | 0.03 |       | 0.04 |       | 0.06 | ns/pF |

| CMOS              | Output Module Timing <sup>4</sup> |       |      |       |      |       |      |       |      |       |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                  |       | 3.9  |       | 4.5  |       | 5.1  |       | 6.05 |       | 8.5  | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                   |       | 3.4  |       | 3.9  |       | 4.4  |       | 5.2  |       | 7.3  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH              |       | 3.4  |       | 3.9  |       | 4.4  |       | 5.2  |       | 7.3  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW               |       | 4.9  |       | 5.6  |       | 6.4  |       | 7.5  |       | 10.5 | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z              |       | 7.9  |       | 9.1  |       | 10.4 |       | 12.2 |       | 17.0 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z               |       | 5.9  |       | 6.8  |       | 7.7  |       | 9.0  |       | 12.6 | ns    |

| d <sub>TLH</sub>  | Delta LOW to<br>HIGH              |       | 0.03 |       | 0.04 |       | 0.04 |       | 0.05 |       | 0.07 | ns/pF |

| d <sub>THL</sub>  | Delta HIGH to<br>LOW              |       | 0.02 |       | 0.02 |       | 0.03 |       | 0.03 |       | 0.04 | ns/pF |

# Table 34 •A40MX02 Timing Characteristics (Nominal 5.0 V Operation) (continued)<br/>(Worst-Case Commercial Conditions, VCC = 4.75 V, $T_J = 70^{\circ}$ C)

1. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance

2. Set-up times assume fanout of 3. Further testing information can be obtained from the Timer utility

3. The hold time for the DFME1A macro may be greater than 0 ns. Use the Timer tool from the Designer software to check

the hold time for this macro.

4. Delays based on 35pF loading

# Table 35 •A40MX02 Timing Characteristics (Nominal 3.3 V Operation)<br/>(Worst-Case Commercial Conditions, VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                  |                                 | –3 Sp          | beed | –2 Sp | beed | –1 S | beed | Std S | Speed | –F Speed |      |       |

|------------------|---------------------------------|----------------|------|-------|------|------|------|-------|-------|----------|------|-------|

| Parame           | eter / Description              | Min.           | Max. | Min.  | Max. | Min. | Max. | Min.  | Max.  | Min.     | Max. | Units |

| Logic M          | Module Propagation Delays       |                |      |       |      |      |      |       |       |          |      |       |

| t <sub>PD1</sub> | Single Module                   |                | 1.7  |       | 2.0  |      | 2.3  |       | 2.7   |          | 3.7  | ns    |

| t <sub>PD2</sub> | Dual-Module Macros              |                | 3.7  |       | 4.3  |      | 4.9  |       | 5.7   |          | 8.0  | ns    |

| t <sub>CO</sub>  | Sequential Clock-to-Q           |                | 1.7  |       | 2.0  |      | 2.3  |       | 2.7   |          | 3.7  | ns    |

| t <sub>GO</sub>  | Latch G-to-Q                    |                | 1.7  |       | 2.0  |      | 2.3  |       | 2.7   |          | 3.7  | ns    |

| t <sub>RS</sub>  | Flip-Flop (Latch) Reset-to-Q    |                | 1.7  |       | 2.0  |      | 2.3  |       | 2.7   |          | 3.7  | ns    |

| Logic M          | Module Predicted Routing Delays | s <sup>1</sup> |      |       |      |      |      |       |       |          |      |       |

# Table 36 •A40MX04 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                                    |                     | –3 Sp          | beed       | –2 S       | beed       | –1 S        | peed       | Std S      | Speed      | –F Sp        | beed         |       |

|--------------------|----------------------------------------------------|---------------------|----------------|------------|------------|------------|-------------|------------|------------|------------|--------------|--------------|-------|

| Parame             | ter / Description                                  |                     | Min.           | Max.       | Min.       | Max.       | Min.        | Max.       | Min.       | Max.       | Min.         | Max.         | Units |

| t <sub>HENA</sub>  | Flip-Flop (Latch)<br>Enable Hold                   |                     | 0.0            |            | 0.0        |            | 0.0         |            | 0.0        |            | 0.0          |              | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse V          | Vidth               | 3.3            |            | 3.8        |            | 4.3         |            | 5.0        |            | 7.0          |              | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse            | e Width             | 3.3            |            | 3.8        |            | 4.3         |            | 5.0        |            | 7.0          |              | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Inpu                               | t Period            | 4.8            |            | 5.6        |            | 6.3         |            | 7.5        |            | 10.4         |              | ns    |

| f <sub>MAX</sub>   | Flip-Flop (Latch)<br>Clock Frequency<br>(FO = 128) |                     |                | 181        |            | 167        |             | 154        |            | 134        |              | 80           | MHz   |

| Input M            | odule Propagation D                                | )elays              |                |            |            |            |             |            |            |            |              |              |       |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                      |                     |                | 0.7        |            | 0.8        |             | 0.9        |            | 1.1        |              | 1.5          | ns    |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                       |                     |                | 0.6        |            | 0.7        |             | 0.8        |            | 1.0        |              | 1.3          | ns    |

| Input M            | odule Predicted Rou                                | ting Delays         | s <sup>1</sup> |            |            |            |             |            |            |            |              |              |       |

| t <sub>IRD1</sub>  | FO = 1 Routing Dela                                | ау                  |                | 2.1        |            | 2.4        |             | 2.2        |            | 3.2        |              | 4.5          | ns    |

| t <sub>IRD2</sub>  | FO = 2 Routing Dela                                | ау                  |                | 2.6        |            | 3.0        |             | 3.4        |            | 4.0        |              | 5.6          | ns    |

| t <sub>IRD3</sub>  | FO = 3 Routing Dela                                | ау                  |                | 3.1        |            | 3.6        |             | 4.1        |            | 4.8        |              | 6.7          | ns    |

| t <sub>IRD4</sub>  | FO = 4 Routing Dela                                | ау                  |                | 3.6        |            | 4.2        |             | 4.8        |            | 5.6        |              | 7.8          | ns    |

| t <sub>IRD8</sub>  | FO = 8 Routing Dela                                | ау                  |                | 5.7        |            | 6.6        |             | 7.5        |            | 8.8        |              | 12.4         | ns    |

| Global (           | Clock Network                                      |                     |                |            |            |            |             |            |            |            |              |              |       |

| t <sub>СКН</sub>   | Input Low to HIGH                                  | FO = 16<br>FO = 128 |                | 4.6<br>4.6 |            | 5.3<br>5.3 |             | 6.0<br>6.0 |            | 7.0<br>7.0 |              | 9.8<br>9.8   | ns    |

| t <sub>CKL</sub>   | Input High to LOW                                  | FO = 16<br>FO = 128 |                | 4.8<br>4.8 |            | 5.6<br>5.6 |             | 6.3<br>6.3 |            | 7.4<br>7.4 |              | 10.4<br>10.4 | ns    |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH                        | FO = 16<br>FO = 128 | 2.2<br>2.4     |            | 2.6<br>2.7 |            | 2.9<br>3.1  |            | 3.4<br>3.6 |            | 4.8<br>5.1   |              | ns    |

| t <sub>PWL</sub>   | Minimum Pulse<br>Width LOW                         | FO = 16<br>FO = 128 | 2.2<br>2.4     |            | 2.6<br>2.7 |            | 2.9<br>3.01 |            | 3.4<br>3.6 |            | 4.8<br>5.1   |              | ns    |

| t <sub>CKSW</sub>  | Maximum Skew                                       | FO = 16<br>FO = 128 |                | 0.4<br>0.5 |            | 0.5<br>0.6 |             | 0.5<br>0.7 |            | 0.6<br>0.8 |              | 0.8<br>1.2   | ns    |

| t <sub>P</sub>     | Minimum Period                                     | FO = 16<br>FO = 128 | 4.7<br>4.8     |            | 5.4<br>5.6 |            | 6.1<br>6.3  |            | 7.2<br>7.5 |            | 10.0<br>10.4 |              | ns    |

| f <sub>MAX</sub>   | Maximum<br>Frequency                               | FO = 16<br>FO = 128 |                | 188<br>181 |            | 175<br>168 |             | 160<br>154 |            | 139<br>134 |              | 83<br>80     | MHz   |

| TTL Out            | tput Module Timing <sup>4</sup>                    | ,                   |                |            |            |            |             |            |            |            |              |              |       |

| t <sub>DLH</sub>   | Data-to-Pad HIGH                                   |                     |                | 3.3        |            | 3.8        |             | 4.3        |            | 5.1        |              | 7.2          | ns    |

| t <sub>DHL</sub>   | Data-to-Pad LOW                                    |                     |                | 4.0        |            | 4.6        |             | 5.2        |            | 6.1        |              | 8.6          | ns    |

| t <sub>ENZH</sub>  | Enable Pad Z to HIC                                | ЭH                  |                | 3.7        |            | 4.3        |             | 4.9        |            | 5.8        |              | 8.0          | ns    |

| t <sub>ENZL</sub>  | Enable Pad Z to LO                                 | W                   |                | 4.7        |            | 5.4        |             | 6.1        |            | 7.2        |              | 10.1         | ns    |

| t <sub>ENHZ</sub>  | Enable Pad HIGH to                                 | Σ                   |                | 7.9        |            | 9.1        |             | 10.4       |            | 12.2       |              | 17.1         | ns    |

# Table 37 • A40MX04 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial Conditions, VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                    | –3 SI | peed | –2 S | beed | –1 Sp | beed | Std S | Speed | –F Sj | peed |       |

|--------------------|----------------------------------------------------|-------|------|------|------|-------|------|-------|-------|-------|------|-------|

| Paramet            | er / Description                                   | Min.  | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min.  | Max. | Units |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width      | 4.6   |      | 5.3  |      | 5.6   |      | 7.0   |       | 9.8   |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width      | 4.6   |      | 5.3  |      | 5.6   |      | 7.0   |       | 9.8   |      | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period                       | 6.8   |      | 7.8  |      | 8.9   |      | 10.4  |       | 14.6  |      | ns    |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock<br>Frequency<br>(FO = 128) |       | 109  |      | 101  |       | 92   |       | 80    |       | 48   | MHz   |

| Input Mo           | odule Propagation Delays                           |       |      |      |      |       |      |       |       |       |      |       |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                      |       | 1.0  |      | 1.1  |       | 1.3  |       | 1.5   |       | 2.1  | ns    |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                       |       | 0.9  |      | 1.0  |       | 1.1  |       | 1.3   |       | 1.9  | ns    |

| PQ144      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX09 Function |  |

| 80         | GNDI             |  |

| 81         | NC               |  |

| 82         | I/O              |  |

| 83         | I/O              |  |

| 84         | I/O              |  |

| 85         | I/O              |  |

| 86         | I/O              |  |

| 87         | I/O              |  |

| 88         | VKS              |  |

| 89         | VPP              |  |

| 90         | VCC              |  |

| 91         | VCCI             |  |

| 92         | NC               |  |

| 93         | VSV              |  |

| 94         | I/O              |  |

| 95         | I/O              |  |

| 96         | I/O              |  |

| 97         | I/O              |  |

| 98         | I/O              |  |

| 99         | I/O              |  |

| 100        | GND              |  |

| 101        | GNDI             |  |

| 102        | NC               |  |

| 103        | I/O              |  |

| 104        | I/O              |  |

| 105        | I/O              |  |

| 106        | I/O              |  |

| 107        | I/O              |  |

| 108        | I/O              |  |

| 109        | I/O              |  |

| 110        | SDI              |  |

| 111        | I/O              |  |

| 112        | I/O              |  |

| 113        | I/O              |  |

| 114        | I/O              |  |

| 115        | I/O              |  |

| 116        | GNDQ             |  |

### Table 51 • PQ144

### Table 52 • PQ160

| PQ160      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 95         | I/O              | I/O              | I/O              |

| 96         | I/O              | I/O              | WD, I/O          |

| 97         | I/O              | I/O              | I/O              |

| 98         | VCCA             | VCCA             | VCCA             |

| 99         | GND              | GND              | GND              |

| 100        | NC               | I/O              | I/O              |

| 101        | I/O              | I/O              | I/O              |

| 102        | I/O              | I/O              | I/O              |

| 103        | NC               | I/O              | I/O              |

| 104        | I/O              | I/O              | I/O              |

| 105        | I/O              | I/O              | I/O              |

| 106        | I/O              | I/O              | WD, I/O          |

| 107        | I/O              | I/O              | WD, I/O          |

| 108        | I/O              | I/O              | I/O              |

| 109        | GND              | GND              | GND              |

| 110        | NC               | I/O              | I/O              |

| 111        | I/O              | I/O              | WD, I/O          |

| 112        | I/O              | I/O              | WD, I/O          |

| 13         | I/O              | I/O              | I/O              |

| 114        | NC               | VCCI             | VCCI             |

| 115        | I/O              | I/O              | WD, I/O          |

| 116        | NC               | I/O              | WD, I/O          |

| 117        | I/O              | I/O              | I/O              |

| 118        | I/O              | I/O              | TDI, I/O         |

| 119        | I/O              | I/O              | TMS, I/O         |

| 120        | GND              | GND              | GND              |

| 121        | I/O              | I/O              | I/O              |

| 122        | I/O              | I/O              | I/O              |

| 123        | I/O              | I/O              | I/O              |

| 124        | NC               | I/O              | I/O              |

| 125        | GND              | GND              | GND              |

| 126        | I/O              | I/O              | I/O              |

| 127        | I/O              | I/O              | I/O              |

| 128        | I/O              | I/O              | I/O              |

| 129        | NC               | I/O              | I/O              |

| 130        | GND              | GND              | GND              |

| 131        | I/O              | I/O              | I/O              |

| PQ240      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 163        | WD, I/O          |

| 164        | WD, I/O          |

| 165        | I/O              |

| 166        | QCLKA, I/O       |

| 167        | I/O              |

| 168        | I/O              |

| 169        | I/O              |

| 170        | I/O              |

| 171        | I/O              |

| 172        | VCCI             |

| 173        | I/O              |

| 174        | WD, I/O          |

| 175        | WD, I/O          |

| 176        | I/O              |

| 177        | I/O              |

| 178        | TDI, I/O         |

| 179        | TMS, I/O         |

| 180        | GND              |

| 181        | VCCA             |

| 82         | GND              |

| 183        | I/O              |

| 184        | I/O              |

| 185        | I/O              |

| 186        | I/O              |

| 187        | I/O              |

| 188        | I/O              |

| 89         | I/O              |

| 190        | I/O              |

| 191        | I/O              |

| 192        | VCCI             |

| 193        | I/O              |

| 194        | I/O              |

| 195        | I/O              |

| 196        | I/O              |

| 197        | I/O              |

| 198        | I/O              |

| 199        | I/O              |

| PQ240      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 200        | I/O              |

| 201        | I/O              |

| 202        | I/O              |

| 203        | I/O              |

| 204        | I/O              |

| 205        | I/O              |

| 206        | VCCA             |

| 207        | I/O              |

| 208        | I/O              |

| 209        | VCCA             |

| 210        | VCCI             |

| 211        | I/O              |

| 212        | I/O              |

| 213        | I/O              |

| 214        | I/O              |

| 215        | I/O              |

| 216        | I/O              |

| 217        | I/O              |

| 218        | I/O              |

| 219        | VCCA             |

| 220        | I/O              |

| 221        | I/O              |

| 222        | I/O              |

| 223        | I/O              |

| 224        | I/O              |

| 225        | I/O              |

| 226        | I/O              |

| 227        | VCCI             |

| 228        | I/O              |

| 229        | I/O              |

| 230        | I/O              |

| 231        | I/O              |

| 232        | I/O              |

| 233        | I/O              |

| 234        | I/O              |

| 235        | I/O              |

| 236        | I/O              |

| CQ208      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 148        | I/O              |

| 149        | I/O              |

| 150        | GND              |

| 151        | I/O              |

| 152        | I/O              |

| 153        | I/O              |

| 154        | I/O              |

| 155        | I/O              |

| 156        | I/O              |

| 157        | GND              |

| 158        | I/O              |

| 159        | SDI, I/O         |

| 160        | I/O              |

| 161        | WD, I/O          |

| 162        | WD, I/O          |

| 163        | I/O              |

| 164        | VCCI             |

| 165        | I/O              |

| 166        | I/O              |

| 167        | I/O              |

| 168        | WD, I/O          |

| 169        | WD, I/O          |

| 170        | I/O              |

| 71         | QCLKD, I/O       |

| 72         | I/O              |

| 73         | I/O              |

| 174        | I/O              |

| 175        | I/O              |

| 176        | WD, I/O          |

| 177        | WD, I/O          |

| 178        | PRA, I/O         |

| 179        | I/O              |

| 180        | CLKA, I/O        |

| 181        | I/O              |

| 182        | VCCI             |

| 183        | VCCA             |

| 184        | GND              |

| CQ256      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 96         | VCCA             |

| 97         | GND              |

| 98         | GND              |

| 99         | I/O              |

| 100        | I/O              |

| 101        | I/O              |

| 102        | I/O              |

| 103        | I/O              |

| 104        | I/O              |

| 105        | WD, I/O          |

| 106        | WD, I/O          |

| 107        | I/O              |

| 108        | I/O              |

| 109        | WD, I/O          |

| 110        | WD, I/O          |

| 111        | I/O              |

| 112        | QCLKA, I/O       |

| 113        | I/O              |

| 114        | GND              |

| 115        | I/O              |

| 116        | I/O              |

| 117        | I/O              |

| 118        | I/O              |

| 119        | VCCI             |

| 120        | I/O              |

| 121        | WD, I/O          |

| 122        | WD, I/O          |

| 123        | I/O              |

| 124        | I/O              |

| 125        | I/O              |

| 126        | I/O              |

| 127        | GND              |

| 128        | NC               |

| 129        | NC               |

| 130        | NC               |

| 131        | GND              |

| 132        | I/O              |

| CQ256      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 207        | I/O              |

| 208        | I/O              |

| 209        | QCLKC, I/O       |

| 210        | I/O              |

| 211        | WD, I/O          |

| 212        | WD, I/O          |

| 213        | I/O              |

| 214        | I/O              |

| 215        | WD, I/O          |

| 216        | WD, I/O          |

| 217        | I/O              |

| 218        | PRB, I/O         |

| 219        | I/O              |

| 220        | CLKB, I/O        |

| 221        | I/O              |

| 222        | GND              |

| 223        | GND              |

| 224        | VCCA             |

| 225        | VCCI             |

| 226        | I/O              |

| 227        | CLKA, I/O        |

| 228        | I/O              |

| 229        | PRA, I/O         |

| 230        | I/O              |

| 231        | I/O              |

| 232        | WD, I/O          |

| 233        | WD, I/O          |

| 234        | I/O              |

| 235        | I/O              |

| 236        | I/O              |

| 237        | I/O              |

| 238        | I/O              |

| 239        | I/O              |

| 240        | QCLKD, I/O       |

| 241        | I/O              |

| 242        | WD, I/O          |

| 243        | GND              |

### Figure 53 • CQ172

### Table 62 • CQ172

| CQ172      |                     |  |

|------------|---------------------|--|

| Pin Number | A42MX16<br>Function |  |

| 1          | MODE                |  |

| 2          | I/O                 |  |

| 3          | I/O                 |  |

| 1          | I/O                 |  |

| 5          | I/O                 |  |

| 6          | I/O                 |  |

| 7          | GND                 |  |

| 3          | I/O                 |  |

| )          | I/O                 |  |

| 0          | I/O                 |  |

| 1          | I/O                 |  |

| 2          | VCC                 |  |

| 13         | I/O                 |  |

| 14         | I/O                 |  |

| 5          | I/O                 |  |

| 16         | I/O                 |  |

| 7          | GND                 |  |

| 8          | I/O                 |  |

| 19         | I/O                 |  |

| 20         | I/O                 |  |

|            |                     |  |

| 21 | I/O    |

|----|--------|

| 22 | GND    |

| 23 | VCCI   |

| 24 | VSV    |

| 25 | I/O    |

| 26 | I/O    |

| 27 | VCC    |

| 28 | I/O    |

| 29 | I/O    |

| 30 | I/O    |

| 31 | I/O    |

| 32 | GND    |

| 33 | I/O    |

| 34 | I/O    |

| 35 | I/O    |

| 36 | I/O    |

| 37 | GND    |

| 38 | I/O    |

| 39 | I/O    |

| 40 | I/O    |

| 41 | I/O    |

| 42 | I/O    |

| 43 | I/O    |

| 44 | BININ  |

| 45 | BINOUT |

| 46 | I/O    |

| 47 | I/O    |

| 48 | I/O    |

| 49 | I/O    |

| 50 | VCCI   |

| 51 | I/O    |

| 52 | I/O    |

| 53 | I/O    |

| 54 | I/O    |

| 55 | GND    |

| 56 | I/O    |

| 57 | I/O    |

| 58 | I/O    |

|    |        |