# E·XFL

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | -                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 140                                                                       |

| Number of Gates                | 24000                                                                     |

| Voltage - Supply               | 3V ~ 3.6V, 4.5V ~ 5.5V                                                    |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | -40°C ~ 85°C (TA)                                                         |

| Package / Case                 | 208-BFQFP                                                                 |

| Supplier Device Package        | 208-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx16-pqg208i |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

## 2 40MX and 42MX FPGA Families

## 2.1 Features

The following sections list out various features of the 40MX and 42MX FPGA family devices.

## 2.1.1 High Capacity

- Single-Chip ASIC Alternative

- 3,000 to 54,000 System Gates

- Up to 2.5 kbits Configurable Dual-Port SRAM

- Fast Wide-Decode Circuitry

- Up to 202 User-Programmable I/O Pins

## 2.1.2 High Performance

- 5.6 ns Clock-to-Out

- 250 MHz Performance

- 5 ns Dual-Port SRAM Access

- 100 MHz FIFOs

- 7.5 ns 35-Bit Address Decode

## 2.1.3 HiRel Features

- Commercial, Industrial, Automotive, and Military Temperature Plastic Packages

- Commercial, Military Temperature, and MIL-STD-883 Ceramic Packages

- QML Certification

- Ceramic Devices Available to DSCC SMD

## 2.1.4 Ease of Integration

- Mixed-Voltage Operation (5.0 V or 3.3 V for core and I/Os), with PCI-Compliant I/Os

- Up to 100% Resource Utilization and 100% Pin Locking

- Deterministic, User-Controllable Timing

- Unique In-System Diagnostic and Verification Capability with Silicon Explorer II

## Low Power Consumption IEEE Standard 1149.1 (JTAG) Boundary Scan Testing

## 2.2 **Product Profile**

The following table gives the features of the products.

## Table 1 • Product profile

| Device               | A40MX02 | A40MX04 | A42MX09 | A42MX16 | A42MX24 | A42MX36 |

|----------------------|---------|---------|---------|---------|---------|---------|

| Capacity             |         |         |         |         |         |         |

| System Gates         | 3,000   | 6,000   | 14,000  | 24,000  | 36,000  | 54,000  |

| SRAM Bits            | -       | -       | _       | -       | _       | 2,560   |

| Logic Modules        |         |         |         |         |         |         |

| Sequential           | _       | _       | 348     | 624     | 954     | 1,230   |

| Combinatorial        | 295     | 547     | 336     | 608     | 912     | 1,184   |

| Decode               | -       | -       | _       | -       | 24      | 24      |

| Clock-to-Out         | 9.5 ns  | 9.5 ns  | 5.6 ns  | 6.1 ns  | 6.1 ns  | 6.3 ns  |

| SRAM Modules         |         |         |         |         |         |         |

| (64x4 or 32x8)       | _       | -       | _       | _       | _       | 10      |

| Dedicated Flip-Flops | _       | _       | 348     | 624     | 954     | 1,230   |

## 2.6 Temperature Grade Offerings

## Table 4 • Temperature Grade Offerings

| Package  | A40MX02    | A40MX04    | A42MX09    | A42MX16    | A42MX24    | A42MX36    |

|----------|------------|------------|------------|------------|------------|------------|

| PLCC 44  | C, I, M    | C, I, M    |            |            |            |            |

| PLCC 68  | C, I, A, M | C, I, M    |            |            |            |            |

| PLCC 84  |            | C, I, A, M | C, I, A, M | C, I, M    | C, I, M    |            |

| PQFP 100 | C, I, A, M | C, I, A, M | C, I, A, M | C, I, M    |            |            |

| PQFP 144 |            |            | С          |            |            |            |

| PQFP 160 |            |            | C, I, A, M | C, I, M    | C, I, A, M |            |

| PQFP 208 |            |            |            | C, I, A, M | C, I, A, M | C, I, A, M |

| PQFP 240 |            |            |            |            |            | C, I, A, M |

| VQFP 80  | C, I, A, M | C, I, A, M |            |            |            |            |

| VQFP 100 |            |            | C, I, A, M | C, I, A, M |            |            |

| TQFP 176 |            |            | C, I, A, M | C, I, A, M | C, I, A, M |            |

| PBGA 272 |            |            |            |            |            | C, I, M    |

| CQFP 172 |            |            |            | С, М, В    |            |            |

| CQFP 208 |            |            |            |            |            | С, М, В    |

| CQFP 256 |            |            |            |            |            | С, М, В    |

| CPGA 132 |            |            | С, М, В    |            |            |            |

Note: C = Commercial

I = Industrial

A = Automotive

M = Military

B = MIL-STD-883 Class B

## 2.7 Speed Grade Offerings

## Table 5 • Speed Grade Offerings

|   | – F | Std | –1 | -2 | -3 |  |

|---|-----|-----|----|----|----|--|

| С | Р   | Р   | Р  | Р  | Р  |  |

| Ι |     | Р   | Р  | Р  | Р  |  |

| A |     | Р   |    |    |    |  |

| Μ |     | Р   | Р  |    |    |  |

| В |     | Р   | Р  |    |    |  |

**Note:** See the 40MX and 42MX Automotive Family FPGAs datasheet for details on automotive-grade MX offerings.

Contact your local *Microsemi Sales representative* for device availability.

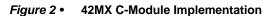

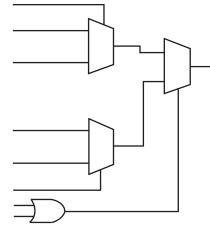

The 42MX devices contain three types of logic modules: combinatorial (C-modules), sequential (S-modules) and decode (D-modules). The following figure illustrates the combinatorial logic module. The S-module, shown in Figure 4, page 8, implements the same combinatorial logic function as the C-module while adding a sequential element. The sequential element can be configured as either a D-flip-flop or a transparent latch. The S-module register can be bypassed so that it implements purely combinatorial logic.

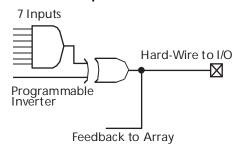

### Figure 5 • A42MX24 and A42MX36 D-Module Implementation

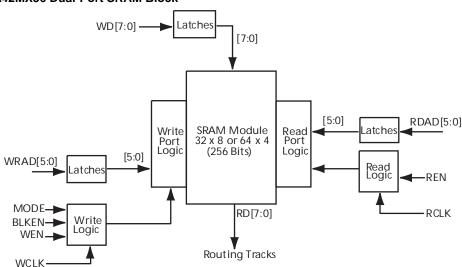

### Figure 6 • A42MX36 Dual-Port SRAM Block

## 3.2.3 Routing Structure

The MX architecture uses vertical and horizontal routing tracks to interconnect the various logic and I/O modules. These routing tracks are metal interconnects that may be continuous or split into segments. Varying segment lengths allow the interconnect of over 90% of design tracks to occur with only two antifuse connections. Segments can be joined together at the ends using antifuses to increase their lengths up to the full length of the track. All interconnects can be accomplished with a maximum of four antifuses.

## 3.2.3.1 Horizontal Routing

Horizontal routing tracks span the whole row length or are divided into multiple segments and are located in between the rows of modules. Any segment that spans more than one-third of the row length is considered a long horizontal segment. A typical channel is shown in Figure 7, page 10. Within horizontal routing, dedicated routing tracks are used for global clock networks and for power and ground tie-off tracks. Non-dedicated tracks are used for signal nets.

## 3.2.3.2 Vertical Routing

Another set of routing tracks run vertically through the module. There are three types of vertical tracks: input, output, and long. Long tracks span the column length of the module, and can be divided into multiple segments. Each segment in an input track is dedicated to the input of a particular module; each segment in an output track is dedicated to the output of a particular module. Long segments are uncommitted and can be assigned during routing.

Each output segment spans four channels (two above and two below), except near the top and bottom of the array, where edge effects occur. Long vertical tracks contain either one or two segments. An example of vertical routing tracks and segments is shown in Figure 7, page 10.

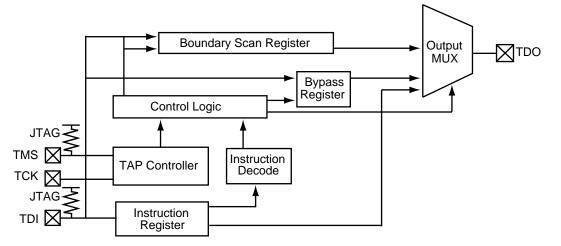

Each I/O cell has three boundary-scan register cells, each with a serial-in, serial-out, parallel-in, and parallel-out pin. The serial pins are used to serially connect all the boundary-scan register cells in a device into a boundary-scan register chain, which starts at the TDI pin and ends at the TDO pin. The parallel ports are connected to the internal core logic tile and the input, output and control ports of an I/O buffer to capture and load data into the register to control or observe the logic state of each I/O.

## Figure 14 • 42MX IEEE 1149.1 Boundary Scan Circuitry

### Table 9 • Test Access Port Descriptions

| Port                      | Description                                                                                                                                                                                                                                               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMS<br>(Test Mode Select) | Serial input for the test logic control bits. Data is captured on the rising edge of the test logic clock (TCK).                                                                                                                                          |

| TCK<br>(Test Clock Input) | Dedicated test logic clock used serially to shift test instruction, test data, and control inputs on the rising edge of the clock, and serially to shift the output data on the falling edge of the clock. The maximum clock frequency for TCK is 20 MHz. |

| TDI<br>(Test Data Input)  | Serial input for instruction and test data. Data is captured on the rising edge of the test logic clock.                                                                                                                                                  |

| TDO<br>(Test Data Output) | Serial output for test instruction and data from the test logic. TDO is set to an Inactive Drive state (high impedance) when data scanning is not in progress.                                                                                            |

#### Table 10 • Supported BST Public Instructions

| Instruction    | IR Code<br>(IR2.IR0) | Instruction<br>Type | Description                                                                                                                                                                  |

|----------------|----------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000                  | Mandatory           | Allows the external circuitry and board-level interconnections to be<br>tested by forcing a test pattern at the output pins and capturing test<br>results at the input pins. |

| SAMPLE/PRELOAD | 001                  | Mandatory           | Allows a snapshot of the signals at the device pins to be captured and examined during operation                                                                             |

| HIGH Z         | 101                  | Optional            | Tristates all I/Os to allow external signals to drive pins. See the IEEE Standard 1149.1 specification.                                                                      |

| CLAMP          | 110                  | Optional            | Allows state of signals driven from component pins to be determined<br>from the Boundary-Scan Register. See the IEEE Standard 1149.1<br>specification for details.           |

| BYPASS         | 111                  | Mandatory           | Enables the bypass register between the TDI and TDO pins. The test data passes through the selected device to adjacent devices in the test chain.                            |

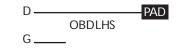

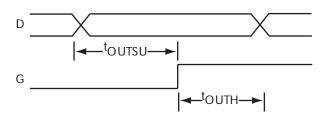

## Figure 27 • Output Buffer Latches

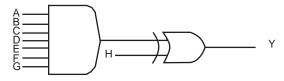

## 3.10.4 Decode Module Timing

The following figure shows decode module timing.

## Figure 28 • Decode Module Timing

## 3.10.5 SRAM Timing Characteristics

The following figure shows SRAM timing characteristics.

## Figure 29 • SRAM Timing Characteristics

| Write Port                                         |                                         | Read Port                                    |  |

|----------------------------------------------------|-----------------------------------------|----------------------------------------------|--|

| <br>WRAD [5:0]<br>BLKEN<br>WEN<br>WCLK<br>WD [7:0] | RAM Array<br>32x8 or 64x4<br>(256 Bits) | RDAD [5:0]<br>LEW<br>REN<br>RCLK<br>RD [7:0] |  |

## 3.10.6 Dual-Port SRAM Timing Waveforms

The following figures show dual-port SRAM timing waveforms.

| Table 31 • | 40MX Temperature and Voltage Derating Factors (Normalized to TJ = 25°C, VCC = 3.3 V) |

|------------|--------------------------------------------------------------------------------------|

|            |                                                                                      |

|              | Temperat | ure   |      |      |      |      |       |

|--------------|----------|-------|------|------|------|------|-------|

| 40MX Voltage | –55°C    | –40°C | 0°C  | 25°C | 70°C | 85°C | 125°C |

| 3.60         | 0.83     | 0.85  | 0.92 | 0.96 | 1.14 | 1.25 | 1.53  |

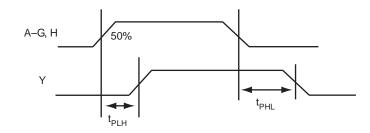

## *Figure 37* • 40MX Junction Temperature and Voltage Derating Curves (Normalized to T<sub>J</sub> = 25°C, VCC = 3.3 V)

Voltage (V)

Note: This derating factor applies to all routing and propagation delays

## 3.11.5 PCI System Timing Specification

The following tables list the critical PCI timing parameters and the corresponding timing parameters for the MX PCI-compliant devices.

## 3.11.6 PCI Models

Microsemi provides synthesizable VHDL and Verilog-HDL models for a PCI Target interface, a PCI Target and Target+DMA Master interface. Contact the Microsemi sales representative for more details.

### Table 32 • Clock Specification for 33 MHz PCI

|                   |                | PCI A42MX24 |      | 24   | A42MX |      |      |       |

|-------------------|----------------|-------------|------|------|-------|------|------|-------|

| Symbol            | Parameter      | Min.        | Max. | Min. | Max.  | Min. | Max. | Units |

| t <sub>CYC</sub>  | CLK Cycle Time | 30          | _    | 4.0  | -     | 4.0  | -    | ns    |

| t <sub>HIGH</sub> | CLK High Time  | 11          | _    | 1.9  | -     | 1.9  | -    | ns    |

| t <sub>LOW</sub>  | CLK Low Time   | 11          | _    | 1.9  | -     | 1.9  | -    | ns    |

## Table 33 • Timing Parameters for 33 MHz PCI

|                       |                                        | PCI            | A42N | IX24 | A42MX36          |      |                  |       |

|-----------------------|----------------------------------------|----------------|------|------|------------------|------|------------------|-------|

| Symbol                | Parameter                              | Min.           | Max. | Min. | Max.             | Min. | Max.             | Units |

| t <sub>VAL</sub>      | CLK to Signal Valid—Bused Signals      | 2              | 11   | 2.0  | 9.0              | 2.0  | 9.0              | ns    |

| t <sub>VAL(PTP)</sub> | CLK to Signal Valid—Point-to-Point     | 2 <sup>2</sup> | 12   | 2.0  | 9.0              | 2.0  | 9.0              | ns    |

| t <sub>ON</sub>       | Float to Active                        | 2              | _    | 2.0  | 4.0              | 2.0  | 4.0              | ns    |

| t <sub>OFF</sub>      | Active to Float                        | _              | 28   | -    | 8.3 <sup>1</sup> | _    | 8.3 <sup>1</sup> | ns    |

| t <sub>SU</sub>       | Input Set-Up Time to CLK—Bused Signals | 7              | _    | 1.5  | -                | 1.5  | -                | ns    |

# Table 34 •A40MX02 Timing Characteristics (Nominal 5.0 V Operation) (continued)<br/>(Worst-Case Commercial Conditions, VCC = 4.75 V, $T_J = 70^{\circ}$ C)

|                   |                             |                     | -3 Sp            | beed       | –2 Sp      | beed       | –1 Sp       | eed        | Std S      | peed       | –F Sp        | beed         |       |

|-------------------|-----------------------------|---------------------|------------------|------------|------------|------------|-------------|------------|------------|------------|--------------|--------------|-------|

| Param             | eter / Description          |                     | Min.             | Max.       | Min.       | Max.       | Min.        | Max.       | Min.       | Max.       | Min.         | Max.         | Units |

| Input N           | Iodule Propagation          | Delays              |                  |            |            |            |             |            |            |            |              |              |       |

| t <sub>INYH</sub> | Pad-to-Y HIGH               |                     |                  | 0.7        |            | 0.8        |             | 0.9        |            | 1.1        |              | 1.5          | ns    |

| t <sub>INYL</sub> | Pad-to-Y LOW                |                     |                  | 0.6        |            | 0.7        |             | 0.8        |            | 1.0        |              | 1.3          | ns    |

| Input N           | Iodule Predicted Ro         | outing Dela         | iys <sup>1</sup> |            |            |            |             |            |            |            |              |              |       |

| t <sub>IRD1</sub> | FO = 1 Routing De           | lay                 |                  | 2.1        |            | 2.4        |             | 2.2        |            | 3.2        |              | 4.5          | ns    |

| t <sub>IRD2</sub> | FO = 2 Routing De           | lay                 |                  | 2.6        |            | 3.0        |             | 3.4        |            | 4.0        |              | 5.6          | ns    |

| t <sub>IRD3</sub> | FO = 3 Routing De           | lay                 |                  | 3.1        |            | 3.6        |             | 4.1        |            | 4.8        |              | 6.7          | ns    |

| t <sub>IRD4</sub> | FO = 4 Routing De           | lay                 |                  | 3.6        |            | 4.2        |             | 4.8        |            | 5.6        |              | 7.8          | ns    |

| t <sub>IRD8</sub> | FO = 8 Routing De           | lay                 |                  | 5.7        |            | 6.6        |             | 7.5        |            | 8.8        |              | 12.4         | ns    |

| Global            | Clock Network               |                     |                  |            |            |            |             |            |            |            |              |              |       |

| t <sub>CKH</sub>  | Input Low to HIGH           | FO = 16<br>FO = 128 |                  | 4.6<br>4.6 |            | 5.3<br>5.3 |             | 6.0<br>6.0 |            | 7.0<br>7.0 |              | 9.8<br>9.8   | ns    |

| t <sub>CKL</sub>  | Input High to LOW           | FO = 16<br>FO = 128 |                  | 4.8<br>4.8 |            | 5.6<br>5.6 |             | 6.3<br>6.3 |            | 7.4<br>7.4 |              | 10.4<br>10.4 | ns    |

| t <sub>PWH</sub>  | Minimum Pulse<br>Width HIGH | FO = 16<br>FO = 128 | 2.2<br>2.4       |            | 2.6<br>2.7 |            | 2.9<br>3.1  |            | 3.4<br>3.6 |            | 4.8<br>5.1   |              | ns    |

| t <sub>PWL</sub>  | Minimum Pulse<br>Width LOW  | FO = 16<br>FO = 128 | 2.2<br>2.4       |            | 2.6<br>2.7 |            | 2.9<br>3.01 |            | 3.4<br>3.6 |            | 4.8<br>5.1   |              | ns    |

| t <sub>CKSW</sub> | Maximum Skew                | FO = 16<br>FO = 128 |                  | 0.4<br>0.5 |            | 0.5<br>0.6 |             | 0.5<br>0.7 |            | 0.6<br>0.8 |              | 0.8<br>1.2   | ns    |

| t <sub>P</sub>    | Minimum Period              | FO = 16<br>FO = 128 | 4.7<br>4.8       |            | 5.4<br>5.6 |            | 6.1<br>6.3  |            | 7.2<br>7.5 |            | 10.0<br>10.4 |              | ns    |

| f <sub>MAX</sub>  | Maximum<br>Frequency        | FO = 16<br>FO = 128 |                  | 188<br>181 |            | 175<br>168 |             | 160<br>154 |            | 139<br>134 |              | 83<br>80     | MHz   |

# Table 37 • A40MX04 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                         |                                                    | –3 SI | beed | –2 S | beed | –1 Sp | eed  | Std S | Speed | –F S | peed |       |

|-------------------------|----------------------------------------------------|-------|------|------|------|-------|------|-------|-------|------|------|-------|

| Parameter / Description |                                                    | Min.  | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| t <sub>WCLKA</sub>      | Flip-Flop (Latch)<br>Clock Active Pulse Width      | 4.6   |      | 5.3  |      | 5.6   |      | 7.0   |       | 9.8  |      | ns    |

| t <sub>WASYN</sub>      | Flip-Flop (Latch)<br>Asynchronous Pulse Width      | 4.6   |      | 5.3  |      | 5.6   |      | 7.0   |       | 9.8  |      | ns    |

| t <sub>A</sub>          | Flip-Flop Clock Input Period                       | 6.8   |      | 7.8  |      | 8.9   |      | 10.4  |       | 14.6 |      | ns    |

| f <sub>MAX</sub>        | Flip-Flop (Latch) Clock<br>Frequency<br>(FO = 128) |       | 109  |      | 101  |       | 92   |       | 80    |      | 48   | MHz   |

| Input Mo                | odule Propagation Delays                           |       |      |      |      |       |      |       |       |      |      |       |

| t <sub>INYH</sub>       | Pad-to-Y HIGH                                      |       | 1.0  |      | 1.1  |       | 1.3  |       | 1.5   |      | 2.1  | ns    |

| t <sub>INYL</sub>       | Pad-to-Y LOW                                       |       | 0.9  |      | 1.0  |       | 1.1  |       | 1.3   |      | 1.9  | ns    |

## Table 41 •A42MX16 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                         |                                                     | –3 S | peed | –2 Sp | beed | –1 S | peed | Std S | Speed | –F Sp | beed |       |

|-------------------------|-----------------------------------------------------|------|------|-------|------|------|------|-------|-------|-------|------|-------|

| Parameter / Description |                                                     | Min. | Max. | Min.  | Max. | Min. | Max. | Min.  | Max.  | Min.  | Max. | Units |

| t <sub>ACO</sub>        | Array Clock-to-Out<br>(Pad-to-Pad),64 Clock Loading |      | 11.3 |       | 12.5 |      | 14.2 |       | 16.7  |       | 23.3 | ns    |

| $d_{TLH}$               | Capacitive Loading, LOW to<br>HIGH                  |      | 0.04 |       | 0.04 |      | 0.05 |       | 0.06  |       | 0.08 | ns/pF |

| d <sub>THL</sub>        | Capacitive Loading, HIGH to LOW                     |      | 0.05 |       | 0.05 |      | 0.06 |       | 0.07  |       | 0.10 | ns/pF |

1. For dual-module macros use tPD1 + tRD1 + taped, to + tRD1 + taped, or tPD1 + tRD1 + tusk, whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing ansalysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

4. Set-up and hold timing parameters for the input buffer latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G inputs subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

## Table 42 •A42MX24 Timing Characteristics (Nominal 5.0 V Operation) (Worst-Case Commercial Conditions,<br/>VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                               | –3 S | peed | –2 S | beed | –1 S | peed | Std Speed |      | –F Speed |      |       |

|--------------------|-----------------------------------------------|------|------|------|------|------|------|-----------|------|----------|------|-------|

| Paramete           | Parameter / Description                       |      | Max. | Min. | Max. | Min. | Max. | Min.      | Max. | Min.     | Max. | Units |

| Logic Mo           | odule Combinatorial Functions <sup>1</sup>    |      |      |      |      |      |      |           |      |          |      |       |

| t <sub>PD</sub>    | Internal Array Module Delay                   |      | 1.2  |      | 1.3  |      | 1.5  |           | 1.8  |          | 2.5  | ns    |

| t <sub>PDD</sub>   | Internal Decode Module Delay                  |      | 1.4  |      | 1.6  |      | 1.8  |           | 2.1  |          | 3.0  | ns    |

| Logic Mo           | odule Predicted Routing Delays <sup>2</sup>   |      |      |      |      |      |      |           |      |          |      |       |

| t <sub>RD1</sub>   | FO = 1 Routing Delay                          |      | 0.8  |      | 0.9  |      | 1.0  |           | 1.2  |          | 1.7  | ns    |

| t <sub>RD2</sub>   | FO = 2 Routing Delay                          |      | 1.0  |      | 1.2  |      | 1.3  |           | 1.5  |          | 2.1  | ns    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                          |      | 1.3  |      | 1.4  |      | 1.6  |           | 1.9  |          | 2.6  | ns    |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |      | 1.5  |      | 1.7  |      | 1.9  |           | 2.2  |          | 3.1  | ns    |

| t <sub>RD5</sub>   | FO = 8 Routing Delay                          |      | 2.4  |      | 2.7  |      | 3.0  |           | 3.6  |          | 5.0  | ns    |

| Logic Mo           | odule Sequential Timing <sup>3, 4</sup>       |      |      |      |      |      |      |           |      |          |      |       |

| t <sub>CO</sub>    | Flip-Flop Clock-to-Output                     |      | 1.3  |      | 1.4  |      | 1.6  |           | 1.9  |          | 2.7  | ns    |

| t <sub>GO</sub>    | Latch Gate-to-Output                          |      | 1.2  |      | 1.3  |      | 1.5  |           | 1.8  |          | 2.5  | ns    |

| t <sub>SUD</sub>   | Flip-Flop (Latch) Set-Up Time                 | 0.3  |      | 0.4  |      | 0.4  |      | 0.5       |      | 0.7      |      | ns    |

| t <sub>HD</sub>    | Flip-Flop (Latch) Hold Time                   | 0.0  |      | 0.0  |      | 0.0  |      | 0.0       |      | 0.0      |      | ns    |

| t <sub>RO</sub>    | Flip-Flop (Latch) Reset-to-Output             |      | 1.4  |      | 1.6  |      | 1.8  |           | 2.1  |          | 2.9  | ns    |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.4  |      | 0.5  |      | 0.5  |      | 0.6       |      | 0.8      |      | ns    |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0  |      | 0.0  |      | 0.0  |      | 0.0       |      | 0.0      |      | ns    |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width | 3.3  |      | 3.7  |      | 4.2  |      | 4.9       |      | 6.9      |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 4.4  |      | 4.8  |      | 5.3  |      | 6.5       |      | 9.0      |      | ns    |

# Table 45 • A42MX36 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                     |                                        | –3 SI | beed | –2 S | peed | –1 Sp | beed | Std S | Speed | –F S | peed |       |

|---------------------|----------------------------------------|-------|------|------|------|-------|------|-------|-------|------|------|-------|

| Paramete            | er / Description                       | Min.  | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| Synchro             | nous SRAM Operations (continue         | ed)   |      |      |      |       |      |       |       |      |      |       |

| t <sub>ADH</sub>    | Address/Data Hold Time                 | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>RENSU</sub>  | Read Enable Set-Up                     | 0.9   |      | 1.0  |      | 1.1   |      | 1.3   |       | 1.8  |      | ns    |

| t <sub>RENH</sub>   | Read Enable Hold                       | 4.8   |      | 5.3  |      | 6.0   |      | 7.0   |       | 9.8  |      | ns    |

| t <sub>WENSU</sub>  | Write Enable Set-Up                    | 3.8   |      | 4.2  |      | 4.8   |      | 5.6   |       | 7.8  |      | ns    |

| t <sub>WENH</sub>   | Write Enable Hold                      | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>BENS</sub>   | Block Enable Set-Up                    | 3.9   |      | 4.3  |      | 4.9   |      | 5.7   |       | 8.0  |      | ns    |

| t <sub>BENH</sub>   | Block Enable Hold                      | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| Asynchr             | onous SRAM Operations                  |       |      |      |      |       |      |       |       |      |      |       |

| t <sub>RPD</sub>    | Asynchronous Access Time               |       | 11.3 |      | 12.6 |       | 14.3 |       | 16.8  |      | 23.5 | ns    |

| t <sub>RDADV</sub>  | Read Address Valid                     | 12.3  |      | 13.7 |      | 15.5  |      | 18.2  |       | 25.5 |      | ns    |

| t <sub>ADSU</sub>   | Address/Data Set-Up Time               | 2.3   |      | 2.5  |      | 2.8   |      | 3.4   |       | 4.8  |      | ns    |

| t <sub>ADH</sub>    | Address/Data Hold Time                 | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>RENSUA</sub> | Read Enable Set-Up to Address<br>Valid | 0.9   |      | 1.0  |      | 1.1   |      | 1.3   |       | 1.8  |      | ns    |

| t <sub>RENHA</sub>  | Read Enable Hold                       | 4.8   |      | 5.3  |      | 6.0   |      | 7.0   |       | 9.8  |      | ns    |

| t <sub>WENSU</sub>  | Write Enable Set-Up                    | 3.8   |      | 4.2  |      | 4.8   |      | 5.6   |       | 7.8  |      | ns    |

| t <sub>WENH</sub>   | Write Enable Hold                      | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>DOH</sub>    | Data Out Hold Time                     |       | 1.8  |      | 2.0  |       | 2.1  |       | 2.5   |      | 3.5  | ns    |

| Input Mo            | dule Propagation Delays                |       |      |      |      |       |      |       |       |      |      |       |

| t <sub>INPY</sub>   | Input Data Pad-to-Y                    |       | 1.4  |      | 1.6  |       | 1.8  |       | 2.1   |      | 3.0  | ns    |

| t <sub>INGO</sub>   | Input Latch Gate-to-Output             |       | 2.0  |      | 2.2  |       | 2.5  |       | 2.9   |      | 4.1  | ns    |

| t <sub>INH</sub>    | Input Latch Hold                       | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>INSU</sub>   | Input Latch Set-Up                     | 0.7   |      | 0.7  |      | 0.8   |      | 1.0   |       | 1.4  |      | ns    |

| t <sub>ILA</sub>    | Latch Active Pulse Width               | 6.5   |      | 7.3  |      | 8.2   |      | 9.7   |       | 13.5 |      | ns    |

Input, output, tristate or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/Os pins are configured by the Designer software as shown in Table 46, page 84.

| Device           | Configuration |

|------------------|---------------|

| A40MX02, A40MX04 | Pulled LOW    |

| A42MX09, A42MX16 | Pulled LOW    |

| A42MX24, A42MX36 | Tristated     |

Table 46 • Configuration of Unused I/Os

In all cases, it is recommended to tie all unused MX I/O pins to LOW on the board. This applies to all dual-purpose pins when configured as I/Os as well.

#### LP, Low Power Mode

Controls the low power mode of all 42MX devices. The device is placed in the low power mode by connecting the LP pin to logic HIGH. In low power mode, all I/Os are tristated, all input buffers are turned OFF, and the core of the device is turned OFF. To exit the low power mode, the LP pin must be set LOW. The device enters the low power mode 800 ns after the LP pin is driven to a logic HIGH. It will resume normal operation in 200 µs after the LP pin is driven to a logic LOW.

#### MODE, Mode

Controls the use of multifunction pins (DCLK, PRA, PRB, SDI, TDO). The MODE pin is held HIGH to provide verification capability. The MODE pin should be terminated to GND through a  $10k\Omega$  resistor so that the MODE pin can be pulled HIGH when required.

#### NC, No Connection

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

### PRA, I/O

### PRB, I/OProbe A/B

The Probe pin is used to output data from any user-defined design node within the device. Each diagnostic pin can be used in conjunction with the other probe pin to allow real-time diagnostic output of any signal path within the device. The Probe pin can be used as a user-defined I/O when verification has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. The Probe pin is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### QCLKA/B/C/D, I/O Quadrant Clock

Quadrant clock inputs for A42MX36 devices. When not used as a register control signal, these pins can function as user I/Os.

### SDI, I/OSerial Data Input

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### SDO, I/OSerial Data Output

Serial data output for diagnostic probe and device programming. SDO is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW. SDO is available for 42MX devices only.

When Silicon Explorer II is being used, SDO will act as an output while the "checksum" command is run. It will return to user I/O when "checksum" is complete.

### TCK, I/O Test Clock

## Table 52 • PQ160

| PQ160      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 58         | VCCI             | VCCI             | VCCI             |

| 59         | GND              | GND              | GND              |

| 60         | VCCA             | VCCA             | VCCA             |

| 61         | LP               | LP               | LP               |

| 62         | I/O              | I/O              | TCK, I/O         |

| 63         | I/O              | I/O              | I/O              |

| 64         | GND              | GND              | GND              |

| 65         | I/O              | I/O              | I/O              |

| 66         | I/O              | I/O              | I/O              |

| 67         | I/O              | I/O              | I/O              |

| 68         | I/O              | I/O              | I/O              |

| 69         | GND              | GND              | GND              |

| 70         | NC               | I/O              | I/O              |

| 71         | I/O              | I/O              | I/O              |

| 72         | I/O              | I/O              | I/O              |

| 73         | I/O              | I/O              | I/O              |

| 74         | I/O              | I/O              | I/O              |

| 75         | NC               | I/O              | I/O              |

| 76         | I/O              | I/O              | I/O              |

| 77         | NC               | I/O              | I/O              |

| 78         | I/O              | I/O              | I/O              |

| 79         | NC               | I/O              | I/O              |

| 30         | GND              | GND              | GND              |

| 81         | I/O              | I/O              | I/O              |

| 82         | SDO, I/O         | SDO, I/O         | SDO, TDO, I/O    |

| 83         | I/O              | I/O              | WD, I/O          |

| 84         | I/O              | I/O              | WD, I/O          |

| 85         | I/O              | I/O              | I/O              |

| 86         | NC               | VCCI             | VCCI             |

| 87         | I/O              | I/O              | I/O              |

| 88         | I/O              | I/O              | WD, I/O          |

| 89         | GND              | GND              | GND              |

| 90         | NC               | I/O              | I/O              |

| 91         | I/O              | I/O              | I/O              |

| 92         | I/O              | I/O              | I/O              |

| 93         | I/O              | I/O              | I/O              |

| 94         | I/O              | I/O              | I/O              |

| PQ240      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 126        | WD, I/O          |

| 127        | I/O              |

| 128        | VCCI             |

| 129        | I/O              |

| 130        | I/O              |

| 131        | I/O              |

| 132        | WD, I/O          |

| 133        | WD, I/O          |

| 134        | I/O              |

| 135        | QCLKB, I/O       |

| 136        | I/O              |

| 137        | I/O              |

| 138        | I/O              |

| 139        | I/O              |

| 140        | I/O              |

| 141        | I/O              |

| 142        | WD, I/O          |

| 143        | WD, I/O          |

| 144        | I/O              |

| 145        | I/O              |

| 146        | I/O              |

| 147        | I/O              |

| 148        | I/O              |

| 149        | I/O              |

| 150        | VCCI             |

| 151        | VCCA             |

| 152        | GND              |

| 153        | I/O              |

| 154        | I/O              |

| 155        | I/O              |

| 156        | I/O              |

| 157        | I/O              |

| 158        | I/O              |

| 159        | WD, I/O          |

| 160        | WD, I/O          |

| 161        | I/O              |

| 162        | I/O              |

| CQ208      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 74         | I/O              |

| 75         | I/O              |

| 76         | I/O              |

| 77         | I/O              |

| 78         | GND              |

| 79         | VCCA             |

| 80         | VCCI             |

| 81         | I/O              |

| 32         | I/O              |

| 83         | I/O              |

| 84         | I/O              |

| 35         | WD, I/O          |

| 36         | WD, I/O          |

| 87         | I/O              |

| 88         | I/O              |

| 89         | I/O              |

| 90         | I/O              |

| 91         | QCLKB, I/O       |

| 92         | I/O              |

| 93         | WD, I/O          |

| 94         | WD, I/O          |

| 95         | I/O              |

| 96         | I/O              |

| 97         | I/O              |

| 98         | VCCI             |

| 99         | I/O              |

| 100        | WD, I/O          |

| 101        | WD, I/O          |

| 102        | I/O              |

| 103        | TDO, I/O         |

| 104        | I/O              |

| 105        | GND              |

| 106        | VCCA             |

| 107        | I/O              |

| 108        | I/O              |

| 109        | I/O              |

| 110        | I/O              |

| CQ256      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 59         | I/O              |

| 60         | VCCA             |

| 61         | GND              |

| 62         | GND              |

| 63         | NC               |

| 64         | NC               |

| 65         | NC               |

| 66         | I/O              |

| 67         | SDO, TDO, I/O    |

| 68         | I/O              |

| 69         | WD, I/O          |

| 70         | WD, I/O          |

| 71         | I/O              |

| 72         | VCCI             |

| 73         | I/O              |

| 74         | I/O              |

| 75         | I/O              |

| 76         | WD, I/O          |

| 77         | GND              |

| 78         | WD, I/O          |

| 79         | I/O              |

| 80         | QCLKB, I/O       |

| 81         | I/O              |

| 82         | I/O              |

| 83         | I/O              |

| 84         | I/O              |

| 85         | I/O              |

| 86         | I/O              |

| 87         | WD, I/O          |

| 88         | WD, I/O          |

| 89         | I/O              |

| 90         | I/O              |

| 91         | I/O              |

| 92         | I/O              |

| 93         | I/O              |

| 94         | I/O              |

| 95         | VCCI             |

| CQ256      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 207        | I/O              |

| 208        | I/O              |

| 209        | QCLKC, I/O       |

| 210        | I/O              |

| 211        | WD, I/O          |

| 212        | WD, I/O          |

| 213        | I/O              |

| 214        | I/O              |

| 215        | WD, I/O          |

| 216        | WD, I/O          |

| 217        | I/O              |

| 218        | PRB, I/O         |

| 219        | I/O              |

| 220        | CLKB, I/O        |

| 221        | I/O              |

| 222        | GND              |

| 223        | GND              |

| 224        | VCCA             |

| 225        | VCCI             |

| 226        | I/O              |

| 227        | CLKA, I/O        |

| 228        | I/O              |

| 229        | PRA, I/O         |

| 230        | I/O              |

| 231        | I/O              |

| 232        | WD, I/O          |

| 233        | WD, I/O          |

| 234        | I/O              |

| 235        | I/O              |

| 236        | I/O              |

| 237        | I/O              |

| 238        | I/O              |

| 239        | I/O              |

| 240        | QCLKD, I/O       |

| 241        | I/O              |

| 242        | WD, I/O          |

| 243        | GND              |

| Table 60 • B | G272             |

|--------------|------------------|

| BG272        |                  |

| Pin Number   | A42MX36 Function |

| T19          | I/O              |

| T20          | I/O              |

| U1           | I/O              |

| U2           | I/O              |

| U3           | I/O              |

| U4           | I/O              |

| U5           | VCCI             |

| U6           | WD, I/O          |

| U7           | I/O              |

| U8           | I/O              |

| U9           | WD, I/O          |

| U10          | VCCA             |

| U11          | VCCI             |

| U12          | I/O              |

| U13          | I/O              |

| U14          | QCLKB, I/O       |

| U15          | I/O              |

| U16          | VCCI             |

| U17          | I/O              |

| U18          | GND              |

| U19          | I/O              |

| U20          | I/O              |

| V1           | I/O              |

| V2           | I/O              |

| V3           | GND              |

| V4           | GND              |

| V5           | I/O              |

| V6           | I/O              |

| V7           | I/O              |

| V8           | WD, I/O          |

| V9           | I/O              |

| V10          | I/O              |

| V11          | I/O              |

| V12          | I/O              |

| V13          | WD, I/O          |

| V14          | I/O              |

| V15          | WD, I/O          |

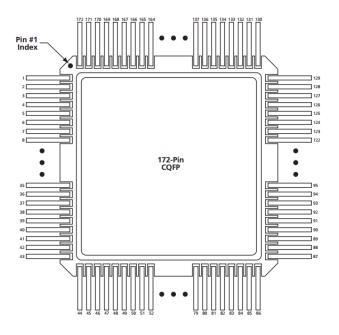

## Figure 53 • CQ172

| CQ172      |                     |  |

|------------|---------------------|--|

| Pin Number | A42MX16<br>Function |  |

| 1          | MODE                |  |

| 2          | I/O                 |  |

| 3          | I/O                 |  |

| 4          | I/O                 |  |

| 5          | I/O                 |  |

| 6          | I/O                 |  |

| 7          | GND                 |  |

| 8          | I/O                 |  |

| 9          | I/O                 |  |

| 10         | I/O                 |  |

| 11         | I/O                 |  |

| 12         | VCC                 |  |

| 13         | I/O                 |  |

| 14         | I/O                 |  |

| 15         | I/O                 |  |

| 16         | I/O                 |  |

| 17         | GND                 |  |

| 18         | I/O                 |  |

| 19         | I/O                 |  |

| 20         | I/O                 |  |

|            |                     |  |