Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | -                                                                          |

| Total RAM Bits                 | -                                                                          |

| Number of I/O                  | 125                                                                        |

| Number of Gates                | 36000                                                                      |

| Voltage - Supply               | 3V ~ 3.6V, 4.5V ~ 5.5V                                                     |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -55°C ~ 125°C (TC)                                                         |

| Package / Case                 | 160-BQFP                                                                   |

| Supplier Device Package        | 160-PQFP (28x28)                                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx24-1pqg160m |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3.7 Low Power Mode

42MX devices have been designed with a Low Power Mode. This feature, activated with setting the special LP pin to HIGH for a period longer than 800 ns, is particularly useful for battery-operated systems where battery life is a primary concern. In this mode, the core of the device is turned off and the device consumes minimal power with low standby current. In addition, all input buffers are turned off, and all outputs and bidirectional buffers are tristated. Since the core of the device is turned off, the states of the registers are lost. The device must be re-initialized when exiting Low Power Mode. I/Os can be driven during LP mode, and clock pins should be driven HIGH or LOW and should not float to avoid drawing current. To exit LP mode, the LP pin must be pulled LOW for over 200 µs to allow for charge pumps to power up, and device initialization will begin.

## 3.4 Power Dissipation

The general power consumption of MX devices is made up of static and dynamic power and can be expressed with the following equation.

### 3.4.1 General Power Equation

P = [ICCstandby + ICCactive]\*VCCI + IOL\*VOL\*N + IOH\*(VCCI - VOH)\*M

EQ 1

#### where:

- ICCstandby is the current flowing when no inputs or outputs are changing.

- ICCactive is the current flowing due to CMOS switching.

- IOL, IOH are TTL sink/source currents.

- VOL, VOH are TTL level output voltages.

- N equals the number of outputs driving TTL loads to VOL.

- M equals the number of outputs driving TTL loads to VOH.

Accurate values for N and M are difficult to determine because they depend on the family type, on design details, and on the system I/O. The power can be divided into two components: static and active.

## 3.4.2 Static Power Component

The static power due to standby current is typically a small component of the overall power consumption. Standby power is calculated for commercial, worst-case conditions. The static power dissipation by TTL loads depends on the number of outputs driving, and on the DC load current. For instance, a 32-bit bus sinking 4mA at 0.33V will generate 42mW with all outputs driving LOW, and 140mW with all outputs driving HIGH. The actual dissipation will average somewhere in between, as I/Os switch states with time.

## 3.4.3 Active Power Component

Power dissipation in CMOS devices is usually dominated by the dynamic power dissipation. Dynamic power consumption is frequency-dependent and is a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitances due to PC board traces and load device inputs. An additional component of the active power dissipation is the totem pole current in the CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

The power dissipated by a CMOS circuit can be expressed by the equation:

Power(

$$\mu$$

W) =  $C_{EO}^*$  VCCA2\* F(1)

EQ 2

### where:

C<sub>FO</sub> = Equivalent capacitance expressed in picofarads (pF)

Figure 13 • Silicon Explorer II Setup with 42MX

Serial Connection to Windows PC

Silicon Explorer II

Silicon Explorer II

Silicon Explorer II

Table 8 • Device Configuration Options for Probe Capability

| Security Fuse(s) Programmed | Mode | PRA, PRB <sup>1</sup>  | SDI, SDO, DCLK <sup>1</sup> |

|-----------------------------|------|------------------------|-----------------------------|

| No                          | LOW  | User I/Os <sup>2</sup> | User I/Os <sup>2</sup>      |

| No                          | HIGH | Probe Circuit Outputs  | Probe Circuit Inputs        |

| Yes                         | _    | Probe Circuit Secured  | Probe Circuit Secured       |

<sup>1.</sup> Avoid using SDI, SDO, DCLK, PRA and PRB pins as input or bidirectional ports. Since these pins are active during probing, input signals will not pass through these pins and may cause contention.

### 3.4.7 Design Consideration

It is recommended to use a series  $70\Omega$  termination resistor on every probe connector (SDI, SDO, MODE, DCLK, PRA and PRB). The  $70~\Omega$  series termination is used to prevent data transmission corruption during probing and reading back the checksum.

## 3.4.8 IEEE Standard 1149.1 Boundary Scan Test (BST) Circuitry

42MX24 and 42MX36 devices are compatible with IEEE Standard 1149.1 (informally known as Joint Testing Action Group Standard or JTAG), which defines a set of hardware architecture and mechanisms for cost-effective board-level testing. The basic MX boundary-scan logic circuit is composed of the TAP (test access port), TAP controller, test data registers and instruction register (Figure 14, page 18). This circuit supports all mandatory IEEE 1149.1 instructions (EXTEST, SAMPLE/PRELOAD and BYPASS) and some optional instructions. Table 9, page 18 describes the ports that control JTAG testing, while Table 10, page 18 describes the test instructions supported by these MX devices.

Each test section is accessed through the TAP, which has four associated pins: TCK (test clock input), TDI and TDO (test data input and output), and TMS (test mode selector).

The TAP controller is a four-bit state machine. The '1's and '0's represent the values that must be present at TMS at a rising edge of TCK for the given state transition to occur. IR and DR indicate that the instruction register or the data register is operating in that state.

The TAP controller receives two control inputs (TMS and TCK) and generates control and clock signals for the rest of the test logic architecture. On power-up, the TAP controller enters the Test-Logic-Reset state. To guarantee a reset of the controller from any of the possible states, TMS must remain high for five TCK cycles.

42MX24 and 42MX36 devices support three types of test data registers: bypass, device identification, and boundary scan. The bypass register is selected when no other register needs to be accessed in a device. This speeds up test data transfer to other devices in a test data path. The 32-bit device identification register is a shift register with four fields (lowest significant byte (LSB), ID number, part number and version). The boundary-scan register observes and controls the state of each I/O pin.

<sup>2.</sup> If no user signal is assigned to these pins, they will behave as unused I/Os in this mode. See the Pin Descriptions, page 83 for information on unused I/O pins

Additionally, the back-annotation flow is compatible with all the major simulators and the simulation results can be cross-probed with Silicon Explorer II, Microsemi's integrated verification and logic analysis tool. Another tool included in the Libero software is the SmartGen macro builder, which easily creates popular and commonly used logic functions for implementation into your schematic or HDL design.

Microsemi's Libero software is compatible with the most popular FPGA design entry and verification tools from companies such as Mentor Graphics, Synopsys, and Cadence design systems.

See the Libero IDE web content at www.microsemi.com/soc/products/software/libero/default.aspx for further information on licensing and current operating system support.

### 3.6 Related Documents

The following sections give the list of related documents which can be refered for this datasheet.

### 3.6.1 Application Notes

- AC278: BSDL Files Format Description

- AC225: Programming Antifuse Devices

- AC168: Implementation of Security in Microsemi Antifuse FPGAs

### 3.6.2 User Guides and Manuals

- Antifuse Macro Library Guide

- Silicon Sculptor Programmers User Guide

### 3.6.3 Miscellaneous

Libero IDE Flow Diagram

## 3.7 5.0 V Operating Conditions

The following tables show 5.0 V operating conditions.

Table 12 • Absolute Maximum Ratings for 40MX Devices\*

| Symbol           | Parameter           | Limits          | Units |  |

|------------------|---------------------|-----------------|-------|--|

| VCC              | DC Supply Voltage   | -0.5 to +7.0    | V     |  |

| VI               | Input Voltage       | -0.5 to VCC+0.5 | V     |  |

| VO               | Output Voltage      | -0.5 to VCC+0.5 | V     |  |

| t <sub>STG</sub> | Storage Temperature | -65 to +150     | °C    |  |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

Table 13 • Absolute Maximum Ratings for 42MX Devices\*

| Symbol           | Parameter                   | Limits           | Units |

|------------------|-----------------------------|------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | -0.5 to +7.0     | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0     | V     |

| VI               | Input Voltage               | -0.5 to VCCI+0.5 | V     |

| VO               | Output Voltage              | -0.5 to VCCI+0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150      | °C    |

3. All outputs unloaded. All inputs = VCC/VCCI or GND

## 3.8 3.3 V Operating Conditions

The following table shows 3.3 V operating conditions.

Table 16 • Absolute Maximum Ratings for 40MX Devices\*

| Symbol           | Parameter           | Limits            | Units |  |

|------------------|---------------------|-------------------|-------|--|

| VCC              | DC Supply Voltage   | -0.5 to +7.0      | V     |  |

| VI               | Input Voltage       | -0.5 to VCC + 0.5 | V     |  |

| VO               | Output Voltage      | -0.5 to VCC + 0.5 | V     |  |

| t <sub>STG</sub> | Storage Temperature | -65 to + 150      | °C    |  |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

Table 17 • Absolute Maximum Ratings for 42MX Devices\*

| Symbol           | Parameter                   | Limits           | Units |

|------------------|-----------------------------|------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | -0.5 to +7.0     | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0     | V     |

| VI               | Input Voltage               | -0.5 to VCCI+0.5 | V     |

| VO               | Output Voltage              | -0.5 to VCCI+0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150      | °C    |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

Table 18 • Recommended Operating Conditions

| Parameter          | Commercial | Industrial | Military    | Units |

|--------------------|------------|------------|-------------|-------|

| Temperature Range* | 0 to +70   | -40 to +85 | -55 to +125 | °C    |

| VCC (40MX)         | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

| VCCA (42MX)        | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

| VCCI (42MX)        | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

Note: \*Ambient temperature  $(T_A)$  is used for commercial and industrial grades; case temperature  $(T_C)$  is used for military grades.

All the following tables show various specifications and operating conditions of 40MX and 42MX FPGAs.

reliability. Devices should not be operated outside the recommended operating conditions.

Table 21 • Recommended Operating Conditions

| Parameter          | Commercial   | Industrial | Military    | Units |

|--------------------|--------------|------------|-------------|-------|

| Temperature Range* | 0 to +70     | -40 to +85 | -55 to +125 | °C    |

| VCCA               | 4.75 to 5.25 | 4.5 to 5.5 | 4.5 to 5.5  | V     |

| VCCI               | 3.14 to 3.47 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

**Note:** \*Ambient temperature  $(T_A)$  is used for commercial and industrial grades; case temperature  $(T_C)$  is used for military grades.

## 3.9.1 Mixed 5.0V/3.3V Electrical Specifications

Table 22 • Mixed 5.0V/3.3V Electrical Specifications

|                                                             |                     | Commercial |            | Commercial –F |            | Industrial |            | Military |            | · <u> </u> |

|-------------------------------------------------------------|---------------------|------------|------------|---------------|------------|------------|------------|----------|------------|------------|

| Symbol                                                      | Parameter           | Min.       | Max.       | Min.          | Max.       | Min.       | Max.       | Min.     | Max.       | Units      |

| VOH <sup>1</sup>                                            | IOH = −10 mA        | 2.4        |            | 2.4           |            |            |            |          |            | V          |

|                                                             | IOH = -4 mA         |            |            |               |            | 2.4        |            | 2.4      |            | V          |

| VOL <sup>1</sup>                                            | IOL = 10 mA         |            | 0.5        |               | 0.5        |            |            |          |            | V          |

|                                                             | IOL = 6 mA          |            |            |               |            |            | 0.4        |          | 0.4        | V          |

| VIL                                                         |                     | -0.3       | 0.8        | -0.3          | 0.8        | -0.3       | 0.8        | -0.3     | 0.8        | V          |

| VIH <sup>2</sup>                                            |                     | 2.0        | VCCA + 0.3 | 2.0           | VCCA + 0.3 | 2.0        | VCCA + 0.3 | 2.0      | VCCA + 0.3 | V          |

| IL                                                          | VIN = 0.5 V         |            | -10        |               | -10        |            | -10        |          | -10        | μΑ         |

| IH                                                          | VIN = 2.7 V         |            | -10        |               | -10        |            | -10        |          | -10        | μΑ         |

| Input Transition<br>Time, T <sub>R</sub> and T <sub>F</sub> |                     |            | 500        |               | 500        |            | 500        |          | 500        | ns         |

| C <sub>IO</sub> I/O Capacitance                             |                     |            | 10         |               | 10         |            | 10         |          | 10         | pF         |

| Standby Current,                                            | A42MX09             |            | 5          |               | 25         |            | 25         |          | 25         | mA         |

| ICC <sup>3</sup>                                            | A42MX16             |            | 6          |               | 25         |            | 25         |          | 25         | mΑ         |

|                                                             | A42MX24,<br>A42MX36 |            | 20         |               | 25         |            | 25         |          | 25         | mA         |

| Low Power Mode<br>Standby Current                           |                     |            | 0.5        |               | ICC - 5.0  |            | ICC - 5.0  |          | ICC - 5.0  | mA         |

IIO I/O source sink Can be derived from the *IBIS model* (http://www.microsemi.com/soc/techdocs/models/ibis.html) current

## 3.9.2 Output Drive Characteristics for 5.0 V PCI Signaling

MX PCI device I/O drivers were designed specifically for high-performance PCI systems. Figure 16, page 28 shows the typical output drive characteristics of the MX devices. MX output drivers are compliant with the PCI Local Bus Specification.

Table 23 • DC Specification (5.0 V PCI Signaling)<sup>1</sup>

|                  |                            |                              | PCI  |             | MX   |                   |       |

|------------------|----------------------------|------------------------------|------|-------------|------|-------------------|-------|

| Symbol           | Parameter                  | Condition                    | Min. | Max.        | Min. | Max.              | Units |

| VCCI             | Supply Voltage for I/Os    |                              | 4.75 | 5.25        | 4.75 | 5.25 <sup>2</sup> | V     |

| VIH <sup>3</sup> | Input High Voltage         |                              | 2.0  | VCC + 0.5   | 2.0  | VCCI + 0.3        | V     |

| VIL              | Input Low Voltage          |                              | -0.5 | 0.8         | -0.3 | 0.8               | V     |

| IIH              | Input High Leakage Current | VIN = 2.7 V                  |      | 70          | _    | 10                | μA    |

| IIL              | Input Low Leakage Current  | VIN=0.5 V                    |      | <b>-7</b> 0 | _    | -10               | μA    |

| VOH              | Output High Voltage        | IOUT = -2 mA<br>IOUT = -6 mA | 2.4  |             | 3.84 |                   | V     |

| VOL              | Output Low Voltage         | IOUT = 3 mA, 6 mA            |      | 0.55        | _    | 0.33              | V     |

<sup>1.</sup> Only one output tested at a time. VCCI = min.

<sup>2.</sup> VIH(Min) is 2.4V for A42MX36 family. This applies only to VCCI of 5V and is not applicable to VCCI of 3.3V

<sup>3.</sup> All outputs unloaded. All inputs = VCCI or GND

approximately a 3 ns to a 6 ns delay, which is represented statistically in higher fanout (FO=8) routing delays in the data sheet specifications section, shown in Table 34, page 41.

### 3.11.3 Timing Derating

MX devices are manufactured with a CMOS process. Therefore, device performance varies according to temperature, voltage, and process changes. Minimum timing parameters reflect maximum operating voltage, minimum operating temperature and best-case processing. Maximum timing parameters reflect minimum operating voltage, maximum operating temperature and worst-case processing.

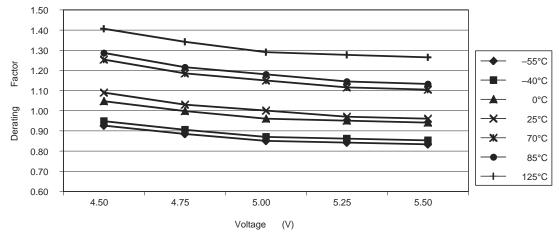

### 3.11.4 Temperature and Voltage Derating Factors

The following tables and figures show temperature and voltage derating factors for 40MX and 42MX FPGAs.

Table 28 • 42MX Temperature and Voltage Derating Factors (Normalized to T<sub>J</sub> = 25°C, VCCA = 5.0 V)

|          | Temperat   | Temperature |      |      |      |      |       |  |  |  |  |

|----------|------------|-------------|------|------|------|------|-------|--|--|--|--|

| 42MX Vol | tage -55°C | -40°C       | 0°C  | 25°C | 70°C | 85°C | 125°C |  |  |  |  |

| 4.50     | 0.93       | 0.95        | 1.05 | 1.09 | 1.25 | 1.29 | 1.41  |  |  |  |  |

| 4.75     | 0.88       | 0.90        | 1.00 | 1.03 | 1.18 | 1.22 | 1.34  |  |  |  |  |

| 5.00     | 0.85       | 0.87        | 0.96 | 1.00 | 1.15 | 1.18 | 1.29  |  |  |  |  |

| 5.25     | 0.84       | 0.86        | 0.95 | 0.97 | 1.12 | 1.14 | 1.28  |  |  |  |  |

| 5.50     | 0.83       | 0.85        | 0.94 | 0.96 | 1.10 | 1.13 | 1.26  |  |  |  |  |

Figure 34 • 42MX Junction Temperature and Voltage Derating Curves (Normalized to TJ = 25°C, VCCA = 5.0 V)

Note: This derating factor applies to all routing and propagation delays

Table 29 • 40MX Temperature and Voltage Derating Factors(Normalized to TJ = 25°C, VCC = 5.0 V)

| Temperature |                           |                                                                                                                                     |                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -55°C       | -40°C                     | 0°C                                                                                                                                 | 25°C                                                                                                                                                                                                | 70°C                                                                                                                                                                                                                                                                 | 85°C                                                                                                                                                                                                                                                                                                                                  | 125°C                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 0.89        | 0.93                      | 1.02                                                                                                                                | 1.09                                                                                                                                                                                                | 1.25                                                                                                                                                                                                                                                                 | 1.31                                                                                                                                                                                                                                                                                                                                  | 1.45                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0.84        | 0.88                      | 0.97                                                                                                                                | 1.03                                                                                                                                                                                                | 1.18                                                                                                                                                                                                                                                                 | 1.24                                                                                                                                                                                                                                                                                                                                  | 1.37                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0.82        | 0.85                      | 0.94                                                                                                                                | 1.00                                                                                                                                                                                                | 1.15                                                                                                                                                                                                                                                                 | 1.20                                                                                                                                                                                                                                                                                                                                  | 1.33                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0.80        | 0.82                      | 0.91                                                                                                                                | 0.97                                                                                                                                                                                                | 1.12                                                                                                                                                                                                                                                                 | 1.16                                                                                                                                                                                                                                                                                                                                  | 1.29                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 0.79        | 0.82                      | 0.90                                                                                                                                | 0.96                                                                                                                                                                                                | 1.10                                                                                                                                                                                                                                                                 | 1.15                                                                                                                                                                                                                                                                                                                                  | 1.28                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|             | -55°C 0.89 0.84 0.82 0.80 | -55°C         -40°C           0.89         0.93           0.84         0.88           0.82         0.85           0.80         0.82 | -55°C         -40°C         0°C           0.89         0.93         1.02           0.84         0.88         0.97           0.82         0.85         0.94           0.80         0.82         0.91 | -55°C         -40°C         0°C         25°C           0.89         0.93         1.02         1.09           0.84         0.88         0.97         1.03           0.82         0.85         0.94         1.00           0.80         0.82         0.91         0.97 | -55°C         -40°C         0°C         25°C         70°C           0.89         0.93         1.02         1.09         1.25           0.84         0.88         0.97         1.03         1.18           0.82         0.85         0.94         1.00         1.15           0.80         0.82         0.91         0.97         1.12 | -55°C         -40°C         0°C         25°C         70°C         85°C           0.89         0.93         1.02         1.09         1.25         1.31           0.84         0.88         0.97         1.03         1.18         1.24           0.82         0.85         0.94         1.00         1.15         1.20           0.80         0.82         0.91         0.97         1.12         1.16 |  |  |  |

Table 38 • A42MX09 Timing Characteristics (Nominal 5.0 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                         |                                                          | -3 Sp | eed  | -2 S | peed | -1 Sp | peed | Std S | Speed | −F S | peed |       |

|-------------------------|----------------------------------------------------------|-------|------|------|------|-------|------|-------|-------|------|------|-------|

| Parameter / Description |                                                          | Min.  | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| CMOS                    | Output Module Timing <sup>5</sup>                        |       |      |      |      |       |      |       |       |      |      |       |

| t <sub>DLH</sub>        | Data-to-Pad HIGH                                         |       | 2.4  |      | 2.7  |       | 3.1  |       | 3.6   |      | 5.1  | ns    |

| t <sub>DHL</sub>        | Data-to-Pad LOW                                          |       | 2.9  |      | 3.2  |       | 3.6  |       | 4.3   |      | 6.0  | ns    |

| t <sub>ENZH</sub>       | Enable Pad Z to HIGH                                     |       | 2.7  |      | 2.9  |       | 3.3  |       | 3.9   |      | 5.5  | ns    |

| t <sub>ENZL</sub>       | Enable Pad Z to LOW                                      |       | 2.9  |      | 3.2  |       | 3.7  |       | 4.3   |      | 6.1  | ns    |

| t <sub>ENHZ</sub>       | Enable Pad HIGH to Z                                     |       | 4.9  |      | 5.4  |       | 6.2  |       | 7.3   |      | 10.2 | ns    |

| t <sub>ENLZ</sub>       | Enable Pad LOW to Z                                      |       | 5.3  |      | 5.9  |       | 6.7  |       | 7.9   |      | 11.1 | ns    |

| t <sub>GLH</sub>        | G-to-Pad HIGH                                            |       | 4.2  |      | 4.6  |       | 5.2  |       | 6.1   |      | 8.6  | ns    |

| t <sub>GHL</sub>        | G-to-Pad LOW                                             |       | 4.2  |      | 4.6  |       | 5.2  |       | 6.1   |      | 8.6  | ns    |

| t <sub>LSU</sub>        | I/O Latch Set-Up                                         | 0.5   |      | 0.5  |      | 0.6   |      | 0.7   |       | 1.0  |      | ns    |

| t <sub>LH</sub>         | I/O Latch Hold                                           | 0.0   |      | 0.0  |      | 0.0   |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>LCO</sub>        | I/O Latch Clock-to-Out<br>(Pad-to-Pad), 64 Clock Loading |       | 5.2  |      | 5.8  |       | 6.6  |       | 7.7   |      | 10.8 | ns    |

| t <sub>ACO</sub>        | Array Clock-to-Out (<br>Pad-to-Pad), 64 Clock Loading    |       | 7.4  |      | 8.2  |       | 9.3  |       | 10.9  |      | 15.3 | ns    |

| d <sub>TLH</sub>        | Capacity Loading, LOW to HIGH                            |       | 0.03 |      | 0.03 |       | 0.03 |       | 0.04  |      | 0.06 | ns/pF |

| d <sub>THL</sub>        | Capacity Loading, HIGH to LOW                            |       | 0.04 |      | 0.04 |       | 0.04 |       | 0.05  |      | 0.07 | ns/pF |

<sup>1.</sup> For dual-module macros, use  $t_{PD1}$  +  $t_{RD1}$  +  $t_{PDn}$ ,  $t_{CO}$  +  $t_{RD1}$  +  $t_{PDn}$ , or  $t_{PD1}$  +  $t_{RD1}$  +  $t_{SUD}$ , whichever is appropriate.

Table 39 • A42MX09 Timing Characteristics (Nominal 3.3 V Operation) (Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                         |                                              | -3 Speed  | -2 Speed  | -1 Speed  | Std Speed | -F Speed  |       |

|-------------------------|----------------------------------------------|-----------|-----------|-----------|-----------|-----------|-------|

| Parameter / Description |                                              | Min. Max. | Units |

| Logic M                 | lodule Propagation Delays <sup>1</sup>       |           |           |           |           |           |       |

| t <sub>PD1</sub>        | Single Module                                | 1.6       | 1.8       | 2.1       | 2.5       | 3.5       | ns    |

| t <sub>CO</sub>         | Sequential Clock-to-Q                        | 1.8       | 2.0       | 2.3       | 2.7       | 3.8       | ns    |

| t <sub>GO</sub>         | Latch G-to-Q                                 | 1.7       | 1.9       | 2.1       | 2.5       | 3.5       | ns    |

| t <sub>RS</sub>         | Flip-Flop (Latch) Reset-to-Q                 | 2.0       | 2.2       | 2.5       | 2.9       | 4.1       | ns    |

| Logic M                 | lodule Predicted Routing Delays <sup>2</sup> |           |           |           |           |           |       |

| t <sub>RD1</sub>        | FO = 1 Routing Delay                         | 1.0       | 1.1       | 1.2       | 1.4       | 2.0       | ns    |

| t <sub>RD2</sub>        | FO = 2 Routing Delay                         | 1.3       | 1.4       | 1.6       | 1.9       | 2.7       | ns    |

| t <sub>RD3</sub>        | FO = 3 Routing Delay                         | 1.6       | 1.8       | 2.0       | 2.4       | 3.3       | ns    |

Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

<sup>3.</sup> Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

<sup>4.</sup> Set-up and hold timing parameters for the input buffer latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

<sup>5.</sup> Delays based on 35 pF loading

Table 40 • A42MX16 Timing Characteristics (Nominal 5.0 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                               | −3 S       | peed       | -2 S       | peed       | -1 S <sub>I</sub> | peed       | Std S      | peed       | −F Sp      | peed       |          |

|--------------------|-----------------------------------------------|------------|------------|------------|------------|-------------------|------------|------------|------------|------------|------------|----------|

| Parame             | ter / Description                             | Min.       | Max.       | Min.       | Max.       | Min.              | Max.       | Min.       | Max.       | Min.       | Max.       | Units    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                          |            | 1.3        |            | 1.4        |                   | 1.6        |            | 1.9        |            | 2.7        | ns       |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |            | 1.6        |            | 1.7        |                   | 2.0        |            | 2.3        |            | 3.2        | ns       |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                          |            | 2.6        |            | 2.9        |                   | 3.2        |            | 3.8        |            | 5.3        | ns       |

| Logic M            | lodule Sequential Timing <sup>3,4</sup>       |            |            |            |            |                   |            |            |            |            |            |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up        | 0.3        |            | 0.4        |            | 0.4               |            | 0.5        |            | 0.7        |            | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input Hold             | 0.0        |            | 0.0        |            | 0.0               |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.7        |            | 0.8        |            | 0.9               |            | 1.0        |            | 1.4        |            | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0        |            | 0.0        |            | 0.0               |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width | 3.4        |            | 3.8        |            | 4.3               |            | 5.0        |            | 7.1        |            | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 4.5        |            | 5.0        |            | 5.6               |            | 6.6        |            | 9.2        |            | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input Period                  | 6.8        |            | 7.6        |            | 8.6               |            | 10.1       |            | 14.1       |            | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Hold                       | 0.0        |            | 0.0        |            | 0.0               |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Set-Up                     | 0.5        |            | 0.5        |            | 0.6               |            | 0.7        |            | 1.0        |            | ns       |

| t <sub>OUTH</sub>  | Output Buffer Latch Hold                      | 0.0        |            | 0.0        |            | 0.0               |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>OUTSU</sub> | Output Buffer Latch Set-Up                    | 0.5        |            | 0.5        |            | 0.6               |            | 0.7        |            | 1.0        |            | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock Frequency             | ,          | 215        |            | 195        |                   | 179        |            | 156        |            | 94         | MHz      |

| Input Mo           | odule Propagation Delays                      |            |            |            |            |                   |            |            |            |            |            |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                 |            | 1.1        |            | 1.2        |                   | 1.3        |            | 1.6        |            | 2.2        | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                  |            | 8.0        |            | 0.9        |                   | 1.0        |            | 1.2        |            | 1.7        | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                                   |            | 1.4        |            | 1.6        |                   | 1.8        |            | 2.1        |            | 2.9        | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                    |            | 1.4        |            | 1.6        |                   | 1.8        |            | 2.1        |            | 2.9        | ns       |

| Input Mo           | odule Predicted Routing Delays <sup>2</sup>   |            |            |            |            |                   |            |            |            |            |            |          |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                          |            | 1.8        |            | 2.0        |                   | 2.3        |            | 2.7        |            | 4.0        | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                          |            | 2.1        |            | 2.3        |                   | 2.6        |            | 3.1        |            | 4.3        | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                          |            | 2.3        |            | 2.6        |                   | 3.0        |            | 3.5        |            | 4.9        | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                          |            | 2.6        |            | 3.0        |                   | 3.3        |            | 3.9        |            | 5.4        | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                          |            | 3.6        |            | 4.0        |                   | 4.6        |            | 5.4        |            | 7.5        | ns       |

| Global (           | Clock Network                                 |            |            |            |            |                   |            |            |            |            |            |          |

| t <sub>CKH</sub>   | Input LOW to HIGH FO = 32<br>FO = 384         |            | 2.6<br>2.9 |            | 2.9<br>3.2 |                   | 3.3<br>3.6 |            | 3.9<br>4.3 |            | 5.4<br>6.0 | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW FO = 32<br>FO = 384         |            | 3.8<br>4.5 |            | 4.2<br>5.0 |                   | 4.8<br>5.6 |            | 5.6<br>6.6 |            | 7.8<br>9.2 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse Width FO = 32<br>HIGH FO = 384  | 3.2<br>3.7 |            | 3.5<br>4.1 |            | 4.0<br>4.6        |            | 4.7<br>5.4 |            | 6.6<br>7.6 |            | ns<br>ns |

Table 42 • A42MX24 Timing Characteristics (Nominal 5.0 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                         |                                         |                     | -3 S       | peed       | -2 Sp      | peed       | -1 S <sub>I</sub> | peed       | Std S      | peed       | −F S         | peed       |          |

|-------------------------|-----------------------------------------|---------------------|------------|------------|------------|------------|-------------------|------------|------------|------------|--------------|------------|----------|

| Parameter / Description |                                         | Min.                | Max.       | Min.       | Max.       | Min.       | Max.              | Min.       | Max.       | Min.       | Max.         | Units      |          |

| Input Mo                | odule Predicted Routing                 | Delays <sup>2</sup> |            |            |            |            |                   |            |            |            |              |            |          |

| t <sub>IRD1</sub>       | FO = 1 Routing Delay                    |                     |            | 1.8        |            | 2.0        |                   | 2.3        |            | 2.7        |              | 3.8        | ns       |

| t <sub>IRD2</sub>       | FO = 2 Routing Delay                    |                     |            | 2.1        |            | 2.3        |                   | 2.6        |            | 3.1        |              | 4.3        | ns       |

| t <sub>IRD3</sub>       | FO = 3 Routing Delay                    |                     |            | 2.3        |            | 2.5        |                   | 2.9        |            | 3.4        |              | 4.8        | ns       |

| t <sub>IRD4</sub>       | FO = 4 Routing Delay                    |                     |            | 2.5        |            | 2.8        |                   | 3.2        |            | 3.7        |              | 5.2        | ns       |

| t <sub>IRD8</sub>       | FO = 8 Routing Delay                    |                     |            | 3.4        |            | 3.8        |                   | 4.3        |            | 5.1        |              | 7.1        | ns       |

| Global C                | Clock Network                           |                     |            |            |            |            |                   |            |            |            |              |            |          |

| t <sub>CKH</sub>        | Input LOW to HIGH                       | FO = 32<br>FO = 486 |            | 2.6<br>2.9 |            | 2.9<br>3.2 |                   | 3.3<br>3.6 |            | 3.9<br>4.3 |              | 5.4<br>5.9 | ns<br>ns |

| t <sub>CKL</sub>        | Input HIGH to LOW                       | FO = 32<br>FO = 486 |            | 3.7<br>4.3 |            | 4.1<br>4.7 |                   | 4.6<br>5.4 |            | 5.4<br>6.3 |              | 7.6<br>8.8 | ns<br>ns |

| t <sub>PWH</sub>        | Minimum Pulse<br>Width HIGH             | FO = 32<br>FO = 486 | 2.2<br>2.4 |            | 2.4<br>2.6 |            | 2.7<br>3.0        |            | 3.2<br>3.5 |            | 4.5<br>4.9   |            | ns<br>ns |

| t <sub>PWL</sub>        | Minimum Pulse<br>Width LOW              | FO = 32<br>FO = 486 | 2.2<br>2.4 |            | 2.4<br>2.6 |            | 2.7<br>3.0        |            | 3.2<br>3.5 |            | 4.5<br>4.9   |            | ns<br>ns |

| t <sub>CKSW</sub>       | Maximum Skew                            | FO = 32<br>FO = 486 |            | 0.5<br>0.5 |            | 0.6<br>0.6 |                   | 0.7<br>0.7 |            | 0.8<br>0.8 |              | 1.1<br>1.1 | ns<br>ns |

| t <sub>SUEXT</sub>      | Input Latch External<br>Set-Up          | FO = 32<br>FO = 486 | 0.0        |            | 0.0        |            | 0.0               |            | 0.0        |            | 0.0          |            | ns<br>ns |

| t <sub>HEXT</sub>       | Input Latch External<br>Hold            | FO = 32<br>FO = 486 | 2.8<br>3.3 |            | 3.1<br>3.7 |            | 3.5<br>4.2        |            | 4.1<br>4.9 |            | 5.7<br>6.9   |            | ns<br>ns |

| t <sub>P</sub>          | Minimum Period<br>(1/f <sub>MAX</sub> ) | FO = 32<br>FO = 486 | 4.7<br>5.1 |            | 5.2<br>5.7 |            | 5.7<br>6.2        |            | 6.5<br>7.1 |            | 10.9<br>11.9 |            | ns<br>ns |

Table 44 • A42MX36 Timing Characteristics (Nominal 5.0 V Operation)(Worst-Case Commercial Conditions, VCCA = 4.75 V,  $T_J = 70^{\circ}$ C)

|                    |                                |          | -3 S | peed | -2 S <sub>I</sub> | peed | –1 Sp | peed | Std S | peed | –F Sp | eed  |       |

|--------------------|--------------------------------|----------|------|------|-------------------|------|-------|------|-------|------|-------|------|-------|

| Parame             | ter / Description              |          | Min. | Max. | Min.              | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| t <sub>SUEXT</sub> | Input Latch External           | FO = 32  | 0.0  |      | 0.0               |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

|                    | Set-Up                         | FO = 635 | 0.0  |      | 0.0               |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>HEXT</sub>  | Input Latch External           | FO = 32  | 2.8  |      | 3.2               |      | 3.6   |      | 4.2   |      | 5.9   |      | ns    |

|                    | Hold                           | FO = 635 | 3.3  |      | 3.7               |      | 4.2   |      | 4.9   |      | 6.9   |      | ns    |

| t <sub>P</sub>     | Minimum Period                 | FO = 32  | 5.5  |      | 6.1               |      | 6.6   |      | 7.6   |      | 12.7  |      | ns    |

|                    | (1/f <sub>MAX</sub> )          | FO = 635 | 6.0  |      | 6.6               |      | 7.2   |      | 8.3   |      | 13.8  |      | ns    |

| f <sub>MAX</sub>   | Maximum Datapath               | FO = 32  |      | 180  |                   | 164  |       | 151  |       | 131  |       | 79   | MHz   |

|                    | Frequency                      | FO = 635 |      | 166  |                   | 151  |       | 139  |       | 121  |       | 73   | MHz   |

| TTL Out            | put Module Timing <sup>5</sup> |          |      |      |                   |      |       |      |       |      |       |      |       |

| t <sub>DLH</sub>   | Data-to-Pad HIGH               |          |      | 2.6  |                   | 2.8  |       | 3.2  |       | 3.8  |       | 5.3  | ns    |

| t <sub>DHL</sub>   | Data-to-Pad LOW                |          |      | 3.0  |                   | 3.3  |       | 3.7  |       | 4.4  |       | 6.2  | ns    |

| t <sub>ENZH</sub>  | Enable Pad Z to HIG            | Н        |      | 2.7  |                   | 3.0  |       | 3.3  |       | 3.9  |       | 5.5  | ns    |

| t <sub>ENZL</sub>  | Enable Pad Z to LOV            | V        |      | 3.0  |                   | 3.3  |       | 3.7  |       | 4.3  |       | 6.1  | ns    |

| t <sub>ENHZ</sub>  | Enable Pad HIGH to             | Z        |      | 5.3  |                   | 5.8  |       | 6.6  |       | 7.8  |       | 10.9 | ns    |

Input, output, tristate or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/Os pins are configured by the Designer software as shown in Table 46, page 84.

Table 46 • Configuration of Unused I/Os

| Device           | Configuration |

|------------------|---------------|

| A40MX02, A40MX04 | Pulled LOW    |

| A42MX09, A42MX16 | Pulled LOW    |

| A42MX24, A42MX36 | Tristated     |

In all cases, it is recommended to tie all unused MX I/O pins to LOW on the board. This applies to all dual-purpose pins when configured as I/Os as well.

#### LP, Low Power Mode

Controls the low power mode of all 42MX devices. The device is placed in the low power mode by connecting the LP pin to logic HIGH. In low power mode, all I/Os are tristated, all input buffers are turned OFF, and the core of the device is turned OFF. To exit the low power mode, the LP pin must be set LOW. The device enters the low power mode 800 ns after the LP pin is driven to a logic HIGH. It will resume normal operation in 200 µs after the LP pin is driven to a logic LOW.

#### MODE, Mode

Controls the use of multifunction pins (DCLK, PRA, PRB, SDI, TDO). The MODE pin is held HIGH to provide verification capability. The MODE pin should be terminated to GND through a  $10k\Omega$  resistor so that the MODE pin can be pulled HIGH when required.

#### NC, No Connection

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### PRA, I/O

### PRB, I/OProbe A/B

The Probe pin is used to output data from any user-defined design node within the device. Each diagnostic pin can be used in conjunction with the other probe pin to allow real-time diagnostic output of any signal path within the device. The Probe pin can be used as a user-defined I/O when verification has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. The Probe pin is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### QCLKA/B/C/D, I/O Quadrant Clock

Quadrant clock inputs for A42MX36 devices. When not used as a register control signal, these pins can function as user I/Os.

#### SDI, I/OSerial Data Input

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

#### SDO, I/OSerial Data Output

Serial data output for diagnostic probe and device programming. SDO is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW. SDO is available for 42MX devices only.

When Silicon Explorer II is being used, SDO will act as an output while the "checksum" command is run. It will return to user I/O when "checksum" is complete.

### TCK, I/O Test Clock

Table 51 • PQ144

Table 53 • PQ208

| PQ208      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX16 Function | A42MX24 Function | A42MX36 Function |

| 169        | I/O              | WD, I/O          | WD, I/O          |

| 170        | I/O              | I/O              | I/O              |

| 171        | NC               | I/O              | QCLKD, I/O       |

| 172        | I/O              | I/O              | I/O              |

| 173        | I/O              | I/O              | I/O              |

| 174        | I/O              | I/O              | I/O              |

| 175        | I/O              | I/O              | I/O              |

| 176        | I/O              | WD, I/O          | WD, I/O          |

| 177        | I/O              | WD, I/O          | WD, I/O          |

| 178        | PRA, I/O         | PRA, I/O         | PRA, I/O         |

| 179        | I/O              | I/O              | I/O              |

| 180        | CLKA, I/O        | CLKA, I/O        | CLKA, I/O        |

| 181        | NC               | I/O              | I/O              |

| 182        | NC               | VCCI             | VCCI             |

| 183        | VCCA             | VCCA             | VCCA             |

| 184        | GND              | GND              | GND              |

| 185        | I/O              | I/O              | I/O              |

| 186        | CLKB, I/O        | CLKB, I/O        | CLKB, I/O        |

| 187        | I/O              | I/O              | I/O              |

| 188        | PRB, I/O         | PRB, I/O         | PRB, I/O         |

| 189        | I/O              | I/O              | I/O              |

| 190        | I/O              | WD, I/O          | WD, I/O          |

| 191        | I/O              | WD, I/O          | WD, I/O          |

| 192        | I/O              | I/O              | I/O              |

| 193        | NC               | I/O              | I/O              |

| 194        | NC               | WD, I/O          | WD, I/O          |

| 195        | NC               | WD, I/O          | WD, I/O          |

| 196        | I/O              | I/O              | QCLKC, I/O       |

| 197        | NC               | I/O              | I/O              |

| 198        | I/O              | I/O              | I/O              |

| 199        | I/O              | I/O              | I/O              |

| 200        | I/O              | I/O              | I/O              |

| 201        | NC               | I/O              | I/O              |

| 202        | VCCI             | VCCI             | VCCI             |

| 203        | I/O              | WD, I/O          | WD, I/O          |

| 204        | I/O              | WD, I/O          | WD, I/O          |

| 205        | I/O              | I/O              | I/O              |

Table 54 • PQ240

| PQ240      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX36 Function |  |

| 52         | VCCI             |  |

| 53         | I/O              |  |

| 54         | WD, I/O          |  |

| 55         | WD, I/O          |  |

| 56         | I/O              |  |

| 57         | SDI, I/O         |  |

| 58         | I/O              |  |

| 59         | VCCA             |  |

| 60         | GND              |  |

| 61         | GND              |  |

| 62         | I/O              |  |

| 63         | I/O              |  |

| 64         | I/O              |  |

| 65         | I/O              |  |

| 66         | I/O              |  |

| 67         | I/O              |  |

| 68         | I/O              |  |

| 69         | I/O              |  |

| 70         | I/O              |  |

| 71         | VCCI             |  |

| 72         | I/O              |  |

| 73         | I/O              |  |

| 74         | I/O              |  |

| 75         | I/O              |  |

| 76         | I/O              |  |

| 77         | I/O              |  |

| 78         | I/O              |  |

| 79         | I/O              |  |

| 80         | I/O              |  |

| 81         | I/O              |  |

| 82         | I/O              |  |

| 83         | I/O              |  |

| 84         | I/O              |  |

| 85         | VCCA             |  |

| 86         | I/O              |  |

| 87         | I/O              |  |

| 88         | VCCA             |  |

Table 55 • VQ80

| VQ80       |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A40MX02<br>Function | A40MX04<br>Function |

| 49         | I/O                 | I/O                 |

| 50         | CLK, I/O            | CLK, I/O            |

| 51         | I/O                 | I/O                 |

| 52         | MODE                | MODE                |

| 53         | VCC                 | VCC                 |

| 54         | NC                  | I/O                 |

| 55         | NC                  | I/O                 |

| 56         | NC                  | I/O                 |

| 57         | SDI, I/O            | SDI, I/O            |

| 58         | DCLK, I/O           | DCLK, I/O           |

| 59         | PRA, I/O            | PRA, I/O            |

| 60         | NC                  | NC                  |

| 61         | PRB, I/O            | PRB, I/O            |

| 62         | I/O                 | I/O                 |

| 63         | I/O                 | I/O                 |

| 64         | I/O                 | I/O                 |

| 65         | I/O                 | I/O                 |

| 66         | I/O                 | I/O                 |

| 67         | I/O                 | I/O                 |

| 68         | GND                 | GND                 |

| 69         | I/O                 | I/O                 |

| 70         | I/O                 | I/O                 |

| 71         | I/O                 | I/O                 |

| 72         | I/O                 | I/O                 |

| 73         | I/O                 | I/O                 |

| 74         | VCC                 | VCC                 |

| 75         | I/O                 | I/O                 |

| 76         | I/O                 | I/O                 |

| 77         | I/O                 | I/O                 |

| 78         | I/O                 | I/O                 |

| 79         | I/O                 | I/O                 |

| 80         | I/O                 | I/O                 |

|            |                     |                     |

Table 56 • VQ100

| VQ100      |                     |                     |

|------------|---------------------|---------------------|

| Pin Number | A42MX09<br>Function | A42MX16<br>Function |

| 21         | I/O                 | I/O                 |

| 22         | I/O                 | I/O                 |

| 23         | I/O                 | I/O                 |

| 24         | I/O                 | I/O                 |

| 25         | I/O                 | I/O                 |

| 26         | I/O                 | I/O                 |

| 27         | I/O                 | I/O                 |

| 28         | I/O                 | I/O                 |

| 29         | I/O                 | I/O                 |

| 30         | I/O                 | I/O                 |

| 31         | I/O                 | I/O                 |

| 32         | GND                 | GND                 |

| 33         | I/O                 | I/O                 |

| 34         | I/O                 | I/O                 |

| 35         | I/O                 | I/O                 |

| 36         | I/O                 | I/O                 |

| 37         | I/O                 | I/O                 |

| 38         | VCCA                | VCCA                |

| 39         | I/O                 | I/O                 |

| 40         | I/O                 | I/O                 |

| 41         | I/O                 | I/O                 |

| 42         | I/O                 | I/O                 |

| 43         | I/O                 | I/O                 |

| 44         | GND                 | GND                 |

| 45         | I/O                 | I/O                 |

| 46         | I/O                 | I/O                 |

| 47         | I/O                 | I/O                 |

| 48         | I/O                 | I/O                 |

| 49         | I/O                 | I/O                 |

| 50         | SDO, I/O            | SDO, I/O            |

| 51         | I/O                 | I/O                 |

| 52         | I/O                 | I/O                 |

| 53         | I/O                 | I/O                 |

| 54         | I/O                 | I/O                 |

| 55         | GND                 | GND                 |

| 56         | I/O                 | I/O                 |

Table 57 • TQ176

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 121        | NC               | NC               | I/O              |

| 122        | I/O              | I/O              | I/O              |

| 123        | I/O              | I/O              | I/O              |

| 124        | NC               | I/O              | I/O              |

| 125        | NC               | I/O              | I/O              |

| 126        | NC               | NC               | I/O              |

| 127        | I/O              | I/O              | I/O              |

| 128        | I/O              | I/O              | I/O              |

| 129        | I/O              | I/O              | I/O              |

| 130        | I/O              | I/O              | I/O              |

| 131        | I/O              | I/O              | I/O              |

| 132        | I/O              | I/O              | I/O              |

| 133        | GND              | GND              | GND              |

| 134        | I/O              | I/O              | I/O              |

| 135        | SDI, I/O         | SDI, I/O         | SDI, I/O         |

| 136        | NC               | I/O              | I/O              |

| 137        | I/O              | I/O              | WD, I/O          |

| 138        | I/O              | I/O              | WD, I/O          |

| 139        | I/O              | I/O              | I/O              |

| 140        | NC               | VCCI             | VCCI             |

| 141        | I/O              | I/O              | I/O              |

| 142        | I/O              | I/O              | I/O              |

| 143        | NC               | I/O              | I/O              |

| 144        | NC               | I/O              | WD, I/O          |

| 145        | NC               | NC               | WD, I/O          |

| 146        | I/O              | I/O              | I/O              |

| 147        | NC               | I/O              | I/O              |

| 148        | I/O              | I/O              | I/O              |

| 149        | I/O              | I/O              | I/O              |

| 150        | I/O              | I/O              | WD, I/O          |

| 151        | NC               | I/O              | WD, I/O          |

| 152        | PRA, I/O         | PRA, I/O         | PRA, I/O         |

| 153        | I/O              | I/O              | I/O              |

| 154        | CLKA, I/O        | CLKA, I/O        | CLKA, I/O        |

| 155        | VCCA             | VCCA             | VCCA             |

| 156        | GND              | GND              | GND              |

|            |                  |                  |                  |

Table 58 • CQ208

| CQ208      |                  |  |

|------------|------------------|--|

| Pin Number | A42MX36 Function |  |

| 1          | GND              |  |

| 2          | VCCA             |  |

| 3          | MODE             |  |

| 4          | I/O              |  |

| 5          | I/O              |  |

| 6          | I/O              |  |

| 7          | I/O              |  |

| 8          | I/O              |  |

| 9          | I/O              |  |

| 10         | I/O              |  |

| 11         | I/O              |  |

| 12         | I/O              |  |

| 13         | I/O              |  |

| 14         | I/O              |  |

| 15         | I/O              |  |

| 16         | I/O              |  |

| 17         | VCCA             |  |

| 18         | I/O              |  |

| 19         | I/O              |  |

| 20         | I/O              |  |

| 21         | I/O              |  |

| 22         | GND              |  |

| 23         | I/O              |  |

| 24         | I/O              |  |

| 25         | I/O              |  |

| 26         | I/O              |  |

| 27         | GND              |  |

| 28         | VCCI             |  |

| 29         | VCCA             |  |

| 30         | I/O              |  |

| 31         | I/O              |  |

| 32         | VCCA             |  |

| 33         | I/O              |  |

| 34         | I/O              |  |

| 35         | I/O              |  |

| 36         | I/O              |  |

|            | <del></del>      |  |

Table 62 • CQ172

| 60       | I/O  |

|----------|------|

| 61       | I/O  |

| 62       | I/O  |

| 63       | I/O  |

| 64       | I/O  |

| 65       | GND  |

| 66       | VCC  |

| 67       | I/O  |

| 68       | I/O  |

| 69       | I/O  |

| 70       | I/O  |

| 71       | I/O  |

| 72       | I/O  |

| 73       | I/O  |

| 74       | I/O  |

| 75       | GND  |

| 76       | I/O  |

| 77       | I/O  |

| 78       | I/O  |

| 79       | I/O  |

| 80       | VCCI |

| 81       | I/O  |

| 82       | I/O  |

| 83       | I/O  |

| 84       | I/O  |

| 85       | SDO  |

| 86       | I/O  |

| 87       | I/O  |

| 88       | I/O  |

| 89       | I/O  |

| 90       | I/O  |

| 91       | I/O  |

| 92       | I/O  |

| 93       | I/O  |

| 94       | I/O  |

| 95       | I/O  |

| 96       | I/O  |

|          | ., • |

| 97       | 1/0  |

| 97<br>98 |      |