# Ξ·XF

Welcome to E-XFL.COM

### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Det | tai | ls |

|-----|-----|----|

|     |     |    |

| Details                        |                                                                           |

|--------------------------------|---------------------------------------------------------------------------|

| Product Status                 | Active                                                                    |

| Number of LABs/CLBs            | -                                                                         |

| Number of Logic Elements/Cells | ·                                                                         |

| Total RAM Bits                 | -                                                                         |

| Number of I/O                  | 176                                                                       |

| Number of Gates                | 36000                                                                     |

| Voltage - Supply               | 3V ~ 3.6V, 4.75V ~ 5.25V                                                  |

| Mounting Type                  | Surface Mount                                                             |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                           |

| Package / Case                 | 208-BFQFP                                                                 |

| Supplier Device Package        | 208-PQFP (28x28)                                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/a42mx24-fpqg208 |

|                                |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- The Transient Current, page 13 is new (SAR 36930).

- Package names were revised according to standards established in Package Mechanical Drawings (SAR 34774)

## 1.7 Revision 9.0

The following is a summary of the changes in revision 9.0 of this document

In Table 20, page 23, the limits in VI were changed from -0.5 to VCCI + 0.5 to -0.5 to VCCA + 0.5

In Table 22, page 25,  $V_{OH}$  was changed from 3.7 to 2.4 for the min in industrial and military.  $V_{IH}$  had  $V_{CCI}$  and that was changed to VCCA

## 1.8 Revision 6.0

The following is a summary of the changes in revision 6.0 of this document.

- The Ease of Integration, page 1 was updated

- The Temperature Grade Offerings, page 5 is new

- The Speed Grade Offerings, page 5 is new

- The General Description, page 6 was updated

- The MultiPlex I/O Modules, page 11 was updated

- The User Security, page 12 was updated

- Table 6, page 13 was updated

- The Power Dissipation, page 14 was updated.

- The Static Power Component, page 14 was updated

- The Equivalent Capacitance, page 15 was updated

- Figure 13, page 17 was updated

- Table 10, page 18 was updated.

- Figure 14, page 18 was updated.

- Table 11, page 19 was updated.

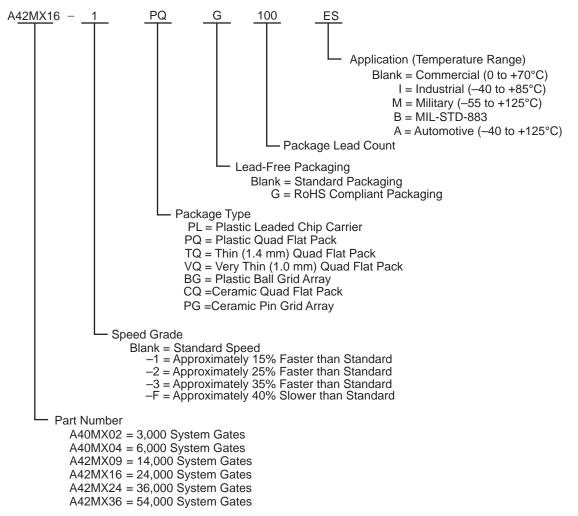

## 2.3 Ordering Information

The following figure shows ordering information.All the following tables show plastic and ceramic device resources, temperature and speed grade offerings.

### Figure 1 • Ordering Information

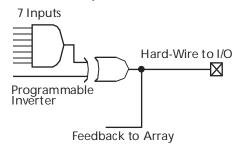

### *Figure 5* • A42MX24 and A42MX36 D-Module Implementation

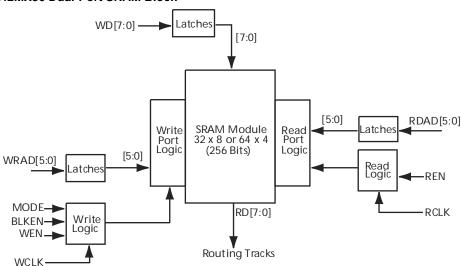

### Figure 6 • A42MX36 Dual-Port SRAM Block

### 3.2.3 Routing Structure

The MX architecture uses vertical and horizontal routing tracks to interconnect the various logic and I/O modules. These routing tracks are metal interconnects that may be continuous or split into segments. Varying segment lengths allow the interconnect of over 90% of design tracks to occur with only two antifuse connections. Segments can be joined together at the ends using antifuses to increase their lengths up to the full length of the track. All interconnects can be accomplished with a maximum of four antifuses.

### 3.2.3.1 Horizontal Routing

Horizontal routing tracks span the whole row length or are divided into multiple segments and are located in between the rows of modules. Any segment that spans more than one-third of the row length is considered a long horizontal segment. A typical channel is shown in Figure 7, page 10. Within horizontal routing, dedicated routing tracks are used for global clock networks and for power and ground tie-off tracks. Non-dedicated tracks are used for signal nets.

### 3.2.3.2 Vertical Routing

Another set of routing tracks run vertically through the module. There are three types of vertical tracks: input, output, and long. Long tracks span the column length of the module, and can be divided into multiple segments. Each segment in an input track is dedicated to the input of a particular module; each segment in an output track is dedicated to the output of a particular module. Long segments are uncommitted and can be assigned during routing.

Each output segment spans four channels (two above and two below), except near the top and bottom of the array, where edge effects occur. Long vertical tracks contain either one or two segments. An example of vertical routing tracks and segments is shown in Figure 7, page 10.

| Device Type | r1 routed_Clk1 | r2 routed_Clk2 |

|-------------|----------------|----------------|

| A40MX02     | 41.4           | N/A            |

| A40MX04     | 68.6           | N/A            |

| A42MX09     | 118            | 118            |

| A42MX16     | 165            | 165            |

| A42MX24     | 185            | 185            |

| A42MX36     | 220            | 220            |

Fixed Capacitance Values for MX FPGAs (pF)

$f_{a2}$  = Average second routed array clock rate in MHz)

Table 7 •

### 3.4.6 Test Circuitry and Silicon Explorer II Probe

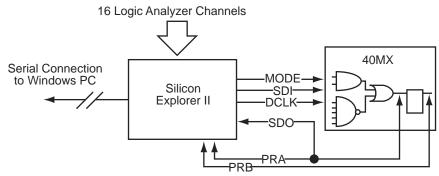

MX devices contain probing circuitry that provides built-in access to every node in a design, via the use of Silicon Explorer II. Silicon Explorer II is an integrated hardware and software solution that, in conjunction with the Designer software, allow users to examine any of the internal nets of the device while it is operating in a prototyping or a production system. The user can probe into an MX device without changing the placement and routing of the design and without using any additional resources. Silicon Explorer II's noninvasive method does not alter timing or loading effects, thus shortening the debug cycle and providing a true representation of the device under actual functional situations.

Silicon Explorer II samples data at 100 MHz (asynchronous) or 66 MHz (synchronous). Silicon Explorer II attaches to a PC's standard COM port, turning the PC into a fully functional 18-channel logic analyzer. Silicon Explorer II allows designers to complete the design verification process at their desks and reduces verification time from several hours per cycle to a few seconds.

Silicon Explorer II is used to control the MODE, DCLK, SDI and SDO pins in MX devices to select the desired nets for debugging. The user simply assigns the selected internal nets in the Silicon Explorer II software to the PRA/PRB output pins for observation. Probing functionality is activated when the MODE pin is held HIGH.

Figure 12, page 16 illustrates the interconnection between Silicon Explorer II and 40MX devices, while Figure 13, page 17 illustrates the interconnection between Silicon Explorer II and 42MX devices

To allow for probing capabilities, the security fuses must not be programmed. (See User Security, page 12 for the security fuses of 40MX and 42MX devices). Table 8, page 17 summarizes the possible device configurations for probing.

PRA and PRB pins are dual-purpose pins. When the "Reserve Probe Pin" is checked in the Designer software, PRA and PRB pins are reserved as dedicated outputs for probing. If PRA and PRB pins are required as user I/Os to achieve successful layout and "Reserve Probe Pin" is checked, the layout tool will override the option and place user I/Os on PRA and PRB pins.

### Figure 12 • Silicon Explorer II Setup with 40MX

reliability. Devices should not be operated outside the recommended operating conditions.

Table 21 •

Recommended Operating Conditions

| Parameter          | Commercial   | Industrial | Military    | Units |

|--------------------|--------------|------------|-------------|-------|

| Temperature Range* | 0 to +70     | -40 to +85 | -55 to +125 | °C    |

| VCCA               | 4.75 to 5.25 | 4.5 to 5.5 | 4.5 to 5.5  | V     |

| VCCI               | 3.14 to 3.47 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

**Note:** \*Ambient temperature (T<sub>A</sub>) is used for commercial and industrial grades; case temperature (T<sub>C</sub>) is used for military grades.

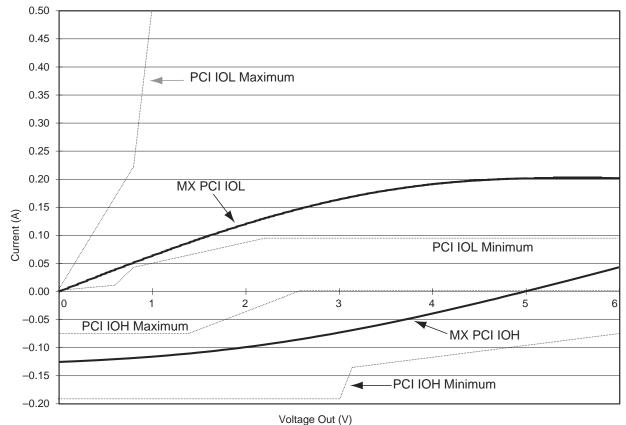

### 3.9.3 Output Drive Characteristics for 3.3 V PCI Signaling

|                  |                            |                   | PCI  |           | MX   |                     |       |

|------------------|----------------------------|-------------------|------|-----------|------|---------------------|-------|

| Symbol           | Parameter                  | Condition         | Min. | Max.      | Min. | Max.                | Units |

| VCCI             | Supply Voltage for I/Os    |                   | 3.0  | 3.6       | 3.0  | 3.6 <sup>2</sup>    | V     |

| VIH              | Input High Voltage         |                   | 0.5  | VCC + 0.5 | 0.5  | VCCI + 0.3          | V     |

| VIL              | Input Low Voltage          |                   | -0.5 | 0.8       | -0.3 | 0.8                 | V     |

| IIH              | Input High Leakage Current | VIN = 2.7 V       |      | 70        |      | 10                  | μA    |

| IIL              | Input Leakage Current      |                   |      | -70       |      | -10                 | μA    |

| VOH              | Output High Voltage        | IOUT = -2 mA      | 0.9  |           | 3.3  |                     | V     |

| VOL              | Output Low Voltage         | IOUT = 3 mA, 6 mA |      | 0.1       |      | 0.1 VCCI            | V     |

| C <sub>IN</sub>  | Input Pin Capacitance      |                   |      | 10        |      | 10                  | pF    |

| C <sub>CLK</sub> | CLK Pin Capacitance        |                   | 5    | 12        |      | 10                  | pF    |

| L <sub>PIN</sub> | Pin Inductance             |                   |      | 20        |      | < 8 nH <sup>3</sup> | nH    |

### Table 25 • DC Specification (3.3 V PCI Signaling)<sup>1</sup>

1. PCI Local Bus Specification, Version 2.1, Section 4.2.2.1.

2. Maximum rating for VCCI -0.5 V to 7.0V.

3. Dependent upon the chosen package. PCI recommends QFP and BGA packaging to reduce pin inductance and capacitance.

### Table 26 • AC Specifications for (3.3 V PCI Signaling)\*

|          |                       | Condition           | PCI                   | Ν    | – Units |      |          |

|----------|-----------------------|---------------------|-----------------------|------|---------|------|----------|

| Symbol   | Parameter             | Condition           | Min.                  | Max. | Min.    | Max. | - 011115 |

| ICL      | Low Clamp Current     | $-5 < VIN \leq -1$  | -25 + (VIN +1) /0.015 |      | -60     | -10  | mA       |

| Slew (r) | Output Rise Slew Rate | 0.2 V to 0.6 V load | 1                     | 4    | 1.8     | 2.8  | V/ns     |

| Slew (f) | Output Fall Slew Rate | 0.6 V to 0.2 V load | 1                     | 4    | 2.8     | 4.0  | V/ns     |

Note: \*PCI Local Bus Specification, Version 2.1, Section 4.2.2.2.

Figure 16 • Typical Output Drive Characteristics (Based Upon Measured Data)

### 3.9.4 Junction Temperature (T<sub>J</sub>)

The temperature variable in the Designer software refers to the junction temperature, not the ambient temperature. This is an important distinction because the heat generated from dynamic power consumption is usually hotter than the ambient temperature. The following equation can be used to calculate junction temperature.

Junction Temperature =  $\Delta T + T_a(1)$

EQ 4

where:

- T<sub>a</sub> = Ambient Temperature

- $\Delta T$  = Temperature gradient between junction (silicon) and ambient

- $\Delta T = \theta_{ia} * P(2)$

- P = Power

- $\theta_{ia}$  = Junction to ambient of package.  $\theta_{ia}$  numbers are located in Table 27, page 29.

### 3.9.5 Package Thermal Characteristics

The device junction-to-case thermal characteristic is  $\theta_{jc}$ , and the junction-to-ambient air characteristic is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown with two different air flow rates.

The maximum junction temperature is 150°C.

Maximum power dissipation for commercial- and industrial-grade devices is a function of  $\theta_{ia}$ .

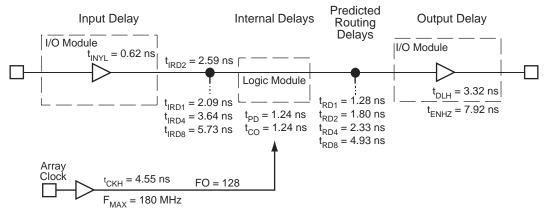

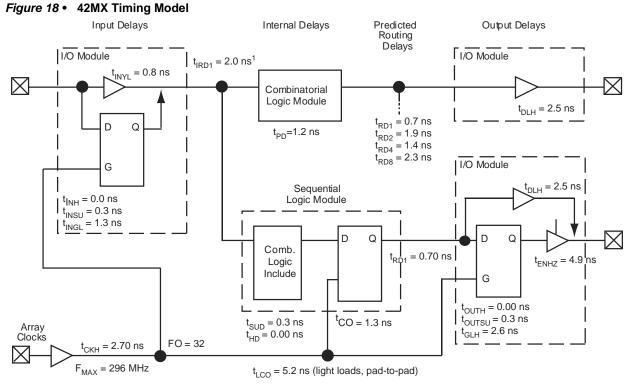

## 3.10 Timing Models

The following figures show various timing models.

### Figure 17 • 40MX Timing Model\*

Note: Values are shown for 40MX –3 speed devices at 5.0 V worst-case commercial conditions.

Note: 1. Input module predicted routing delay

Note: 2. Values are shown for A42MX09 -3 at 5.0 V worst-case commercial conditions.

# Table 35 •A40MX02 Timing Characteristics (Nominal 3.3 V Operation) (continued)<br/>(Worst-Case Commercial Conditions, VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                              |                                             |                        | –3 Sp      | beed       | –2 S       | beed       | –1 S       | beed       | Std S      | Speed        | –F Speed   |              |       |

|------------------------------|---------------------------------------------|------------------------|------------|------------|------------|------------|------------|------------|------------|--------------|------------|--------------|-------|

| Paramete                     | er / Description                            |                        | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.         | Min.       | Max.         | Units |

| t <sub>RD1</sub>             | FO = 1 Routing Dela                         | ıy                     |            | 2.0        |            | 2.2        |            | 2.5        |            | 3.0          |            | 4.2          | ns    |

| t <sub>RD2</sub>             | FO = 2 Routing Dela                         | ıy                     |            | 2.7        |            | 3.1        |            | 3.5        |            | 4.1          |            | 5.7          | ns    |

| t <sub>RD3</sub>             | FO = 3 Routing Dela                         | ıy                     |            | 3.4        |            | 3.9        |            | 4.4        |            | 5.2          |            | 7.3          | ns    |

| t <sub>RD4</sub>             | FO = 4 Routing Dela                         | ıy                     |            | 4.2        |            | 4.8        |            | 5.4        |            | 6.3          |            | 8.9          | ns    |

| t <sub>RD8</sub>             | FO = 8 Routing Dela                         | ıy                     |            | 7.1        |            | 8.2        |            | 9.2        |            | 10.9         |            | 15.2         | ns    |

| Logic Mo                     | odule Sequential Timi                       | ng²                    |            |            |            |            |            |            |            |              |            |              |       |

| t <sub>SUD</sub>             | Flip-Flop (Latch)<br>Data Input Set-Up      |                        | 4.3        |            | 4.9        |            | 5.6        |            | 6.6        |              | 9.2        |              | ns    |

| t <sub>HD</sub> <sup>3</sup> | Flip-Flop (Latch)<br>Data Input Hold        |                        | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |              | 0.0        |              | ns    |

| t <sub>SUENA</sub>           | Flip-Flop (Latch) Ena                       | able Set-Up            | 4.3        |            | 4.9        |            | 5.6        |            | 6.6        |              | 9.2        |              | ns    |

| t <sub>HENA</sub>            | Flip-Flop (Latch) Ena                       | able Hold              | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |              | 0.0        |              | ns    |

| t <sub>WCLKA</sub>           | Flip-Flop (Latch)<br>Clock Active Pulse V   | Vidth                  | 4.6        |            | 5.3        |            | 6.0        |            | 7.0        |              | 9.8        |              | ns    |

| t <sub>WASYN</sub>           | Flip-Flop (Latch)<br>Asynchronous Pulse     | Width                  | 4.6        |            | 5.3        |            | 6.0        |            | 7.0        |              | 9.8        |              | ns    |

| t <sub>A</sub>               | Flip-Flop Clock Input                       | t Period               | 6.8        |            | 7.8        |            | 8.9        |            | 10.4       |              | 14.6       |              | ns    |

| f <sub>MAX</sub>             | Flip-Flop (Latch) Clo<br>Frequency (FO = 12 |                        |            | 109        |            | 101        |            | 92         |            | 80           |            | 48           | MHz   |

| Input Mo                     | dule Propagation Del                        | lays                   |            |            |            |            |            |            |            |              |            |              |       |

| t <sub>INYH</sub>            | Pad-to-Y HIGH                               |                        |            | 1.0        |            | 1.1        |            | 1.3        |            | 1.5          |            | 2.1          | ns    |

| t <sub>INYL</sub>            | Pad-to-Y LOW                                |                        |            | 0.9        |            | 1.0        |            | 1.1        |            | 1.3          |            | 1.9          | ns    |

| Input Mo                     | dule Predicted Routi                        | ng Delays <sup>1</sup> |            |            |            |            |            |            |            |              |            |              |       |

| t <sub>IRD1</sub>            | FO = 1 Routing Dela                         | ıy                     |            | 2.9        |            | 3.4        |            | 3.8        |            | 4.5          |            | 6.3          | ns    |

| t <sub>IRD2</sub>            | FO = 2 Routing Dela                         | ıy                     |            | 3.6        |            | 4.2        |            | 4.8        |            | 5.6          |            | 7.8          | ns    |

| t <sub>IRD3</sub>            | FO = 3 Routing Dela                         | ıy                     |            | 4.4        |            | 5.0        |            | 5.7        |            | 6.7          |            | 9.4          | ns    |

| t <sub>IRD4</sub>            | FO = 4 Routing Dela                         | ıy                     |            | 5.1        |            | 5.9        |            | 6.7        |            | 7.8          |            | 11.0         | ns    |

| t <sub>IRD8</sub>            | FO = 8 Routing Dela                         | ıy                     |            | 8.0        |            | 9.26       |            | 10.5       |            | 12.6         |            | 17.3         | ns    |

| Global C                     | lock Network                                |                        |            |            |            |            |            |            |            |              |            |              |       |

| t <sub>СКН</sub>             | Input LOW to HIGH                           | FO = 16<br>FO = 128    |            | 6.4<br>6.4 |            | 7.4<br>7.4 |            | 8.3<br>8.3 |            | 9.8<br>9.8   |            | 13.7<br>13.7 | ns    |

| t <sub>CKL</sub>             | Input HIGH to LOW                           | FO = 16<br>FO = 128    |            | 6.7<br>6.7 |            | 7.8<br>7.8 |            | 8.8<br>8.8 |            | 10.4<br>10.4 |            | 14.5<br>14.5 | ns    |

| t <sub>PWH</sub>             | Minimum Pulse<br>Width HIGH                 | FO = 16<br>FO = 128    | 3.1<br>3.3 |            | 3.6<br>3.8 |            | 4.1<br>4.3 |            | 4.8<br>5.1 |              | 6.7<br>7.1 |              | ns    |

| t <sub>PWL</sub>             | Minimum Pulse<br>Width LOW                  | FO = 16<br>FO = 128    | 3.1<br>3.3 |            | 3.6<br>3.8 |            | 4.1<br>4.3 |            | 4.8<br>5.1 |              | 6.7<br>7.1 |              | ns    |

| t <sub>CKSW</sub>            | Maximum Skew                                | FO = 16<br>FO = 128    |            | 0.6<br>0.8 |            | 0.6<br>0.9 |            | 0.7<br>1.0 |            | 0.8<br>1.2   |            | 1.2<br>1.6   | ns    |

# Table 40 •A42MX16 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                               | –3 S       | peed       | –2 S       | peed       | –1 S       | peed       | Std S      | speed      | –F S       | peed       |          |

|--------------------|-----------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|----------|

| Paramet            | ter / Description                             | Min.       | Max.       | Units    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                          |            | 1.3        |            | 1.4        |            | 1.6        |            | 1.9        |            | 2.7        | ns       |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |            | 1.6        |            | 1.7        |            | 2.0        |            | 2.3        |            | 3.2        | ns       |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                          |            | 2.6        |            | 2.9        |            | 3.2        |            | 3.8        |            | 5.3        | ns       |

| Logic M            | odule Sequential Timing <sup>3,4</sup>        |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up        | 0.3        |            | 0.4        |            | 0.4        |            | 0.5        |            | 0.7        |            | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input Hold             | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.7        |            | 0.8        |            | 0.9        |            | 1.0        |            | 1.4        |            | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width | 3.4        |            | 3.8        |            | 4.3        |            | 5.0        |            | 7.1        |            | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 4.5        |            | 5.0        |            | 5.6        |            | 6.6        |            | 9.2        |            | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input Period                  | 6.8        |            | 7.6        |            | 8.6        |            | 10.1       |            | 14.1       |            | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Hold                       | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Set-Up                     | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 1.0        |            | ns       |

| t <sub>OUTH</sub>  | Output Buffer Latch Hold                      | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>OUTSU</sub> | Output Buffer Latch Set-Up                    | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 1.0        |            | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock Frequence             | зy         | 215        |            | 195        |            | 179        |            | 156        |            | 94         | MHz      |

| Input Mo           | odule Propagation Delays                      |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                 |            | 1.1        |            | 1.2        |            | 1.3        |            | 1.6        |            | 2.2        | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                  |            | 0.8        |            | 0.9        |            | 1.0        |            | 1.2        |            | 1.7        | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                                   |            | 1.4        |            | 1.6        |            | 1.8        |            | 2.1        |            | 2.9        | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                    |            | 1.4        |            | 1.6        |            | 1.8        |            | 2.1        |            | 2.9        | ns       |

| Input Me           | odule Predicted Routing Delays <sup>2</sup>   | 2          |            |            |            |            |            |            |            |            |            |          |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                          |            | 1.8        |            | 2.0        |            | 2.3        |            | 2.7        |            | 4.0        | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                          |            | 2.1        |            | 2.3        |            | 2.6        |            | 3.1        |            | 4.3        | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                          |            | 2.3        |            | 2.6        |            | 3.0        |            | 3.5        |            | 4.9        | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                          |            | 2.6        |            | 3.0        |            | 3.3        |            | 3.9        |            | 5.4        | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                          |            | 3.6        |            | 4.0        |            | 4.6        |            | 5.4        |            | 7.5        | ns       |

| Global (           | Clock Network                                 |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>CKH</sub>   | Input LOW to HIGH FO = 32<br>FO = 384         |            | 2.6<br>2.9 |            | 2.9<br>3.2 |            | 3.3<br>3.6 |            | 3.9<br>4.3 |            | 5.4<br>6.0 | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW FO = 32<br>FO = 384         |            | 3.8<br>4.5 |            | 4.2<br>5.0 |            | 4.8<br>5.6 |            | 5.6<br>6.6 |            | 7.8<br>9.2 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse WidthFO = 32HIGHFO = 384        | 3.2<br>3.7 |            | 3.5<br>4.1 |            | 4.0<br>4.6 |            | 4.7<br>5.4 |            | 6.6<br>7.6 |            | ns<br>ns |

|                    |                                           |                        | –3 S       | peed       | –2 Sp      | eed        | –1 Sj      | beed       | Std S      | Speed      | –F Sp        | beed         |          |

|--------------------|-------------------------------------------|------------------------|------------|------------|------------|------------|------------|------------|------------|------------|--------------|--------------|----------|

| Paramete           | er / Description                          |                        | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.         | Max.         | Units    |

| Logic Mo           | odule Sequential Timi                     | ng <sup>3, 4</sup>     |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up    |                        | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 0.9          |              | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data                    | a Input Hold           | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Ena                     | ble Set-Up             | 1.0        |            | 1.1        |            | 1.2        |            | 1.4        |            | 2.0          |              | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Ena                     | ble Hold               | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse W | /idth                  | 4.8        |            | 5.3        |            | 6.0        |            | 7.1        |            | 9.9          |              | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse   | Width                  | 6.2        |            | 6.9        |            | 7.9        |            | 9.2        |            | 12.9         |              | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input                     | Period                 | 9.5        |            | 10.6       |            | 12.0       |            | 14.1       |            | 19.8         |              | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Ho                     | old                    | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Se                     | et-Up                  | 0.7        |            | 0.8        |            | 0.9        |            | 1.01       |            | 1.4          |              | ns       |

| t <sub>оитн</sub>  | Output Buffer Latch H                     | Hold                   | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0          |              | ns       |

| t <sub>outsu</sub> | Output Buffer Latch S                     | Set-Up                 | 0.7        |            | 0.8        |            | 0.89       |            | 1.01       |            | 1.4          |              | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Cloo<br>Frequency       | ck                     |            | 129        |            | 117        |            | 108        |            | 94         |              | 56           | MHz      |

| Input Mo           | dule Propagation Del                      | ays                    |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                             |                        |            | 1.5        |            | 1.6        |            | 1.9        |            | 2.2        |              | 3.1          | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                              |                        |            | 1.1        |            | 1.3        |            | 1.4        |            | 1.7        |              | 2.4          | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                               |                        |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9        |              | 4.1          | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                |                        |            | 2.0        |            | 2.2        |            | 2.5        |            | 2.9        |              | 4.1          | ns       |

| Input Mo           | dule Predicted Routir                     | ng Delays <sup>2</sup> |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>IRD1</sub>  | FO = 1 Routing<br>Delay                   |                        |            | 2.6        |            | 2.9        |            | 3.2        |            | 3.8        |              | 5.3          | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing<br>Delay                   |                        |            | 2.9        |            | 3.2        |            | 3.7        |            | 4.3        |              | 6.1          | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing<br>Delay                   |                        |            | 3.3        |            | 3.6        |            | 4.1        |            | 4.9        |              | 6.8          | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing<br>Delay                   |                        |            | 3.6        |            | 4.0        |            | 4.6        |            | 5.4        |              | 7.6          | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing<br>Delay                   |                        |            | 5.1        |            | 5.6        |            | 6.4        |            | 7.5        |              | 10.5         | ns       |

| Global C           | lock Network                              |                        |            |            |            |            |            |            |            |            |              |              |          |

| t <sub>CKH</sub>   | Input LOW to HIGH                         | FO = 32<br>FO = 384    |            | 4.4<br>4.8 |            | 4.8<br>5.3 |            | 5.5<br>6.0 |            | 6.5<br>7.1 |              | 9.0<br>9.9   | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW                         | FO = 32<br>FO = 384    |            | 5.3<br>6.2 |            | 5.9<br>6.9 |            | 6.7<br>7.9 |            | 7.8<br>9.2 |              | 11.0<br>12.9 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH               | FO = 32<br>FO = 384    | 5.7<br>6.6 |            | 6.3<br>7.4 |            | 7.1<br>8.3 |            | 8.4<br>9.8 |            | 11.8<br>13.7 |              | ns<br>ns |

# Table 41 • A42MX16 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                   |                                                |                     | –3 S       | peed | –2 Sj      | beed | –1 S        | beed | Std S        | peed | –F S         | peed |          |

|-------------------|------------------------------------------------|---------------------|------------|------|------------|------|-------------|------|--------------|------|--------------|------|----------|

| Paramet           | ter / Description                              |                     | Min.       | Max. | Min.       | Max. | Min.        | Max. | Min.         | Max. | Min.         | Max. | Units    |

| TTL Out           | put Module Timing <sup>5</sup> (con            | tinued)             |            |      |            |      |             |      |              |      |              |      |          |

| t <sub>LH</sub>   | I/O Latch Output Hold                          |                     | 0.0        |      | 0.0        |      | 0.0         |      | 0.0          |      | 0.0          |      | ns       |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O  |                     |            | 7.7  |            | 8.5  |             | 9.6  |              | 11.3 |              | 15.9 | ns       |

| t <sub>ACO</sub>  | Array Latch Clock-to-Ou<br>(Pad-to-Pad) 32 I/O | ut                  |            | 14.8 |            | 16.5 |             | 18.7 |              | 22.0 |              | 30.8 | ns       |

| d <sub>TLH</sub>  | Capacitive Loading, LO                         | W to HIGH           |            | 0.05 |            | 0.05 |             | 0.06 |              | 0.07 |              | 0.10 | ns/pF    |

| d <sub>THL</sub>  | Capacitive Loading, HIC                        | GH to LOW           |            | 0.04 |            | 0.04 |             | 0.05 |              | 0.06 |              | 0.08 | ns/pF    |

| CMOS C            | Dutput Module Timing <sup>5</sup>              |                     |            |      |            |      |             |      |              |      |              |      |          |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                               |                     |            | 4.8  |            | 5.3  |             | 5.5  |              | 6.4  |              | 9.0  | ns       |

| t <sub>DHL</sub>  | Data-to-Pad LOW                                |                     |            | 3.5  |            | 3.9  |             | 4.1  |              | 4.9  |              | 6.8  | ns       |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH                           |                     |            | 3.6  |            | 4.0  |             | 4.5  |              | 5.3  |              | 7.4  | ns       |

| t <sub>ENZL</sub> | Enable Pad Z to LOW                            |                     |            | 3.4  |            | 4.0  |             | 5.0  |              | 5.8  |              | 8.2  | ns       |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z                           |                     |            | 7.2  |            | 8.0  |             | 9.0  |              | 10.7 |              | 14.9 | ns       |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                            |                     |            | 6.7  |            | 7.5  |             | 8.5  |              | 9.9  |              | 13.9 | ns       |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                  |                     |            | 6.8  |            | 7.6  |             | 8.6  |              | 10.1 |              | 14.2 | ns       |

| t <sub>GHL</sub>  | G-to-Pad LOW                                   |                     |            | 6.8  |            | 7.6  |             | 8.6  |              | 10.1 |              | 14.2 | ns       |

| t <sub>LSU</sub>  | I/O Latch Set-Up                               |                     | 0.7        |      | 0.7        |      | 0.8         |      | 1.0          |      | 1.4          |      | ns       |

| t <sub>LH</sub>   | I/O Latch Hold                                 |                     | 0.0        |      | 0.0        |      | 0.0         |      | 0.0          |      | 0.0          |      | ns       |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O  |                     |            | 7.7  |            | 8.5  |             | 9.6  |              | 11.3 |              | 15.9 | ns       |

| t <sub>ACO</sub>  | Array Latch Clock-to-Ou<br>(Pad-to-Pad) 32 I/O | ut                  |            | 14.8 |            | 16.5 |             | 18.7 |              | 22.0 |              | 30.8 | ns       |

| d <sub>TLH</sub>  | Capacitive Loading, LO                         | W to HIGH           |            | 0.05 |            | 0.05 |             | 0.06 |              | 0.07 |              | 0.10 | ns/pF    |

| d <sub>THL</sub>  | Capacitive Loading, HIC                        | GH to LOW           |            | 0.04 |            | 0.04 |             | 0.05 |              | 0.06 |              | 0.08 | ns/pF    |

| t <sub>HEXT</sub> | Input Latch External<br>Hold                   | FO = 32<br>FO = 486 | 3.9<br>4.6 |      | 4.3<br>5.2 |      | 4.9<br>5.8  |      | 5.7<br>6.9   |      | 8.1<br>9.6   |      | ns<br>ns |

| t <sub>P</sub>    | Minimum Period<br>(1/f <sub>MAX</sub> )        | FO = 32<br>FO = 486 | 7.8<br>8.6 |      | 8.7<br>9.5 |      | 9.5<br>10.4 |      | 10.8<br>11.9 |      | 18.2<br>19.9 |      | ns<br>ns |

# Table 43 • A42MX24 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

1. For dual-module macros, use  $t_{PD1} + t_{RD1} + t_{PDn}$ ,  $t_{CO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

4. Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

|                   |                                                 | –3 S | peed | –2 S | beed | –1 Sp | beed | Std S | peed | –F Sp | beed |       |

|-------------------|-------------------------------------------------|------|------|------|------|-------|------|-------|------|-------|------|-------|

| Parame            | eter / Description                              | Min. | Max. | Min. | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| TTL Ou            | tput Module Timing <sup>5</sup> (Continued)     |      |      |      |      |       |      |       |      |       |      |       |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                             |      | 4.9  |      | 5.5  |       | 6.2  |       | 7.3  |       | 10.2 | ns    |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                   |      | 2.9  |      | 3.3  |       | 3.7  |       | 4.4  |       | 6.1  | ns    |

| t <sub>GHL</sub>  | G-to-Pad LOW                                    |      | 2.9  |      | 3.3  |       | 3.7  |       | 4.4  |       | 6.1  | ns    |

| t <sub>LSU</sub>  | I/O Latch Output Set-Up                         | 0.5  |      | 0.5  |      | 0.6   |      | 0.7   |      | 1.0   |      | ns    |

| t <sub>LH</sub>   | I/O Latch Output Hold                           | 0.0  |      | 0.0  |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O   |      | 5.7  |      | 6.3  |       | 7.1  |       | 8.4  |       | 11.8 | ns    |

| t <sub>ACO</sub>  | Array Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O |      | 7.8  |      | 8.6  |       | 9.8  |       | 11.5 |       | 16.1 | ns    |

| d <sub>TLH</sub>  | Capacitive Loading,<br>LOW to HIGH              |      | 0.07 |      | 0.08 |       | 0.09 |       | 0.10 |       | 0.14 | ns/pF |

| d <sub>THL</sub>  | Capacitive Loading,<br>HIGH to LOW              |      | 0.07 |      | 0.08 |       | 0.09 |       | 0.10 |       | 0.14 | ns/pF |

# Table 44 •A42MX36 Timing Characteristics (Nominal 5.0 V Operation)(Worst-Case Commercial Conditions,<br/>VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                   |                                                 | –3 S | peed | –2 S | peed | –1 S | peed | Std S | Speed | –F S | peed |       |

|-------------------|-------------------------------------------------|------|------|------|------|------|------|-------|-------|------|------|-------|

| Parame            | eter / Description                              | Min. | Max. | Min. | Max. | Min. | Max. | Min.  | Max.  | Min. | Max. | Units |

| t <sub>ACO</sub>  | Array Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O |      | 10.9 |      | 12.1 |      | 13.7 |       | 16.1  |      | 22.5 | ns    |

| d <sub>TLH</sub>  | Capacitive Loading, LOW to HIGH                 |      | 0.10 |      | 0.11 |      | 0.12 |       | 0.14  |      | 0.20 | ns/pF |

| d <sub>THL</sub>  | Capacitive Loading, HIGH to LOW                 |      | 0.10 |      | 0.11 |      | 0.12 |       | 0.14  |      | 0.20 | ns/pF |

| CMOS              | Output Module Timing <sup>5</sup>               |      |      |      |      |      |      |       |       |      |      |       |

| t <sub>DLH</sub>  | Data-to-Pad HIGH                                |      | 4.9  |      | 5.5  |      | 6.2  |       | 7.3   |      | 10.3 | ns    |

| t <sub>DHL</sub>  | Data-to-Pad LOW                                 |      | 3.4  |      | 3.8  |      | 4.3  |       | 5.1   |      | 7.1  | ns    |

| t <sub>ENZH</sub> | Enable Pad Z to HIGH                            |      | 3.7  |      | 4.1  |      | 4.7  |       | 5.5   |      | 7.7  | ns    |

| t <sub>ENZL</sub> | Enable Pad Z to LOW                             |      | 4.1  |      | 4.6  |      | 5.2  |       | 6.1   |      | 8.5  | ns    |

| t <sub>ENHZ</sub> | Enable Pad HIGH to Z                            |      | 7.4  |      | 8.2  |      | 9.3  |       | 10.9  |      | 15.3 | ns    |

| t <sub>ENLZ</sub> | Enable Pad LOW to Z                             |      | 6.9  |      | 7.6  |      | 8.7  |       | 10.2  |      | 14.3 | ns    |

| t <sub>GLH</sub>  | G-to-Pad HIGH                                   |      | 7.0  |      | 7.8  |      | 8.9  |       | 10.4  |      | 14.6 | ns    |

| t <sub>GHL</sub>  | G-to-Pad LOW                                    |      | 7.0  |      | 7.8  |      | 8.9  |       | 10.4  |      | 14.6 | ns    |

| t <sub>LSU</sub>  | I/O Latch Set-Up                                | 0.7  |      | 0.7  |      | 0.8  |      | 1.0   |       | 1.4  |      | ns    |

| t <sub>LH</sub>   | I/O Latch Hold                                  | 0.0  |      | 0.0  |      | 0.0  |      | 0.0   |       | 0.0  |      | ns    |

| t <sub>LCO</sub>  | I/O Latch Clock-to-Out<br>(Pad-to-Pad) 32 I/O   |      | 7.9  |      | 8.8  |      | 10.0 |       | 11.8  |      | 16.5 | ns    |

# Table 45 • A42MX36 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

1. For dual-module macros, use  $t_{PD1} + t_{RD1} + t_{PDn}$ ,  $t_{CO} + t_{RD1} + t_{PDn}$ , or  $t_{PD1} + t_{RD1} + t_{SUD}$ , whichever is appropriate.

2. Routing delays are for typical designs across worst-case operating conditions. These parameters should be used for estimating device performance. Post-route timing analysis or simulation is required to determine actual performance.

3. Data applies to macros based on the S-module. Timing parameters for sequential macros constructed from C-modules can be obtained from the Timer utility.

4. Set-up and hold timing parameters for the Input Buffer Latch are defined with respect to the PAD and the D input. External setup/hold timing parameters must account for delay from an external PAD signal to the G inputs. Delay from an external PAD signal to the G input subtracts (adds) to the internal setup (hold) time.

5. Delays based on 35 pF loading.

## 3.12 Pin Descriptions

This section lists the pin descriptions for 40MX and 42MX series FPGAs.

### CLK/A/B, I/O Global Clock

Clock inputs for clock distribution networks. CLK is for 40MX while CLKA and CLKB are for 42MX devices. The clock input is buffered prior to clocking the logic modules. This pin can also be used as an I/O.

### DCLK, I/ODiagnostic Clock

Clock input for diagnostic probe and device programming. DCLK is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### **GND**, Ground

Input LOW supply voltage.

### I/O, Input/Output

Input, output, tristate or bidirectional buffer. Input and output levels are compatible with standard TTL and CMOS specifications. Unused I/Os pins are configured by the Designer software as shown in Table 46, page 84.

| Device           | Configuration |

|------------------|---------------|

| A40MX02, A40MX04 | Pulled LOW    |

| A42MX09, A42MX16 | Pulled LOW    |

| A42MX24, A42MX36 | Tristated     |

Table 46 • Configuration of Unused I/Os

In all cases, it is recommended to tie all unused MX I/O pins to LOW on the board. This applies to all dual-purpose pins when configured as I/Os as well.

#### LP, Low Power Mode

Controls the low power mode of all 42MX devices. The device is placed in the low power mode by connecting the LP pin to logic HIGH. In low power mode, all I/Os are tristated, all input buffers are turned OFF, and the core of the device is turned OFF. To exit the low power mode, the LP pin must be set LOW. The device enters the low power mode 800 ns after the LP pin is driven to a logic HIGH. It will resume normal operation in 200 µs after the LP pin is driven to a logic LOW.

#### MODE, Mode

Controls the use of multifunction pins (DCLK, PRA, PRB, SDI, TDO). The MODE pin is held HIGH to provide verification capability. The MODE pin should be terminated to GND through a  $10k\Omega$  resistor so that the MODE pin can be pulled HIGH when required.

#### NC, No Connection

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

### PRA, I/O

### PRB, I/OProbe A/B

The Probe pin is used to output data from any user-defined design node within the device. Each diagnostic pin can be used in conjunction with the other probe pin to allow real-time diagnostic output of any signal path within the device. The Probe pin can be used as a user-defined I/O when verification has been completed. The pin's probe capabilities can be permanently disabled to protect programmed design confidentiality. The Probe pin is accessible when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### QCLKA/B/C/D, I/O Quadrant Clock

Quadrant clock inputs for A42MX36 devices. When not used as a register control signal, these pins can function as user I/Os.

#### SDI, I/OSerial Data Input

Serial data input for diagnostic probe and device programming. SDI is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW.

### SDO, I/OSerial Data Output

Serial data output for diagnostic probe and device programming. SDO is active when the MODE pin is HIGH. This pin functions as an I/O when the MODE pin is LOW. SDO is available for 42MX devices only.

When Silicon Explorer II is being used, SDO will act as an output while the "checksum" command is run. It will return to user I/O when "checksum" is complete.

### TCK, I/O Test Clock

### Table 52 • PQ160

| PQ160      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 21         | CLKA, I/O        | CLKA, I/O        | CLKA, I/O        |

| 22         | I/O              | I/O              | I/O              |

| 23         | PRA, I/O         | PRA, I/O         | PRA, I/O         |

| 24         | NC               | I/O              | WD, I/O          |

| 25         | I/O              | I/O              | WD, I/O          |

| 26         | I/O              | I/O              | I/O              |

| 27         | I/O              | I/O              | I/O              |

| 28         | NC               | I/O              | I/O              |

| 29         | I/O              | I/O              | WD, I/O          |

| 30         | GND              | GND              | GND              |

| 31         | NC               | I/O              | WD, I/O          |

| 32         | I/O              | I/O              | I/O              |

| 33         | I/O              | I/O              | I/O              |

| 34         | I/O              | I/O              | I/O              |

| 35         | NC               | VCCI             | VCCI             |

| 36         | I/O              | I/O              | WD, I/O          |

| 37         | I/O              | I/O              | WD, I/O          |

| 38         | SDI, I/O         | SDI, I/O         | SDI, I/O         |

| 39         | I/O              | I/O              | I/O              |

| 40         | GND              | GND              | GND              |

| 41         | I/O              | I/O              | I/O              |

| 42         | I/O              | I/O              | I/O              |

| 43         | I/O              | I/O              | I/O              |

| 44         | GND              | GND              | GND              |

| 45         | I/O              | I/O              | I/O              |

| 46         | I/O              | I/O              | I/O              |

| 47         | I/O              | I/O              | I/O              |

| 48         | I/O              | I/O              | I/O              |

| 49         | GND              | GND              | GND              |

| 50         | I/O              | I/O              | I/O              |

| 51         | I/O              | I/O              | I/O              |

| 52         | NC               | I/O              | I/O              |

| 53         | I/O              | I/O              | I/O              |

| 54         | NC               | VCCA             | VCCA             |

| 55         | I/O              | I/O              | I/O              |

| 56         | I/O              | I/O              | I/O              |

| 57         | VCCA             | VCCA             | VCCA             |

### Table 53 • PQ208

| PQ208      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX16 Function | A42MX24 Function | A42MX36 Function |

| 21         | I/O              | I/O              | I/O              |

| 22         | GND              | GND              | GND              |

| 23         | I/O              | I/O              | I/O              |

| 24         | I/O              | I/O              | I/O              |

| 25         | I/O              | I/O              | I/O              |

| 26         | I/O              | I/O              | I/O              |

| 27         | GND              | GND              | GND              |

| 28         | VCCI             | VCCI             | VCCI             |

| 29         | VCCA             | VCCA             | VCCA             |

| 30         | I/O              | I/O              | I/O              |

| 31         | I/O              | I/O              | I/O              |

| 32         | VCCA             | VCCA             | VCCA             |

| 33         | I/O              | I/O              | I/O              |

| 34         | I/O              | I/O              | I/O              |

| 35         | I/O              | I/O              | I/O              |

| 36         | I/O              | I/O              | I/O              |

| 37         | I/O              | I/O              | I/O              |

| 38         | I/O              | I/O              | I/O              |

| 39         | I/O              | I/O              | I/O              |

| 40         | I/O              | I/O              | I/O              |

| 41         | NC               | I/O              | I/O              |

| 42         | NC               | I/O              | I/O              |

| 43         | NC               | I/O              | I/O              |

| 44         | I/O              | I/O              | I/O              |

| 45         | I/O              | I/O              | I/O              |

| 46         | I/O              | I/O              | I/O              |

| 47         | I/O              | I/O              | I/O              |

| 48         | I/O              | I/O              | I/O              |

| 49         | I/O              | I/O              | I/O              |

| 50         | NC               | I/O              | I/O              |

| 51         | NC               | I/O              | I/O              |

| 52         | GND              | GND              | GND              |

| 53         | GND              | GND              | GND              |

| 54         | I/O              | TMS, I/O         | TMS, I/O         |

| 55         | I/O              | TDI, I/O         | TDI, I/O         |

| 56         | I/O              | I/O              | I/O              |

| 57         | I/O              | WD, I/O          | WD, I/O          |

| Table 60 • BG272 |                    |  |

|------------------|--------------------|--|

| BG272            |                    |  |

| Pin Numbe        | r A42MX36 Function |  |

| D20              | I/O                |  |

| E1               | I/O                |  |

| E2               | I/O                |  |

| E3               | I/O                |  |

| E4               | VCCA               |  |

| E17              | VCCI               |  |

| E18              | I/O                |  |

| E19              | I/O                |  |

| E20              | I/O                |  |

| F1               | I/O                |  |

| F2               | I/O                |  |

| F3               | I/O                |  |

| F4               | VCCI               |  |

| F17              | I/O                |  |

| F18              | I/O                |  |

| F19              | I/O                |  |

| F20              | I/O                |  |

| G1               | I/O                |  |

| G2               | I/O                |  |

| G3               | I/O                |  |

| G4               | VCCI               |  |

| G17              | VCCI               |  |

| G18              | I/O                |  |

| G19              | I/O                |  |

| G20              | I/O                |  |

| H1               | I/O                |  |

| H2               | I/O                |  |

| H3               | I/O                |  |

| H4               | VCCA               |  |

| H17              | I/O                |  |

| H18              | I/O                |  |

| H19              | I/O                |  |

| H20              | I/O                |  |

| J1               | I/O                |  |

| J2               | I/O                |  |

| J3               | I/O                |  |

| J4               | VCCI               |  |

| Table 60 • BG272 |                  |  |

|------------------|------------------|--|

| BG272            |                  |  |

| Pin Number       | A42MX36 Function |  |

| M10              | GND              |  |

| M11              | GND              |  |

| M12              | GND              |  |

| M17              | I/O              |  |

| M18              | I/O              |  |

| M19              | I/O              |  |

| M20              | I/O              |  |

| N1               | I/O              |  |

| N2               | I/O              |  |

| N3               | I/O              |  |

| N4               | VCCI             |  |

| N17              | VCCI             |  |

| N18              | I/O              |  |

| N19              | I/O              |  |

| N20              | I/O              |  |

| P1               | I/O              |  |

| P2               | I/O              |  |

| P3               | I/O              |  |

| P4               | VCCA             |  |

| P17              | I/O              |  |

| P18              | I/O              |  |

| P19              | I/O              |  |

| P20              | I/O              |  |

| R1               | I/O              |  |

| R2               | I/O              |  |

| R3               | I/O              |  |

| R4               | VCCI             |  |

| R17              | VCCI             |  |

| R18              | I/O              |  |

| R19              | I/O              |  |

| R20              | I/O              |  |

| T1               | I/O              |  |

| T2               | I/O              |  |

| Т3               | I/O              |  |

| T4               | I/O              |  |

| T17              | VCCA             |  |

| T18              | I/O              |  |

| 138 | I/O   |

|-----|-------|

| 139 | I/O   |

| 140 | I/O   |

| 141 | GND   |

| 142 | I/O   |

| 143 | I/O   |

| 144 | I/O   |

| 145 | I/O   |

| 146 | I/O   |

| 147 | I/O   |

| 148 | PROBA |

| 149 | I/O   |

| 150 | CLKA  |

| 151 | VCC   |

| 152 | GND   |

| 153 | I/O   |

| 154 | CLKB  |

| 155 | I/O   |

| 156 | PROBB |

| 157 | I/O   |

| 158 | I/O   |

| 159 | I/O   |

| 160 | I/O   |

| 161 | GND   |

| 162 | I/O   |

| 163 | I/O   |

| 164 | I/O   |

| 165 | I/O   |

| 166 | VCCI  |

| 167 | I/O   |

| 168 | I/O   |

| 169 | I/O   |

|     | 1/2   |

| 170 | I/O   |