Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                          |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6390-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

| Pin Name                                                     | Pin Number       |                   | Buffer             | Description                                                                                                                              |  |  |  |  |

|--------------------------------------------------------------|------------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| T III Naille                                                 | TQFP             | Туре              | Туре               | Description                                                                                                                              |  |  |  |  |

|                                                              |                  |                   |                    | PORTC is a bidirectional I/O port.                                                                                                       |  |  |  |  |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI                   | 30               | I/O<br>O<br>I     | ST<br>—<br>ST      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                         |  |  |  |  |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(1)</sup>        | 29               | I/O<br>I<br>I/O   | ST<br>CMOS<br>ST   | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.                                                |  |  |  |  |

| RC2/CCP1/SEG13<br>RC2<br>CCP1<br>SEG13                       | 33               | I/O<br>I/O<br>O   | ST<br>ST<br>Analog | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>SEG13 output for LCD.                                                   |  |  |  |  |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                             | 34               | I/O<br>I/O<br>I/O | ST<br>ST<br>ST     | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |  |  |  |  |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                             | 35               | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |  |  |  |  |

| RC5/SDO/SEG12<br>RC5<br>SDO<br>SEG12                         | 36               | I/O<br>O<br>O     | ST<br>—<br>Analog  | Digital I/O.<br>SPI data out.<br>SEG12 output for LCD.                                                                                   |  |  |  |  |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                             | 31               | I/O<br>O<br>I/O   | ST<br>—<br>ST      | Digital I/O.<br>EUSART1 asynchronous transmit.<br>EUSART1 synchronous clock (see related RX1/DT1).                                       |  |  |  |  |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                             | 32               | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>EUSART1 asynchronous receive.<br>EUSART1 synchronous data (see related TX1/CK1).                                         |  |  |  |  |

| Legend: TTL = TTL co<br>ST = Schmi<br>I = Input<br>P = Power | tt Trigger input | with C            | MOS leve           | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                     |  |  |  |  |

| TABLE 1-2: PIC18F6X90 PINOUT I/O DESCRI | PTIONS (CONTINUED) |

|-----------------------------------------|--------------------|

|-----------------------------------------|--------------------|

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                               | Pin Number       | Pin             | Buffer               | Description                                                                                                   |  |  |  |  |

|----------------------------------------|------------------|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Fill Naille                            | TQFP             | Туре            | Туре                 | Description                                                                                                   |  |  |  |  |

|                                        |                  |                 |                      | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |  |  |  |  |

| RB0/INT0<br>RB0<br>INT0                | 58               | I/O<br>I        | TTL<br>ST            | Digital I/O.<br>External interrupt 0.                                                                         |  |  |  |  |

| RB1/INT1/SEG8<br>RB1<br>INT1<br>SEG8   | 57               | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External interrupt 1.<br>SEG8 output for LCD.                                                 |  |  |  |  |

| RB2/INT2/SEG9<br>RB2<br>INT2<br>SEG9   | 56               | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External interrupt 2.<br>SEG9 output for LCD.                                                 |  |  |  |  |

| RB3/INT3/SEG10<br>RB3<br>INT3<br>SEG10 | 55               | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External interrupt 3.<br>SEG10 output for LCD.                                                |  |  |  |  |

| RB4/KBI0/SEG11<br>RB4<br>KBI0<br>SEG11 | 54               | I/O<br>I<br>O   | TTL<br>TTL<br>Analog | Digital I/O.<br>Interrupt-on-change pin.<br>SEG11 output for LCD.                                             |  |  |  |  |

| RB5/KBI1<br>RB5<br>KBI1                | 53               | I/O<br>I        | TTL<br>TTL           | Digital I/O.<br>Interrupt-on-change pin.                                                                      |  |  |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC     | 52               | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming clock pin.              |  |  |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD     | 47               | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                |  |  |  |  |

| I = Input<br>P = Power                 | tt Trigger input |                 |                      | O = Output<br>OD = Open-Drain (no P diode to VDD)                                                             |  |  |  |  |

| Note 1: Default assignment             | nent for CCP2    | when (          | Configura            | tion bit, CCP2MX, is set.                                                                                     |  |  |  |  |

#### TABLE 1-3: PIC18F8X90 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

NOTES:

| File Name                | Bit 7      | Bit 6          | Bit 5           | Bit 4       | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Details<br>on page: |

|--------------------------|------------|----------------|-----------------|-------------|-------|-------|-------|-------|----------------------|---------------------|

| SPBRGH1                  | EUSART1 Ba | aud Rate Gene  | erator Register | r High Byte |       |       |       |       | 0000 0000            | 62, 201             |

| BAUDCON1                 | ABDOVF     | RCIDL          | _               | SCKP        | BRG16 | _     | WUE   | ABDEN | 01-0 0-00            | 62, 200             |

| LCDDATA23(6)             | S47C3      | S46C3          | S45C3           | S44C3       | S43C3 | S42C3 | S41C3 | S40C3 | XXXX XXXX            | 63, 261             |

| LCDDATA22(6)             | S39C3      | S38C3          | S37C3           | S36C3       | S35C3 | S34C3 | S33C3 | S32C3 | XXXX XXXX            | 63, 261             |

| LCDDATA21                | S31C3      | S30C3          | S29C3           | S28C3       | S27C3 | S26C3 | S25C3 | S24C3 | XXXX XXXX            | 63, 261             |

| LCDDATA20                | S23C3      | S22C3          | S21C3           | S20C3       | S19C3 | S18C3 | S17C3 | S16C3 | XXXX XXXX            | 63, 261             |

| LCDDATA19                | S15C3      | S14C3          | S13C3           | S12C3       | S11C3 | S10C3 | S09C3 | S08C3 | XXXX XXXX            | 63, 261             |

| LCDDATA18                | S07C3      | S06C3          | S05C3           | S04C3       | S03C3 | S02C3 | S01C3 | S00C3 | XXXX XXXX            | 63, 261             |

| LCDDATA17 <sup>(6)</sup> | S47C2      | S46C2          | S45C2           | S44C2       | S43C2 | S42C2 | S41C2 | S40C2 | XXXX XXXX            | 63, 261             |

| LCDDATA16 <sup>(6)</sup> | S39C2      | S38C2          | S37C2           | S36C2       | S35C2 | S34C2 | S33C2 | S32C2 | XXXX XXXX            | 63, 261             |

| LCDDATA15                | S31C2      | S30C2          | S29C2           | S28C2       | S27C2 | S26C2 | S25C2 | S24C2 | XXXX XXXX            | 63, 261             |

| LCDDATA14                | S23C2      | S22C2          | S21C2           | S20C2       | S19C2 | S18C2 | S17C2 | S16C2 | XXXX XXXX            | 63, 261             |

| LCDDATA13                | S15C2      | S14C2          | S13C2           | S12C2       | S11C2 | S10C2 | S09C2 | S08C2 | XXXX XXXX            | 63, 261             |

| LCDDATA12                | S07C2      | S06C2          | S05C2           | S04C2       | S03C2 | S02C2 | S01C2 | S00C2 | XXXX XXXX            | 63, 261             |

| LCDDATA11 <sup>(6)</sup> | S47C1      | S46C1          | S45C1           | S44C1       | S43C1 | S42C1 | S41C1 | S40C1 | XXXX XXXX            | 63, 261             |

| SPBRG2                   | AUSART2 Ba | aud Rate Gene  | erator Register | r           |       |       |       |       | 0000 0000            | 63, 220             |

| RCREG2                   | AUSART2 Re | eceive Registe | er -            |             |       |       |       |       | 0000 0000            | 63, 224             |

| TXREG2                   | AUSART2 Tr | ansmit Registe | er              |             |       |       |       |       | 0000 0000            | 63, 222             |

| TXSTA2                   | CSRC       | TX9            | TXEN            | SYNC        |       | BRGH  | TRMT  | TX9D  | 0000 -010            | 63, 218             |

| RCSTA2                   | SPEN       | RX9            | SREN            | CREN        | ADDEN | FERR  | OERR  | RX9D  | 0000 000x            | 63, 219             |

| LCDDATA10 <sup>(6)</sup> | S39C1      | S38C1          | S37C1           | S36C1       | S35C1 | S34C1 | S33C1 | S32C1 | XXXX XXXX            | 63, 261             |

| LCDDATA9                 | S31C1      | S30C1          | S29C1           | S28C1       | S27C1 | S26C1 | S25C1 | S24C1 | XXXX XXXX            | 63, 261             |

| LCDDATA8                 | S23C1      | S22C1          | S21C1           | S20C1       | S19C1 | S18C1 | S17C1 | S16C1 | XXXX XXXX            | 63, 261             |

| LCDDATA7                 | S15C1      | S14C1          | S13C1           | S12C1       | S11C1 | S10C1 | S09C1 | S08C1 | XXXX XXXX            | 63, 261             |

| LCDDATA6                 | S07C1      | S06C1          | S05C1           | S04C1       | S03C1 | S02C1 | S01C1 | S00C1 | XXXX XXXX            | 63, 261             |

| LCDDATA5 <sup>(6)</sup>  | S47C0      | S46C0          | S45C0           | S44C0       | S43C0 | S42C0 | S41C0 | S40C0 | XXXX XXXX            | 63, 261             |

| LCDDATA4 <sup>(6)</sup>  | S39C0      | S38C0          | S37C0           | S36C0       | S35C0 | S34C0 | S33C0 | S32C0 | XXXX XXXX            | 63, 261             |

| LCDDATA3                 | S31C0      | S30C0          | S29C0           | S28C0       | S27C0 | S26C0 | S25C0 | S24C0 | XXXX XXXX            | 63, 261             |

| LCDDATA2                 | S23C0      | S22C0          | S21C0           | S20C0       | S19C0 | S18C0 | S17C0 | S16C0 | XXXX XXXX            | 63, 261             |

| LCDDATA1                 | S15C0      | S14C0          | S13C0           | S12C0       | S11C0 | S10C0 | S09C0 | S08C0 | XXXX XXXX            | 63, 261             |

| LCDDATA0                 | S07C0      | S06C0          | S05C0           | S04C0       | S03C0 | S02C0 | S01C0 | S00C0 | XXXX XXXX            | 63, 261             |

| LCDSE5 <sup>(2)</sup>    | SE47       | SE46           | SE45            | SE44        | SE43  | SE42  | SE41  | SE40  | 0000 0000            | 64, 261             |

| LCDSE4 <sup>(2)</sup>    | SE39       | SE38           | SE37            | SE36        | SE35  | SE34  | SE33  | SE32  | 0000 0000            | 64, 260             |

| LCDSE3                   | SE31       | SE30           | SE29            | SE28        | SE27  | SE26  | SE25  | SE24  | 0000 0000            | 64, 260             |

| LCDSE2                   | SE23       | SE22           | SE21            | SE20        | SE19  | SE18  | SE17  | SE16  | 0000 0000            | 64, 260             |

| LCDSE1                   | SE15       | SE14           | SE13            | SE12        | SE11  | SE10  | SE9   | SE8   | 0000 0000            | 64, 260             |

| LCDSE0                   | SE7        | SE6            | SE5             | SE4         | SE3   | SE2   | SE1   | SE0   | 0000 0000            | 64, 260             |

| LCDCON                   | LCDEN      | SLPEN          | WERR            | _           | CS1   | CS0   | LMUX1 | LMUX0 | 000- 0000            | 64, 258             |

| LCDPS                    | WFT        | BIASMD         | LCDA            | WA          | LP3   | LP2   | LP1   | LP0   | 0000 0000            | 64, 259             |

Note 1: The SBOREN bit is only available when the BOREN1:BOREN0 Configuration bits = 01; otherwise it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

2: These registers and/or bits are not implemented on 64-pin devices; read as '0'.

3: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

4: The RG5 bit is only available when Master Clear is disabled (MCLRE Configuration bit = 0); otherwise, RG5 reads as '0'. This bit is read-only.

5: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

6: These registers are implemented but unused in 64-pin devices and may be used as general-purpose data RAM if required.

| R/W-1      | R/W-1                                                            | R/W-1                             | R/W-1             | R/W-1             | R/W-1            | R/W-1           | R/W-1 |

|------------|------------------------------------------------------------------|-----------------------------------|-------------------|-------------------|------------------|-----------------|-------|

| RBPU       | INTEDG0                                                          | INTEDG1                           | INTEDG2           | INTEDG3           | TMR0IP           | INT3IP          | RBIP  |

| bit 7      |                                                                  |                                   |                   |                   |                  |                 | bit C |

| Legend:    |                                                                  |                                   |                   |                   |                  |                 |       |

| R = Read   | able bit                                                         | W = Writable                      | bit               | U = Unimpler      | nented bit, read | d as '0'        |       |

| -n = Value | e at POR                                                         | '1' = Bit is set                  |                   | '0' = Bit is clea |                  | x = Bit is unkn | own   |

| bit 7      | <b>RBPU</b> : PORT                                               | B Pull-up Enat                    | ole bit           |                   |                  |                 |       |

|            |                                                                  | B pull-ups are bull-ups are       |                   | dual port latch v | alues            |                 |       |

| bit 6      | INTEDG0: Ex                                                      | ternal Interrupt                  | 0 Edge Selec      | t bit             |                  |                 |       |

|            |                                                                  | on rising edge<br>on falling edge |                   |                   |                  |                 |       |

| bit 5      |                                                                  | tternal Interrupt                 |                   | t hit             |                  |                 |       |

|            |                                                                  | on rising edge                    |                   |                   |                  |                 |       |

|            |                                                                  | on falling edge                   |                   |                   |                  |                 |       |

| bit 4      |                                                                  | ternal Interrupt                  | 2 Edge Selec      | t bit             |                  |                 |       |

|            |                                                                  | on rising edge<br>on falling edge |                   |                   |                  |                 |       |

| bit 3      | •                                                                | ternal Interrupt                  |                   | t bit             |                  |                 |       |

|            |                                                                  | on rising edge                    | ·                 |                   |                  |                 |       |

|            | •                                                                | on falling edge                   |                   |                   |                  |                 |       |

| bit 2      | 1 = High prio                                                    | R0 Overflow Int                   | errupt Priority   | bit               |                  |                 |       |

|            | 0 = Low prior                                                    | •                                 |                   |                   |                  |                 |       |

| bit 1      | INT3IP: INT3                                                     | External Interr                   | upt Priority bit  |                   |                  |                 |       |

|            | 1 = High prio                                                    |                                   |                   |                   |                  |                 |       |

| 1.11.0     | 0 = Low prior                                                    | •                                 |                   |                   |                  |                 |       |

| bit 0      | 1 = High prio                                                    | rt Change Inter                   | rupt Priority bit |                   |                  |                 |       |

|            | 0 = Low prior                                                    | •                                 |                   |                   |                  |                 |       |

| Note:      | Interrupt flag bits<br>enable bit or the g<br>are clear prior to | global interrupt                  | enable bit. Use   | er software sho   | uld ensure the   | appropriate int |       |

#### REGISTER 8-2: INTCON2: INTERRUPT CONTROL REGISTER 2

#### REGISTER 8-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0                               | R/W-0                                      | R-0              | R-0             | U-0               | U-0             | U-0              | U-0     |

|-----------------------------------|--------------------------------------------|------------------|-----------------|-------------------|-----------------|------------------|---------|

|                                   | LCDIE                                      | RC2IE            | TX2IE           | _                 |                 |                  | _       |

| bit 7                             |                                            |                  |                 |                   |                 |                  | bit 0   |

|                                   |                                            |                  |                 |                   |                 |                  |         |

| Legend:                           |                                            |                  |                 |                   |                 |                  |         |

| R = Readable bit W = Writable bit |                                            |                  |                 | U = Unimplem      | ented bit, reac | l as '0'         |         |

| -n = Value at I                   | POR                                        | '1' = Bit is set |                 | '0' = Bit is clea | red             | x = Bit is unkn  | own     |

| bit 6                             | 1 = Enabled                                | ·                | bit (valid wher | n Type-B wavefo   | orm with Non-S  | tatic mode is se | lected) |

|                                   | 0 = Disabled                               |                  |                 |                   |                 |                  |         |

| bit 5                             |                                            | ART Receive Int  | errupt Enable   | bit               |                 |                  |         |

| bit 5<br>bit 4                    | RC2IE: AUSA<br>1 = Enabled<br>0 = Disabled | ART Receive Int  | ·               |                   |                 |                  |         |

© 2007 Microchip Technology Inc.

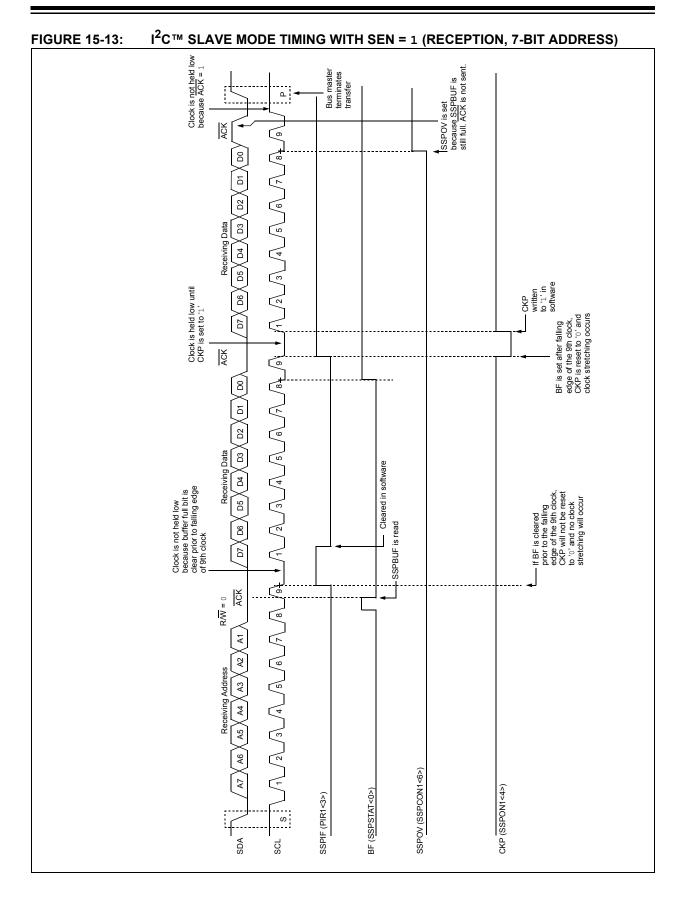

#### 15.4.4 CLOCK STRETCHING

Both 7 and 10-Bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 15.4.4.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, on the falling edge of the ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to '0' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 15-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 15.4.4.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 15.4.4.3 Clock Stretching for 7-Bit Slave Transmit Mode

7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 15-9).

| Note 1: | If the user loads the contents of SSPBUF,     |  |  |  |  |  |  |  |

|---------|-----------------------------------------------|--|--|--|--|--|--|--|

|         | setting the BF bit before the falling edge of |  |  |  |  |  |  |  |

|         | the ninth clock, the CKP bit will not be      |  |  |  |  |  |  |  |

|         | cleared and clock stretching will not occur.  |  |  |  |  |  |  |  |

| 2:      | The CKP bit can be set in software            |  |  |  |  |  |  |  |

|         |                                               |  |  |  |  |  |  |  |

|         | regardless of the state of the BF bit.        |  |  |  |  |  |  |  |

|         |                                               |  |  |  |  |  |  |  |

#### 15.4.4.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence which contains the highorder bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 15-11).

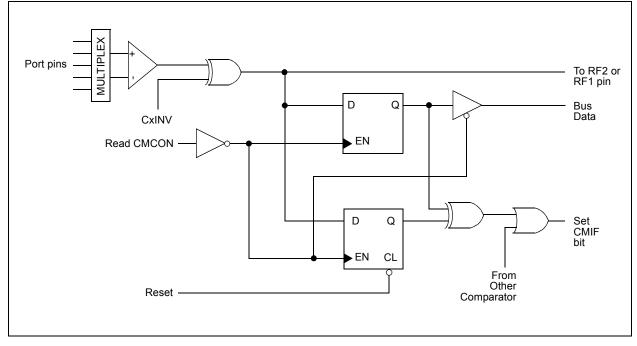

## **19.0 COMPARATOR MODULE**

The analog comparator module contains two comparators that can be configured in a variety of ways. The inputs can be selected from the analog inputs multiplexed with pins RF3 through RF6, as well as the on-chip voltage reference (see Section 20.0 "Comparator Voltage Reference Module"). The digital outputs (normal or inverted) are available at the pin level and can also be read through the control register.

The CMCON register (Register 19-1) selects the comparator input and output configuration. Block diagrams of the various comparator configurations are shown in Figure 19-1.

#### REGISTER 19-1: CMCON: COMPARATOR CONTROL REGISTER

| R-0           | R-0                                               | R/W-0            | R/W-0            | R/W-0             | R/W-1           | R/W-1           | R/W-1 |

|---------------|---------------------------------------------------|------------------|------------------|-------------------|-----------------|-----------------|-------|

| C2OUT         | C1OUT                                             | C2INV            | C1INV            | CIS               | CM2             | CM1             | CM0   |

| bit 7         |                                                   |                  |                  |                   |                 |                 | bit 0 |

| Legend:       |                                                   |                  |                  |                   |                 |                 |       |

| R = Readable  | e bit                                             | W = Writable     | bit              | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value at | POR                                               | '1' = Bit is set |                  | '0' = Bit is clea |                 | x = Bit is unkr | nown  |

| bit 7         | C2OUT: Corr                                       | parator 2 Outp   | ut bit           |                   |                 |                 |       |

|               | When C2INV                                        | • •              |                  |                   |                 |                 |       |

|               | 1 = C2 VIN+ 2                                     |                  |                  |                   |                 |                 |       |

|               | 0 = C2 VIN+ ·                                     | < C2 VIN-        |                  |                   |                 |                 |       |

|               | When C2INV                                        |                  |                  |                   |                 |                 |       |

|               | 1 = C2 VIN+ ·                                     |                  |                  |                   |                 |                 |       |

|               | 0 = C2 VIN+ :                                     |                  |                  |                   |                 |                 |       |

| bit 6         |                                                   | parator 1 Outp   | ut bit           |                   |                 |                 |       |

|               | $\frac{\text{When C1INV}}{1 = C1 \text{VIN} + 3}$ |                  |                  |                   |                 |                 |       |

|               | 1 = C1 VIN+2<br>0 = C1 VIN+2                      | • • • • • •      |                  |                   |                 |                 |       |

|               | When C1INV                                        |                  |                  |                   |                 |                 |       |

|               | 1 = C1 VIN+                                       |                  |                  |                   |                 |                 |       |

|               | 0 = C1 VIN+ 3                                     | > C1 VIN-        |                  |                   |                 |                 |       |

| bit 5         | C2INV: Com                                        | parator 2 Outpu  | It Inversion bit |                   |                 |                 |       |

|               | 1 = C2 outpu                                      |                  |                  |                   |                 |                 |       |

|               | 0 = C2 outpu                                      | t not inverted   |                  |                   |                 |                 |       |

| bit 4         | C1INV: Com                                        | parator 1 Outpu  | It Inversion bit |                   |                 |                 |       |

|               | 1 = C1 Outpu                                      |                  |                  |                   |                 |                 |       |

|               |                                                   | ut not inverted  |                  |                   |                 |                 |       |

| bit 3         | CIS: Compar                                       | ator Input Swite | ch bit           |                   |                 |                 |       |

|               | When CM2:C                                        |                  |                  |                   |                 |                 |       |

|               |                                                   | connects to RF   |                  |                   |                 |                 |       |

|               |                                                   | connects to RF3  |                  |                   |                 |                 |       |

|               |                                                   | connects to RF   |                  |                   |                 |                 |       |

| bit 2-0       |                                                   | comparator Mod   |                  |                   |                 |                 |       |

|               |                                                   | •                | parator modes    |                   |                 |                 |       |

### FIGURE 19-3: COMPARATOR OUTPUT BLOCK DIAGRAM

### 19.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that occurred. The CMIF bit (PIR2<6>) is the Comparator Interrupt Flag. The CMIF bit must be reset by clearing it. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

Both the CMIE bit (PIE2<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit (INTCON<7>) must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

| Note: | lf a                                       | change     | in | the | CMCON | register |  |  |  |  |

|-------|--------------------------------------------|------------|----|-----|-------|----------|--|--|--|--|

|       | (C1OUT or C2OUT) should occur when a       |            |    |     |       |          |  |  |  |  |

|       | read operation is being executed (start of |            |    |     |       |          |  |  |  |  |

|       | the Q2 cycle), then the CMIF (PIR2<6>)     |            |    |     |       |          |  |  |  |  |

|       |                                            | upt flag m |    |     |       |          |  |  |  |  |

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON will end the mismatch condition.

- b) Clear flag bit, CMIF.

A mismatch condition will continue to set flag bit, CMIF. Reading CMCON will end the mismatch condition and allow flag bit, CMIF, to be cleared.

### 19.7 Comparator Operation During Sleep

When a comparator is active and the device is placed in Sleep mode, the comparator remains active and the interrupt is functional, if enabled. This interrupt will wake-up the device from Sleep mode, when enabled. While the comparator is powered up, higher Sleep currents than shown in the power-down current specification will occur. Each operational comparator will consume additional current, as shown in the comparator specifications. To minimize power consumption while in Sleep mode, turn off the comparators (CM2:CM0 = 111) before entering Sleep. If the device wakes up from Sleep, the contents of the CMCON register are not affected.

#### 19.8 Effects of a Reset

A device Reset forces the CMCON register to its Reset state, causing the comparator module to be in the Comparator Reset mode (CM2:CM0 = 000). This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at Reset time. The comparators are powered down during the Reset interval.

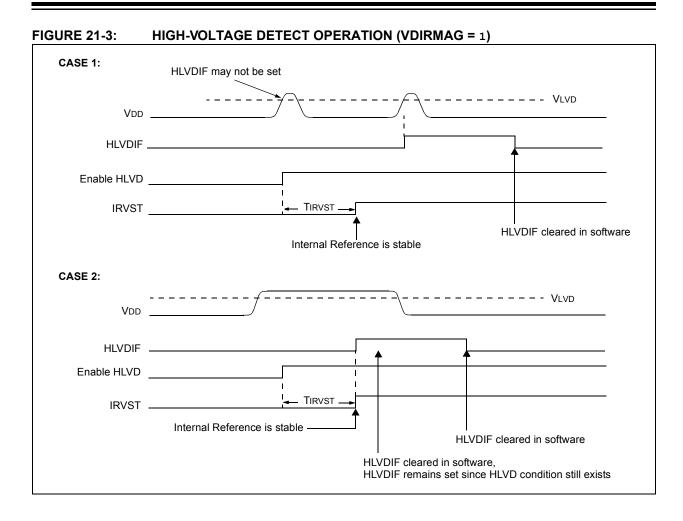

### 21.5 Applications

In many applications, the ability to detect a drop below, or rise above a particular threshold, is desirable. For example, the HLVD module could be periodically enabled to detect USB attach or detach. This assumes the device is powered by a lower voltage source than the Universal Serial Bus when detached. An attach would indicate a high-voltage detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

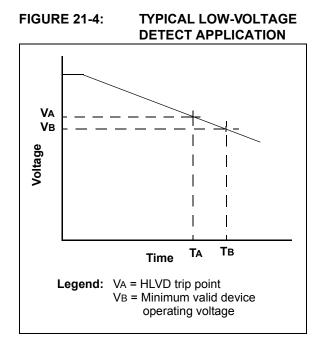

For general battery applications, Figure 21-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "house-keeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB. The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

### 22.1 LCD Registers

The LCD driver module has 32 registers:

- LCD Control Register (LCDCON)

- LCD Phase Register (LCDPS)

- Six LCD Segment Enable Registers (LCDSE5:LCDSE0)

- 24 LCD Data Registers (LCDDATA23:LCDDATA0)

-n = Value at POR

The LCDCON register, shown in Register 22-1, controls the overall operation of the module. Once the module is configured, the LCDEN (LCDCON<7>) bit is

used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN (LCDCON<6>) bit.

The LCDPS register, shown in Register 22-2, configures the LCD clock source prescaler and the type of waveform, Type-A or Type-B. Details on these features are provided in Section 22.2 "LCD Clock Source Selection", Section 22.3 "LCD Bias Types" and Section 22.8 "LCD Waveform Generation".

x = Bit is unknown

#### REGISTER 22-1: LCDCON: LCD CONTROL REGISTER

'1' = Bit is set

| R = Readable bit W = Writable bit |                        |       | U = Unimplem |       |       |       |       |

|-----------------------------------|------------------------|-------|--------------|-------|-------|-------|-------|

| Legend:                           | C = Clearable Only bit |       |              |       |       |       |       |

| bit 7                             |                        |       |              |       |       |       | bit 0 |

| LCDEN                             | SLPEN                  | WERR  | —            | CS1   | CS0   | LMUX1 | LMUX0 |

| R/W-0                             | R/W-0                  | R/C-0 | U-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

'0' = Bit is cleared

| bit 7 | I CDEN: I CD Driver Enchle hit |

|-------|--------------------------------|

| Dit 7   | LCDEN: LCD Driver Enable bit                                                          |

|---------|---------------------------------------------------------------------------------------|

|         | 1 = LCD driver module is enabled                                                      |

|         | 0 = LCD driver module is disabled                                                     |

| bit 6   | SLPEN: LCD Driver Enable in Sleep mode bit                                            |

|         | 1 = LCD driver module is disabled in Sleep mode                                       |

|         | 0 = LCD driver module is enabled in Sleep mode                                        |

| bit 5   | WERR: LCD Write Failed Error bit                                                      |

|         | 1 = LCDDATAx register written while LCDPS <wa> = 0 (must be cleared in software)</wa> |

|         | 0 = No LCD write error                                                                |

| bit 4   | Unimplemented: Read as '0'                                                            |

| bit 3-2 | CS1:CS0: Clock Source Select bits                                                     |

|         | 00 = (Fosc/4)/8192                                                                    |

|         | 01 = T13CKI (Timer1)/32                                                               |

|         | 1x = INTRC (31.25 kHz)/32                                                             |

| hit 1 0 | I MUX1: I MUX0: Commons Select hits                                                   |

bit 1-0 LMUX1:LMUX0: Commons Select bits

| LMUX1:LMUX0 | Multiplex       | Maximum<br>Number of<br>Pixels<br>(PIC18F6X90) | Maximum<br>Number of<br>Pixels<br>(PIC18F8X90) | Bias       |

|-------------|-----------------|------------------------------------------------|------------------------------------------------|------------|

| 00          | Static (COM0)   | 32                                             | 48                                             | Static     |

| 01          | 1/2 (COM1:COM0) | 64                                             | 96                                             | 1/2 or 1/3 |

| 10          | 1/3 (COM2:COM0) | 96                                             | 144                                            | 1/2 or 1/3 |

| 11          | 1/4 (COM3:COM0) | 128                                            | 192                                            | 1/3        |

NOTES:

| BNC          | V                                                                                             | Branch if                                                                | Not Overflo                                                                             | w                                                    | BNZ                                                                                         | Br                                                     |

|--------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Synta        | ax:                                                                                           | BNOV n                                                                   |                                                                                         |                                                      | Syntax:                                                                                     | BN                                                     |

| Oper         | ands:                                                                                         | -128 ≤ n ≤ 1                                                             | 127                                                                                     |                                                      | Operands:                                                                                   | -12                                                    |

| Oper         | ation:                                                                                        | if Overflow<br>(PC) + 2 + 2                                              | ,                                                                                       |                                                      | Operation:                                                                                  | if Z<br>(P0                                            |

| Statu        | s Affected:                                                                                   | None                                                                     |                                                                                         |                                                      | Status Affected:                                                                            | No                                                     |

| Enco         | oding:                                                                                        | 1110                                                                     | 0101 nn:                                                                                | nn nnnn                                              | Encoding:                                                                                   |                                                        |

| Desc         | ription:                                                                                      | program wil<br>The 2's con<br>added to the<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the i<br>the new addre<br>n. This instruct | ber '2n' is<br>e PC will have<br>next<br>ess will be | Description:                                                                                | If th<br>will<br>The<br>add<br>inc<br>ins<br>PC<br>two |

| Word         | ls:                                                                                           | 1                                                                        |                                                                                         |                                                      | Words:                                                                                      | 1                                                      |

| Cycle        | es:                                                                                           | 1(2)                                                                     |                                                                                         |                                                      | Cycles:                                                                                     | 1(2                                                    |

| Q C<br>If Ju | ycle Activity:<br>Imp:                                                                        |                                                                          |                                                                                         |                                                      | Q Cycle Activity:<br>If Jump:                                                               |                                                        |

|              | Q1                                                                                            | Q2                                                                       | Q3                                                                                      | Q4                                                   | Q1                                                                                          |                                                        |

|              | Decode                                                                                        | Read literal<br>'n'                                                      | Process<br>Data                                                                         | Write to PC                                          | Decode                                                                                      | Read                                                   |

|              | No                                                                                            | No                                                                       | No                                                                                      | No                                                   | No                                                                                          |                                                        |

| 16 5 1       | operation                                                                                     | operation                                                                | operation                                                                               | operation                                            | operation                                                                                   | оре                                                    |

| If No        | o Jump:                                                                                       | 02                                                                       | 00                                                                                      | 04                                                   | If No Jump:                                                                                 |                                                        |

|              | Q1<br>Decode                                                                                  | Q2<br>Read literal                                                       | Q3<br>Process                                                                           | Q4<br>No                                             | Q1<br>Decode                                                                                | Read                                                   |

|              | Decode                                                                                        | 'n'                                                                      | Data                                                                                    | operation                                            | Decode                                                                                      | Read                                                   |

|              | nple:<br>Before Instruct<br>PC<br>After Instruction<br>If Overflot<br>PC<br>If Overflot<br>PC | = adv<br>on<br>ow = 0;<br>= adv<br>ow = 1;                               | BNOV Jump<br>dress (HERE<br>dress (Jump<br>dress (HERE                                  | )                                                    | Example:<br>Before Instruc<br>PC<br>After Instructi<br>If Zero<br>PC<br>If Zero<br>PC<br>PC | on                                                     |

| BNZ          | BNZ Branch if Not Zero |                                                                                          |                                                       |                                                  |                        |  |  |

|--------------|------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|------------------------|--|--|

| Synta        | ax:                    | BNZ n                                                                                    |                                                       |                                                  |                        |  |  |

| Oper         | ands:                  | -128 ≤ n ≤ ′                                                                             | 127                                                   |                                                  |                        |  |  |

| Oper         | ation:                 |                                                                                          | if Zero bit is '0',<br>(PC) + 2 + 2n $\rightarrow$ PC |                                                  |                        |  |  |

| Statu        | is Affected:           | None                                                                                     |                                                       |                                                  |                        |  |  |

| Enco         | oding:                 | 1110                                                                                     | 0001                                                  | nnnn                                             | nnnn                   |  |  |

| Desc         | ription:               | If the Zero I will branch.                                                               | bit is '0',                                           | then the p                                       | brogram                |  |  |

|              |                        | The 2's con<br>added to the<br>incremente<br>instruction,<br>PC + 2 + 2r<br>two-cycle ir | e PC. Sir<br>d to fetch<br>the new<br>n. This in      | nce the PO<br>the next<br>address v<br>struction | C will have<br>will be |  |  |

| Word         | ls:                    | 1                                                                                        |                                                       |                                                  |                        |  |  |

| Cycle        | es:                    | 1(2)                                                                                     | 1(2)                                                  |                                                  |                        |  |  |

| Q C<br>If Ju | ycle Activity:         |                                                                                          |                                                       |                                                  |                        |  |  |

|              | Q1                     | Q2                                                                                       | Q3                                                    |                                                  | Q4                     |  |  |

|              | Decode                 | Read literal<br>'n'                                                                      | Proce<br>Data                                         |                                                  | ite to PC              |  |  |

|              | No<br>operation        | No<br>operation                                                                          | No<br>operat                                          | ion o                                            | No<br>peration         |  |  |

| lf No        | o Jump:                |                                                                                          |                                                       |                                                  |                        |  |  |

|              | Q1                     | Q2                                                                                       | Q3                                                    |                                                  | Q4                     |  |  |

|              | Decode                 | Read literal<br>'n'                                                                      | Proce<br>Data                                         |                                                  | No<br>peration         |  |  |

| Exan         | Before Instruc         |                                                                                          |                                                       | Jump                                             |                        |  |  |

|              | PC<br>After Instructio |                                                                                          | dress (H                                              | ERE)                                             |                        |  |  |

0; address (Jump)

1; address (HERE + 2)

= = =

After Instruction W =

| тоти                                             | FSZ                                      | Test f, Ski                                                                                                                                                          | ip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |  |  |

|--------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| Synta                                            | IX:                                      | TSTFSZ f {,                                                                                                                                                          | .a}                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |

| Operands:                                        |                                          | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |

| Opera                                            | ation:                                   | skip if f = 0                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |

| Statu                                            | s Affected:                              | None                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |

| Enco                                             | ding:                                    | 0110                                                                                                                                                                 | 011a fff                                                                                                                                                                                                                                                                                                                                                                                                                                                  | f ffff          |  |  |

| Encoding:<br>Description:                        |                                          | during the c<br>is discarded<br>making this<br>If 'a' is '0', th<br>If 'a' is '1', th<br>GPR bank.<br>If 'a' is '0' an<br>set is enable<br>in Indexed I<br>mode when | If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a two-cycle instruction.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See |                 |  |  |

|                                                  |                                          | Bit-Oriente                                                                                                                                                          | 2.3 "Byte-Ori<br>d Instruction<br>et Mode" for                                                                                                                                                                                                                                                                                                                                                                                                            | s in Indexed    |  |  |

| Word                                             | s:                                       | 1                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |

| Cycle                                            | es:                                      | •                                                                                                                                                                    | rcles if skip and<br>a 2-word instru                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |  |  |

| Q C                                              | cle Activity:                            |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |

| ,                                                | Q1                                       | Q2                                                                                                                                                                   | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q4              |  |  |

| [                                                | Decode                                   | Read                                                                                                                                                                 | Process                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No              |  |  |

|                                                  |                                          | register 'f'                                                                                                                                                         | Data                                                                                                                                                                                                                                                                                                                                                                                                                                                      | operation       |  |  |

| lf ski                                           | p:                                       |                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |

| Г                                                | Q1                                       | Q2                                                                                                                                                                   | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q4              |  |  |

|                                                  | No<br>operation                          | No<br>operation                                                                                                                                                      | No<br>operation                                                                                                                                                                                                                                                                                                                                                                                                                                           | No<br>operation |  |  |

| lf ski                                           |                                          | d by 2-word ins                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oporation       |  |  |