Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                          |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6390-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 64/80-Pin Flash Microcontrollers with LCD Driver and nanoWatt Technology

#### **LCD Driver Module Features:**

- · Direct Driving of LCD Panel

- · Up to 48 Segments: Software Selectable

- · Programmable LCD Timing module:

- Multiple LCD timing sources available

- Up to 4 commons: Static, 1/2, 1/3 or 1/4 multiplex

- Static, 1/2 or 1/3 bias configuration

- Can drive LCD Panel while in Sleep mode

#### **Power-Managed Modes:**

- Run: CPU On, Peripherals On

- Idle: CPU Off, Peripherals On

- · Sleep: CPU Off, Peripherals Off

- Run mode Currents Down to 14.0 μA Typical

- Idle mode Currents Down to 5.8 μA Typical

- Sleep Current Down to 0.1 μA Typical

- Timer1 Oscillator: 1.8 μA, 32 kHz, 2V

- Watchdog Timer: 2.1 μA

- Two-Speed Oscillator Start-up

#### **Flexible Oscillator Structure:**

- Four Crystal modes:

- LP: up to 200 kHz

- XT: up to 4 MHz

- HS: up to 40 MHz

- HSPLL: 4-10 MHz (16-40 MHz internal)

- 4x Phase Lock Loop (available for crystal and internal oscillators)

- Two External RC modes, up to 4 MHz

- Two External Clock modes, up to 40 MHz

- Internal Oscillator Block:

- 8 user-selectable frequencies, from 31 kHz to 8 MHz

- Provides a complete range of clock speeds from 31 kHz to 32 MHz when used with PLL

User-tunable to compensate for frequency drift

- Secondary Oscillator using Timer1 @ 32 kHz

- Fail-Safe Clock Monitor:

- Allows for safe shut down of device if primary or secondary clock fails

#### **Peripheral Highlights:**

- High-Current Sink/Source 25 mA/25 mA

- Four External Interrupts

- Four Input Change Interrupts

- Four 8-Bit/16-Bit Timer/Counter modules

- · Real-Time Clock (RTC) Software module:

- Configurable 24-hour clock, calendar, automatic 100-year or 12800-year, day-of-week calculator

Uses Timer1

- Up to 2 Capture/Compare/PWM (CCP) modules

- Master Synchronous Serial Port (MSSP) module supporting 3-Wire SPI (all 4 modes) and I<sup>2</sup>C<sup>™</sup> Master and Slave modes

- Addressable USART module:

- Supports RS-485 and RS-232

- Enhanced Addressable USART module: - Supports RS-485, RS-232 and LIN 1.2

- Auto-wake-up on Start bit

- Auto-Baud Detect

- 10-Bit, up to 12-Channel Analog-to-Digital (A/D) Converter module:

- Auto-acquisition capability

- Conversion available during Sleep

- Dual Analog Comparators with Input Multiplexing

#### **Special Microcontroller Features:**

- C Compiler Optimized Architecture:

- Optional extended instruction set designed to optimize re-entrant code

- 1000 Erase/Write Cycle Flash Program Memory Typical

- Flash Retention: 100 Years Typical

- Priority Levels for Interrupts

- 8 x 8 Single-Cycle Hardware Multiplier

- Extended Watchdog Timer (WDT):

- Programmable period from 4 ms to 132s

2% stability over VDD and temperature

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- In-Circuit Debug (ICD) via Two Pins

- Wide Operating Voltage Range: 2.0V to 5.5V

| Device     | Program Memory   |                               | Data<br>Memory  | I/O | LCD     | 10-Bit   | ССР   | MSSP |                             | ART/<br>ART | Compositors | Timers   |

|------------|------------------|-------------------------------|-----------------|-----|---------|----------|-------|------|-----------------------------|-------------|-------------|----------|

| Device     | Flash<br>(bytes) | # Single-Word<br>Instructions | SRAM<br>(bytes) | 1/0 | (pixel) | A/D (ch) | (PWM) | SPI  | Master<br>I <sup>2</sup> C™ | EUS/<br>AUS | Comparators | 8/16-Bit |

| PIC18F6390 | 8K               | 4096                          | 768             | 50  | 128     | 12       | 2     | Y    | Y                           | 1/1         | 2           | 1/3      |

| PIC18F6490 | 16K              | 8192                          | 768             | 50  | 128     | 12       | 2     | Y    | Y                           | 1/1         | 2           | 1/3      |

| PIC18F8390 | 8K               | 4096                          | 768             | 66  | 192     | 12       | 2     | Y    | Y                           | 1/1         | 2           | 1/3      |

| PIC18F8490 | 16K              | 8192                          | 768             | 66  | 192     | 12       | 2     | Y    | Y                           | 1/1         | 2           | 1/3      |

#### **Table of Contents**

| 1.0   | Device Overview                                                              | 7 |

|-------|------------------------------------------------------------------------------|---|

| 2.0   | Oscillator Configurations                                                    |   |

| 3.0   | Power-Managed Modes                                                          |   |

| 4.0   | Reset                                                                        |   |

| 5.0   | Memory Organization                                                          |   |

| 6.0   | Flash Program Memory                                                         |   |

| 7.0   | 8 x 8 Hardware Multiplier                                                    |   |

| 8.0   | Interrupts                                                                   |   |

| 9.0   | I/O Ports                                                                    |   |

| 10.0  | Timer0 Module                                                                |   |

| 11.0  | Timer1 Module                                                                |   |

| 12.0  | Timer2 Module                                                                |   |

| 13.0  | Timer3 Module                                                                |   |

| 14.0  | Capture/Compare/PWM (CCP) Modules                                            |   |

|       | Master Synchronous Serial Port (MSSP) Module                                 |   |

| 16.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)    |   |

| 17.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |   |

| 18.0  | 10-Bit Analog-to-Digital Converter (A/D) Module                              |   |

| 19.0  | Comparator Module                                                            |   |

| 20.0  | Comparator Voltage Reference Module                                          |   |

| 21.0  | High/Low-Voltage Detect (HLVD)                                               |   |

| 22.0  | Liquid Crystal Display (LCD) Driver Module                                   |   |

| 23.0  | Special Features of the CPU                                                  |   |

| 24.0  | Instruction Set Summary                                                      |   |

| 25.0  | Development Support                                                          |   |

|       | Electrical Characteristics                                                   |   |

|       | DC and AC Characteristics Graphs and Tables                                  |   |

| 28.0  | Packaging Information                                                        |   |

| Appe  | endix A: Revision History                                                    |   |

| Appe  | endix B: Device Differences                                                  |   |

| Appe  | endix C: Conversion Considerations                                           |   |

| Appe  | endix D: Migration from Baseline to Enhanced Devices                         |   |

| Appe  | endix E: migration from Mid-Range to Enhanced Devices                        |   |

|       | endix F: Migration from High-End to Enhanced Devices                         |   |

| Index | <                                                                            |   |

| The I | Microchip Web Site                                                           |   |

|       | omer Change Notification Service                                             |   |

| Cust  | omer Support                                                                 |   |

|       | ler Response                                                                 |   |

| PIC1  | 8F6390/6490/8390/8490 Product Identification System                          |   |

| Din Nama                                                                                                          | Pin Number                          | Pin                | Buffer                           | Deceritien                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name                                                                                                          | TQFP                                | Туре               | Туре                             | Description                                                                                                          |

|                                                                                                                   |                                     |                    |                                  | PORTF is a bidirectional I/O port.                                                                                   |

| RF0/AN5/SEG18<br>RF0<br>AN5<br>SEG18                                                                              | 18                                  | I/O<br>I<br>O      | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog input 5.<br>SEG18 output for LCD.                                                             |

| RF1/AN6/C2OUT/SEG19<br>RF1<br>AN6<br>C2OUT<br>SEG19                                                               | 17                                  | I/O<br>I<br>O<br>O | ST<br>Analog<br>—<br>Analog      | Digital I/O.<br>Analog input 6.<br>Comparator 2 output.<br>SEG19 output for LCD.                                     |

| RF2/AN7/C1OUT/SEG20<br>RF2<br>AN7<br>C1OUT<br>SEG20                                                               | 16                                  | I/O<br>I<br>O<br>O | ST<br>Analog<br>—<br>Analog      | Digital I/O.<br>Analog input 7.<br>Comparator 1 output.<br>SEG20 output for LCD.                                     |

| RF3/AN8/SEG21<br>RF3<br>AN8<br>SEG21                                                                              | 15                                  | I/O<br>I<br>O      | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog input 8.<br>SEG21 output for LCD.                                                             |

| RF4/AN9/SEG22<br>RF4<br>AN9<br>SEG22                                                                              | 14                                  | I/O<br>I<br>O      | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog input 9.<br>SEG22 output for LCD.                                                             |

| RF5/AN10/CVREF/SEG23<br>RF5<br>AN10<br>CVREF<br>SEG23                                                             | 13                                  | I/O<br>I<br>O<br>O | ST<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 10.<br>Comparator reference voltage output.<br>SEG23 output for LCD.                    |

| RF6/AN11/SEG2412I/OSTDigital I/O.RF6I/OSTDigital I/O.AN11IAnalogAnalog input 11.SEG24OAnalogSEG24 output for LCD. |                                     | Analog input 11.   |                                  |                                                                                                                      |

| RF7/ <del>SS</del> /SEG25<br>RF7<br>SS<br>SEG25                                                                   | 11                                  | I/O<br>I<br>O      | ST<br>TTL<br>Analog              | Digital I/O.<br>SPI slave select input.<br>SEG25 output for LCD.                                                     |

|                                                                                                                   | mpatible input<br>t Trigger input v | with C             | MOS leve                         | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |

#### TABLE 1-2: PIC18F6X90 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                                              | Pin Number | Pin               |                    | Description                                                                                                                              |

|-------------------------------------------------------|------------|-------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Fin Name                                              | TQFP       | Туре              | Туре               | Description                                                                                                                              |

|                                                       |            |                   |                    | PORTC is a bidirectional I/O port.                                                                                                       |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI            | 36         | I/O<br>O<br>I     | ST<br>—<br>ST      | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                         |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(1)</sup> | 35         | I/O<br>I<br>I/O   | ST<br>CMOS<br>ST   | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.                                                |

| RC2/CCP1/SEG13<br>RC2<br>CCP1<br>SEG13                | 43         | I/O<br>I/O<br>O   | ST<br>ST<br>Analog | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.<br>SEG13 output for LCD.                                                   |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                      | 44         | I/O<br>I/O<br>I/O | ST<br>ST<br>ST     | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode. |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                      | 45         | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                               |

| RC5/SDO/SEG12<br>RC5<br>SDO<br>SEG12                  | 46         | I/O<br>O<br>O     | ST<br>—<br>Analog  | Digital I/O.<br>SPI data out.<br>SEG12 output for LCD.                                                                                   |

| RC6/TX1/CK1<br>RC6<br>TX1<br>CK1                      | 37         | I/O<br>O<br>I/O   | ST<br>—<br>ST      | Digital I/O.<br>EUSART1 asynchronous transmit.<br>EUSART1 synchronous clock (see related RX1/DT1).                                       |

| RC7/RX1/DT1<br>RC7<br>RX1<br>DT1                      | 38         | I/O<br>I<br>I/O   | ST<br>ST<br>ST     | Digital I/O.<br>EUSART1 asynchronous receive.<br>EUSART1 synchronous data (see related TX1/CK1).                                         |

|                                                       |            | with C            | MOS leve           | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                     |

#### TABLE 1-3: PIC18F8X90 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

NOTES:

#### 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then set SCS1:SCS0 to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 3-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled, but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

#### 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set after the INTOSC output becomes stable after an interval of TIOBST (parameter 39, Table 26-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled; the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

#### 3.5 Exiting Idle and Sleep Modes

An exit from Sleep mode or any of the Idle modes is triggered by an interrupt, a Reset or a WDT time-out. This section discusses the triggers that cause exits from power-managed modes. The clocking subsystem actions are discussed in each of the power-managed modes (see Section 3.2 "Run Modes" through Section 3.4 "Idle Modes").

#### 3.5.1 EXIT BY INTERRUPT

Any of the available interrupt sources can cause the device to exit from an Idle or Sleep mode to a Run mode. To enable this functionality, an interrupt source must be enabled by setting its enable bit in one of the INTCON or PIE registers. The exit sequence is initiated when the corresponding interrupt flag bit is set.

On all exits from Idle or Sleep modes by interrupt, code execution branches to the interrupt vector if the GIE/GIEH bit (INTCON<7>) is set. Otherwise, code execution continues or resumes without branching (see Section 8.0 "Interrupts").

A fixed delay of interval, TCSD, following the wake event, is required when leaving Sleep and Idle modes. This delay is required for the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### 3.5.2 EXIT BY WDT TIME-OUT

A WDT time-out will cause different actions depending on which power-managed mode the device is in when the time-out occurs.

If the device is not executing code (all Idle modes and Sleep mode), the time-out will result in an exit from the power-managed mode (see Section 3.2 "Run Modes" and Section 3.3 "Sleep Mode"). If the device is executing code (all Run modes), the time-out will result in a WDT Reset (see Section 23.2 "Watchdog Timer (WDT)").

The WDT timer and postscaler are cleared by executing a SLEEP or CLRWDT instruction, losing a currently selected clock source (if the Fail-Safe Clock Monitor is enabled) and modifying the IRCF bits in the OSCCON register if the internal oscillator block is the device clock source.

#### 3.5.3 EXIT BY RESET

Normally, the device is held in Reset by the Oscillator Start-up Timer (OST) until the primary clock becomes ready. At that time, the OSTS bit is set and the device begins executing code. If the internal oscillator block is the new clock source, the IOFS bit is set instead.

The exit delay time from Reset to the start of code execution depends on both the clock sources before and after the wake-up and the type of oscillator if the new clock source is the primary clock. Exit delays are summarized in Table 3-2.

Code execution can begin before the primary clock becomes ready. If either the Two-Speed Start-up (see **Section 23.3 "Two-Speed Start-up"**) or Fail-Safe Clock Monitor (see **Section 23.4 "Fail-Safe Clock Monitor"**) is enabled, the device may begin execution as soon as the Reset source has cleared. Execution is clocked by the INTOSC multiplexer driven by the internal oscillator block. Execution is clocked by the internal oscillator block until either the primary clock becomes ready, or a power-managed mode is entered before the primary clock becomes ready; the primary clock is then shut down.

#### 3.5.4 EXIT WITHOUT AN OSCILLATOR START-UP DELAY

Certain exits from power-managed modes do not invoke the OST at all. There are two cases:

- PRI\_IDLE mode, where the primary clock source is not stopped; and

- the primary clock source is not any of the LP, XT, HS or HSPLL modes.

In these instances, the primary clock source either does not require an oscillator start-up delay since it is already running (PRI\_IDLE), or normally does not require an oscillator start-up delay (RC, EC and INTIO Oscillator modes). However, a fixed delay of interval, TCSD, following the wake event, is still required when leaving Sleep and Idle modes to allow the CPU to prepare for execution. Instruction execution resumes on the first clock cycle following this delay.

#### REGISTER 8-9: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

| U-0                                                                                                                                                                                                    | R/W-0                                      | R-0             | R-0           | U-0          | U-0             | U-0      | U-0   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------|---------------|--------------|-----------------|----------|-------|--|

|                                                                                                                                                                                                        | LCDIE                                      | RC2IE           | TX2IE         | _            |                 |          | _     |  |

| bit 7                                                                                                                                                                                                  |                                            |                 |               |              |                 |          | bit 0 |  |

|                                                                                                                                                                                                        |                                            |                 |               |              |                 |          |       |  |

| Legend:                                                                                                                                                                                                |                                            |                 |               |              |                 |          |       |  |

| R = Readable                                                                                                                                                                                           | e bit                                      | W = Writable b  | bit           | U = Unimplem | ented bit, reac | l as '0' |       |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown                                                                                                                             |                                            |                 |               |              |                 |          | own   |  |

| <ul> <li>Dit 7 Unimplemented: Read as '0'</li> <li>LCDIE: LCD Interrupt Enable bit (valid when Type-B waveform with Non-Static mode is selected)</li> <li>1 = Enabled</li> <li>0 = Disabled</li> </ul> |                                            |                 |               |              |                 |          |       |  |

|                                                                                                                                                                                                        |                                            |                 |               |              |                 |          |       |  |

| bit 5                                                                                                                                                                                                  |                                            | ART Receive Int | errupt Enable | bit          |                 |          |       |  |

| bit 5<br>bit 4                                                                                                                                                                                         | RC2IE: AUSA<br>1 = Enabled<br>0 = Disabled | ART Receive Int | ·             |              |                 |          |       |  |

© 2007 Microchip Technology Inc.

| TADLE 9-1.               | PURIA    | 1               |     | 1      |                                                                                                     |

|--------------------------|----------|-----------------|-----|--------|-----------------------------------------------------------------------------------------------------|

| Pin Name                 | Function | TRIS<br>Setting | I/O | Buffer | Description                                                                                         |

| RA0/AN0                  | RA0      | 0               | 0   | DIG    | LATA<0> data output. Not affected by analog pin setting.                                            |

|                          |          | 1               | Ι   | TTL    | PORTA<0> data input. Reads '0' on POR.                                                              |

|                          | AN0      | 1               | Ι   | ANA    | A/D input channel 0. Default configuration on POR.                                                  |

| RA1/AN1                  | RA1      | 0               | 0   | DIG    | LATA<1> data output. Not affected by analog pin setting.                                            |

|                          |          | 1               | Ι   | TTL    | PORTA<1> data input. Reads '0' on POR.                                                              |

|                          | AN1      | 1               | Ι   | ANA    | A/D input channel 1. Default configuration on POR.                                                  |

| RA2/AN2/VREF-/<br>SEG16  | RA2      | 0               | 0   | DIG    | LATA<2> data output. Not affected by analog pin setting; disabled when LCD segment enabled.         |

|                          |          | 1               | -   | TTL    | PORTA<2> data input. Reads '0' on POR.                                                              |

|                          | AN2      | 1               | -   | ANA    | A/D input channel 2. Default configuration on POR.                                                  |

|                          | VREF-    | 1               | Ι   | ANA    | A/D low reference voltage input.                                                                    |

|                          | SEG16    | х               | 0   | ANA    | Segment 16 analog output for LCD.                                                                   |

| RA3/AN3/VREF+/<br>SEG17  | RA3      | 0               | 0   | DIG    | LATA<3> data output. Output is unaffected by analog pin setting; disabled when LCD segment enabled. |

|                          |          | 1               | Ι   | TTL    | PORTA<3> data input. Reads '0' on POR.                                                              |

|                          | AN3      | 1               | Ι   | ANA    | A/D input channel 3. Default configuration on POR.                                                  |

|                          | VREF+    | 1               | Ι   | ANA    | A/D high reference voltage input.                                                                   |

|                          | SEG17    | х               | 0   | ANA    | Segment 17 analog output for LCD. Disables all other digital outputs.                               |

| RA4/T0CKI/               | RA4      | 0               | 0   | DIG    | LATA<4> data output; disabled when LCD segment enabled.                                             |

| SEG14                    |          | 1               | Ι   | ST     | PORTA<4> data input.                                                                                |

|                          | TOCKI    |                 | -   | ST     | Timer0 clock input.                                                                                 |

|                          | SEG14    | х               | 0   | ANA    | Segment 14 analog output for LCD.                                                                   |

| RA5/AN4/<br>HLVDIN/SEG15 | RA5      | 0               | 0   | DIG    | LATA<5> data output. Not affected by analog pin setting; disabled when LCD segment enabled.         |

|                          |          | 1               | Ι   | TTL    | PORTA<5> data input. Reads '0' on POR.                                                              |

|                          | AN4      | 1               | Ι   | ANA    | A/D input channel 5. Default configuration on POR.                                                  |

|                          | HLVDIN   | 1               | Ι   | ANA    | High/Low-Voltage Detect external trip point input.                                                  |

|                          | SEG15    | х               | 0   | ANA    | Segment 15 analog output for LCD.                                                                   |

| OSC2/CLKO/RA6            | OSC2     | x               | 0   | ANA    | Main oscillator feedback output connection (XT, HS and LP modes).                                   |

|                          | CLKO     | х               | 0   | DIG    | System cycle clock output (Fosc/4) in all oscillator modes except RCIO, INTIO2 and ECIO.            |

|                          | RA6      | 0               | 0   | DIG    | LATA<6> data output. Enabled in RCIO, INTIO2 and ECIO modes only.                                   |

|                          |          | 1               | Ι   | TTL    | PORTA<6> data input. Enabled in RCIO, INTIO2 and ECIO modes only.                                   |

| OSC1/CLKI/RA7            | OSC1     | х               |     | ANA    | Main oscillator input connection, all modes except INTIO.                                           |

|                          | CLKI     | х               | I   | ANA    | Main clock input connection, all modes except INTIO.                                                |

|                          | RA7      | 0               | 0   | DIG    | LATA<7> data output. Available only in INTIO modes; otherwise reads as '0'.                         |

|                          |          | 1               | Ι   | TTL    | PORTA<7> data input. Available only in INTIO modes; otherwise reads as '0'.                         |

#### TABLE 9-1:PORTA FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Buffer Input, TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

#### 13.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 13-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

#### 13.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in **Section 11.0** "Timer1 Module".

#### 13.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

#### 13.5 Resetting Timer3 Using the CCP Special Event Trigger

If either of the CCP modules is configured in Compare mode to generate a Special Event Trigger (CCP1M3:CCP1M0 or CCP2M3:CCP2M0 = 1011), this signal will reset Timer1. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 14.3.4 "Special Event Trigger"** for more information.).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPR2H:CCPR2L register pair effectively becomes a Period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

**Note:** The Special Event Triggers from the CCP2 module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name   | Bit 7      | Bit 6         | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values |

|--------|------------|---------------|---------|---------|---------|--------|--------|--------|-----------------|

|        |            |               |         |         |         |        |        |        | on Page         |

| INTCON | GIE/GIEH   | PEIE/GIEL     | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 59              |

| PIR2   | OSCFIF     | CMIF          | _       | _       | BCLIF   | HLVDIF | TMR3IF | CCP2IF | 61              |

| PIE2   | OSCFIE     | CMIE          | _       | _       | BCLIE   | HLVDIE | TMR3IE | CCP2IE | 61              |

| IPR2   | OSCFIP     | CMIP          | _       | _       | BCLIP   | HLVDIP | TMR3IP | CCP2IP | 61              |

| TMR3L  | Timer3 Reg | gister Low B  | yte     |         |         |        |        |        | 61              |

| TMR3H  | Timer3 Reg | gister High B | yte     |         |         |        |        |        | 61              |

| T1CON  | RD16       | T1RUN         | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N | 60              |

| T3CON  | RD16       | T3CCP2        | T3CKPS1 | T3CKPS0 | T3CCP1  | T3SYNC | TMR3CS | TMR3ON | 61              |

TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

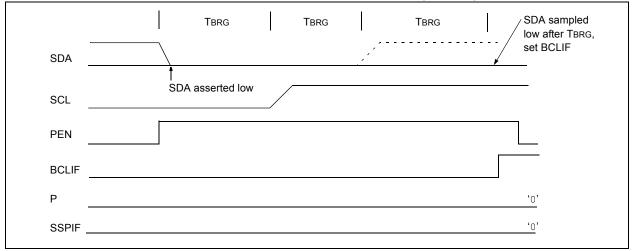

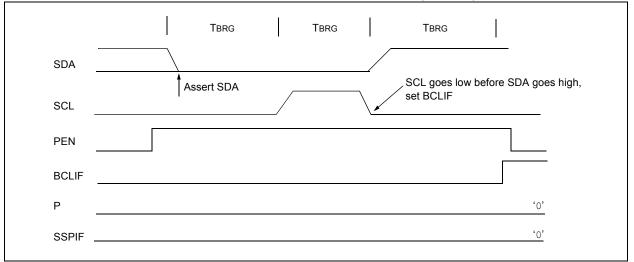

#### 15.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 15-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 15-32).

#### FIGURE 15-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 15-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

#### 18.8 Use of the CCP2 Trigger

An A/D conversion can be started by the "Special Event Trigger" of the CCP2 module. This requires that the CCP2M3:CCP2M0 bits (CCP2CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D acquisition and conversion and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH/ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition period is either timed by the user, or an appropriate TACQ time selected before the "Special Event Trigger" sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the "Special Event Trigger" will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

| Name   | Bit 7                             | Bit 6                                      | Bit 5    | Bit 4          | Bit 3    | Bit 2  | Bit 1   | Bit 0  | Reset<br>Values<br>on Page |  |

|--------|-----------------------------------|--------------------------------------------|----------|----------------|----------|--------|---------|--------|----------------------------|--|

| INTCON | GIE/GIEH                          | PEIE/GIEL                                  | TMR0IE   | INT0IE         | RBIE     | TMR0IF | INT0IF  | RBIF   | 59                         |  |

| PIR1   | _                                 | ADIF                                       | RC1IF    | TX1IF          | SSPIF    | CCP1IF | TMR2IF  | TMR1IF | 61                         |  |

| PIE1   | _                                 | ADIE                                       | RC1IE    | TX1IE          | SSPIE    | CCP1IE | TMR2IE  | TMR1IE | 61                         |  |

| IPR1   |                                   | ADIP                                       | RC1IP    | TX1IP          | SSPIP    | CCP1IP | TMR2IP  | TMR1IP | 61                         |  |

| PIR2   | OSCFIF                            | CMIF                                       |          | _              | BCLIF    | HLVDIF | TMR3IF  | CCP2IF | 61                         |  |

| PIE2   | OSCFIE                            | CMIE                                       |          | _              | BCLIE    | HLVDIE | TMR3IE  | CCP2IE | 61                         |  |

| IPR2   | OSCFIP                            | OSCFIP CMIP — — BCLIP HLVDIP TMR3IP CCP2IP |          |                |          |        |         |        |                            |  |

| ADRESH | A/D Result                        | Register Hig                               | gh Byte  |                |          |        |         |        | 61                         |  |

| ADRESL | A/D Result                        | Register Lov                               | w Byte   |                |          |        |         |        | 61                         |  |

| ADCON0 |                                   | _                                          | CHS3     | CHS2           | CHS1     | CHS0   | GO/DONE | ADON   | 61                         |  |

| ADCON1 |                                   | _                                          | VCFG1    | VCFG0          | PCFG3    | PCFG2  | PCFG1   | PCFG0  | 61                         |  |

| ADCON2 | ADFM                              |                                            | ACQT2    | ACQT1          | ACQT0    | ADCS2  | ADCS1   | ADCS0  | 61                         |  |

| PORTA  | RA7 <sup>(1)</sup>                | RA6 <sup>(1)</sup>                         | RA5      | RA4            | RA3      | RA2    | RA1     | RA0    | 62                         |  |

| TRISA  | TRISA7 <sup>(1)</sup>             | TRISA6 <sup>(1)</sup>                      | PORTA Da | ta Direction I | Register |        |         |        | 62                         |  |

| PORTF  | Read PORTF pins, Write LATF Latch |                                            |          |                |          |        |         |        |                            |  |

| TRISF  | PORTF Dat                         | a Direction F                              | Register |                |          |        |         |        | 62                         |  |

| LATF   | LATF Data                         | Output Regis                               | ster     |                |          |        |         |        | 62                         |  |

TABLE 18-2:

REGISTERS ASSOCIATED WITH A/D OPERATION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

**Note 1:** These pins may be configured as port pins depending on the oscillator mode selected.

NOTES:

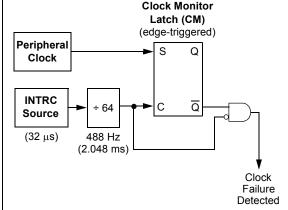

#### 23.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 23-3) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the Clock Monitor latch (CM). The CM is set on the falling edge of the device clock source, but cleared on the rising edge of the sample clock.

Clock failure is tested for on the falling edge of the sample clock. If a sample clock falling edge occurs while CM is still set, a clock failure has been detected (Figure 23-4). This causes the following:

- the FSCM generates an oscillator fail interrupt by setting bit OSCFIF (PIR2<7>);

- the device clock source is switched to the internal oscillator block (OSCCON is not updated to show the current clock source – this is the Fail-Safe condition); and

- · the WDT is reset.

During switchover, the postscaler frequency from the internal oscillator block may not be sufficiently stable for timing sensitive applications. In these cases, it may be desirable to select another clock configuration and enter an alternate power-managed mode. This can be done to attempt a partial recovery or execute a controlled shutdown. See Section 3.1.2 "Entering Power-Managed Modes" and Section 23.3.1 "Special Considerations for Using Two-Speed Start-up" for more details.

To use a higher clock speed on wake-up, the INTOSC or postscaler clock sources can be selected to provide a higher clock speed by setting bits, IRCF2:IRCF0, immediately after Reset. For wake-ups from Sleep, the INTOSC or postscaler clock sources can be selected by setting the IRCF2:IRCF0 bits prior to entering Sleep mode.

The FSCM will detect failures of the primary or secondary clock sources only. If the internal oscillator block fails, no failure would be detected, nor would any action be possible.

#### 23.4.1 FSCM AND THE WATCHDOG TIMER

Both the FSCM and the WDT are clocked by the INTRC oscillator. Since the WDT operates with a separate divider and counter, disabling the WDT has no effect on the operation of the INTRC oscillator when the FSCM is enabled.

As already noted, the clock source is switched to the INTOSC clock when a clock failure is detected. Depending on the frequency selected by the IRCF2:IRCF0 bits, this may mean a substantial change in the speed of code execution. If the WDT is enabled with a small prescale value, a decrease in clock speed allows a WDT time-out to occur and a subsequent device Reset. For this reason, Fail-Safe Clock Monitor events also reset the WDT and postscaler, allowing them to start timing from when execution speed was changed and decreasing the likelihood of an erroneous time-out.

#### 23.4.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 1H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTOSC multiplexer provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The Fail-Safe Clock Monitor then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTOSC multiplexer. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

| ADDWFC                                               | ADD W a                                                             | nd Carry bit                                                                                                                                                                                                                                                                                                                                                                                     | to f                 | AN   | DLW                                                | AND Lite            | ral with W                   |     |           |

|------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------------------------------------|---------------------|------------------------------|-----|-----------|

| Syntax:                                              | ADDWFC                                                              | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                      |                      | Syn  | tax:                                               | ANDLW               | k                            |     |           |

| Operands:                                            | $0 \leq f \leq 255$                                                 |                                                                                                                                                                                                                                                                                                                                                                                                  |                      | Оре  | rands:                                             | $0 \le k \le 255$   |                              |     |           |

|                                                      | d ∈ [0,1]                                                           |                                                                                                                                                                                                                                                                                                                                                                                                  |                      | Ope  | ration:                                            | (W) .AND.           | $k \rightarrow W$            |     |           |

| Operation                                            | a ∈ [0,1]                                                           | (C) deat                                                                                                                                                                                                                                                                                                                                                                                         |                      | Stat | us Affected:                                       | N, Z                |                              |     |           |

| Operation:<br>Status Affected:                       | . , .,                                                              | $(C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                           |                      | Enc  | oding:                                             | 0000                | 1011 k                       | kkk | kkkk      |

| Encoding:                                            |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                  |                      | Des  | cription:                                          |                     | ts of W are<br>'k'. The resu |     |           |

| Description:                                         | ,                                                                   | , 0                                                                                                                                                                                                                                                                                                                                                                                              | I data memory        | Wor  | ds:                                                | 1                   |                              |     |           |

|                                                      |                                                                     | If 'd' is '0', the<br>V. If 'd' is '1', tł                                                                                                                                                                                                                                                                                                                                                       |                      | Сус  | es:                                                | 1                   |                              |     |           |

|                                                      | ,<br>placed in d                                                    | ata memory                                                                                                                                                                                                                                                                                                                                                                                       |                      | Q    | Cycle Activity:                                    |                     |                              |     |           |

|                                                      | location 'f'.                                                       |                                                                                                                                                                                                                                                                                                                                                                                                  | ali in a classia d   |      | Q1                                                 | Q2                  | Q3                           |     | Q4        |

|                                                      | lf 'a' is '1', t                                                    | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                      |      | Decode                                             | Read literal<br>'k' | Process<br>Data              | Wi  | rite to W |

|                                                      | set is enab<br>in Indexed<br>mode when<br>Section 24<br>Bit-Oriente |                                                                                                                                                                                                                                                                                                                                                                                                  |                      |      | mple:<br>Before Instru<br>W<br>After Instruct<br>W | = A3h               |                              |     |           |

| Words:                                               | 1                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                  |                      |      |                                                    |                     |                              |     |           |

| Cycles:                                              | 1                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                  |                      |      |                                                    |                     |                              |     |           |

| Q Cycle Activity                                     | :                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                  |                      |      |                                                    |                     |                              |     |           |

| Q1                                                   | Q2                                                                  | Q3                                                                                                                                                                                                                                                                                                                                                                                               | Q4                   |      |                                                    |                     |                              |     |           |

| Decode                                               | Read<br>register 'f'                                                | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                  | Write to destination |      |                                                    |                     |                              |     |           |

| Example:                                             | ADDWFC                                                              | REG, 0,                                                                                                                                                                                                                                                                                                                                                                                          | 1                    |      |                                                    |                     |                              |     |           |

| Before Instr<br>Carry I<br>REG<br>W<br>After Instruc | bit = 1<br>= 02h<br>= 4Dh                                           |                                                                                                                                                                                                                                                                                                                                                                                                  |                      |      |                                                    |                     |                              |     |           |

| Carry<br>REG<br>W                                    |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                  |                      |      |                                                    |                     |                              |     |           |

### 26.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                               | 40°C to +125°C       |

|--------------------------------------------------------------|----------------------|

| Storage temperature                                          | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                           | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                 | 0V to +13.25V        |

| Total power dissipation (Note 1)                             | 1.0W                 |

| Maximum current out of Vss pin                               | 300 mA               |

| Maximum current into VDD pin                                 | 250 mA               |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                 | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)               | ±20 mA               |

| Maximum output current sunk by any I/O pin                   | 25 mA                |

| Maximum output current sourced by any I/O pin                | 25 mA                |

| Maximum current sunk by all ports                            | 200 mA               |

| Maximum current sourced by all ports                         | 200 mA               |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $- \sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL)

- **2:** Voltage spikes below Vss at the MCLR/VPP/RG5 pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP/ RG5 pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Param<br>No. | Sym             | Characteristic                | Min | Тур† | Max | Units | Conditions   |

|--------------|-----------------|-------------------------------|-----|------|-----|-------|--------------|

| F10          | Fosc            | Oscillator Frequency Range    | 4   | _    | 10  | MHz   | HS mode only |

| F11          | Fsys            | On-Chip VCO System Frequency  | 16  | —    | 40  | MHz   | HS mode only |

| F12          | t <sub>rc</sub> | PLL Start-up Time (Lock Time) | _   | —    | 2   | ms    |              |

| F13          | $\Delta CLK$    | CLKO Stability (Jitter)       | -2  | _    | +2  | %     |              |

#### TABLE 26-7: PLL CLOCK TIMING SPECIFICATIONS (VDD = 4.2V TO 5.5V)

† Data in "Typ" column is at 5V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

# TABLE 26-8:AC CHARACTERISTICS: INTERNAL RC ACCURACYPIC18LF6390/6490/8390/8490 (INDUSTRIAL)PIC18F6390/6490/8390/8490 (INDUSTRIAL)

| PIC18LF6390/6490/8390/8490<br>(Industrial) |                                                                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |        |       |                |                |  |  |

|--------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|--------|-------|----------------|----------------|--|--|

| PIC18F6390/6490/8390/8490<br>(Industrial)  |                                                                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |        |       |                |                |  |  |

| Param<br>No.                               | Device                                                                                        | Min                                                                                                                                | Тур  | Max    | Units | Conditions     |                |  |  |

|                                            | INTOSC Accuracy @ Freq = 8 MHz, 4 MHz, 2 MHz, 1 MHz, 500 kHz, 250 kHz, 125 kHz <sup>(1)</sup> |                                                                                                                                    |      |        |       |                |                |  |  |

|                                            | PIC18LF6390/6490/8390/8490                                                                    | -2                                                                                                                                 | +/-1 | 2      | %     | +25°C          | VDD = 2.7-3.3V |  |  |

|                                            |                                                                                               | -5                                                                                                                                 | —    | 5      | %     | -10°C to +85°C | VDD = 2.7-3.3V |  |  |

|                                            |                                                                                               | -10                                                                                                                                | +/-1 | 10     | %     | -40°C to +85°C | VDD = 2.7-3.3V |  |  |

|                                            | PIC18F6390/6490/8390/8490                                                                     | -2                                                                                                                                 | +/-1 | 2      | %     | +25°C          | VDD = 4.5-5.5V |  |  |

|                                            |                                                                                               | -5                                                                                                                                 | —    | 5      | %     | -10°C to +85°C | VDD = 4.5-5.5V |  |  |

|                                            |                                                                                               | -10                                                                                                                                | +/-1 | 10     | %     | -40°C to +85°C | VDD = 4.5-5.5V |  |  |

|                                            | INTRC Accuracy @ Freq = 31 kHz <sup>(2)</sup>                                                 |                                                                                                                                    |      |        |       |                |                |  |  |

|                                            | PIC18LF6390/6490/8390/8490                                                                    | 26.562                                                                                                                             | _    | 35.938 | kHz   | -40°C to +85°C | VDD = 2.7-3.3V |  |  |

|                                            | PIC18F6390/6490/8390/8490                                                                     | 26.562                                                                                                                             | _    | 35.938 | kHz   | -40°C to +85°C | VDD = 4.5-5.5V |  |  |

Legend: Shading of rows is to assist in readability of the table.

Note 1: Frequency calibrated at 25°C. OSCTUNE register can be used to compensate for temperature drift.

2: INTRC frequency after calibration.

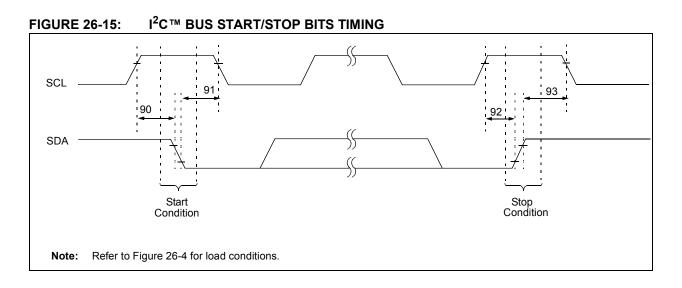

#### TABLE 26-17: I<sup>2</sup>C<sup>™</sup> BUS START/STOP BITS REQUIREMENTS (SLAVE MODE)

| Param.<br>No. | Symbol  | Characte        | Min          | Max  | Units | Conditions |                                                       |

|---------------|---------|-----------------|--------------|------|-------|------------|-------------------------------------------------------|

| 90 Tsu:sta    |         | Start Condition | 100 kHz mode | 4700 | —     | ns         | Only relevant for Repeated                            |

|               |         | Setup Time      | 400 kHz mode | 600  | _     |            | Start condition                                       |

| 91 The        | THD:STA | Start Condition | 100 kHz mode | 4000 | _     | ns         | After this period, the first clock pulse is generated |

|               |         | Hold Time       | 400 kHz mode | 600  | —     |            |                                                       |

| 92            | Tsu:sto | Stop Condition  | 100 kHz mode | 4700 | _     | ns         |                                                       |

|               |         | Setup Time      | 400 kHz mode | 600  | _     |            |                                                       |

| 93            | THD:STO | Stop Condition  | 100 kHz mode | 4000 | —     | ns         |                                                       |

|               |         | Hold Time       | 400 kHz mode | 600  | _     |            |                                                       |

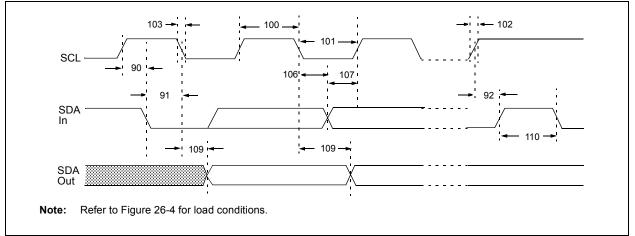

#### FIGURE 26-16: I<sup>2</sup>C<sup>™</sup> BUS DATA TIMING

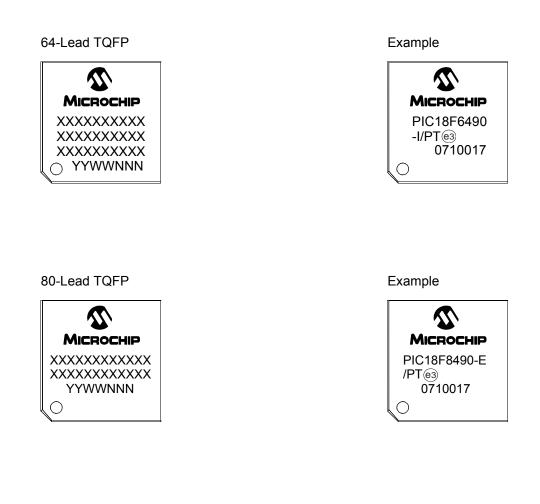

#### 28.0 PACKAGING INFORMATION

#### 28.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>(@3)<br>*                                                                                                                                                                    | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|        | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

#### APPENDIX E: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES