Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                          |

| Number of I/O              | 66                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8490-e-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome                                                                                                                                                                                                                                                                                                                                                                            | Pin Number | Pin                | Buffer                            | Description                                                                                                 |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name                                                                                                                                                                                                                                                                                                                                                                            | TQFP       | Туре Туре          |                                   | Description                                                                                                 |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                     |            |                    |                                   | PORTA is a bidirectional I/O port.                                                                          |  |  |  |  |  |

| RA0/AN0<br>RA0<br>AN0                                                                                                                                                                                                                                                                                                                                                               | 24         | I/O<br>I           | TTL<br>Analog                     | Digital I/O.<br>Analog input 0.                                                                             |  |  |  |  |  |

| RA1/AN1<br>RA1<br>AN1                                                                                                                                                                                                                                                                                                                                                               | 23         | I/O<br>I           | TTL<br>Analog                     | Digital I/O.<br>Analog input 1.                                                                             |  |  |  |  |  |

| RA2/AN2/VREF-/SEG16<br>RA2<br>AN2<br>VREF-<br>SEG16                                                                                                                                                                                                                                                                                                                                 | 22         | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>SEG16 output for LCD.              |  |  |  |  |  |

| RA3/AN3/VREF+/SEG17<br>RA3<br>AN3<br>VREF+<br>SEG17                                                                                                                                                                                                                                                                                                                                 | 21         | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.<br>SEG17 output for LCD.             |  |  |  |  |  |

| RA4/T0CKI/SEG14<br>RA4<br>T0CKI<br>SEG14                                                                                                                                                                                                                                                                                                                                            | 28         | I/O<br>I<br>O      | ST/OD<br>ST<br>Analog             | Digital I/O. Open-drain when configured as output.<br>Timer0 external clock input.<br>SEG14 output for LCD. |  |  |  |  |  |

| RA5/AN4/HLVDIN/SEG15<br>RA5<br>AN4<br>HLVDIN<br>SEG15                                                                                                                                                                                                                                                                                                                               | 27         | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 4.<br>Low-Voltage Detect input.<br>SEG15 output for LCD.                       |  |  |  |  |  |

| RA6                                                                                                                                                                                                                                                                                                                                                                                 |            |                    |                                   | See the OSC2/CLKO/RA6 pin.                                                                                  |  |  |  |  |  |

| RA7                                                                                                                                                                                                                                                                                                                                                                                 |            |                    |                                   | See the OSC1/CLKI/RA7 pin.                                                                                  |  |  |  |  |  |

| RA7       See the OSC1/CLKI/RA7 pin.         Legend:       TTL = TTL compatible input<br>ST = Schmitt Trigger input with CMOS levels<br>I = Input<br>P = Power       CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)         Note 1:       Default assignment for CCP2 when Configuration bit, CCP2MX, is set. |            |                    |                                   |                                                                                                             |  |  |  |  |  |

| TABLE 1-2: | PIC18F6X90 PINOUT I/O DESCRIPTIONS (CONTINUED) |  |

|------------|------------------------------------------------|--|

|            |                                                |  |

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

# 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then set SCS1:SCS0 to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 3-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled, but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

### 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set after the INTOSC output becomes stable after an interval of TIOBST (parameter 39, Table 26-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled; the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

### 4.5 Device Reset Timers

PIC18F6390/6490/8390/8490 devices incorporate three separate on-chip timers that help regulate the Power-on Reset process. Their main function is to ensure that the device clock is stable before code is executed. These timers are:

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- PLL Lock Time-out

#### 4.5.1 POWER-UP TIMER (PWRT)

The Power-up Timer (PWRT) of PIC18F6390/6490/8390/8490 devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 for details.

The PWRT is enabled by clearing the PWRTEN Configuration bit.

#### 4.5.2 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over (parameter 33). This ensures that the crystal oscillator or resonator has started and is stabilized.

The OST time-out is invoked only for XT, LP, HS and HSPLL modes and only on Power-on Reset, or on exit from most power-managed modes.

### 4.5.3 PLL LOCK TIME-OUT

With the PLL enabled in its PLL mode, the time-out sequence following a Power-on Reset is slightly different from other oscillator modes. A separate timer is used to provide a fixed time-out that is sufficient for the PLL to lock to the main oscillator frequency. This PLL lock time-out (TPLL) is typically 2 ms and follows the oscillator start-up time-out.

#### 4.5.4 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows:

- 1. After the POR pulse has cleared, PWRT time-out is invoked (if enabled).

- 2. Then, the OST is activated.

The total time-out will vary based on oscillator configuration and the status of the PWRT. Figure 4-3, Figure 4-4, Figure 4-5, Figure 4-6 and Figure 4-7 all depict time-out sequences on power-up, with the Power-up Timer enabled and the device operating in HS Oscillator mode. Figures 4-3 through 4-6 also apply to devices operating in XT or LP modes. For devices in RC mode and with the PWRT disabled, on the other hand, there will be no time-out at all.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, all time-outs will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (Figure 4-5). This is useful for testing purposes, or to synchronize more than one PIC18FXXXX device operating in parallel.

| Oscillator     | Power-up <sup>(2)</sup> an                             | Exit from                          |                                 |  |

|----------------|--------------------------------------------------------|------------------------------------|---------------------------------|--|

| Configuration  | <b>PWRTEN =</b> 0                                      | PWRTEN = 1         Power-Managed N | Power-Managed Mode              |  |

| HSPLL          | 66 ms <sup>(1)</sup> + 1024 Tosc + 2 ms <sup>(2)</sup> | 1024 Tosc + 2 ms <sup>(2)</sup>    | 1024 Tosc + 2 ms <sup>(2)</sup> |  |

| HS, XT, LP     | 66 ms <sup>(1)</sup> + 1024 Tosc                       | 1024 Tosc                          | 1024 Tosc                       |  |

| EC, ECIO       | 66 ms <sup>(1)</sup>                                   | _                                  | —                               |  |

| RC, RCIO       | 66 ms <sup>(1)</sup>                                   | _                                  | —                               |  |

| INTIO1, INTIO2 | 66 ms <sup>(1)</sup>                                   | _                                  | —                               |  |

| TABLE 4-2: | TIME-OUT IN VARIOUS SITUATIONS |

|------------|--------------------------------|

|            |                                |

**Note 1:** 66 ms (65.5 ms) is the nominal Power-up Timer (PWRT) delay.

2: 2 ms is the nominal time required for the PLL to lock.

# 5.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds five additional two-word commands to the existing PIC18 instruction set: ADDFSR, CALLW, MOVSF, MOVSS and SUBFSR. These instructions are executed as described in Section 5.2.4 "Two-Word Instructions".

# 5.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

#### 5.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode. When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

### 5.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 5-8.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 24.2.1** "Extended Instruction Syntax".

| EXAMPLE   | 6-1: F  | READING A FLASH PI | ROGRAM MEMORY WORD               |

|-----------|---------|--------------------|----------------------------------|

|           | MOVLW   | CODE_ADDR_UPPER    | ; Load TBLPTR with the base      |

|           | MOVWF   | TBLPTRU            | ; address of the word            |

|           | MOVLW   | CODE ADDR HIGH     |                                  |

|           | MOVWF   | TBLPTRH            |                                  |

|           | MOVLW   | CODE ADDR LOW      |                                  |

|           | MOVWF   | TBLPTRL            |                                  |

| READ WORD |         |                    |                                  |

| _         | TBLRD*+ |                    | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W          | ; get data                       |

|           | MOVWF   | WORD EVEN          |                                  |

|           | TBLRD*+ | —                  | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W          | ; get data                       |

|           | MOVWF   | WORD_ODD           |                                  |

|           |         |                    |                                  |

| <b>TABLE 6-2:</b> | REGISTERS ASSOCIATED WITH READING PROGRAM FLASH MEMORY |             |        |       |                                                           |  |  |    |    |  |

|-------------------|--------------------------------------------------------|-------------|--------|-------|-----------------------------------------------------------|--|--|----|----|--|

| Name              | Bit 7                                                  | Bit 6       | Bit 5  | Bit 4 | Bit 4 Bit 3 Bit 2 Bit 1 Bit 0                             |  |  |    |    |  |

| TBLPTRU           | —                                                      |             | bit 21 | •     | Program Memory Table Pointer Upper Byte<br>TBLPTR<20:16>) |  |  |    |    |  |

| TBLPTRH           | Program Memory Table Pointer High Byte (TBLPTR<15:8>)  |             |        |       |                                                           |  |  |    |    |  |

| TBLPTRL           | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)    |             |        |       |                                                           |  |  | 59 |    |  |

| TABLAT            | Program Me                                             | emory Table | Latch  |       |                                                           |  |  |    | 59 |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash access.

|        |           |                               |       |       |       |       |       | _     | _                          |  |  |

|--------|-----------|-------------------------------|-------|-------|-------|-------|-------|-------|----------------------------|--|--|

| Name   | Bit 7     | Bit 6                         | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset<br>Values<br>on Page |  |  |

| PORTC  | RC7       | RC6                           | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   | 62                         |  |  |

| LATC   | LATC Data | LATC Data Output Register     |       |       |       |       |       |       |                            |  |  |

| TRISC  | PORTC D   | PORTC Data Direction Register |       |       |       |       |       |       |                            |  |  |

| LCDSE1 | SE15      | SE14                          | SE13  | SE12  | SE11  | SE10  | SE9   | SE8   | 64                         |  |  |

|        |           |                               |       |       |       |       |       |       |                            |  |  |

### TABLE 9-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

Legend: Shaded cells are not used by PORTC.

# 10.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- · Dedicated 8-bit software programmable prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 10-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 10-1. Figure 10-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 10-1: TOCON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1     | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-----------|-------|-------|

| TMR0ON | T08BIT | TOCS  | TOSE  | PSA   | PSA T0PS2 |       | T0PS0 |

| bit 7  |        |       |       |       |           |       | bit 0 |

| Legend:    |            |                                      |                               |                    |  |  |  |  |  |  |

|------------|------------|--------------------------------------|-------------------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | able bit   | W = Writable bit                     | U = Unimplemented bit         | d bit, read as '0' |  |  |  |  |  |  |

| -n = Value | at POR     | '1' = Bit is set                     | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |  |  |  |

|            |            |                                      |                               |                    |  |  |  |  |  |  |

| bit 7      | TMR0ON     | : Timer0 On/Off Control bit          |                               |                    |  |  |  |  |  |  |

|            |            | les Timer0                           |                               |                    |  |  |  |  |  |  |

|            | 0 = Stops  | Timer0                               |                               |                    |  |  |  |  |  |  |

| bit 6      | T08BIT: 1  | Timer0 8-Bit/16-Bit Control bi       | t                             |                    |  |  |  |  |  |  |

|            |            | 0 is configured as an 8-bit ti       |                               |                    |  |  |  |  |  |  |

|            | 0 = Timer  | 0 is configured as a 16-bit ti       | mer/counter                   |                    |  |  |  |  |  |  |

| bit 5      | TOCS: Tir  | TOCS: Timer0 Clock Source Select bit |                               |                    |  |  |  |  |  |  |

|            |            | 1 = Transition on TOCKI pin          |                               |                    |  |  |  |  |  |  |

|            | 0 = Intern | al instruction cycle clock (Cl       | _KO)                          |                    |  |  |  |  |  |  |

| bit 4      | TOSE: Tir  | ner0 Source Edge Select bit          |                               |                    |  |  |  |  |  |  |

|            |            | ment on high-to-low transition       |                               |                    |  |  |  |  |  |  |

|            |            | ment on low-to-high transition       |                               |                    |  |  |  |  |  |  |

| bit 3      | PSA: Tim   | er0 Prescaler Assignment bi          | it                            |                    |  |  |  |  |  |  |

|            |            |                                      | Timer0 clock input bypasses   |                    |  |  |  |  |  |  |

|            |            |                                      | er0 clock input comes from pr | escaler output.    |  |  |  |  |  |  |

| bit 2-0    |            | 0PS0: Timer0 Prescaler Sele          | ect bits                      |                    |  |  |  |  |  |  |

|            |            | 256 Prescale value                   |                               |                    |  |  |  |  |  |  |

|            |            | 28 Prescale value                    |                               |                    |  |  |  |  |  |  |

|            |            | 32 Prescale value                    |                               |                    |  |  |  |  |  |  |

|            |            | 6 Prescale value                     |                               |                    |  |  |  |  |  |  |

|            | 010 = 1:8  | B Prescale value                     |                               |                    |  |  |  |  |  |  |

|            |            | Prescale value                       |                               |                    |  |  |  |  |  |  |

|            | 000 = 1:2  | Prescale value                       |                               |                    |  |  |  |  |  |  |

### 11.2 Timer1 16-Bit Read/Write Mode

Timer1 can be configured for 16-bit reads and writes (see Figure 11-2). When the RD16 control bit (T1CON<7>) is set, the address for TMR1H is mapped to a buffer register for the high byte of Timer1. A read from TMR1L will load the contents of the high byte of Timer1 into the Timer1 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer1 must also take place through the TMR1H Buffer register. The Timer1 high byte is updated with the contents of TMR1H when a write occurs to TMR1L. This allows a user to write all 16 bits to both the high and low bytes of Timer1 at once.

The high byte of Timer1 is not directly readable or writable in this mode. All reads and writes must take place through the Timer1 High Byte Buffer register. Writes to TMR1H do not clear the Timer1 prescaler. The prescaler is only cleared on writes to TMR1L.

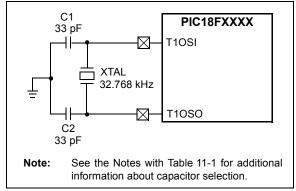

# 11.3 Timer1 Oscillator

An on-chip crystal oscillator circuit is incorporated between pins T1OSI (input) and T1OSO (amplifier output). It is enabled by setting the Timer1 Oscillator Enable bit, T1OSCEN (T1CON<3>). The oscillator is a low-power circuit rated for 32 kHz crystals. It will continue to run during all power-managed modes. The circuit for a typical LP oscillator is shown in Figure 11-3. Table 11-1 shows the capacitor selection for the Timer1 oscillator.

The user must provide a software time delay to ensure proper start-up of the Timer1 oscillator.

### FIGURE 11-3: EXTERNAL COMPONENTS FOR THE TIMER1 LP OSCILLATOR

#### TABLE 11-1: CAPACITOR SELECTION FOR THE TIMER1 OSCILLATOR<sup>(2,3,4)</sup>

| Osc Type                                                                                          | Freq                                                                                                                                                                            | C1                   | C2                   |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|--|--|--|--|--|--|--|

| LP                                                                                                | 32 kHz                                                                                                                                                                          | 27 pF <sup>(1)</sup> | 27 pF <sup>(1)</sup> |  |  |  |  |  |  |  |

| Note 1: Microchip suggests these values as a starting point in validating the oscillator circuit. |                                                                                                                                                                                 |                      |                      |  |  |  |  |  |  |  |

| 2:                                                                                                | Higher capacitance increases the stability of the oscillator, but also increases the start-up time.                                                                             |                      |                      |  |  |  |  |  |  |  |

| 3:                                                                                                | Since each resonator/crystal has its own<br>characteristics, the user should consult<br>the resonator/crystal manufacturer for<br>appropriate values of external<br>components. |                      |                      |  |  |  |  |  |  |  |

| 4:                                                                                                | Capacitor value only.                                                                                                                                                           | es are for des       | ign guidance         |  |  |  |  |  |  |  |

#### 11.3.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS1:SCS0 (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode; both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in **Section 3.0 "Power-Managed Modes"**.

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, T1RUN (T1CON<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source being currently used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the T1RUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

### 11.3.2 LOW-POWER TIMER1 OPTION

The Timer1 oscillator can operate at two distinct levels of power consumption based on device configuration. When the LPT1OSC Configuration bit is set, the Timer1 oscillator operates in a low-power mode. When LPT1OSC is not set, Timer1 operates at a higher power level. Power consumption for a particular mode is relatively constant, regardless of the device's operating mode. The default Timer1 configuration is the higher power mode.

As the Low-Power Timer1 mode tends to be more sensitive to interference, high noise environments may cause some oscillator instability. The low-power option is therefore best suited for low noise applications where power conservation is an important design consideration.

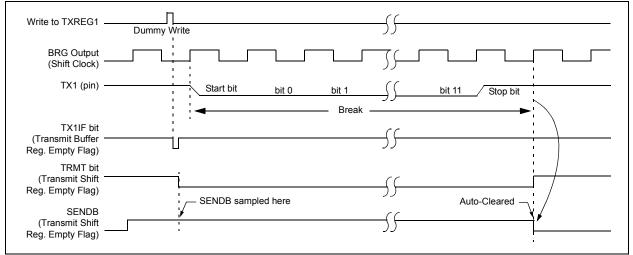

### 16.2.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift Register is loaded with data. Note that the value of data written to TXREG1 will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

Note that the data value written to the TXREG1 for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 16-10 for the timing of the Break character sequence.

#### 16.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG1 with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG1 to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG1 becomes empty, as indicated by the TX1IF, the next data byte can be written to TXREG1.

#### 16.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in **Section 16.2.4 "Auto-Wake-up on Sync Break Character"**. By enabling this feature, the EUSART will sample the next two transitions on RX1/DT1, cause an RC1IF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABD bit once the TX1IF interrupt is observed.

### FIGURE 16-10: SEND BREAK CHARACTER SEQUENCE

|                     | BRGH = 0           |            |                             |                    |            |                             |                    |            |                             |                    |            |                             |

|---------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

|                     | Foso               | = 40.00    | 0 MHz                       | Fosc               | ; = 20.00  | 0 MHz                       | Foso               | c = 10.000 | 0 MHz                       | Fosc = 8.000 MHz   |            |                             |

| BAUD<br>RATE<br>(K) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3                 | —                  |            | _                           | _                  | _          | _                           | —                  | _          | _                           | _                  | _          | _                           |

| 1.2                 | —                  | —          | —                           | 1.221              | 1.73       | 255                         | 1.202              | 0.16       | 129                         | 1.201              | -0.16      | 103                         |

| 2.4                 | 2.441              | 1.73       | 255                         | 2.404              | 0.16       | 129                         | 2.404              | 0.16       | 64                          | 2.403              | -0.16      | 51                          |

| 9.6                 | 9.615              | 0.16       | 64                          | 9.766              | 1.73       | 31                          | 9.766              | 1.73       | 15                          | 9.615              | -0.16      | 12                          |

| 19.2                | 19.531             | 1.73       | 31                          | 19.531             | 1.73       | 15                          | 19.531             | 1.73       | 7                           | —                  | _          | _                           |

| 57.6                | 56.818             | -1.36      | 10                          | 62.500             | 8.51       | 4                           | 52.083             | -9.58      | 2                           | —                  | _          | _                           |

| 115.2               | 125.000            | 8.51       | 4                           | 104.167            | -9.58      | 2                           | 78.125             | -32.18     | 1                           | —                  | —          | —                           |

#### TABLE 17-3: BAUD RATES FOR ASYNCHRONOUS MODES

|                     | BRGH = 0           |            |                             |                    |            |                             |                    |            |                             |

|---------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

|                     | Fosc = 4.000 MHz   |            |                             | Fos                | c = 2.000  | MHz                         | Fosc = 1.000 MHz   |            |                             |

| BAUD<br>RATE<br>(K) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3                 | 0.300              | 0.16       | 207                         | 0.300              | -0.16      | 103                         | 0.300              | -0.16      | 51                          |

| 1.2                 | 1.202              | 0.16       | 51                          | 1.201              | -0.16      | 25                          | 1.201              | -0.16      | 12                          |

| 2.4                 | 2.404              | 0.16       | 25                          | 2.403              | -0.16      | 12                          | —                  | _          | —                           |

| 9.6                 | 8.929              | -6.99      | 6                           | _                  | _          | _                           | —                  | _          | —                           |

| 19.2                | 20.833             | 8.51       | 2                           | —                  | _          | _                           | —                  | _          | _                           |

| 57.6                | 62.500             | 8.51       | 0                           | —                  | _          | _                           | —                  | _          | _                           |

| 115.2               | 62.500             | -45.75     | 0                           | —                  | _          | —                           | —                  | _          | —                           |

|              | BRGH = 1           |            |                             |                    |                   |                             |                    |                   |                             |                    |                  |                             |  |

|--------------|--------------------|------------|-----------------------------|--------------------|-------------------|-----------------------------|--------------------|-------------------|-----------------------------|--------------------|------------------|-----------------------------|--|

| BAUD<br>RATE | Foso               | ; = 40.00  | 0 MHz                       | Fosc               | Fosc = 20.000 MHz |                             |                    | Fosc = 10.000 MHz |                             |                    | Fosc = 8.000 MHz |                             |  |

| (K)          | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3          | _                  | _          | _                           | _                  |                   | _                           | _                  | _                 | _                           | —                  | _                | _                           |  |

| 1.2          |                    | —          | —                           | —                  |                   | —                           | —                  | —                 |                             | —                  | —                | —                           |  |

| 2.4          | _                  | _          | _                           | _                  | _                 | _                           | 2.441              | 1.73              | 255                         | 2.403              | -0.16            | 207                         |  |

| 9.6          | 9.766              | 1.73       | 255                         | 9.615              | 0.16              | 129                         | 9.615              | 0.16              | 64                          | 9.615              | -0.16            | 51                          |  |

| 19.2         | 19.231             | 0.16       | 129                         | 19.231             | 0.16              | 64                          | 19.531             | 1.73              | 31                          | 19.230             | -0.16            | 25                          |  |

| 57.6         | 58.140             | 0.94       | 42                          | 56.818             | -1.36             | 21                          | 56.818             | -1.36             | 10                          | 55.555             | 3.55             | 8                           |  |

| 115.2        | 113.636            | -1.36      | 21                          | 113.636            | -1.36             | 10                          | 125.000            | 8.51              | 4                           | —                  | _                | _                           |  |

|       | BRGH = 1           |            |                             |                    |                  |                             |                    |                  |                             |  |  |

|-------|--------------------|------------|-----------------------------|--------------------|------------------|-----------------------------|--------------------|------------------|-----------------------------|--|--|

| BAUD  | Fosc = 4.000 MHz   |            |                             | Fos                | Fosc = 2.000 MHz |                             |                    | Fosc = 1.000 MHz |                             |  |  |

| (K)   | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |

| 0.3   | _                  | _          |                             | _                  | _                |                             | 0.300              | -0.16            | 207                         |  |  |

| 1.2   | 1.202              | 0.16       | 207                         | 1.201              | -0.16            | 103                         | 1.201              | -0.16            | 51                          |  |  |

| 2.4   | 2.404              | 0.16       | 103                         | 2.403              | -0.16            | 51                          | 2.403              | -0.16            | 25                          |  |  |

| 9.6   | 9.615              | 0.16       | 25                          | 9.615              | -0.16            | 12                          | _                  | _                | _                           |  |  |

| 19.2  | 19.231             | 0.16       | 12                          | —                  | _                | _                           | _                  | _                | _                           |  |  |

| 57.6  | 62.500             | 8.51       | 3                           | _                  | _                | _                           | _                  | _                | _                           |  |  |

| 115.2 | 125.000            | 8.51       | 1                           | _                  | _                | _                           | _                  | _                | _                           |  |  |

© 2007 Microchip Technology Inc.

# REGISTER 23-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| U-0                                                                        | U-0                                                                                           | U-0                                                                         | R/P-1         | R/P-1          | R/P-1                 | R/P-1                 | R/P-1                 |  |  |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|----------------|-----------------------|-----------------------|-----------------------|--|--|--|--|

| _                                                                          | _                                                                                             | —                                                                           | BORV1         | BORV0          | BOREN1 <sup>(1)</sup> | BOREN0 <sup>(1)</sup> | PWRTEN <sup>(1)</sup> |  |  |  |  |

| bit 7                                                                      |                                                                                               | •                                                                           |               |                | •                     |                       | bit 0                 |  |  |  |  |

|                                                                            |                                                                                               |                                                                             |               |                |                       |                       |                       |  |  |  |  |

| Legend:                                                                    |                                                                                               |                                                                             |               |                |                       |                       |                       |  |  |  |  |

| R = Reada                                                                  | ıble bit                                                                                      | P = Programn                                                                | nable bit     | U = Unimplen   | nented bit, read      | l as '0'              |                       |  |  |  |  |

| -n = Value when device is unprogrammed u = Unchanged from programmed state |                                                                                               |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            |                                                                                               |                                                                             |               |                |                       |                       |                       |  |  |  |  |

| bit 7-5                                                                    | Unimplemented: Read as '0'                                                                    |                                                                             |               |                |                       |                       |                       |  |  |  |  |

| bit 4-3                                                                    | BORV1:BORV0: Brown-out Reset Voltage bits<br>11 = VBOR set to 2.1V                            |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            |                                                                                               |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 10 = VBOR se                                                                                  | t to 2.8V                                                                   |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 01 = VBOR se                                                                                  |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 00 = VBOR se                                                                                  |                                                                             |               |                |                       |                       |                       |  |  |  |  |

| bit 2-1                                                                    | BOREN1:BOREN0 Brown-out Reset Enable bits <sup>(1)</sup>                                      |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 11 = Brown-out Reset enabled in hardware only (SBOREN is disabled)                            |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 10 = Brown-out Reset enabled in hardware only and disabled in Sleep mode (SBOREN is disabled) |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            |                                                                                               | 10 = Brown-out Reset enabled and controlled by software (SBOREN is enabled) |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 10 = Brown-out Reset disabled in hardware and software                                        |                                                                             |               |                |                       |                       |                       |  |  |  |  |

| bit 0                                                                      | <b>PWRTEN</b> : Power-up Timer Enable bit <sup>(1)</sup>                                      |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 1 = PWRT dis                                                                                  |                                                                             |               |                |                       |                       |                       |  |  |  |  |

|                                                                            | 0 = PWRT en                                                                                   | abled                                                                       |               |                |                       |                       |                       |  |  |  |  |

| Note 1                                                                     | The Power-up Tin                                                                              | ner is decouple                                                             | d from Brown- | out Reset allo | wing these feat       | ures to be inde       | nendently             |  |  |  |  |

**Note 1:** The Power-up Timer is decoupled from Brown-out Reset, allowing these features to be independently controlled.

#### REGISTER 23-7: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F6390/6490/8390/8490 DEVICES

| R            | R                 | R                | R              | R                                   | R               | R      | R     |  |

|--------------|-------------------|------------------|----------------|-------------------------------------|-----------------|--------|-------|--|

| DEV2         | DEV1              | DEV0             | REV4           | REV3                                | REV2            | REV1   | REV0  |  |

| bit 7        |                   | •                |                | •                                   |                 |        | bit C |  |

|              |                   |                  |                |                                     |                 |        |       |  |

| Legend:      |                   |                  |                |                                     |                 |        |       |  |

| R = Readab   | le bit            | P = Program      | nable bit      | U = Unimplem                        | ented bit, read | as '0' |       |  |

| -n = Value w | vhen device is ur | programmed       |                | u = Unchanged from programmed state |                 |        |       |  |

|              |                   |                  |                |                                     |                 |        |       |  |

| bit 7-5      | DEV2:DEV0:        | Device ID bits   |                |                                     |                 |        |       |  |

|              | 100 = PIC18F      | 8390/8490        |                |                                     |                 |        |       |  |

|              | 101 = PIC18F      | 6390/6490        |                |                                     |                 |        |       |  |

| bit 4-0      | REV4:REV0:        | Revision ID bi   | ts             |                                     |                 |        |       |  |

|              | These bits are    | e used to indica | ate the device | revision.                           |                 |        |       |  |

#### REGISTER 23-8: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F6390/6490/8390/8490 DEVICES

| R                    | R                   | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> | DEV3 <sup>(1)</sup> |

| bit 7                |                     |                     |                     |                     |                     |                     | bit 0               |

|                      |                     |                     |                     |                     |                     |                     |                     |

| l egend.             |                     |                     |                     |                     |                     |                     |                     |

| Legenu.                   |                      |                                     |  |  |  |

|---------------------------|----------------------|-------------------------------------|--|--|--|

| R = Readable bit          | P = Programmable bit | U = Unimplemented bit, read as '0'  |  |  |  |

| -n = Value when device is | s unprogrammed       | u = Unchanged from programmed state |  |  |  |

# bit 7-0 **DEV10:DEV3:** Device ID bits<sup>(1)</sup>

These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number. 0000 0110 = PIC18F6490/8490 devices 0000 1011 = PIC18F6390/8390 devices

**Note 1:** These values for DEV10:DEV3 may be shared with other devices. The specific device is always identified by using the entire DEV10:DEV0 bit sequence.

| Byte-oriented file register operations                                                                                                                                                                                                                | Example Instruction       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| <u>15 10 9 8 7 0</u>                                                                                                                                                                                                                                  |                           |

| OPCODE d a f (FILE #)                                                                                                                                                                                                                                 | ADDWF MYREG, W, B         |

| <ul> <li>d = 0 for result destination to be WREG register</li> <li>d = 1 for result destination to be file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul> |                           |

| Byte to Byte move operations (2-word)                                                                                                                                                                                                                 |                           |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                           |

| OPCODE f (Source FILE #)                                                                                                                                                                                                                              | MOVFF MYREG1, MYREG2      |

| <u>15 12 11 0</u>                                                                                                                                                                                                                                     |                           |

| 1111 f (Destination FILE #)                                                                                                                                                                                                                           |                           |

| f = 12-bit file register address                                                                                                                                                                                                                      |                           |

| Bit-oriented file register operations                                                                                                                                                                                                                 |                           |

| <u>15 12 11 9 8 7 0</u>                                                                                                                                                                                                                               |                           |

| OPCODE b (BIT #) a f (FILE #)                                                                                                                                                                                                                         | BSF MYREG, bit, B         |

| <ul> <li>b = 3-bit position of bit in file register (f)</li> <li>a = 0 to force Access Bank</li> <li>a = 1 for BSR to select bank</li> <li>f = 8-bit file register address</li> </ul>                                                                 |                           |

| Literal operations                                                                                                                                                                                                                                    |                           |

| 15 8 7 0                                                                                                                                                                                                                                              |                           |

| OPCODE k (literal)                                                                                                                                                                                                                                    | MOVLW 7Fh                 |

| k = 8-bit immediate value                                                                                                                                                                                                                             |                           |

| Control operations                                                                                                                                                                                                                                    |                           |

| CALL, GOTO and Branch operations                                                                                                                                                                                                                      |                           |

| 15 8 7 0                                                                                                                                                                                                                                              |                           |

| OPCODE n<7:0> (literal)                                                                                                                                                                                                                               | GOTO Label                |

| 15 12 11 0                                                                                                                                                                                                                                            |                           |

| 1111 n<19:8> (literal)                                                                                                                                                                                                                                |                           |

| n = 20-bit immediate value                                                                                                                                                                                                                            |                           |

| 15 0.7 0                                                                                                                                                                                                                                              |                           |

| 15 8 7 0                                                                                                                                                                                                                                              |                           |

| 15         8 7         0           OPCODE         S         n<7:0> (literal)                                                                                                                                                                          | CALL MYFUNC               |

|                                                                                                                                                                                                                                                       | CALL MYFUNC               |

| OPCODE S n<7:0> (literal)                                                                                                                                                                                                                             | CALL MYFUNC               |

| OPCODE         S         n<7:0> (literal)           15         12         11         0                                                                                                                                                                | CALL MYFUNC               |

| OPCODE         S         n<7:0> (literal)           15         12         11         0           1111         n<19:8> (literal)                                                                                                                       | CALL MYFUNC               |

| OPCODE         S         n<7:0> (literal)           15         12         11         0           1111         n<19:8> (literal)         S = Fast bit           15         11         10         0                                                     | CALL MYFUNC<br>BRA MYFUNC |

| OPCODE         S         n<7:0> (literal)           15         12         11         0           1111         n<19:8> (literal)         S = Fast bit           15         11         10         0                                                     |                           |

| OPCODE         S         n<7:0> (literal)           15         12         11         0           1111         n<19:8> (literal)         S = Fast bit           15         11         10         0                                                     |                           |

| ANDWF             | AND W w                                                                                                                                                                                                                                                                           | ith f                                                                                                                          |                                                                                      |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Syntax:           | ANDWF                                                                                                                                                                                                                                                                             | f {,d {,a}}                                                                                                                    |                                                                                      |  |  |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                |                                                                                                                                |                                                                                      |  |  |

| Operation:        | (W) .AND. (                                                                                                                                                                                                                                                                       | (f) $\rightarrow$ dest                                                                                                         |                                                                                      |  |  |

| Status Affected:  | N, Z                                                                                                                                                                                                                                                                              |                                                                                                                                |                                                                                      |  |  |

| Encoding:         | 0001                                                                                                                                                                                                                                                                              | 01da ff                                                                                                                        | ff ffff                                                                              |  |  |

| Description:      | The contents of W are ANDed with<br>register 'f'. If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank. |                                                                                                                                |                                                                                      |  |  |

|                   | set is enabl<br>in Indexed I<br>mode when<br>Section 24<br>Bit-Oriente                                                                                                                                                                                                            | nd the extend<br>ed, this instru-<br>Literal Offset A<br>ever $f \le 95$ (5<br>.2.3 "Byte-Or<br>d Instruction<br>set Mode" for | ction operates<br>Addressing<br>Fh). See<br><b>iented and</b><br><b>s in Indexed</b> |  |  |