Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                          |

| Number of I/O              | 66                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 768 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

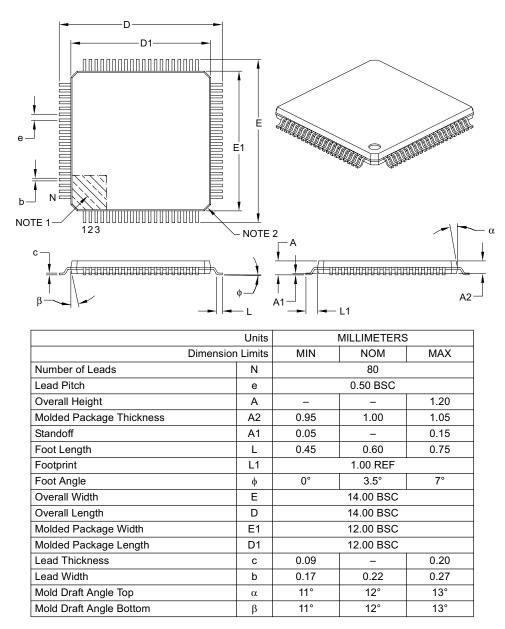

| Package / Case             | 80-TQFP                                                                   |

| Supplier Device Package    | 80-TQFP (12x12)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8490-i-pt |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                      | Pin Number        |                                         | Dir. Duffer                             |                                                                                            |  |  |  |

|--------------------------------------|-------------------|-----------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                             |                   | Pin<br>Type                             | Buffer<br>Type                          | Description                                                                                |  |  |  |

|                                      | TQFP              | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                                                                                            |  |  |  |

| MCLR/VPP/RG5                         | 7                 |                                         |                                         | Master Clear (input) or programming voltage (input).                                       |  |  |  |

| MCLR                                 |                   | I                                       | ST                                      | Master Clear (Reset) input. This pin is an active-low                                      |  |  |  |

| Vpp                                  |                   | Р                                       |                                         | Reset to the device.<br>Programming voltage input.                                         |  |  |  |

| RG5                                  |                   |                                         | ST                                      | Digital input.                                                                             |  |  |  |

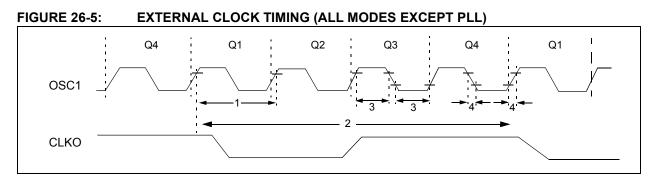

| OSC1/CLKI/RA7                        | 39                |                                         |                                         | Oscillator crystal or external clock input.                                                |  |  |  |

| OSC1                                 |                   | I                                       | ST                                      | Oscillator crystal input or external clock source input.                                   |  |  |  |

|                                      |                   |                                         |                                         | ST buffer when configured in RC mode, CMOS<br>otherwise.                                   |  |  |  |

| CLKI                                 |                   | I                                       | CMOS                                    | External clock source input. Always associated                                             |  |  |  |

|                                      |                   |                                         |                                         | with pin function OSC1. (See related OSC1/CLKI,                                            |  |  |  |

|                                      |                   | 1/0                                     |                                         | OSC2/CLKO pins.)                                                                           |  |  |  |

| RA7                                  |                   | I/O                                     | TTL                                     | General purpose I/O pin.                                                                   |  |  |  |

| OSC2/CLKO/RA6<br>OSC2                | 40                | 0                                       |                                         | Oscillator crystal or clock output.                                                        |  |  |  |

| 0302                                 |                   | 0                                       | _                                       | Oscillator crystal output. Connects to crystal or<br>resonator in Crystal Oscillator mode. |  |  |  |

| CLKO                                 |                   | 0                                       | _                                       | In RC mode, OSC2 pin outputs CLKO, which has                                               |  |  |  |

|                                      |                   |                                         |                                         | 1/4 the frequency of OSC1 and denotes the                                                  |  |  |  |

| DAG                                  |                   |                                         | TTI                                     | instruction cycle rate.                                                                    |  |  |  |

| RA6 I/O TTL General purpose I/O pin. |                   |                                         |                                         |                                                                                            |  |  |  |

| -                                    | ompatible input   |                                         |                                         | CMOS = CMOS compatible input or output                                                     |  |  |  |

|                                      | itt Trigger input | with CI                                 | vius leve                               |                                                                                            |  |  |  |

| I = Input                            | r                 |                                         |                                         | O = Output                                                                                 |  |  |  |

| P = Powe                             | I                 |                                         |                                         | OD = Open-Drain (no P diode to VDD)                                                        |  |  |  |

#### TABLE 1-2:PIC18F6X90 PINOUT I/O DESCRIPTIONS

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| Pin Name                                                                                                                                                                                                                                                                                                             | Pin Number | Pin Buffe       |                      | Description                                                                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------|--|

| Fill Naille                                                                                                                                                                                                                                                                                                          | TQFP       | Туре            | Туре                 | Description                                                                                                   |  |

|                                                                                                                                                                                                                                                                                                                      |            |                 |                      | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |  |

| RB0/INT0<br>RB0<br>INT0                                                                                                                                                                                                                                                                                              | 58         | I/O<br>I        | TTL<br>ST            | Digital I/O.<br>External interrupt 0.                                                                         |  |

| RB1/INT1/SEG8<br>RB1<br>INT1<br>SEG8                                                                                                                                                                                                                                                                                 | 57         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External interrupt 1.<br>SEG8 output for LCD.                                                 |  |

| RB2/INT2/SEG9<br>RB2<br>INT2<br>SEG9                                                                                                                                                                                                                                                                                 | 56         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External interrupt 2.<br>SEG9 output for LCD.                                                 |  |

| RB3/INT3/SEG10<br>RB3<br>INT3<br>SEG10                                                                                                                                                                                                                                                                               | 55         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External interrupt 3.<br>SEG10 output for LCD.                                                |  |

| RB4/KBI0/SEG11<br>RB4<br>KBI0<br>SEG11                                                                                                                                                                                                                                                                               | 54         | I/O<br>I<br>O   | TTL<br>TTL<br>Analog | Digital I/O.<br>Interrupt-on-change pin.<br>SEG11 output for LCD.                                             |  |

| RB5/KBI1<br>RB5<br>KBI1                                                                                                                                                                                                                                                                                              | 53         | I/O<br>I        | TTL<br>TTL           | Digital I/O.<br>Interrupt-on-change pin.                                                                      |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                                                                                                                                                                                                                                                                                   | 52         | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming clock pin.              |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                                                                                                                                                                                                                                                                                   | 47         | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                |  |

| Legend:       TTL       = TTL compatible input       CMOS       = CMOS compatible input or output         ST       = Schmitt Trigger input with CMOS levels       Analog       = Analog input         I       = Input       O       = Output         P       = Power       OD       = Open-Drain (no P diode to VDD) |            |                 |                      |                                                                                                               |  |

| <b>Note 1:</b> Default assignment for CCP2 when Configuration bit, CCP2MX, is set.                                                                                                                                                                                                                                   |            |                 |                      |                                                                                                               |  |

#### TABLE 1-3: PIC18F8X90 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| R/W-0                                                             | R/W-1 <sup>(1)</sup>                                                                                                  | U-0                         | R/W-1                    | R-1               | R-1             | R/W-0            | R/W-0         |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------|-------------------|-----------------|------------------|---------------|

| IPEN                                                              | SBOREN                                                                                                                | _                           | RI                       | TO                | PD              | POR              | BOR           |

| bit 7                                                             |                                                                                                                       |                             |                          |                   |                 |                  | bit           |

| Legend:                                                           |                                                                                                                       |                             |                          |                   |                 |                  |               |

| R = Readable                                                      | <u>e</u> bit                                                                                                          | W = Writable                | bit                      | U = Unimpler      | mented bit, rea | d as '0'         |               |

| -n = Value at                                                     |                                                                                                                       | '1' = Bit is se             |                          | '0' = Bit is cle  |                 | x = Bit is unkr  | nown          |

|                                                                   |                                                                                                                       |                             | -                        |                   |                 |                  | -             |

| bit 7                                                             | IPEN: Interru                                                                                                         | ot Priority Ena             | ble bit                  |                   |                 |                  |               |

|                                                                   |                                                                                                                       | riority levels o            |                          |                   |                 |                  |               |

|                                                                   | -                                                                                                                     | -                           |                          | PIC16CXXX Co      | mpatibility mod | le)              |               |

| bit 6                                                             | SBOREN: BO                                                                                                            | DR Software E               | nable bit <sup>(1)</sup> |                   |                 |                  |               |

|                                                                   | If BOREN1:B                                                                                                           |                             |                          |                   |                 |                  |               |

|                                                                   | 1 = BOR is e<br>0 = BOR is d                                                                                          |                             |                          |                   |                 |                  |               |

|                                                                   | If BOREN1:B                                                                                                           |                             | 10 or 11.                |                   |                 |                  |               |

|                                                                   |                                                                                                                       | and read as                 |                          |                   |                 |                  |               |

| bit 5                                                             | Unimplemen                                                                                                            | ted: Read as                | 'O'                      |                   |                 |                  |               |

| bit 4                                                             | RI: RESET IN                                                                                                          | struction Flag              | bit                      |                   |                 |                  |               |

| 1 = The RESET instruction was not executed (set by firmware only) |                                                                                                                       |                             |                          |                   |                 |                  |               |

|                                                                   |                                                                                                                       | ET instruction              |                          | d causing a de    | vice Reset (m   | ust be set in so | oftware after |

| bit 3                                                             | TO: Watchdo                                                                                                           | g Time-out Fla              | ıg bit                   |                   |                 |                  |               |

|                                                                   | <ul> <li>1 = Set by power-up, CLRWDT instruction or SLEEP instruction</li> <li>0 = A WDT time-out occurred</li> </ul> |                             |                          |                   |                 |                  |               |

|                                                                   |                                                                                                                       |                             |                          |                   |                 |                  |               |

| bit 2                                                             | PD: Power-D                                                                                                           |                             | •                        |                   |                 |                  |               |

|                                                                   |                                                                                                                       |                             | the CLRWDT in            |                   |                 |                  |               |

| bit 1                                                             |                                                                                                                       |                             |                          | Clion             |                 |                  |               |

|                                                                   | <b>POR:</b> Power-on Reset Status bit<br>1 = A Power-on Reset has not occurred (set by firmware only)                 |                             |                          |                   |                 |                  |               |

|                                                                   | <ul> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>             |                             |                          |                   |                 |                  |               |

| bit 0                                                             |                                                                                                                       | out Reset Stat              | •                        |                   |                 |                  | ,             |

|                                                                   | 1 = A Brown                                                                                                           | -out Reset ha               | s not occurred           | (set by firmwa    | re only)        |                  |               |

|                                                                   |                                                                                                                       |                             |                          |                   |                 | n-out Reset occ  | curs)         |

| Note 1: If S                                                      | SBOREN is enal                                                                                                        | oled, its Reset             | state is '1'; ot         | herwise, it is '0 |                 |                  |               |

| Note 1: It                                                        | is recommende                                                                                                         | d that the $\overline{POF}$ | bit be set afte          | er a Power-on F   | Reset has been  | detected, so th  | at subseque   |

|                                                                   | ower-on Resets                                                                                                        |                             |                          |                   |                 |                  |               |

### REGISTER 4-1: RCON: RESET CONTROL REGISTER

2: Brown-out Reset is said to have occurred when BOR is '0' and POR is '1' (assuming that POR was set to '1' by software immediately after a Power-on Reset).

#### 5.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by '1' afterwards

- POSTINC: accesses the FSR value, then automatically increments it by '1' afterwards

- PREINC: increments the FSR value by '1', then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the new value in the operation.

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by the value in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

### 5.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1, using INDF0 as an operand, will return 00h. Attempts to write to INDF1, using INDF0 as the operand, will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair, but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

Example 7-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 7-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 7-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = | ARG1H:ARG1L • ARG2H:ARG2L<br>(ARG1H • ARG2H • $2^{16}$ ) +<br>(ARG1H • ARG2H • $2^{16}$ ) +                   |

|-----------|---|---------------------------------------------------------------------------------------------------------------|

|           |   | $(ARG1H \bullet ARG2L \bullet 2^{8}) +$<br>$(ARG1L \bullet ARG2H \bullet 2^{8}) +$<br>$(ARG1L \bullet ARG2L)$ |

#### EXAMPLE 7-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

| <pre>MOVF ARG1L, W MULWF ARG2L ; ARG1L * ARG2L-&gt; ; PRODH:PRODL MOVFF PRODH, RES1 ; MOVFF PRODL, RES0 ; ; MOVF ARG1H, W MULWF ARG2H ; ARG1H * ARG2H-&gt; ; PRODH:PRODL MOVFF PRODL, RES2 ; ; MOVF ARG1L, W MULWF ARG2H ; ARG1L * ARG2H-&gt; ; PRODH:PRODL MOVF PRODL, W ; ADDWF RES1, F ; Add cross MOVF PRODH, W ; products ADDWFC RES2, F ; CLRF WREG ; ADDWFC RES3, F ; ; MOVF ARG1H, W ; MULWF ARG2L ; ARG1H * ARG2L-&gt; </pre>                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ; PRODH:PRODL<br>MOVFF PRODL, RES1<br>;<br>MOVFF PRODL, RES0<br>;<br>MOVF ARG1H, W<br>MULWF ARG2H ; ARG1H * ARG2H-><br>; PRODH:PRODL<br>MOVFF PRODL, RES3<br>;<br>MOVF ARG1L, W<br>MULWF ARG2H ; ARG1L * ARG2H-><br>; PRODH:PRODL<br>MOVF PRODL, W<br>ADDWF RES1, F ; Add cross<br>MOVF PRODH, W<br>ADDWF RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W<br>; ARG1H * ARG2L ; ARG1H * ARG2L->                         |

| <pre>MOVFF PRODH, RES1 ;<br/>MOVFF PRODL, RES0 ;<br/>;<br/>MOVF ARG1H, W<br/>MULWF ARG2H ; ARG1H * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVFF PRODH, RES3 ;<br/>MOVFF PRODL, RES2 ;<br/>;<br/>MOVF ARG1L, W<br/>MULWF ARG2H ; ARG1L * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVF PRODL, W ;<br/>ADDWF RES1, F ; Add cross<br/>MOVF PRODH, W ; products<br/>ADDWFC RES2, F ;<br/>CLRF WREG ;<br/>ADDWFC RES3, F ;<br/>;<br/>MOVF ARG1H, W ;<br/>MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre> |

| <pre>MOVFF PRODL, RES0 ;  MOVF ARG1H, W MULWF ARG2H ; ARG1H * ARG2H-&gt; ; PRODH:PRODL MOVFF PRODL, RES3 ; MOVFF PRODL, RES2 ;  MOVF ARG1L, W MULWF ARG2H ; ARG1L * ARG2H-&gt; ; PRODH:PRODL MOVF PRODL, W ; ADDWF RES1, F ; Add cross MOVF PRODH, W ; products ADDWFC RES2, F ; CLRF WREG ; ADDWFC RES3, F ; ;  MOVF ARG1H, W ; MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                                                      |

| ;<br>MOVF ARG1H, W<br>MULWF ARG2H ; ARG1H * ARG2H-><br>; PRODH:PRODL<br>MOVFF PRODL, RES3 ;<br>MOVFF PRODL, RES2 ;<br>;<br>MOVF ARG1L, W<br>MULWF ARG2H ; ARG1L * ARG2H-><br>; PRODH:PRODL<br>MOVF PRODL, W ;<br>ADDWF RES1, F ; Add cross<br>MOVF PRODH, W ; products<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                       |

| <pre>MULWF ARG2H ; ARG1H * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVFF PRODL, RES3 ;<br/>MOVFF PRODL, RES2 ;<br/>;<br/>MOVF ARG1L, W<br/>MULWF ARG2H ; ARG1L * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVF PRODL, W ;<br/>ADDWF RES1, F ; Add cross<br/>MOVF PRODH, W ; products<br/>ADDWFC RES2, F ;<br/>CLRF WREG ;<br/>ADDWFC RES3, F ;<br/>;<br/>MOVF ARG1H, W ;<br/>MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                         |

| <pre>MULWF ARG2H ; ARG1H * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVFF PRODL, RES3 ;<br/>MOVFF PRODL, RES2 ;<br/>;<br/>MOVF ARG1L, W<br/>MULWF ARG2H ; ARG1L * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVF PRODL, W ;<br/>ADDWF RES1, F ; Add cross<br/>MOVF PRODH, W ; products<br/>ADDWFC RES2, F ;<br/>CLRF WREG ;<br/>ADDWFC RES3, F ;<br/>;<br/>MOVF ARG1H, W ;<br/>MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                         |

| ; PRODH:PRODL<br>MOVFF PRODL, RES3<br>;<br>MOVF ARG1L, W<br>MULWF ARG2H ; ARG1L * ARG2H-><br>; PRODH:PRODL<br>MOVF PRODL, W ;<br>ADDWF RES1, F ; Add cross<br>MOVF PRODH, W ; products<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                       |

| ; PRODH:PRODL<br>MOVFF PRODL, RES3<br>MOVFF PRODL, RES2<br>;<br>MOVF ARG1L, W<br>MULWF ARG2H ; ARG1L * ARG2H-><br>; PRODH:PRODL<br>MOVF PRODL, W ;<br>ADDWF RES1, F ; Add cross<br>MOVF PRODH, W ; products<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                  |

| <pre>MOVFF PRODH, RES3 ;<br/>MOVFF PRODL, RES2 ;<br/>;<br/>MOVF ARG1L, W<br/>MULWF ARG2H ; ARG1L * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVF PRODL, W ;<br/>ADDWF RES1, F ; Add cross<br/>MOVF PRODH, W ; products<br/>ADDWFC RES2, F ;<br/>CLRF WREG ;<br/>ADDWFC RES3, F ;<br/>;<br/>MOVF ARG1H, W ;<br/>MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                                                                                |

| <pre>MOVFF PRODL, RES2 ;  MOVF ARG1L, W MULWF ARG2H ; ARG1L * ARG2H-&gt; ; PRODH:PRODL MOVF PRODL, W ; ADDWF RES1, F ; Add cross MOVF PRODH, W ; products ADDWFC RES2, F ; CLRF WREG ; ADDWFC RES3, F ; ;  MOVF ARG1H, W ; MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                                                                                                                                                            |

| ;<br>MOVF ARG1L, W<br>MULWF ARG2H ; ARG1L * ARG2H-><br>; PRODH:PRODL<br>MOVF PRODL, W ;<br>ADDWF RES1, F ; Add cross<br>MOVF PRODH, W ; products<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                             |

| <pre>MULWF ARG2H ; ARG1L * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVF PRODL, W ;<br/>ADDWF RES1, F ; Add cross<br/>MOVF PRODH, W ; products<br/>ADDWFC RES2, F ;<br/>CLRF WREG ;<br/>ADDWFC RES3, F ;<br/>;<br/>mOVF ARG1H, W ;<br/>MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                                                                                                                                                        |

| <pre>MULWF ARG2H ; ARG1L * ARG2H-&gt;<br/>; PRODH:PRODL<br/>MOVF PRODL, W ;<br/>ADDWF RES1, F ; Add cross<br/>MOVF PRODH, W ; products<br/>ADDWFC RES2, F ;<br/>CLRF WREG ;<br/>ADDWFC RES3, F ;<br/>;<br/>mOVF ARG1H, W ;<br/>MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                                                                                                                                                        |

| ; PRODH:PRODL<br>MOVF PRODL, W<br>ADDWF RES1, F<br>MOVF PRODH, W<br>ADDWFC RES2, F<br>CLRF WREG<br>ADDWFC RES3, F<br>;<br>MOVF ARG1H, W<br>MULWF ARG2L<br>; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                  |

| <pre>MOVF PRODL, W ; ADDWF RES1, F ; Add cross MOVF PRODH, W ; products ADDWFC RES2, F ; CLRF WREG ; ADDWFC RES3, F ; ; MOVF ARG1H, W ; MULWF ARG2L ; ARG1H * ARG2L-&gt;</pre>                                                                                                                                                                                                                                                                                               |

| ADDWF RES1, F ; Add cross<br>MOVF PRODH, W ; products<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                        |

| MOVF PRODH, W ; products<br>ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                     |

| ADDWFC RES2, F ;<br>CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                 |

| CLRF WREG ;<br>ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                                     |

| ADDWFC RES3, F ;<br>;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                                                    |

| ;<br>MOVF ARG1H, W ;<br>MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MULWF ARG2L ; ARG1H * ARG2L->                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ; PRODH:PRODL                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MOVF PRODL, W ;                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ADDWF RES1, F ; Add cross                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MOVF PRODH, W ; products                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADDWFC RES2, F ;                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CLRF WREG ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ADDWFC RES3, F ;                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADDWIG NEDS, F ,                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Example 7-4 shows the sequence to do a 16 x 16 signed multiply. Equation 7-2 shows the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the signed bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 7-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0= ARG1H:ARG1L • ARG2H:ARG2L                         |    |

|--------------------------------------------------------------|----|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                   |    |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                        |    |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                        |    |

| $(ARG1L \bullet ARG2L) +$                                    | ,  |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{1})$ |    |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H:ARG2L \bullet 2^{1})$ | 6) |

|                                                              |    |

#### EXAMPLE 7-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|          |          |             | •• |                  |

|----------|----------|-------------|----|------------------|

|          | MOVF     | ARG1L, W    |    |                  |

|          | MULWF    | ARG2L       | ;  | ARG1L * ARG2L -> |

|          |          |             | ;  | PRODH:PRODL      |

|          | MOVFF    | PRODH, RES1 | ;  |                  |

|          | MOVFF    | PRODL, RESO | ;  |                  |

| ;        |          |             |    |                  |

|          | MOVF     | ARG1H, W    |    |                  |

|          | MULWF    | ARG2H       | ;  | ARG1H * ARG2H -> |

|          |          |             |    | PRODH:PRODL      |

|          | MOVFF    | PRODH, RES3 | ;  |                  |

|          | MOVFF    |             |    |                  |

| ;        |          |             | ,  |                  |

|          | MOVF     | ARG1L, W    |    |                  |

|          | MULWF    | ARG2H       | ;  | ARG1L * ARG2H -> |

|          |          | mobil       |    | PRODH:PRODL      |

|          | MOVF     | PRODL, W    | ;  | 11100111110000   |

|          |          | RES1, F     |    | Add cross        |

|          | MOVE     | PRODH, W    |    | products         |

|          |          | RES2, F     | ;  |                  |

|          |          | WREG        | ;  |                  |

|          |          | RES3, F     | ;  |                  |

| ;        | IIDDWI C | 1000, 1     | '  |                  |

| '        | MOVE     | ARG1H, W    |    |                  |

|          | MULWF    | ARG2L       | ;  | ARG1H * ARG2L -> |

|          | NOLWE    | ANGZI       |    | PRODH:PRODL      |

|          | MOVF     | PRODL, W    | ;  | 110011.11000     |

|          |          | RES1, F     |    | Add cross        |

|          |          | PRODH, W    |    | products         |

|          |          | RES2, F     | ;  | produces         |

|          |          | WREG        | ;  |                  |

|          |          | RES3, F     | ;  |                  |

| ;        | 11001110 | -           |    |                  |

| '        | BULGC    | ARG2H, 7    |    | ARG2H:ARG2L neg? |

|          | BRA      | SIGN ARG1   | ΄. | no, check ARG1   |

|          | MOVE     | ARG1L, W    | ;  | no, encer mor    |

|          |          | RES2        |    |                  |

|          | MOVF     | ARG1H, W    | ;; |                  |

|          | SUBWFB   |             | '  |                  |

|          | SODWED   | INESS       |    |                  |

| ;<br>STG | N ARG1   |             |    |                  |

| 510      | _        | ARG1H, 7    |    | ARG1H:ARG1L neg? |

|          | BRA      |             |    | no, done         |

|          | MOVF     | ARG2L, W    |    | 110, UUIIC       |

|          | SUBWF    | RES2        | ;  |                  |

|          | MOVF     | ARG2H, W    | ;  |                  |

|          | SUBWFB   |             | ;  |                  |

|          | 20DMED   | 1/100       |    |                  |

| ,<br>COM | T CODE   |             |    |                  |

| CON      | T_CODE   |             |    |                  |

|          | •        |             |    |                  |

|          |          |             |    |                  |

## 8.0 INTERRUPTS

The PIC18F6390/6490/8390/8490 devices have multiple interrupt sources and an interrupt priority feature that allows most interrupt sources to be assigned a high-priority level or a low-priority level. The high-priority interrupt vector is at 0008h and the low-priority interrupt vector is at 0018h. High-priority interrupt events will interrupt any low-priority interrupts that may be in progress.

There are thirteen registers which are used to control interrupt operation. These registers are:

- RCON

- INTCON

- INTCON2

- INTCON3

- PIR1, PIR2, PIR3

- PIE1, PIE2, PIE3

- IPR1, IPR2, IPR3

It is recommended that the Microchip header files supplied with MPLAB<sup>®</sup> IDE be used for the symbolic bit names in these registers. This allows the assembler/ compiler to automatically take care of the placement of these bits within the specified register.

In general, interrupt sources have three bits to control their operation. They are:

- Flag bit to indicate that an interrupt event occurred

- Enable bit that allows program execution to branch to the interrupt vector address when the flag bit is set

- **Priority bit** to select high priority or low priority

The interrupt priority feature is enabled by setting the IPEN bit (RCON<7>). When interrupt priority is enabled, there are two bits which enable interrupts globally. Setting the GIEH bit (INTCON<7>) enables all interrupts that have the priority bit set (high priority). Setting the GIEL bit (INTCON<6>) enables all interrupts that have the priority bit cleared (low priority). When the interrupt flag, enable bit and appropriate global interrupt enable bit are set, the interrupt will vector immediately to address 0008h or 0018h, depending on the priority bit setting. Individual interrupts can be disabled through their corresponding enable bits.

When the IPEN bit is cleared (default state), the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup> mid-range devices. In Compatibility mode, the interrupt priority bits for each source have no effect. INTCON<6> is the PEIE bit, which enables/disables all peripheral interrupt sources. INTCON<7> is the GIE bit, which enables/disables all interrupt sources. All interrupts branch to address 0008h in Compatibility mode.

When an interrupt is responded to, the global interrupt enable bit is cleared to disable further interrupts. If the IPEN bit is cleared, this is the GIE bit. If interrupt priority levels are used, this will be either the GIEH or GIEL bit. High-priority interrupt sources can interrupt a lowpriority interrupt. Low-priority interrupts are not processed while high-priority interrupts are in progress.

The return address is pushed onto the stack and the PC is loaded with the interrupt vector address (0008h or 0018h). Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bits must be cleared in software before re-enabling interrupts to avoid recursive interrupts.

The "return from interrupt" instruction, RETFIE, exits the interrupt routine and sets the GIE bit (GIEH or GIEL if priority levels are used), which re-enables interrupts.

For external interrupt events, such as the INTx pins or the PORTB input change interrupt, the interrupt latency will be three to four instruction cycles. The exact latency is the same for one or two-cycle instructions. Individual interrupt flag bits are set, regardless of the status of their corresponding enable bit or the GIE bit.

Note: Do not use the MOVFF instruction to modify any of the interrupt control registers while any interrupt is enabled. Doing so may cause erratic microcontroller behavior.

### 8.1 INTCON Registers

The INTCON registers are readable and writable registers which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 8-1: INTCON: INTERRUPT CONTROL REGISTER

| GIE/GIEH         PEIE/GIEL         TMR0IE         INT0IE         RBIE         TMR0IF         INT0IF         RBIF <sup>(1)</sup> bit 7         bit | R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| bit 7 bit                                                                                                                                         | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

|                                                                                                                                                   | bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | GIE/GIEH: Global Interrupt Enable bit<br><u>When IPEN = 0:</u><br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts<br><u>When IPEN = 1:</u><br>1 = Enables all high-priority interrupts |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0 = Disables all interrupts                                                                                                                                                                               |

| bit 6   | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                                                                                |

|         | <u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts<br><u>When IPEN = 1:</u>                                                                |

|         | <ul> <li>1 = Enables all low-priority peripheral interrupts</li> <li>0 = Disables all low-priority peripheral interrupts</li> </ul>                                                                       |

| bit 5   | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                                                                                                |

|         | <ul> <li>1 = Enables the TMR0 overflow interrupt</li> <li>0 = Disables the TMR0 overflow interrupt</li> </ul>                                                                                             |

| bit 4   | INTOIE: INTO External Interrupt Enable bit                                                                                                                                                                |

|         | <ul> <li>1 = Enables the INT0 external interrupt</li> <li>0 = Disables the INT0 external interrupt</li> </ul>                                                                                             |

| bit 3   | RBIE: RB Port Change Interrupt Enable bit                                                                                                                                                                 |

|         | <ul> <li>1 = Enables the RB port change interrupt</li> <li>0 = Disables the RB port change interrupt</li> </ul>                                                                                           |

| bit 2   | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                                                                                  |

|         | <ul> <li>1 = TMR0 register has overflowed (must be cleared in software)</li> <li>0 = TMR0 register did not overflow</li> </ul>                                                                            |

| bit 1   | INT0IF: INT0 External Interrupt Flag bit                                                                                                                                                                  |

|         | <ul> <li>1 = The INT0 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT0 external interrupt did not occur</li> </ul>                                                         |

| bit 0   | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                                                                                             |

|         | <ul> <li>1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)</li> <li>0 = None of the RB7:RB4 pins have changed state</li> </ul>                                             |

| Note 1: | A mismatch condition will continue to set this bit. Reading PORTB will end the mismatch condition and                                                                                                     |

allow the bit to be cleared.

## 9.9 PORTJ, TRISJ and LATJ Registers

#### Note: PORTJ is available only on 80-pin devices.

PORTJ is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISJ. Setting a TRISJ bit (= 1) will make the corresponding PORTJ pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISJ bit (= 0) will make the corresponding PORTJ pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATJ) is also memory mapped. Read-modify-write operations on the LATJ register read and write the latched output value for PORTJ.

All pins on PORTJ are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: On a Power-on Reset, these pins an |  |  |  |  |  |  |

|------------------------------------------|--|--|--|--|--|--|

| configured as digital inputs.            |  |  |  |  |  |  |

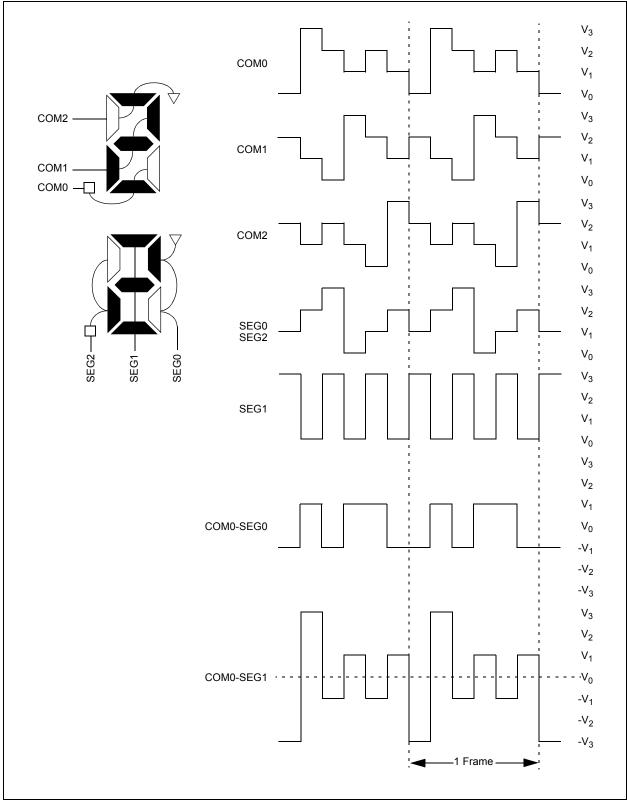

PORTJ is also multiplexed with LCD segment drives controlled by the LCDSE4 register. I/O port functions are only available when the segments are disabled.

#### EXAMPLE 9-9: INITIALIZING PORTJ

| CLRF  | PORTJ | ; Initialize PORTG by   |

|-------|-------|-------------------------|

|       |       | ; clearing output       |

|       |       | ; data latches          |

| CLRF  | LATJ  | ; Alternate method      |

|       |       | ; to clear output       |

|       |       | ; data latches          |

| MOVLW | OxCF  | ; Value used to         |

|       |       | ; initialize data       |

|       |       | ; direction             |

| MOVWF | TRISJ | ; Set RJ3:RJ0 as inputs |

|       |       | ; RJ5:RJ4 as output     |

|       |       | ; RJ7:RJ6 as inputs     |

|       |       |                         |

### 14.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F6390/6490/8390/8490 devices have two CCP (Capture/Compare/PWM) modules, designated CCP1 and CCP2. Both modules implement standard capture, compare and Pulse-Width Modulation (PWM) modes.

Each CCP module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operation in the following sections is described with respect to CCP2, but is equally applicable to CCP1.

#### REGISTER 14-1: CCPxCON: CCPx CONTROL REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |  |  |  |

|-------|-----|-------|-------|--------|--------|--------|--------|--|--|--|

| —     | _   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |  |  |  |

| bit 7 |     |       |       |        |        |        | bit 0  |  |  |  |

|       |     |       |       |        |        |        |        |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

| bit 5-4 | DCxB1:DCxB0: PWM Duty Cycle bit 1 and bit 0 for CCPx Module                                                                                                                        |  |  |  |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|         | Capture mode:                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|         | Unused.                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|         | Compare mode:                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|         | Unused.                                                                                                                                                                            |  |  |  |  |  |  |  |  |

|         | PWM mode:                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|         | These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCxB9:DCxB2) of the duty cycle are found in CCPRxL. |  |  |  |  |  |  |  |  |

| bit 3-0 | CCPxM3:CCPxM0: CCPx Module Mode Select bits                                                                                                                                        |  |  |  |  |  |  |  |  |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                                           |  |  |  |  |  |  |  |  |

|         | 0001 = Reserved                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|         | 0010 = Compare mode, toggle output on match (CCPxIF bit is set)                                                                                                                    |  |  |  |  |  |  |  |  |

|         | 0011 = Reserved                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|         | 0100 = Capture mode, every falling edge                                                                                                                                            |  |  |  |  |  |  |  |  |

|         | 0101 = Capture mode, every rising edge                                                                                                                                             |  |  |  |  |  |  |  |  |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                                         |  |  |  |  |  |  |  |  |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                                        |  |  |  |  |  |  |  |  |

|         | 1000 = Compare mode: initialize CCPx pin low; on compare match, force CCPx pin high (CCPxIF bit is set)                                                                            |  |  |  |  |  |  |  |  |

|         | 1001 = Compare mode: initialize CCPx pin high; on compare match, force CCPx pin low (CCPxIF bit is set)                                                                            |  |  |  |  |  |  |  |  |

|         | 1010 = Compare mode: generate software interrupt on compare match (CCPxIF bit is set, CCPx pin                                                                                     |  |  |  |  |  |  |  |  |

|         | reflects I/O state)                                                                                                                                                                |  |  |  |  |  |  |  |  |

- 1011 = Compare mode: trigger special event, reset timer, start A/D conversion on CCPx match (CCPxIF bit is set)<sup>(1)</sup>

- 11xx = PWM mode

- **Note 1:** CCPxM3:CCPxM0 = 1011 will only reset the timer and not start the A/D conversion on the CCPx match.

#### 15.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full flag bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter #106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter #107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared. If not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 15-21).

After the write to the SSPBUF, each bit of address will be shifted out on the falling edge of SCL until all 7 address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 15.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

#### 15.4.10.2 WCOL Status Flag

If the user writes the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

WCOL must be cleared in software.

#### 15.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

#### 15.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/ low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

#### 15.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

#### 15.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 15.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

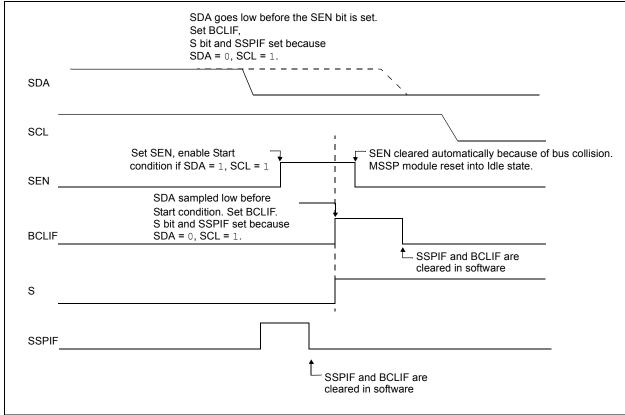

#### 15.4.17.1 Bus Collision During a Start Condition

During a Start condition, a bus collision occurs if:

- a) SDA or SCL are sampled low at the beginning of the Start condition (Figure 15-26).

- b) SCL is sampled low before SDA is asserted low (Figure 15-27).

During a Start condition, both the SDA and the SCL pins are monitored.

If the SDA pin is already low, or the SCL pin is already low, then all of the following occur:

- the Start condition is aborted,

- · the BCLIF flag is set and

- the MSSP module is reset to its Idle state (Figure 15-26).

The Start condition begins with the SDA and SCL pins deasserted. When the SDA pin is sampled high, the Baud Rate Generator is loaded from SSPADD<6:0> and counts down to '0'. If the SCL pin is sampled low while SDA is high, a bus collision occurs because it is assumed that another master is attempting to drive a data '1' during the Start condition.

If the SDA pin is sampled low during this count, the BRG is reset and the SDA line is asserted early (Figure 15-28). If, however, a '1' is sampled on the SDA pin, the SDA pin is asserted low at the end of the BRG count. The Baud Rate Generator is then reloaded and counts down to 0 and during this time, if the SCL pins are sampled as '0', a bus collision does not occur. At the end of the BRG count, the SCL pin is asserted low.

Note: The reason that bus collision is not a factor during a Start condition is that no two bus masters can assert a Start condition at the exact same time. Therefore, one master will always assert SDA before the other. This condition does not cause a bus collision because the two masters must be allowed to arbitrate the first address following the Start condition. If the address is the same, arbitration must be allowed to continue into the data portion, Repeated Start or Stop conditions.

#### FIGURE 15-26: BUS COLLISION DURING START CONDITION (SDA ONLY)

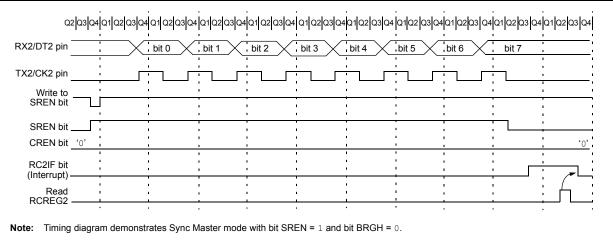

#### 16.4.2 EUSART SYNCHRONOUS SLAVE RECEPTION

The operation of the Synchronous Master and Slave modes is identical except in the case of Sleep or any Idle mode and bit, SREN, which is a "don't care" in Slave mode.

If receive is enabled by setting the CREN bit prior to entering Sleep or any Idle mode, then a word may be received while in this low-power mode. Once the word is received, the RSR register will transfer the data to the RCREG1 register. If the RC1IE enable bit is set, the interrupt generated will wake the chip from the low-power mode. If the global interrupt is enabled, the program will branch to the interrupt vector. To set up a Synchronous Slave Reception:

- 1. Enable the synchronous master serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. If interrupts are desired, set enable bit, RC1IE.

- 3. If 9-bit reception is desired, set bit, RX9.

- 4. To enable reception, set enable bit, CREN.

- 5. Flag bit, RC1IF, will be set when reception is complete. An interrupt will be generated if enable bit, RC1IE, was set.

- Read the RCSTA1 register to get the 9th bit (if enabled) and determine if any error occurred during reception.

- 7. Read the 8-bit received data by reading the RCREG1 register.

- 8. If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7                                                | Bit 6       | Bit 5       | Bit 4       | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|------------------------------------------------------|-------------|-------------|-------------|-------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                             | PEIE/GIEL   | TMR0IE      | INT0IE      | RBIE  | TMR0IF | INT0IF | RBIF   | 59                         |