Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f8490t-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Features                                  | PIC18F6390                                                                                                   | PIC18F6490                                                                                                   | PIC18F8390                                                                                                   | PIC18F8490                                                                                                   |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|                                           | DC – 40 MHz                                                                                                  |

| Operating Frequency                       |                                                                                                              |                                                                                                              |                                                                                                              |                                                                                                              |

| Program Memory (Bytes)                    | 8K                                                                                                           | 16K                                                                                                          | 8K                                                                                                           | 16K                                                                                                          |

| Program Memory (Instructions)             | 4096                                                                                                         | 8192                                                                                                         | 4096                                                                                                         | 8192                                                                                                         |

| Data Memory (Bytes)                       | 768                                                                                                          | 768                                                                                                          | 768                                                                                                          | 768                                                                                                          |

| Interrupt Sources                         | 22                                                                                                           | 22                                                                                                           | 22                                                                                                           | 22                                                                                                           |

| I/O Ports                                 | Ports A, B, C, D, E,<br>F, G                                                                                 | Ports A, B, C, D, E,<br>F, G                                                                                 | Ports A, B, C, D, E,<br>F, G, H, J                                                                           | Ports A, B, C, D, E,<br>F, G, H, J                                                                           |

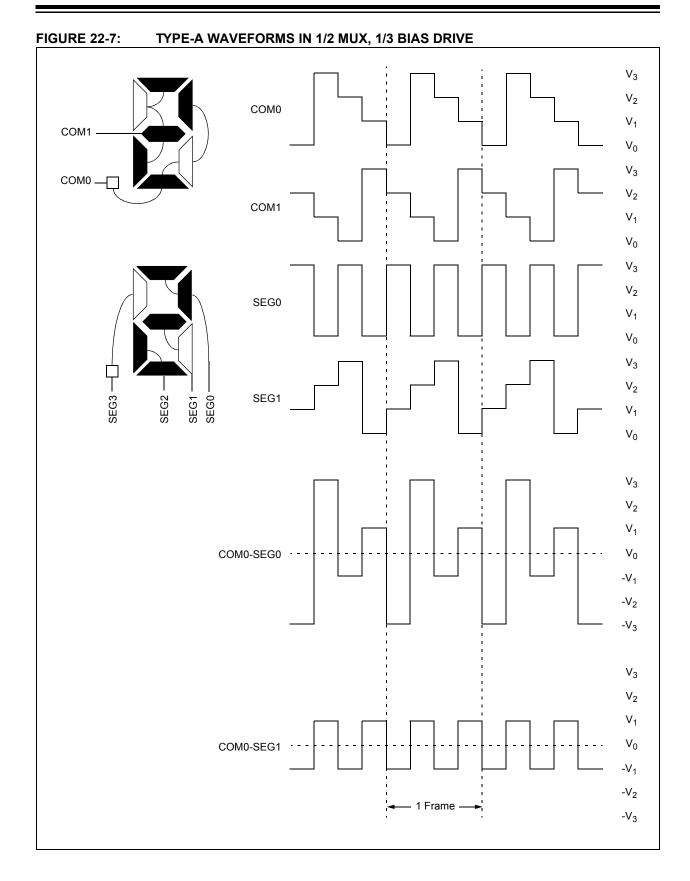

| Number of Pixels the LCD Driver can Drive | 128 (32 SEGs x<br>4 COMs)                                                                                    | 128 (32 SEGs x<br>4 COMs)                                                                                    | 192 (48 SEGs x<br>4 COMs)                                                                                    | 192 (48 SEGs x<br>4 COMs)                                                                                    |

| Timers                                    | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            | 4                                                                                                            |

| Capture/Compare/PWM Modules               | 2                                                                                                            | 2                                                                                                            | 2                                                                                                            | 2                                                                                                            |

| Serial Communications                     | MSSP, AUSART<br>Enhanced USART                                                                               | MSSP, AUSART<br>Enhanced USART                                                                               | MSSP, AUSART<br>Enhanced USART                                                                               | MSSP, AUSART<br>Enhanced USART                                                                               |

| 10-Bit Analog-to-Digital Module           | 12 Input Channels                                                                                            | 12 Input Channels                                                                                            | 12 Input Channels                                                                                            | 12 Input Channels                                                                                            |

| Resets (and Delays)                       | POR, BOR,<br>RESET Instruction,<br>Stack Full,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR (optional),<br>WDT |

| Programmable Low-Voltage Detect           | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |

| Programmable Brown-out Reset              | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          | Yes                                                                                                          |

| Instruction Set                           | 75 Instructions;<br>83 with Extended<br>Instruction Set<br>Enabled                                           |

| Packages                                  | 64-Pin TQFP                                                                                                  | 64-Pin TQFP                                                                                                  | 80-Pin TQFP                                                                                                  | 80-Pin TQFP                                                                                                  |

### TABLE 1-1: DEVICE FEATURES

| Pin Name                | Pin Number                          | Pin      | Buffer       | Description                                                                       |

|-------------------------|-------------------------------------|----------|--------------|-----------------------------------------------------------------------------------|

| Fill Name               | TQFP                                | Туре     | Туре         | Description                                                                       |

|                         |                                     |          |              | PORTD is a bidirectional I/O port.                                                |

| RD0/SEG0<br>RD0<br>SEG0 | 58                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG0 output for LCD.                                              |

| RD1/SEG1<br>RD1<br>SEG1 | 55                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG1 output for LCD.                                              |

| RD2/SEG2<br>RD2<br>SEG2 | 54                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG2 output for LCD.                                              |

| RD3/SEG3<br>RD3<br>SEG3 | 53                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG3 output for LCD.                                              |

| RD4/SEG4<br>RD4<br>SEG4 | 52                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG4 output for LCD.                                              |

| RD5/SEG5<br>RD5<br>SEG5 | 51                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG5 output for LCD.                                              |

| RD6/SEG6<br>RD6<br>SEG6 | 50                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG6 output for LCD.                                              |

| RD7/SEG7<br>RD7<br>SEG7 | 49                                  | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG7 output for LCD.                                              |

|                         | ompatible input<br>tt Trigger input | with C   | MOS leve     | CMOS = CMOS compatible input or output<br>els Analog = Analog input<br>O = Output |

#### **TABLE 1-2:** PIC18F6X90 PINOUT I/O DESCRIPTIONS (CONTINUED)

- Р = Power

- Output

- OD = Open-Drain (no P diode to VDD)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

### 5.3.4 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy three-quarters of Bank 15 (from F40h to FFFh). A list of these registers is given in Table 5-1 and Table 5-2.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their respective chapters, while the ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's.

#### Address Address Name Address Name Name Address Name INDF2<sup>(1)</sup> TOSU FBFh CCPR1H F9Fh IPR1 FFFh FDFh FFEh FDEh POSTINC2<sup>(1)</sup> FBEh CCPR1L F9Eh PIR1 TOSH POSTDEC2<sup>(1)</sup> FFDh TOSL FDDh FBDh CCP1CON F9Dh PIE1 PREINC2<sup>(1)</sup> FFCh STKPTR FDCh FBCh CCPR2H F9Ch MEMCON<sup>(3)</sup> PLUSW2<sup>(1)</sup> OSCTUNE FFBh PCLATU FDBh FBBh CCPR2L F9Bh TRISJ<sup>(3)</sup> FFAh PCLATH FDAh FSR2H FBAh CCP2CON F9Ah \_(2) TRISH(3) FF9h PCL FD9h FSR2L FB9h F99h \_(2) TBLPTRU FF8h FD8h STATUS FB8h F98h TRISG TBLPTRH TMR0H \_\_(2) TRISF FF7h FD7h FB7h F97h \_(2) TBLPTRL TMR0L FF6h FD6h FB6h F96h TRISE FF5h TABLAT FD5h **T0CON** FB5h **CVRCON** F95h TRISD \_(2) FF4h PRODH FD4h FB4h CMCON F94h TRISC PRODL FF3h FD3h OSCCON FB3h TMR3H F93h TRISB FF2h INTCON FD2h HLVDCON FB2h TMR3L F92h TRISA FF1h INTCON2 FD1h WDTCON FB1h T3CON LATJ<sup>(3)</sup> F91h \_\_(2) LATH<sup>(3)</sup> FF0h INTCON3 FD0h RCON FB0h F90h FEFh INDF0<sup>(1)</sup> FCFh TMR1H FAFh SPBRG1 F8Fh LATG POSTINC0<sup>(1)</sup> TMR1L RCREG1 LATF FEEh FCEh FAEh F8Eh POSTDEC0<sup>(1)</sup> FCDh T1CON TXREG1 FEDh FADh F8Dh LATE PREINC0<sup>(1)</sup> TMR2 LATD FECh FCCh TXSTA1 F8Ch FACh PLUSW0<sup>(1)</sup> FEBh FCBh PR2 FABh RCSTA1 F8Bh LATC \_\_(2) FSR0H LATB FEAh FCAh T2CON FAAh F8Ah \_(2) FSR0L SSPBUF LATA FE9h FC9h FA9h F89h \_\_(2) FE8h WREG FC8h SSPADD FA8h F88h PORTJ<sup>(3)</sup> \_(2) FE7h INDF1<sup>(1)</sup> FC7h SSPSTAT FA7h F87h PORTH<sup>(3)</sup> POSTINC1<sup>(1)</sup> \_(2) FE6h FC6h SSPCON1 FA6h F86h PORTG POSTDEC1<sup>(1)</sup> FE5h FC5h SSPCON2 FA5h IPR3 F85h PORTF PREINC1<sup>(1)</sup> FE4h FC4h ADRESH FA4h PIR3 F84h PORTE PLUSW1<sup>(1)</sup> FE3h ADRESL PIE3 PORTD FC3h FA3h F83h FE2h FSR1H FC2h ADCON0 FA2h IPR2 F82h PORTC FE1h FSR1L FC1h ADCON1 FA1h PIR2 F81h PORTB BSR FC0h ADCON2 PIE2 FE0h FA0h F80h PORTA

### TABLE 5-1: SPECIAL FUNCTION REGISTER MAP FOR PIC18F6390/6490/8390/8490 DEVICES

**Note 1:** This is not a physical register.

2: Unimplemented registers are read as '0'.

3: This register is not available on 64-pin devices.

4: This register is implemented but unused on 64-pin devices.

### REGISTER 8-6: PIR3: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 3

| U-0   | R/W-0 | R-0   | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

|       | LCDIF | RC2IF | TX2IF | —   |     | —   | —     |

| bit 7 |       |       |       |     |     |     | bit 0 |

|       |       |       |       |     |     |     |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | LCDIF: LCD Interrupt Flag bit (valid when Type-B waveform with Non-Static mode is selected)                                                      |

|         | <ul> <li>1 = LCD data of all COMs is output (must be cleared in software)</li> <li>0 = LCD data of all COMs is not yet output</li> </ul>         |

| bit 5   | RC2IF: AUSART Receive Interrupt Flag bit                                                                                                         |

|         | <ul> <li>1 = The AUSART receive buffer, RCREG2, is full (cleared when RCREG2 is read)</li> <li>0 = The AUSART receive buffer is empty</li> </ul> |

| bit 4   | TX2IF: AUSART Transmit Interrupt Flag bit                                                                                                        |

|         | 1 = The AUSART transmit buffer, TXREG2, is empty (cleared when TXREG2 is written)                                                                |

|         | 0 = The AUSART transmit buffer is full                                                                                                           |

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                       |

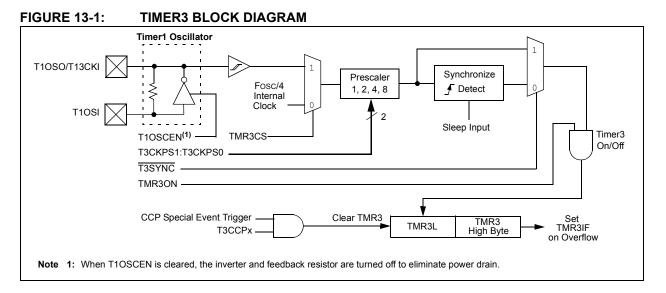

### 13.1 Timer3 Operation

Timer3 can operate in one of three modes:

- Timer

- · Synchronous counter

- Asynchronous counter

The operating mode is determined by the clock select bit, TMR3CS (T3CON<1>). When TMR3CS is cleared (= 0), Timer3 increments on every internal instruction

cycle (Fosc/4). When the bit is set, Timer3 increments on every rising edge of the Timer1 external clock input or the Timer1 oscillator, if enabled.

As with Timer1, the RC1/T1OSI and RC0/T1OSO/T13CKI pins become inputs when the Timer1 oscillator is enabled. This means the values of TRISC<1:0> are ignored and the pins are read as '0'.

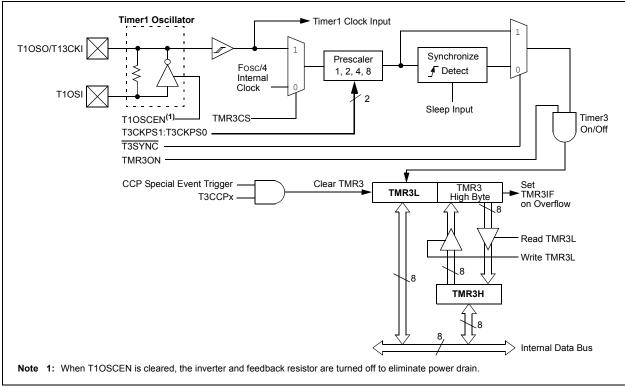

### FIGURE 13-2: TIMER3 BLOCK DIAGRAM (16-BIT READ/WRITE MODE)

| R/W-0         | R/W-0                                                                                                                                                                                    | R/W-0                | R/W-0          | R/W-0                | R/W-0                        | R/W-0                | R/W-0                |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|----------------------|------------------------------|----------------------|----------------------|--|--|

| WCOL          | SSPOV                                                                                                                                                                                    | SSPEN <sup>(1)</sup> | CKP            | SSPM3 <sup>(2)</sup> | SSPM2 <sup>(2)</sup>         | SSPM1 <sup>(2)</sup> | SSPM0 <sup>(2)</sup> |  |  |

| bit 7         |                                                                                                                                                                                          |                      |                |                      |                              |                      | bit (                |  |  |

|               |                                                                                                                                                                                          |                      |                |                      |                              |                      |                      |  |  |

| Legend:       |                                                                                                                                                                                          |                      |                |                      |                              |                      |                      |  |  |

| R = Readabl   |                                                                                                                                                                                          | W = Writable t       | Dit            | -                    | ented bit, read              |                      |                      |  |  |

| -n = Value at | POR                                                                                                                                                                                      | '1' = Bit is set     |                | '0' = Bit is clea    | ared                         | x = Bit is unkr      | IOWN                 |  |  |

| bit 7         | WCOL · Write                                                                                                                                                                             | e Collision Detec    | t bit          |                      |                              |                      |                      |  |  |

|               | In Master Tra                                                                                                                                                                            |                      |                |                      |                              |                      |                      |  |  |

|               |                                                                                                                                                                                          |                      | F register wa  | s attempted wh       | ile the I <sup>2</sup> C cor | nditions were i      | not valid for        |  |  |

|               |                                                                                                                                                                                          |                      |                | eared in softwar     |                              |                      |                      |  |  |

|               | 0 = No collis                                                                                                                                                                            | ion                  |                |                      |                              |                      |                      |  |  |

|               | In Slave Transmit mode:                                                                                                                                                                  |                      |                |                      |                              |                      |                      |  |  |

|               | 1 = The SSPxBUF register is written while it is still transmitting the previous word (must be cleared in                                                                                 |                      |                |                      |                              |                      |                      |  |  |

|               | software)                                                                                                                                                                                |                      |                |                      |                              |                      |                      |  |  |

|               | <ul> <li>0 = No collision</li> <li>In Receive mode (Master or Slave modes):</li> </ul>                                                                                                   |                      |                |                      |                              |                      |                      |  |  |

|               | This is a "dor                                                                                                                                                                           |                      |                | <u>-</u>             |                              |                      |                      |  |  |

| bit 6         | SSPOV: Rec                                                                                                                                                                               | eive Overflow Ir     | ndicator bit   |                      |                              |                      |                      |  |  |

|               | In Receive mode:<br>1 = A byte is received while the SSPxBUF register is still holding the previous byte (must be cleared ir                                                             |                      |                |                      |                              |                      |                      |  |  |

|               | •                                                                                                                                                                                        |                      | the SSPxBUF    | register is still h  | olding the prev              | ious byte (mus       | t be cleared i       |  |  |

|               | software<br>0 = No overf                                                                                                                                                                 | /                    |                |                      |                              |                      |                      |  |  |

|               | In Transmit m                                                                                                                                                                            |                      |                |                      |                              |                      |                      |  |  |

|               |                                                                                                                                                                                          | n't care" bit in Tra | ansmit mode.   |                      |                              |                      |                      |  |  |

| bit 5         |                                                                                                                                                                                          | chronous Serial      |                | <sub>Dit</sub> (1)   |                              |                      |                      |  |  |

|               |                                                                                                                                                                                          |                      |                |                      | CL pins as the               | serial port pins     |                      |  |  |

|               | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as the serial port pins</li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                      |                |                      |                              |                      |                      |  |  |

| bit 4         | CKP: SCK R                                                                                                                                                                               | elease Control b     | oit            |                      |                              |                      |                      |  |  |

|               | In Slave mod                                                                                                                                                                             | e:                   |                |                      |                              |                      |                      |  |  |

|               | 1 = Releases                                                                                                                                                                             |                      |                |                      |                              |                      |                      |  |  |

|               | 0 = Holds clock low (clock stretch), used to ensure data setup time                                                                                                                      |                      |                |                      |                              |                      |                      |  |  |

|               | In Master mo<br>Unused in thi                                                                                                                                                            |                      |                |                      |                              |                      |                      |  |  |

| bit 3-0       |                                                                                                                                                                                          |                      | us Serial Port | Mode Select bit      | <sub>S</sub> (2)             |                      |                      |  |  |

|               |                                                                                                                                                                                          |                      |                | th Start and Stor    |                              | enabled              |                      |  |  |

|               |                                                                                                                                                                                          |                      |                | Start and Stop       |                              |                      |                      |  |  |

|               | 1011 <b>= I<sup>2</sup>C F</b>                                                                                                                                                           | irmware Contro       | lled Master m  | ode (Slave Idle)     |                              |                      |                      |  |  |

|               |                                                                                                                                                                                          |                      |                | * (SSPADD + 1        | ))                           |                      |                      |  |  |

|               |                                                                                                                                                                                          | lave mode, 10-l      |                |                      |                              |                      |                      |  |  |

|               |                                                                                                                                                                                          | lave mode, 7-bi      | 1 1 1 1 1      |                      |                              |                      |                      |  |  |

### REGISTER 15-4: SSPCON1: MSSP CONTROL REGISTER 1 (I<sup>2</sup>C™ MODE)

- **Note 1:** When enabled, the SDA and SCL pins must be configured as inputs.

- 2: Bit combinations not specifically listed here are either reserved or implemented in SPI mode only.

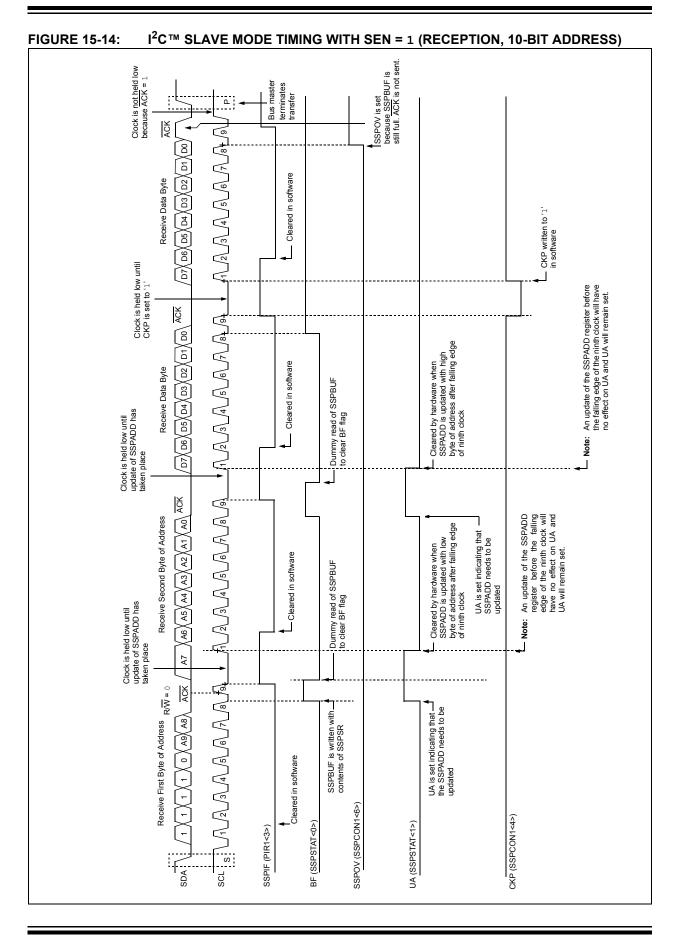

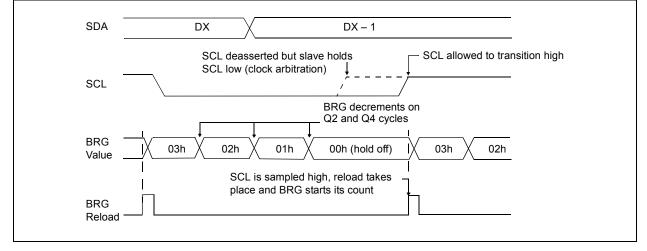

### 15.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 15-18).

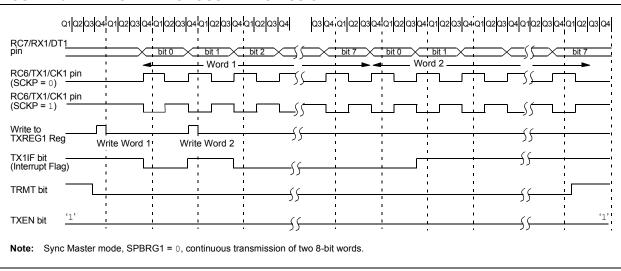

### 16.3 EUSART Synchronous Master Mode

The Synchronous Master mode is entered by setting the CSRC bit (TXSTA<7>). In this mode, the data is transmitted in a half-duplex manner (i.e., transmission and reception do not occur at the same time). When transmitting data, the reception is inhibited and vice versa. Synchronous mode is entered by setting bit, SYNC (TXSTA<4>). In addition, enable bit, SPEN (RCSTA1<7>), is set in order to configure the TX1 and RX1 pins to CK1 (clock) and DT1 (data) lines, respectively.

The Master mode indicates that the processor transmits the master clock on the CK1 line. Clock polarity is selected with the SCKP bit (BAUDCON<4>); setting SCKP sets the Idle state on CK1 as high, while clearing the bit sets the Idle state as low. This option is provided to support Microwire devices with this module.

#### 16.3.1 EUSART SYNCHRONOUS MASTER TRANSMISSION

The EUSART transmitter block diagram is shown in Figure 16-3. The heart of the transmitter is the Transmit (Serial) Shift Register (TSR). The Shift register obtains its data from the Read/Write Transmit Buffer register, TXREG1. The TXREG1 register is loaded with data in software. The TSR register is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from the TXREG1 (if available).

Once the TXREG1 register transfers the data to the TSR register (occurs in one TCYCLE), the TXREG1 is empty and the TX1IF flag bit (PIR1<4>) is set. The interrupt can be enabled or disabled by setting or clearing the interrupt enable bit, TX1IE (PIE1<4>). TX1IF is set regardless of the state of enable bit, TX1IE; it cannot be cleared in software. It will reset only when new data is loaded into the TXREG1 register.

While flag bit, TX1IF, indicates the status of the TXREG1 register, another bit, TRMT (TXSTA<1>), shows the status of the TSR register. TRMT is a read-only bit which is set when the TSR is empty. No interrupt logic is tied to this bit so the user has to poll this bit in order to determine if the TSR register is empty. The TSR is not mapped in data memory so it is not available to the user.

To set up a Synchronous Master Transmission:

- 1. Initialize the SPBRGH1:SPBRG1 registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. If interrupts are desired, set enable bit, TX1IE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREG1 register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

### FIGURE 16-11: SYNCHRONOUS TRANSMISSION

| R/W-0         | U-0                                                                                                                                     | R/W-0                     | R/W-0       | R/W-0                    | R/W-0            | R/W-0           | R/W-0 |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------|--------------------------|------------------|-----------------|-------|

| ADFM          | —                                                                                                                                       | ACQT2                     | ACQT1       | ACQT0                    | ADCS2            | ADCS1           | ADCS0 |

| bit 7         |                                                                                                                                         |                           |             |                          | •                |                 | bit ( |

| Legend:       |                                                                                                                                         |                           |             |                          |                  |                 |       |

| R = Readable  | e bit                                                                                                                                   | W = Writable              | bit         | U = Unimplen             | nented bit, read | d as '0'        |       |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set          |             | '0' = Bit is cle         | ared             | x = Bit is unkr | nown  |

| bit 7         | 1 = Right justi<br>0 = Left justifie                                                                                                    | ed                        |             |                          |                  |                 |       |

| bit 6         | Unimplement                                                                                                                             | ted: Read as '            | )'          |                          |                  |                 |       |

| bit 5-3       | 111 = 20 TAD<br>110 = 16 TAD<br>101 = 12 TAD<br>100 = 8 TAD<br>011 = 6 TAD<br>010 = 4 TAD<br>001 = 2 TAD<br>000 = 0 TAD <sup>(1</sup> ) |                           |             |                          |                  |                 |       |

| bit 2-0       | 111 = FRC (cl<br>110 = FOSC/6<br>101 = FOSC/1<br>100 = FOSC/4                                                                           | 6<br>ock derived fro<br>2 | m A/D RC os | cillator) <sup>(1)</sup> |                  |                 |       |

### **Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

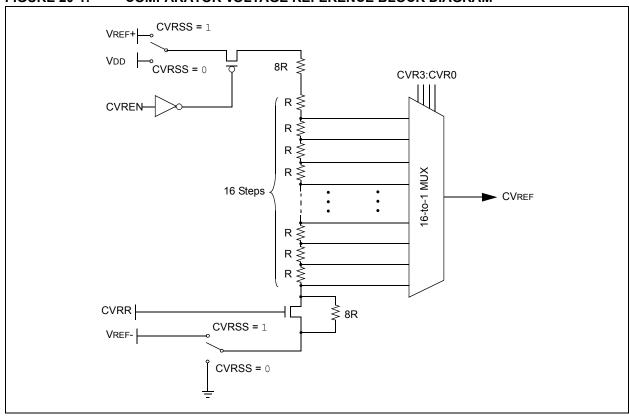

### FIGURE 20-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

### 20.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 20-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

### 20.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

### 20.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>), and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

### 20.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RF5 pin if the TRISF<5> bit and the CVROE bit are both set. Enabling the voltage reference output onto the RF5 pin, with an input signal present, will increase current consumption. Connecting RF5 as a digital output with CVRSS enabled will also increase current consumption.

The RF5 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 20-2 shows an example buffering technique.

NOTES:

### TABLE 24-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                     |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| a               | RAM access bit                                                                                                                                                  |  |  |  |  |  |  |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                     |  |  |  |  |  |  |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                    |  |  |  |  |  |  |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |  |  |  |  |  |  |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |  |  |  |  |  |  |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |  |  |  |  |  |  |

| d               | Destination select bit                                                                                                                                          |  |  |  |  |  |  |

| 1               | d = 0: store result in WREG                                                                                                                                     |  |  |  |  |  |  |

|                 | d = 1: store result in file register f                                                                                                                          |  |  |  |  |  |  |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |  |  |  |  |  |  |

| f               | 8-bit register file address (00h to FFh), or 2-bit FSR designator (0h to 3h).                                                                                   |  |  |  |  |  |  |

| fs              | 12-bit register file address (000h to FFFh). This is the source address.                                                                                        |  |  |  |  |  |  |

| f <sub>d</sub>  | 12-bit register file address (000h to FFFh). This is the destination address.                                                                                   |  |  |  |  |  |  |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |  |  |  |  |  |  |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |  |  |  |  |  |  |

| label           | Label name.                                                                                                                                                     |  |  |  |  |  |  |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.<br>Only used with table read and table write instructions:                     |  |  |  |  |  |  |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |  |  |  |  |  |  |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |  |  |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |  |  |  |  |  |  |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |  |  |  |  |  |  |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                                         |  |  |  |  |  |  |

| 11              | Call/Branch and Return instructions.                                                                                                                            |  |  |  |  |  |  |

| PC              | Program Counter.                                                                                                                                                |  |  |  |  |  |  |

| PCL             | Program Counter Low Byte.                                                                                                                                       |  |  |  |  |  |  |

| PCH             | Program Counter High Byte.                                                                                                                                      |  |  |  |  |  |  |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |  |  |  |  |  |  |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |  |  |  |  |  |  |

| PD              | Power-Down bit.                                                                                                                                                 |  |  |  |  |  |  |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |  |  |  |  |  |  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |  |  |  |  |  |  |

| S               | Fast Call/Return mode select bit                                                                                                                                |  |  |  |  |  |  |

| 1               | s = 0: do not update into/from shadow registers                                                                                                                 |  |  |  |  |  |  |

|                 | s = 1: certain registers loaded into/from shadow registers (Fast mode)                                                                                          |  |  |  |  |  |  |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location).                                                                                                     |  |  |  |  |  |  |

| TABLAT          | 8-bit Table Latch.                                                                                                                                              |  |  |  |  |  |  |

| TO              | Time-out bit.                                                                                                                                                   |  |  |  |  |  |  |

| TOS             | Top-of-Stack.                                                                                                                                                   |  |  |  |  |  |  |

| u               | Unused or unchanged.                                                                                                                                            |  |  |  |  |  |  |

| WDT             | Watchdog Timer.                                                                                                                                                 |  |  |  |  |  |  |

| WREG            | Working register (accumulator).                                                                                                                                 |  |  |  |  |  |  |

| х               | Don't care ('0' or '1'). The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |  |

| Zs              | 7-bit offset value for Indirect Addressing of register files (source).                                                                                          |  |  |  |  |  |  |

| zd              | 7-bit offset value for Indirect Addressing of register files (destination).                                                                                     |  |  |  |  |  |  |

| { }             | Optional argument.                                                                                                                                              |  |  |  |  |  |  |

| [text]          | Indicates an indexed address.                                                                                                                                   |  |  |  |  |  |  |

| (text)          | The contents of text.                                                                                                                                           |  |  |  |  |  |  |

| [expr] <n></n>  | Specifies bit n of the register indicated by the pointer expr.                                                                                                  |  |  |  |  |  |  |

| $\rightarrow$   | Assigned to.                                                                                                                                                    |  |  |  |  |  |  |

| ,<br>< >        | Register bit field.                                                                                                                                             |  |  |  |  |  |  |

|                 | In the set of.                                                                                                                                                  |  |  |  |  |  |  |

| ∈               |                                                                                                                                                                 |  |  |  |  |  |  |

| BCF                                                                      | Bit Clear f                                                                                                                                                                                                                                 | BN                                                                                 | Branch if                                                  | Negative                                                                             |                                               |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------|

| Syntax:                                                                  | BCF                                                                                                                                                                                                                                         | Syntax:                                                                            | BN n                                                       |                                                                                      |                                               |

| Operands:                                                                | $0 \leq f \leq 255$                                                                                                                                                                                                                         | Operands:                                                                          | -128 ≤ n ≤ 1                                               | 27                                                                                   |                                               |

|                                                                          | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                               | Operation:                                                                         | if Negative<br>(PC) + 2 + 2                                |                                                                                      |                                               |

| Operation:                                                               | $0 \rightarrow f \le b >$                                                                                                                                                                                                                   | Status Affected:                                                                   | None                                                       |                                                                                      |                                               |

| Status Affected:                                                         | None                                                                                                                                                                                                                                        | Encoding:                                                                          | 1110                                                       | 0110 nn                                                                              | nn nnnn                                       |

| Encoding:1001bbbaffffffffDescription:Bit 'b' in register 'f' is cleared. |                                                                                                                                                                                                                                             | Description:                                                                       |                                                            | ive bit is '1', t                                                                    |                                               |

| ·                                                                        | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing |                                                                                    | The 2's con<br>added to the<br>incrementer<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the<br>the new addro<br>n. This instruc | e PC will have<br>next<br>ess will be         |

|                                                                          | mode whenever $f \le 95$ (5Fh). See                                                                                                                                                                                                         | Words:                                                                             | 1                                                          |                                                                                      |                                               |

|                                                                          | Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed                                                                                                                                                                   | Cycles:                                                                            | 1(2)                                                       |                                                                                      |                                               |

|                                                                          | Literal Offset Mode" for details.                                                                                                                                                                                                           | Q Cycle Activity:                                                                  |                                                            |                                                                                      |                                               |

| Words:                                                                   | 1                                                                                                                                                                                                                                           | If Jump:                                                                           |                                                            |                                                                                      |                                               |

| Cycles:                                                                  | 1                                                                                                                                                                                                                                           | Q1                                                                                 | Q2                                                         | Q3                                                                                   | Q4                                            |

| Q Cycle Activity:                                                        |                                                                                                                                                                                                                                             | Decode                                                                             | Read literal<br>'n'                                        | Process<br>Data                                                                      | Write to PC                                   |

| Q1                                                                       | Q2 Q3 Q4                                                                                                                                                                                                                                    | No                                                                                 | No                                                         | No                                                                                   | No                                            |

| Decode                                                                   | Read Process Write<br>register 'f' Data register 'f'                                                                                                                                                                                        | operation                                                                          | operation                                                  | operation                                                                            | operation                                     |

|                                                                          |                                                                                                                                                                                                                                             | If No Jump:<br>Q1                                                                  | Q2                                                         | Q3                                                                                   | Q4                                            |

| Example:                                                                 | BCF FLAG REG, 7, 0                                                                                                                                                                                                                          | Decode                                                                             | Read literal                                               | Process                                                                              | No                                            |

| Before Instruc                                                           | =                                                                                                                                                                                                                                           | Dooddo                                                                             | 'n'                                                        | Data                                                                                 | operation                                     |

| FLAG_R<br>After Instruction                                              | EG = C7h<br>on                                                                                                                                                                                                                              | Example:                                                                           | HERE                                                       | BN Jump                                                                              | , <u>, , , , , , , , , , , , , , , , , , </u> |

| FLAG_R                                                                   | EG = 47h                                                                                                                                                                                                                                    | Before Instruct<br>PC<br>After Instruction<br>If Negativ<br>PC<br>If Negativ<br>PC | = ad<br>on<br>ve = 1;<br>= ad<br>ve = 0;                   | dress (HERE)<br>dress (Jump)<br>dress (HERE                                          |                                               |

| BNC          | V                                                                                             | Branch if                                                                | Not Overflo                                                                             | w                                                    | BNZ                                                                                         | Br                                                     |

|--------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Synta        | ax:                                                                                           | BNOV n                                                                   |                                                                                         |                                                      | Syntax:                                                                                     | BN                                                     |

| Oper         | ands:                                                                                         | -128 ≤ n ≤ 1                                                             | 127                                                                                     |                                                      | Operands:                                                                                   | -12                                                    |

| Oper         | ation:                                                                                        | if Overflow<br>(PC) + 2 + 2                                              | ,                                                                                       |                                                      | Operation:                                                                                  | if Z<br>(P0                                            |

| Statu        | is Affected:                                                                                  | None                                                                     |                                                                                         |                                                      | Status Affected:                                                                            | No                                                     |

| Enco         | oding:                                                                                        | 1110                                                                     | 0101 nn:                                                                                | nn nnnn                                              | Encoding:                                                                                   |                                                        |

| Desc         | ription:                                                                                      | program wil<br>The 2's con<br>added to the<br>incremente<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the i<br>the new addre<br>n. This instruct | ber '2n' is<br>e PC will have<br>next<br>ess will be | Description:                                                                                | If th<br>will<br>The<br>add<br>inc<br>ins<br>PC<br>two |

| Word         | ls:                                                                                           | 1                                                                        |                                                                                         |                                                      | Words:                                                                                      | 1                                                      |

| Cycle        | es:                                                                                           | 1(2)                                                                     |                                                                                         |                                                      | Cycles:                                                                                     | 1(2                                                    |

| Q C<br>If Ju | ycle Activity:<br>Imp:                                                                        |                                                                          |                                                                                         |                                                      | Q Cycle Activity:<br>If Jump:                                                               |                                                        |

|              | Q1                                                                                            | Q2                                                                       | Q3                                                                                      | Q4                                                   | Q1                                                                                          |                                                        |

|              | Decode                                                                                        | Read literal<br>'n'                                                      | Process<br>Data                                                                         | Write to PC                                          | Decode                                                                                      | Read                                                   |

|              | No                                                                                            | No                                                                       | No                                                                                      | No                                                   | No                                                                                          |                                                        |

| 16           | operation                                                                                     | operation                                                                | operation                                                                               | operation                                            | operation                                                                                   | оре                                                    |

| If No        | o Jump:                                                                                       | 02                                                                       | 00                                                                                      | 04                                                   | If No Jump:                                                                                 |                                                        |

|              | Q1<br>Decode                                                                                  | Q2<br>Read literal                                                       | Q3<br>Process                                                                           | Q4<br>No                                             | Q1<br>Decode                                                                                | Read                                                   |

|              | Decode                                                                                        | 'n'                                                                      | Data                                                                                    | operation                                            | Decode                                                                                      | Read                                                   |

|              | nple:<br>Before Instruct<br>PC<br>After Instruction<br>If Overflot<br>PC<br>If Overflot<br>PC | = adv<br>on<br>ow = 0;<br>= adv<br>ow = 1;                               | BNOV Jump<br>dress (HERE<br>dress (Jump<br>dress (HERE                                  | )                                                    | Example:<br>Before Instruc<br>PC<br>After Instructi<br>If Zero<br>PC<br>If Zero<br>PC<br>PC | on                                                     |

| BNZ          | 2                      | Branch if                                                 | Branch if Not Zero                                                                                                                                                                                                         |            |                |  |  |  |  |

|--------------|------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|--|--|--|--|

| Synta        | ax:                    | BNZ n                                                     | BNZ n                                                                                                                                                                                                                      |            |                |  |  |  |  |

| Oper         | ands:                  | -128 ≤ n ≤ ′                                              | $-128 \le n \le 127$                                                                                                                                                                                                       |            |                |  |  |  |  |

| Oper         | ation:                 | if Zero bit is<br>(PC) + 2 + 2                            | ,                                                                                                                                                                                                                          | ;          |                |  |  |  |  |

| Statu        | is Affected:           | None                                                      | None                                                                                                                                                                                                                       |            |                |  |  |  |  |