Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6390-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.6 Reset State of Registers

Most registers are unaffected by a Reset. Their status is unknown on POR and unchanged by all other Resets. The other registers are forced to a "Reset state" depending on the type of Reset that occurred.

Most registers are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. Status bits from the RCON register,  $\overline{RI}$ ,  $\overline{TO}$ ,  $\overline{PD}$ ,  $\overline{POR}$  and  $\overline{BOR}$ , are set or cleared differently in different Reset situations, as indicated in Table 4-3. These bits are used in software to determine the nature of the Reset.

Table 4-4 describes the Reset states for all of the Special Function Registers. These are categorized by Power-on and Brown-out Resets, Master Clear and WDT Resets and WDT wake-ups.

| TABLE 4-3: | STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR |

|------------|----------------------------------------------------------------------|

|            | RCON REGISTER                                                        |

| Condition                                                   | Program               |                  | RCC | N Reg | jister |     |     | STKPTR Register |        |  |

|-------------------------------------------------------------|-----------------------|------------------|-----|-------|--------|-----|-----|-----------------|--------|--|

| Condition                                                   | Counter               | SBOREN           | RI  | то    | PD     | POR | BOR | STKFUL          | STKUNF |  |

| Power-on Reset                                              | 0000h                 | 1                | 1   | 1     | 1      | 0   | 0   | 0               | 0      |  |

| RESET Instruction                                           | 0000h                 | u <b>(2)</b>     | 0   | u     | u      | u   | u   | u               | u      |  |

| Brown-out Reset                                             | 0000h                 | u <b>(2)</b>     | 1   | 1     | 1      | u   | 0   | u               | u      |  |

| MCLR Reset during power-managed Run modes                   | 0000h                 | <sub>ບ</sub> (2) | u   | 1     | u      | u   | u   | u               | u      |  |

| MCLR Reset during<br>power-managed Idle modes and<br>Sleep  | 0000h                 | u <b>(2)</b>     | u   | 1     | 0      | u   | u   | u               | u      |  |

| WDT time-out during full power or power-managed Run modes   | 0000h                 | u <b>(2)</b>     | u   | 0     | u      | u   | u   | u               | u      |  |

| MCLR during full-power execution                            | 0000h                 | <sub>ບ</sub> (2) | u   | u     | u      | u   | u   | u               | u      |  |

| Stack Full Reset (STVREN = 1)                               | 0000h                 | u <b>(2)</b>     | u   | u     | u      | u   | u   | 1               | u      |  |

| Stack Underflow Reset<br>(STVREN = 1)                       | 0000h                 | <sub>ບ</sub> (2) | u   | u     | u      | u   | u   | u               | 1      |  |

| Stack Underflow Error (not an actual Reset, STVREN = 0)     | 0000h                 | u <b>(2)</b>     | u   | u     | u      | u   | u   | u               | 1      |  |

| WDT time-out during<br>power-managed Idle or<br>Sleep modes | PC + 2 <sup>(1)</sup> | u <b>(2)</b>     | u   | 0     | 0      | u   | u   | u               | u      |  |

| Interrupt exit from<br>power-managed modes                  | PC + 2 <sup>(1)</sup> | <sub>ປ</sub> (2) | u   | u     | 0      | u   | u   | u               | u      |  |

**Legend:** u = unchanged

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (008h or 0018h).

2: Reset state is '1' for POR and unchanged for all other Resets when software BOR is enabled (BOREN1:BOREN0 Configuration bits = 01 and SBOREN = 1); otherwise, the Reset state is '0'.

## 5.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds five additional two-word commands to the existing PIC18 instruction set: ADDFSR, CALLW, MOVSF, MOVSS and SUBFSR. These instructions are executed as described in Section 5.2.4 "Two-Word Instructions".

# 5.6 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space. This mode also alters the behavior of Indirect Addressing using FSR2 and its associated operands.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect Addressing with FSR0 and FSR1 also remains unchanged.

#### 5.6.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of Indirect Addressing using the FSR2 register pair and its associated file operands. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of Indexed Addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode. When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0); and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in Direct Addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

### 5.6.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use Direct Addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 5-8.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 24.2.1** "Extended Instruction Syntax".

# 6.0 FLASH PROGRAM MEMORY

In PIC18F6390/6490/8390/8490 devices, the program memory is implemented as read-only Flash memory. It is readable over the entire VDD range during normal operation. A read from program memory is executed on one byte at a time.

# 6.1 Table Reads

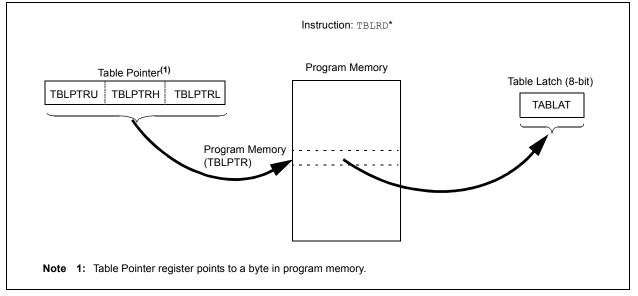

For PIC18 devices, there are two operations that allow the processor to move bytes between the program memory space and the data RAM: table read (TBLRD) and table write (TBLWT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 6-1 shows the operation of a table read with program memory and data RAM.

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register, TABLAT.

FIGURE 6-1: TABLE READ OPERATION

Table reads work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address.

Because the program memory cannot be written to or erased under normal operation, the TBLWT operation is not discussed here.

- Note 1: Although it cannot be used in PIC18F6390/6490/8390/8490 devices in normal operation, the TBLWT instruction is still implemented in the instruction set. Executing the instruction takes two instruction cycles, but effectively results in a NOP.

- The TBLWT instruction is available only in programming modes and is used during In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 9.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 9-5). The pins have Schmitt Trigger input buffers. RC1 is normally configured by Configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings. Note: On a Power-on Reset, these pins are configured as digital inputs.

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

RC2 and RC5 are also multiplexed with LCD segment drives controlled by bits in the LCDSE1 register. I/O port functions are only available when the segments are disabled.

### EXAMPLE 9-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by ; clearing output |

|-------|-------|-----------------------------------------|

|       |       | ; data latches                          |

| CLRF  | LATC  | ; Alternate method                      |

|       |       | ; to clear output                       |

|       |       | ; data latches                          |

| MOVLW | OCFh  | ; Value used to                         |

|       |       | ; initialize data                       |

|       |       | ; direction                             |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                 |

|       |       | ; RC<5:4> as outputs                    |

|       |       | ; RC<7:6> as inputs                     |

|       |       |                                         |

NOTES:

### 14.4.3 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP2 module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR2L register and CCP2CON<5:4> bits.

- 3. Make the CCP2 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP2 module for PWM operation.

| Name    | Bit 7                                      | Bit 6          | Bit 5          | Bit 4     | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on Page |

|---------|--------------------------------------------|----------------|----------------|-----------|----------|--------|---------|---------|----------------------------|

| INTCON  | GIE/GIEH                                   | PEIE/GIEL      | TMR0IE         | INT0IE    | RBIE     | TMR0IF | INT0IF  | RBIF    | 59                         |

| RCON    | IPEN                                       | SBOREN         | —              | RI        | TO       | PD     | POR     | BOR     | 60                         |

| PIR1    | _                                          | ADIF           | RC1IF          | TX1IF     | SSPIF    | CCP1IF | TMR2IF  | TMR1IF  | 61                         |

| PIE1    | _                                          | ADIE           | RC1IE          | TX1IE     | SSPIE    | CCP1IE | TMR2IE  | TMR1IE  | 61                         |

| IPR1    | _                                          | ADIP           | RC1IP          | TX1IP     | SSPIP    | CCP1IP | TMR2IP  | TMR1IP  | 61                         |

| TRISC   | PORTC Da                                   | ta Direction   | Register       |           |          |        |         |         | 62                         |

| TRISE   | PORTE Da                                   | ta Direction I | Register       |           |          |        | _       | —       | 62                         |

| TMR2    | Timer2 Reg                                 | gister         |                |           |          |        |         |         | 60                         |

| PR2     | Timer2 Per                                 | iod Register   |                |           |          |        |         |         | 60                         |

| T2CON   | _                                          | T2OUTPS3       | T2OUTPS2       | T2OUTPS1  | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 60                         |

| CCPR1L  | Capture/Co                                 | mpare/PWN      | I Register 1 L | _ow Byte  |          |        |         |         | 61                         |

| CCPR1H  | Capture/Co                                 | mpare/PWN      | I Register 1 I | ligh Byte |          |        |         |         | 61                         |

| CCP1CON | _                                          | _              | DC1B1          | DC1B0     | CCP1M3   | CCP1M2 | CCP1M1  | CCP1M0  | 61                         |

| CCPR2L  | 2L Capture/Compare/PWM Register 2 Low Byte |                |                |           |          |        |         |         | 61                         |

| CCPR2H  | Capture/Compare/PWM Register 2 High Byte   |                |                |           |          |        |         | 61      |                            |

| CCP2CON | _                                          | _              | DC2B1          | DC2B0     | CCP2M3   | CCP2M2 | CCP2M1  | CCP2M0  | 61                         |

#### TABLE 14-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PWM or Timer2.

| R/W-0        | R/W-0                                             | R/W-0                                  | R/W-0                | R/W-0                | R/W-0                | R/W-0               | R/W-0              |

|--------------|---------------------------------------------------|----------------------------------------|----------------------|----------------------|----------------------|---------------------|--------------------|

| GCEN         | ACKSTAT                                           | ACKDT <sup>(1)</sup>                   | ACKEN <sup>(2)</sup> | RCEN <sup>(2)</sup>  | PEN <sup>(2)</sup>   | RSEN <sup>(2)</sup> | SEN <sup>(2)</sup> |

| bit 7        |                                                   |                                        |                      |                      |                      |                     | bit                |

| Legend:      |                                                   |                                        |                      |                      |                      |                     |                    |

| R = Readab   | le bit                                            | W = Writable                           | bit                  | U = Unimplem         | ented bit, read      | d as '0'            |                    |

| -n = Value a | t POR                                             | '1' = Bit is set                       |                      | '0' = Bit is clea    | ared                 | x = Bit is unkn     | own                |

| bit 7        | GCEN: Gene                                        | eral Call Enable                       | bit (Slave mod       | le only)             |                      |                     |                    |

|              |                                                   | terrupt when a call address dis        |                      | ldress (0000h) i     | s received in t      | he SSPSR            |                    |

| bit 6        | ACKSTAT: A                                        | cknowledge Sta                         | atus bit (Master     | r Transmit mode      | e only)              |                     |                    |

|              |                                                   | edge was not re<br>edge was receiv     |                      | ave                  |                      |                     |                    |

| bit 5        | ACKDT: Ack                                        | nowledge Data                          | bit (Master Re       | ceive mode only      | y) <sup>(1)</sup>    |                     |                    |

|              | 1 = Not Ackn                                      | •                                      |                      |                      |                      |                     |                    |

|              | 0 = Acknowle                                      | •                                      |                      |                      |                      | . (2)               |                    |

| bit 4        |                                                   |                                        |                      | bit (Master Rece     |                      |                     | <b>A</b> 1         |

|              |                                                   | cknowledge se<br>by hardware.          | quence on SD/        | A and SCL pins       | and transmit A       | ACKDT data bit.     | Automatica         |

|              |                                                   | edge sequence                          | Idle                 |                      |                      |                     |                    |

| bit 3        | RCEN: Rece                                        | ive Enable bit (                       | Master mode c        | only) <sup>(2)</sup> |                      |                     |                    |

|              | 1 = Enables I                                     | Receive mode f                         | or I <sup>2</sup> C  |                      |                      |                     |                    |

|              | 0 = Receive                                       |                                        |                      |                      |                      |                     |                    |

| bit 2        |                                                   | ondition Enable                        |                      |                      |                      |                     |                    |

|              | 1 = Initiate St<br>0 = Stop cone                  |                                        | SDA and SCL          | _ pins. Automati     | cally cleared b      | by hardware.        |                    |

| bit 1        | RSEN: Repe                                        | ated Start Cond                        | lition Enable bi     | it (Master mode      | only) <sup>(2)</sup> |                     |                    |

|              |                                                   | Repeated Start of<br>d Start condition |                      | DA and SCL pin       | s. Automatical       | ly cleared by ha    | ardware.           |

| bit 0        | SEN: Start C                                      | ondition Enable                        | Stretch Enabl        | e bit <sup>(2)</sup> |                      |                     |                    |

|              | In Master mo<br>1 = Initiate St<br>0 = Start con  | art condition or                       | SDA and SCL          | ₋ pins. Automati     | cally cleared b      | by hardware.        |                    |

|              | In Slave mod                                      | <u>e:</u>                              |                      | ve transmit and      | slave receive        | (stretch enable     | d)                 |

|              | /alue that will be<br>the I <sup>2</sup> C module |                                        |                      |                      |                      |                     |                    |

If the I<sup>2</sup>C module is not in the Idle mode, these bits may not be set (no spooling) and the SSPBUF may n be written (or writes to the SSPBUF are disabled).

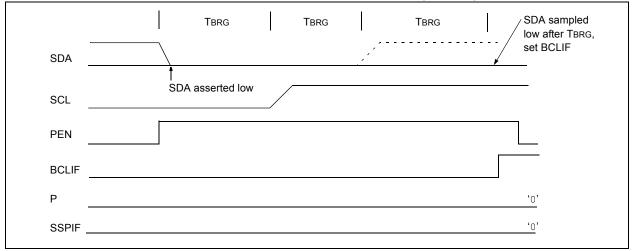

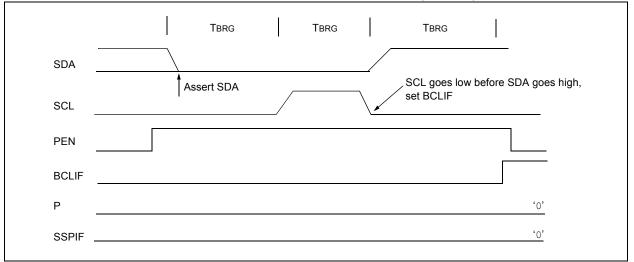

#### 15.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- a) After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD<6:0> and counts down to 0. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 15-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 15-32).

#### FIGURE 15-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 15-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 17.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is very similar in function to the Enhanced USART module, discussed in the previous chapter. It is provided as an additional channel for serial communication, with external devices, for those situations that do not require Auto-Baud Detection or LIN bus support.

The AUSART can be configured in the following modes:

- Asynchronous (full-duplex)

- Synchronous Master (half-duplex)

- Synchronous Slave (half-duplex)

The pins of the AUSART module are multiplexed with the functions of PORTG (RG1/TX2/CK2/SEG29 and RG2/RX2/DT2/SEG28, respectively). In order to configure these pins as an AUSART:

- SPEN bit (RCSTA2<7>) must be set (= 1)

- TRISG<2> bit must be set (= 1)

- TRISG<1> bit must be cleared (= 0) for Asynchronous and Synchronous Master modes

- TRISG<1> bit must be set (= 1) for Synchronous Slave mode

Note: The AUSART control will automatically reconfigure the pin from input to output as needed.

The operation of the Addressable USART module is controlled through two registers, TXSTA2 and RXSTA2. These are detailed in Register 17-1 and Register 17-2 respectively.

# 21.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

PIC18F6390/6490/8390/8490 devices have a High/Low-Voltage Detect module (HLVD). This is a programmable circuit that allows the user to specify both a device voltage trip point and the direction of change from that point. If the device experiences an excursion past the trip point in that direction, an interrupt flag is set. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt. The High/Low-Voltage Detect Control register (Register 21-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

The block diagram for the HLVD module is shown in Figure 21-1.

### REGISTER 21-1: HLVDCON: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER

| R/W-0         | U-0                         | R-0              | R/W-0            | R/W-0                 | R/W-1                 | R/W-0                 | R/W-1                 |

|---------------|-----------------------------|------------------|------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| VDIRMAG       | —                           | IRVST            | HLVDEN           | HLVDL3 <sup>(1)</sup> | HLVDL2 <sup>(1)</sup> | HLVDL1 <sup>(1)</sup> | HLVDL0 <sup>(1)</sup> |

| bit 7         |                             |                  |                  |                       |                       |                       | bit 0                 |

| Legend:       |                             |                  |                  |                       |                       |                       |                       |

| R = Readabl   | e bit                       | W = Writable     | bit              | U = Unimplem          | nented bit, read      | d as '0'              |                       |

| -n = Value at | POR                         | '1' = Bit is set |                  | '0' = Bit is clea     |                       | x = Bit is unkr       | iown                  |

|               |                             |                  |                  |                       |                       |                       |                       |

| bit 7         |                             | /oltage Directio | -                |                       |                       |                       |                       |

|               |                             |                  | •                | xceeds trip poir      | •                     | ,                     |                       |

| bit 6         |                             | nted: Read as '  | •                | alls below trip p     | oint (HLVDL3:F        | HLVDLU)               |                       |

| bit 5         | -                           | nal Reference V  |                  | -log bit              |                       |                       |                       |

| DIL D         |                             |                  | •                | will generate the     | intorrunt flag        | at the energified     | voltago rango         |

|               |                             |                  |                  | will not genera       |                       |                       |                       |

|               |                             | nd the HLVD int  |                  |                       |                       |                       |                       |

| bit 4         | HLVDEN: Hi                  | gh/Low-Voltage   | Detect Power     | Enable bit            |                       |                       |                       |

|               | 1 = HLVD en                 |                  |                  |                       |                       |                       |                       |

|               | 0 = HLVD dis                |                  |                  | (1)                   |                       |                       |                       |

| bit 3-0       |                             | VDL0: Voltage I  |                  |                       |                       |                       |                       |

|               | 1111 = Exten<br>1110 = 4.41 |                  | ut is used (inpu | t comes from th       | ie HLVDIN pin)        | )                     |                       |

|               | 1101 = 4.41<br>1101 = 4.11  |                  |                  |                       |                       |                       |                       |

|               | 1100 = 3.92                 |                  |                  |                       |                       |                       |                       |

|               | 1011 = 3.72                 |                  |                  |                       |                       |                       |                       |

|               | 1010 <b>= 3.53</b>          | V-3.91V          |                  |                       |                       |                       |                       |

|               | 1001 = 3.43                 |                  |                  |                       |                       |                       |                       |

|               | 1000 = 3.24                 |                  |                  |                       |                       |                       |                       |

|               | 0111 = 2.95<br>0110 = 2.75  |                  |                  |                       |                       |                       |                       |

|               | 0110 = 2.75                 |                  |                  |                       |                       |                       |                       |

|               | 0100 = 2.43                 |                  |                  |                       |                       |                       |                       |

|               | 0011 = 2.35                 |                  |                  |                       |                       |                       |                       |

|               | 0010 <b>= 2.16</b>          | V-2.38V          |                  |                       |                       |                       |                       |

|               | 0001 <b>= 1.96</b>          |                  |                  |                       |                       |                       |                       |

|               | 0000 <b>= Rese</b>          | erved            |                  |                       |                       |                       |                       |

**Note 1:** HLVDL3:HLVDL0 modes that result in a trip point below the valid operating voltage of the device are not tested.

### TABLE 24-2: PIC18FXXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | Qualas     | 16-E | Bit Instr | uction V | Vord | Status          | Natas           |  |

|-----------------------|---------------------------------|------------------------------------------|------------|------|-----------|----------|------|-----------------|-----------------|--|

|                       |                                 | Description                              | Cycles     | MSb  |           |          | LSb  | Affected        | Notes           |  |

| BYTE-ORI              | BYTE-ORIENTED OPERATIONS        |                                          |            |      |           |          |      |                 |                 |  |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2            |  |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010 | 00da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2            |  |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001 | 01da      | ffff     | ffff |                 | 1,2             |  |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110 | 101a      | ffff     | ffff | Z               | 2               |  |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001 | 11da      | ffff     |      | Z, N            | 1, 2            |  |

| CPFSEQ                | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3) | 0110 | 001a      | ffff     | ffff | None            | 4               |  |

| CPFSGT                | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3) | 0110 | 010a      | ffff     | ffff | None            | 4               |  |

| CPFSLT                | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3) | 0110 | 000a      | ffff     | ffff | None            | 1, 2            |  |

| DECF                  | f, d, a                         | Decrement f                              | 1          | 0000 | 01da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4      |  |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010 | 11da      | ffff     | ffff | None            | 1, 2, 3, 4      |  |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0               | 1 (2 or 3) |      | 11da      | ffff     | ffff | None            | 1, 2            |  |

| INCF                  | f, d, a                         | Increment f                              | 1 ΄        | 0010 | 10da      | ffff     | ffff | C, DC, Z, OV, N | 1, 2, 3, 4      |  |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011 | 11da      | ffff     |      | None            | 4               |  |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100 | 10da      | ffff     | ffff | None            | 1, 2            |  |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1 ΄        | 0001 | 00da      | ffff     | ffff | Z, N            | 1, 2            |  |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101 | 00da      | ffff     | ffff | Z, N            | 1               |  |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100 | ffff      | ffff     | ffff |                 |                 |  |

|                       | 3, u                            | f <sub>d</sub> (destination) 2nd word    |            | 1111 | ffff      | ffff     | ffff |                 |                 |  |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110 | 111a      | ffff     | ffff | None            |                 |  |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000 | 001a      | ffff     | ffff | None            | 1, 2            |  |

| NEGF                  | f, a                            | Negate f                                 | 1          |      | 110a      | ffff     |      | C, DC, Z, OV, N |                 |  |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011 | 01da      | ffff     |      | C, Z, N         | 1, 2            |  |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100 | 01da      | ffff     | ffff |                 | ,               |  |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011 | 00da      | ffff     |      | Ć, Z, N         |                 |  |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100 | 00da      | ffff     | ffff |                 |                 |  |

| SETF                  | f, a                            | Set f                                    | 1          | 0110 | 100a      | ffff     | ffff |                 | 1, 2            |  |

| SUBFWB                | f, d, a                         | Subtract f from WREG with                | 1          | 0101 | 01da      | ffff     |      | C, DC, Z, OV, N | -, _            |  |

|                       | , - ,                           | Borrow                                   |            |      |           | -        | _    | , _, ,, _       |                 |  |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101 | 11da      | ffff     | ffff | C, DC, Z, OV, N | 1.2             |  |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                | 1          | 0101 |           | ffff     |      | C, DC, Z, OV, N | , =             |  |

|                       | ·,, •                           | Borrow                                   |            |      |           |          |      | ,,,,,           |                 |  |

| SWAPF                 | f, d, a                         | Swap Nibbles in f                        | 1          | 0011 | 10da      | ffff     | ffff | None            | 4               |  |

| TSTFSZ                | f, a, a<br>f, a                 | Test f, Skip if 0                        | 1 (2 or 3) | 0110 | 011a      | ffff     |      | None            | 1, 2            |  |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1          |      | 10da      | ffff     | ffff |                 | ·, <del>-</del> |  |

|                       | i, u, a                         |                                          |            | 0001 | roua      |          |      | <u> </u>        |                 |  |

**Note 1:** When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as an input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, 'd' = 1), the prescaler will be cleared if assigned.

**3:** If the Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| IORLW               | IORLW Inclusive OR Literal with W     |                 |      |            |  |  |  |  |

|---------------------|---------------------------------------|-----------------|------|------------|--|--|--|--|

| Syntax:             | IORLW k                               | IORLW k         |      |            |  |  |  |  |

| Operands:           | $0 \le k \le 255$                     |                 |      |            |  |  |  |  |

| Operation:          | (W) .OR. k                            | $\rightarrow W$ |      |            |  |  |  |  |

| Status Affected:    | N, Z                                  |                 |      |            |  |  |  |  |

| Encoding:           | 0000                                  | 1001            | kkkl | k kkkk     |  |  |  |  |

| Description:        | The conten<br>eight-bit lite<br>in W. |                 |      |            |  |  |  |  |

| Words:              | 1                                     | 1               |      |            |  |  |  |  |

| Cycles:             | 1                                     |                 |      |            |  |  |  |  |

| Q Cycle Activity:   |                                       |                 |      |            |  |  |  |  |

| Q1                  | Q2                                    | Q3              |      | Q4         |  |  |  |  |

| Decode              | Read<br>literal 'k'                   | Proce<br>Data   |      | Write to W |  |  |  |  |

| Example:            | IORLW                                 | 35h             |      |            |  |  |  |  |

| Before Instruc<br>W | tion<br>= 9Ah                         |                 |      |            |  |  |  |  |

| IORWF             | Inclusive                                                                                                                                                                                                                | OR W v                                                                                                                   | vith f                                                                                                        |                                                                                                                                       |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:           | IORWF f                                                                                                                                                                                                                  | {,d {,a}}                                                                                                                |                                                                                                               |                                                                                                                                       |

| Operands:         | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                       |                                                                                                                          |                                                                                                               |                                                                                                                                       |

| Operation:        | (W) .OR. (f)                                                                                                                                                                                                             | $\rightarrow$ dest                                                                                                       |                                                                                                               |                                                                                                                                       |

| Status Affected:  | N, Z                                                                                                                                                                                                                     |                                                                                                                          |                                                                                                               |                                                                                                                                       |

| Encoding:         | 0001                                                                                                                                                                                                                     | 00da                                                                                                                     | ffff                                                                                                          | ffff                                                                                                                                  |

| Description:      | Inclusive O<br>'0', the result is<br>(default).<br>If 'a' is '0', the<br>If 'a' is '1', the<br>GPR bank.<br>If 'a' is '0' a<br>set is enable<br>in Indexed I<br>mode when<br>Section 24<br>Bit-Orienter<br>Literal Offer | It is placed by<br>placed by<br>the Access<br>he BSR i<br>ed, this i<br>Literal Of<br>ever f ≤ c<br>.2.3 "By<br>d Instru | ed in W.<br>back in ro<br>ss Bank i<br>s used to<br>structio<br>fset Add<br>95 (5Fh)<br>te-Orien<br>ctions in | If 'd' is '1',<br>egister 'f'<br>s selected.<br>o select the<br>instruction<br>n operates<br>ressing<br>. See<br>ted and<br>n Indexed |

| Words:            | 1                                                                                                                                                                                                                        |                                                                                                                          |                                                                                                               |                                                                                                                                       |

| Cycles:           | 1                                                                                                                                                                                                                        |                                                                                                                          |                                                                                                               |                                                                                                                                       |

| Q Cycle Activity: |                                                                                                                                                                                                                          |                                                                                                                          |                                                                                                               |                                                                                                                                       |

| Q1                | Q2                                                                                                                                                                                                                       | Q3                                                                                                                       |                                                                                                               | Q4                                                                                                                                    |

| Decode            | Read<br>register 'f'                                                                                                                                                                                                     | Proce<br>Data                                                                                                            |                                                                                                               | Write to estination                                                                                                                   |

| Example:          | IORWF RI                                                                                                                                                                                                                 | ESULT,                                                                                                                   | 0, 1                                                                                                          |                                                                                                                                       |

| ampic.           | 10   | T/AAT. |

|------------------|------|--------|

| Before Instruct  | tion |        |

| RESULT           | =    | 13h    |

| W                | =    | 91h    |

| After Instructio | 'n   |        |

| RESULT           | =    | 13h    |

| W                | =    | 93h    |

W = 9 After Instruction

W = BFh

| РОР                               | Рор Тор                                                               | of Return S                                           | tack                                                                           |

|-----------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|

| Syntax:                           | POP                                                                   |                                                       |                                                                                |

| Operands:                         | None                                                                  |                                                       |                                                                                |

| Operation:                        | $(TOS) \rightarrow b$                                                 | it bucket                                             |                                                                                |

| Status Affected:                  | None                                                                  |                                                       |                                                                                |

| Encoding:                         | 0000                                                                  | 0000 00                                               | 00 0110                                                                        |

| Description:                      | stack and i<br>then becon<br>was pushe<br>This instruc<br>the user to | nes the previo<br>d onto the retu<br>ction is provide | The TOS value<br>us value that<br>urn stack.<br>ed to enable<br>age the return |

| Words:                            | 1                                                                     |                                                       |                                                                                |

| Cycles:                           | 1                                                                     |                                                       |                                                                                |

| Q Cycle Activity:                 |                                                                       |                                                       |                                                                                |

| Q1                                | Q2                                                                    | Q3                                                    | Q4                                                                             |

| Decode                            | No<br>operation                                                       | POP TOS<br>value                                      | No<br>operation                                                                |

| Example:                          | POP<br>GOTO                                                           | NEW                                                   |                                                                                |

| Before Instruc<br>TOS<br>Stack (1 | ction<br>level down)                                                  | = 0031/<br>= 01433                                    |                                                                                |

| After Instructi<br>TOS<br>PC      | on                                                                    | = 01433<br>= NEW                                      | 32h                                                                            |

| PUSH                                    | Push Top                                    | Push Top of Return Stack   |                 |      |               |  |  |

|-----------------------------------------|---------------------------------------------|----------------------------|-----------------|------|---------------|--|--|

| Syntax:                                 | PUSH                                        | PUSH                       |                 |      |               |  |  |

| Operands:                               | None                                        |                            |                 |      |               |  |  |

| Operation:                              | $({\rm PC} + 2) \rightarrow$                | $(PC + 2) \rightarrow TOS$ |                 |      |               |  |  |

| Status Affected:                        | None                                        |                            |                 |      |               |  |  |

| Encoding:                               | 0000                                        | 0000                       | 000             | 0    | 0101          |  |  |

| Description:                            | The PC + 2<br>the return s<br>value is pus  | tack. T                    | he prev         | ious | TOS           |  |  |

|                                         | This instruc<br>software sta<br>then pushin | ack by                     | modifyir        | ng T | OS and        |  |  |

| Words:                                  | 1                                           |                            |                 |      |               |  |  |

| Cycles:                                 | 1                                           |                            |                 |      |               |  |  |

| Q Cycle Activity:                       |                                             |                            |                 |      |               |  |  |

| Q1                                      | Q2                                          | Q3                         |                 |      | Q4            |  |  |

| Decode                                  | PUSH<br>PC + 2 onto<br>return stack         | -                          | No<br>operation |      | No<br>eration |  |  |

|                                         |                                             |                            |                 |      |               |  |  |

| Example:                                | PUSH                                        |                            |                 |      |               |  |  |

| Example:<br>Before Instruc<br>TOS<br>PC |                                             | =<br>=                     | 345Ah<br>0124h  |      |               |  |  |

#### 24.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

| Note: | Enabling  | the    | PIC18       | instruction   | set  |

|-------|-----------|--------|-------------|---------------|------|

|       | extension | may    | cause leg   | gacy applicat | ions |

|       | to behave | errati | cally or fa | ail entirely. |      |

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing mode (Section 5.6.1 "Indexed Addressing With Literal Offset"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank (a = 0), or in a GPR bank designated by the BSR (a = 1). When the extended instruction set is enabled and a = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bit-oriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between 'C' and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 24.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset Addressing mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind that, when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset Addressing mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

### 24.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument, 'f', in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value, 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within brackets, will generate an error in the MPASM<sup>™</sup> Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled) when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument, 'd', functions as before.

In the latest versions of the MPASM Assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option,  $/_{y}$ , or the PE directive in the source listing.

### 24.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18FXX90, it is very important to consider the type of code. A large, reentrant application that is written in 'C' and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

## 26.3 DC Characteristics: PIC18F6390/6490/8390/8490 (Industrial) PIC18LF6390/6490/8390/8490 (Industrial)

| DC CHA       | ARACTE | RISTICS                                    | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                    |        |                                                                                                                             |  |

|--------------|--------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                             | Min                                                                                                                                 | Мах                | Units  | Conditions                                                                                                                  |  |

|              | VIL    | Input Low Voltage                          |                                                                                                                                     |                    |        |                                                                                                                             |  |

|              |        | I/O Ports:                                 |                                                                                                                                     |                    |        |                                                                                                                             |  |

| D030         |        | with TTL Buffer                            | Vss                                                                                                                                 | 0.15 Vdd           | V      | VDD < 4.5V                                                                                                                  |  |

| D030A        |        |                                            | —                                                                                                                                   | 0.8                | V      | $4.5V \le V\text{DD} \le 5.5V$                                                                                              |  |

| D031         |        | with Schmitt Trigger Buffer<br>RC3 and RC4 | Vss<br>Vss                                                                                                                          | 0.2 Vdd<br>0.3 Vdd | V<br>V |                                                                                                                             |  |

| D032         |        | MCLR                                       | Vss                                                                                                                                 | 0.2 Vdd            | V      |                                                                                                                             |  |

| D032A        |        | OSC1 and T1OSI                             | Vss                                                                                                                                 | 0.3 VDD            | V      | LP, XT, HS, HSPLL<br>modes <sup>(1)</sup>                                                                                   |  |

| D033         |        | OSC1                                       | Vss                                                                                                                                 | 0.2 VDD            | V      | EC mode <sup>(1)</sup>                                                                                                      |  |

|              | VIH    | Input High Voltage                         |                                                                                                                                     |                    |        |                                                                                                                             |  |

|              |        | I/O Ports:                                 |                                                                                                                                     |                    |        |                                                                                                                             |  |

| D040         |        | with TTL Buffer                            | 0.25 VDD + 0.8V                                                                                                                     | Vdd                | V      | VDD < 4.5V                                                                                                                  |  |

| D040A        |        |                                            | 2.0                                                                                                                                 | Vdd                | V      | $4.5V \le V\text{DD} \le 5.5V$                                                                                              |  |

| D041         |        | with Schmitt Trigger Buffer<br>RC3 and RC4 | 0.8 VDD<br>0.7 VDD                                                                                                                  | Vdd<br>Vdd         | V<br>V |                                                                                                                             |  |

| D042         |        | MCLR                                       | 0.8 Vdd                                                                                                                             | Vdd                | V      |                                                                                                                             |  |

| D042A        |        | OSC1 and T1OSI                             | 0.7 VDD                                                                                                                             | Vdd                | V      | LP, XT, HS, HSPLL<br>modes <sup>(1)</sup>                                                                                   |  |

| D043         |        | OSC1                                       | 0.8 Vdd                                                                                                                             | Vdd                | V      | EC mode <sup>(1)</sup>                                                                                                      |  |

|              | lı∟    | Input Leakage Current <sup>(2,3)</sup>     |                                                                                                                                     |                    |        |                                                                                                                             |  |

| D060         |        | I/O Ports                                  | -                                                                                                                                   | ±1                 | μA     | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at hi-impedance} \end{split}$ |  |

| D061         |        | MCLR                                       | _                                                                                                                                   | ±5                 | μA     | $Vss \le VPIN \le VDD$                                                                                                      |  |

| D063         |        | OSC1                                       |                                                                                                                                     | ±5                 | μA     | $Vss \leq V PIN \leq V DD$                                                                                                  |  |

|              | IPU    | Weak Pull-up Current                       |                                                                                                                                     |                    |        |                                                                                                                             |  |

| D070         | IPURB  | PORTB Weak Pull-up Current                 | 50                                                                                                                                  | 400                | μA     | VDD = 5V, VPIN = VSS                                                                                                        |  |

**Note 1:** In RC oscillator configuration, the OSC1/CLKI pin is a Schmitt Trigger input. It is not recommended that the  $PIC^{\mathbb{R}}$  device be driven with an external clock while in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

**4:** Parameter is characterized but not tested.

## 26.3 DC Characteristics: PIC18F6390/6490/8390/8490 (Industrial) PIC18LF6390/6490/8390/8490 (Industrial) (Continued)

|                     |        |                                            | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |                                                                        |  |

|---------------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------------------------------------------------------------------|--|

| Param<br>No.        | Symbol | Characteristic                             | Min                                                                                                                                    | Мах | Units | Conditions                                                             |  |

|                     | Vol    | Output Low Voltage                         |                                                                                                                                        |     |       |                                                                        |  |

| D080                |        | I/O Ports                                  | _                                                                                                                                      | 0.6 | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |

| D083                |        | OSC2/CLKO<br>(RC, RCIO, EC, ECIO modes)    | _                                                                                                                                      | 0.6 | V     | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |

|                     | Vон    | Output High Voltage <sup>(3)</sup>         |                                                                                                                                        |     |       |                                                                        |  |

| D090                |        | I/O Ports                                  | Vdd - 0.7                                                                                                                              | —   | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                           |  |

| D092                |        | OSC2/CLKO<br>(RC, RCIO, EC, ECIO modes)    | Vdd - 0.7                                                                                                                              | —   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°C to +85°C                           |  |