Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8390-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome                  | Pin Number     | Pin      | Buffer       | <b>-</b>                                 |

|---------------------------|----------------|----------|--------------|------------------------------------------|

| Pin Name                  | TQFP           | Туре     | Туре         | Description                              |

|                           |                |          |              | PORTJ is a bidirectional I/O port.       |

| RJ0/SEG32<br>RJ0<br>SEG32 | 62             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG32 output for LCD.    |

| RJ1/SEG33<br>RJ1<br>SEG33 | 61             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG33 output for LCD.    |

| RJ2/SEG34<br>RJ2<br>SEG34 | 60             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG34 output for LCD.    |

| RJ3/SEG35<br>RJ3<br>SEG35 | 59             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG35 output for LCD.    |

| RJ4/SEG39<br>RJ4<br>SEG39 | 39             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG39 output for LCD.    |

| RJ5/SEG38<br>RJ5<br>SEG38 | 40             | I/O<br>O | ST<br>Analog | Digital I/O<br>SEG38 output for LCD.     |

| RJ6/SEG37<br>RJ6<br>SEG37 | 41             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG37 output for LCD.    |

| RJ7/SEG36<br>RJ7<br>SEG36 | 42             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG36 output for LCD.    |

| Vss                       | 11, 31, 51, 70 | Р        | _            | Ground reference for logic and I/O pins. |

| Vdd                       | 12, 32, 48, 71 | Р        | _            | Positive supply for logic and I/O pins.  |

| AVss                      | 26             | Р        | _            | Ground reference for analog modules.     |

| AVDD                      | 25             | Р        | _            | Positive supply for analog modules.      |

| TABLE 1-3: | PIC18F8X90 PINOUT I/O DESCRIPTIONS ( | CONTINUED) |

|------------|--------------------------------------|------------|

|            |                                      |            |

= Input = Power Ρ

Т

0 = Output OD = Open-Drain (no P diode to VDD)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

# 2.7.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 2-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS1:SCS0, select the clock source. The available clock sources are the primary clock (defined by the FOSC:FOSC0 Configuration bits), the secondary clock (Timer1 oscillator) and the internal oscillator block. The clock source changes immediately after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits, IRCF2:IRCF0, select the frequency output of the internal oscillator block to drive the device clock. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31.25 kHz to 4 MHz). If the internal oscillator block is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output.

When an output frequency of 31 kHz is selected (IRCF2:IRCF0 = 000), users may choose which internal oscillator acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the Watchdog Timer and the Fail-Safe Clock Monitor.

The OSTS, IOFS and T1RUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer has timed out and the primary clock is providing the device clock in primary clock modes. The IOFS bit indicates when the internal oscillator block has stabilized and is providing the device clock in RC Clock modes. The T1RUN bit (T1CON<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these three bits will be set at any time. If none of these bits are set, the INTRC is providing the clock, or the internal oscillator block has just started and is not yet stable. The IDLEN bit determines if the device goes into Sleep mode or one of the Idle modes when the SLEEP instruction is executed.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 3.0** "Power-Managed Modes".

- Note 1: The Timer1 oscillator must be enabled to select the secondary clock source. The Timer1 oscillator is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select a secondary clock source when executing a SLEEP instruction will be ignored.

- 2: It is recommended that the Timer1 oscillator be operating and stable before executing the SLEEP instruction, or a very long delay may occur while the Timer1 oscillator starts.

# 2.7.2 OSCILLATOR TRANSITIONS

PIC18F6390/6490/8390/8490 devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in greater detail in **Section 3.1.2 "Entering Power-Managed Modes"**.

### 2.8 Effects of Power-Managed Modes on the Various Clock Sources

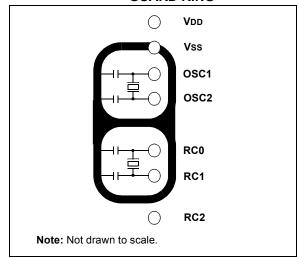

When PRI\_IDLE mode is selected, the designated primary oscillator continues to run without interruption. For all other power-managed modes, the oscillator using the OSC1 pin is disabled. The OSC1 pin (and OSC2 pin, if used by the oscillator) will stop oscillating.

In secondary clock modes (SEC\_RUN and SEC\_IDLE), the Timer1 oscillator is operating and providing the device clock. The Timer1 oscillator may also run in all power-managed modes if required to clock Timer1 or Timer3.

In internal oscillator modes (RC\_RUN and RC\_IDLE), the internal oscillator block provides the device clock source. The 31 kHz INTRC output can be used directly to provide the clock and may be enabled to support various special features, regardless of the power-managed mode (see Section 23.2 "Watchdog Timer (WDT)" through Section 23.4 "Fail-Safe Clock Monitor" for more information on WDT, Fail-Safe Clock Monitor and Two-Speed Start-up). The INTOSC output at 8 MHz may be used directly to clock the device, or may be divided down by the postscaler. The INTOSC output is disabled if the clock is provided directly from the INTRC output.

If the Sleep mode is selected, all clock sources are stopped. Since all the transistor switching currents have been stopped, Sleep mode achieves the lowest current consumption of the device (only leakage currents).

Enabling any on-chip feature that will operate during Sleep will increase the current consumed during Sleep. The INTRC is required to support WDT operation. The Timer1 oscillator may be operating to support a Real-Time Clock. Other features may be operating that do not require a device clock source (i.e., MSSP slave, INTx pins and others). Peripherals that may add significant current consumption are listed in Section 26.2 "DC Characteristics: Power-Down and Supply Current".

# 2.9 Power-up Delays

Power-up delays are controlled by two timers, so that no external Reset circuitry is required for most applications. The delays ensure that the device is kept in Reset until the device power supply is stable under normal circumstances and the primary clock is operating and stable. For additional information on power-up delays, see **Section 4.5 "Device Reset Timers"**.

The first timer is the Power-up Timer (PWRT), which provides a fixed delay on power-up (parameter 33, Table 26-10). It is enabled by clearing (= 0) the PWRTEN Configuration bit.

The second timer is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable (LP, XT and HS modes). The OST does this by counting 1024 oscillator cycles before allowing the oscillator to clock the device.

When the HSPLL Oscillator mode is selected, the device is kept in Reset for an additional 2 ms, following the HS mode OST delay, so the PLL can lock to the incoming clock frequency.

There is a delay of interval TCSD (parameter 38, Table 26-10) following POR while the controller becomes ready to execute instructions. This delay runs concurrently with any other delays. This may be the only delay that occurs when any of the EC, RC or INTIO modes are used as the primary clock source.

| Oscillator Mode | OSC1 Pin                                              | OSC2 Pin                                              |

|-----------------|-------------------------------------------------------|-------------------------------------------------------|

| RC, INTIO1      | Floating, external resistor should pull high          | At logic low (clock/4 output)                         |

| RCIO, INTIO2    | Floating, external resistor should pull high          | Configured as PORTA, bit 6                            |

| ECIO            | Floating, pulled by external clock                    | Configured as PORTA, bit 6                            |

| EC              | Floating, pulled by external clock                    | At logic low (clock/4 output)                         |

| LP, XT and HS   | Feedback inverter disabled at quiescent voltage level | Feedback inverter disabled at quiescent voltage level |

# TABLE 2-3: OSC1 AND OSC2 PIN STATES IN SLEEP MODE

**Note:** See Table 4-2 in **Section 4.0 "Reset"** for time-outs due to Sleep and MCLR Reset.

# 3.4.2 SEC\_IDLE MODE

In SEC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the Timer1 oscillator. This mode is entered from SEC\_RUN by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, set IDLEN first, then set SCS1:SCS0 to '01' and execute SLEEP. When the clock source is switched to the Timer1 oscillator, the primary oscillator is shut down, the OSTS bit is cleared and the T1RUN bit is set.

When a wake event occurs, the peripherals continue to be clocked from the Timer1 oscillator. After an interval of TCSD following the wake event, the CPU begins executing code being clocked by the Timer1 oscillator. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run (see Figure 3-8).

Note: The Timer1 oscillator should already be running prior to entering SEC\_IDLE mode. If the T1OSCEN bit is not set when the SLEEP instruction is executed, the SLEEP instruction will be ignored and entry to SEC\_IDLE mode will not occur. If the Timer1 oscillator is enabled, but not yet running, peripheral clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result.

### 3.4.3 RC\_IDLE MODE

In RC\_IDLE mode, the CPU is disabled but the peripherals continue to be clocked from the internal oscillator block using the INTOSC multiplexer. This mode allows for controllable power conservation during Idle periods.

From RC\_RUN, this mode is entered by setting the IDLEN bit and executing a SLEEP instruction. If the device is in another Run mode, first set IDLEN, then set the SCS1 bit and execute SLEEP. Although its value is ignored, it is recommended that SCS0 also be cleared; this is to maintain software compatibility with future devices. The INTOSC multiplexer may be used to select a higher clock frequency by modifying the IRCF bits before executing the SLEEP instruction. When the clock source is switched to the INTOSC multiplexer, the primary oscillator is shut down and the OSTS bit is cleared.

If the IRCF bits are set to any non-zero value, or the INTSRC bit is set, the INTOSC output is enabled. The IOFS bit becomes set after the INTOSC output becomes stable after an interval of TIOBST (parameter 39, Table 26-10). Clocks to the peripherals continue while the INTOSC source stabilizes. If the IRCF bits were previously at a non-zero value, or INTSRC was set before the SLEEP instruction was executed and the INTOSC source was already stable, the IOFS bit will remain set. If the IRCF bits and INTSRC are all clear, the INTOSC output will not be enabled; the IOFS bit will remain clear and there will be no indication of the current clock source.

When a wake event occurs, the peripherals continue to be clocked from the INTOSC multiplexer. After a delay of TCSD following the wake event, the CPU begins executing code being clocked by the INTOSC multiplexer. The IDLEN and SCS bits are not affected by the wake-up. The INTRC source will continue to run if either the WDT or the Fail-Safe Clock Monitor is enabled.

| EXAMPLE   | 6-1: F  | READING A FLASH PI | ROGRAM MEMORY WORD               |

|-----------|---------|--------------------|----------------------------------|

|           | MOVLW   | CODE_ADDR_UPPER    | ; Load TBLPTR with the base      |

|           | MOVWF   | TBLPTRU            | ; address of the word            |

|           | MOVLW   | CODE ADDR HIGH     |                                  |

|           | MOVWF   | TBLPTRH            |                                  |

|           | MOVLW   | CODE ADDR LOW      |                                  |

|           | MOVWF   | TBLPTRL            |                                  |

| READ WORD |         |                    |                                  |

| _         | TBLRD*+ |                    | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W          | ; get data                       |

|           | MOVWF   | WORD EVEN          |                                  |

|           | TBLRD*+ | —                  | ; read into TABLAT and increment |

|           | MOVF    | TABLAT, W          | ; get data                       |

|           | MOVWF   | WORD_ODD           |                                  |

|           |         |                    |                                  |

| TABLE 6-2: | REGIS                                                 | REGISTERS ASSOCIATED WITH READING PROGRAM FLASH MEMORY |        |                                                                   |                               |  |                            |    |    |  |  |

|------------|-------------------------------------------------------|--------------------------------------------------------|--------|-------------------------------------------------------------------|-------------------------------|--|----------------------------|----|----|--|--|

| Name       | Bit 7                                                 | Bit 6                                                  | Bit 5  | Bit 4                                                             | Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |  | Reset<br>Values on<br>Page |    |    |  |  |

| TBLPTRU    | —                                                     |                                                        | bit 21 | bit 21 Program Memory Table Pointer Upper Byte<br>(TBLPTR<20:16>) |                               |  |                            |    |    |  |  |

| TBLPTRH    | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |                                                        |        |                                                                   |                               |  |                            |    | 59 |  |  |

| TBLPTRL    | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)   |                                                        |        |                                                                   |                               |  |                            | 59 |    |  |  |

| TABLAT     | Program Me                                            | emory Table                                            | Latch  |                                                                   |                               |  |                            |    | 59 |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash access.

### REGISTER 8-3: INTCON3: INTERRUPT CONTROL REGISTER 3

| R/W-1  | R/W-1  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| INT2IP | INT1IP | INT3IE | INT2IE | INT1IE | INT3IF | INT2IF | INT1IF |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:                           |                       |                                                                  |                             |                                                                                          |

|-----------------------------------|-----------------------|------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------|

| R = Readable bit W = Writable bit |                       |                                                                  | U = Unimplemented bit,      | read as '0'                                                                              |

| -n = Value                        | at POR                | '1' = Bit is set                                                 | '0' = Bit is cleared        | x = Bit is unknown                                                                       |

| bit 7                             | INT2IP: IN            | IT2 External Interrupt Priority                                  | bit                         |                                                                                          |

|                                   | 1 = High<br>0 = Low p |                                                                  |                             |                                                                                          |

| bit 6                             | INT1IP: IN            | IT1 External Interrupt Priority                                  | bit                         |                                                                                          |

|                                   | 1 = High<br>0 = Low p | •                                                                |                             |                                                                                          |

| bit 5                             | INT3IE: IN            | IT3 External Interrupt Enable                                    | bit                         |                                                                                          |

|                                   |                       | es the INT3 external interrup<br>les the INT3 external interrup  |                             |                                                                                          |

| bit 4                             | INT2IE: IN            | IT2 External Interrupt Enable                                    | bit                         |                                                                                          |

|                                   |                       | es the INT2 external interrup<br>les the INT2 external interrup  |                             |                                                                                          |

| bit 3                             | INT1IE: IN            | IT1 External Interrupt Enable                                    | bit                         |                                                                                          |

|                                   |                       | es the INT1 external interrup<br>les the INT1 external interrup  |                             |                                                                                          |

| bit 2                             | INT3IF: IN            | IT3 External Interrupt Flag bit                                  |                             |                                                                                          |

|                                   |                       | NT3 external interrupt occurre<br>NT3 external interrupt did not |                             | ire)                                                                                     |

| bit 1                             | INT2IF: IN            | IT2 External Interrupt Flag bit                                  |                             |                                                                                          |

|                                   |                       | NT2 external interrupt occurre<br>NT2 external interrupt did not |                             | ire)                                                                                     |

| bit 0                             | INT1IF: IN            | IT1 External Interrupt Flag bit                                  |                             |                                                                                          |

|                                   |                       | NT1 external interrupt occurre<br>NT1 external interrupt did not |                             | ire)                                                                                     |

| Note:                             | enable bit or t       |                                                                  | User software should ensure | s of the state of its corresponding<br>e the appropriate interrupt flag bits<br>polling. |

| R/W-0        | U-0                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CMIE         | —                                                                                                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                        | BCLIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | HLVDIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | TMR3IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CCP2IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|              |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|              |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|              |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| bit          | W = Writable I                                                                                                                                                                                                                                                   | oit                                                                                                                                                                                                                                                                                                                                                                                                                                      | U = Unimplem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nented bit, read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| POR          | '1' = Bit is set                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | x = Bit is unkn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|              |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| OSCFIE: Osc  | illator Fail Inter                                                                                                                                                                                                                                               | rupt Enable bi                                                                                                                                                                                                                                                                                                                                                                                                                           | t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 1 = Enabled  |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0 = Disabled |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

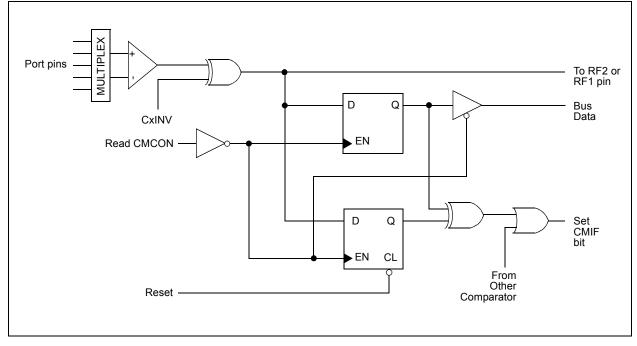

| •            | arator Interrupt                                                                                                                                                                                                                                                 | Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|              |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|              | ted: Deed ee fo                                                                                                                                                                                                                                                  | <b>3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| -            |                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |