Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, LCD, POR, PWM, WDT                           |

| Number of I/O              | 66                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 768 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8490-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nome                                              | Pin Number      | Pin                | Buffer                            | Description                                                                                                                                       |  |  |  |  |  |

|-------------------------------------------------------|-----------------|--------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name                                              | TQFP            | Туре               | Туре                              | Description                                                                                                                                       |  |  |  |  |  |

|                                                       |                 |                    |                                   | PORTA is a bidirectional I/O port.                                                                                                                |  |  |  |  |  |

| RA0/AN0<br>RA0<br>AN0                                 | 24              | I/O<br>I           | TTL<br>Analog                     | Digital I/O.<br>Analog input 0.                                                                                                                   |  |  |  |  |  |

| RA1/AN1<br>RA1<br>AN1                                 | 23              | I/O<br>I           | TTL<br>Analog                     | Digital I/O.<br>Analog input 1.                                                                                                                   |  |  |  |  |  |

| RA2/AN2/VREF-/SEG16<br>RA2<br>AN2<br>VREF-<br>SEG16   | 22              | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 2.<br>A/D reference voltage (Low) input.<br>SEG16 output for LCD.                                                    |  |  |  |  |  |

| RA3/AN3/VREF+/SEG17<br>RA3<br>AN3<br>VREF+<br>SEG17   | 21              | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 3.<br>A/D reference voltage (High) input.<br>SEG17 output for LCD.                                                   |  |  |  |  |  |

| RA4/T0CKI/SEG14<br>RA4<br>T0CKI<br>SEG14              | 28              | I/O<br>I<br>O      | ST/OD<br>ST<br>Analog             | Digital I/O. Open-drain when configured as output.<br>Timer0 external clock input.<br>SEG14 output for LCD.                                       |  |  |  |  |  |

| RA5/AN4/HLVDIN/SEG15<br>RA5<br>AN4<br>HLVDIN<br>SEG15 | 27              | I/O<br>I<br>I<br>O | TTL<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog input 4.<br>Low-Voltage Detect input.<br>SEG15 output for LCD.                                                             |  |  |  |  |  |

| RA6                                                   |                 |                    |                                   | See the OSC2/CLKO/RA6 pin.                                                                                                                        |  |  |  |  |  |

| RA7                                                   |                 |                    |                                   | See the OSC1/CLKI/RA7 pin.                                                                                                                        |  |  |  |  |  |

| I = Input<br>P = Power                                | t Trigger input |                    |                                   | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)<br>tion bit, CCP2MX, is set. |  |  |  |  |  |

| TABLE 1-2: | PIC18F6X90 PINOUT I/O DESCRIPTIONS (CONTINUED) |  |

|------------|------------------------------------------------|--|

|            |                                                |  |

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

| D' Nov                                                                                                                                                                                                                                                                                                                                                         | Pin Number | Pin Buffer      |                    |                                                                                        |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|--------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                                                                                                                                                                                                                                                                                                                                       | TQFP       | Туре            | Туре               | Description                                                                            |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                |            |                 |                    | PORTE is a bidirectional I/O port.                                                     |  |  |  |  |

| LCDBIAS1<br>LCDBIAS1                                                                                                                                                                                                                                                                                                                                           | 4          | I               | Analog             | BIAS1 input for LCD.                                                                   |  |  |  |  |

| LCDBIAS2<br>LCDBIAS2                                                                                                                                                                                                                                                                                                                                           | 3          | I               | Analog             | BIAS2 input for LCD.                                                                   |  |  |  |  |

| LCDBIAS3<br>LCDBIAS3                                                                                                                                                                                                                                                                                                                                           | 78         | I               | Analog             | BIAS3 input for LCD.                                                                   |  |  |  |  |

| COM0<br>COM0                                                                                                                                                                                                                                                                                                                                                   | 77         | 0               | Analog             | COM0 output for LCD.                                                                   |  |  |  |  |

| RE4/COM1<br>RE4<br>COM1                                                                                                                                                                                                                                                                                                                                        | 76         | I/O<br>O        | ST<br>Analog       | Digital I/O.<br>COM1 output for LCD.                                                   |  |  |  |  |

| RE5/COM2<br>RE5<br>COM2                                                                                                                                                                                                                                                                                                                                        | 75         | I/O<br>O        | ST<br>Analog       | Digital I/O.<br>COM2 output for LCD.                                                   |  |  |  |  |

| RE6/COM3<br>RE6<br>COM3                                                                                                                                                                                                                                                                                                                                        | 74         | I/O<br>O        | ST<br>Analog       | Digital I/O.<br>COM3 output for LCD.                                                   |  |  |  |  |

| RE7/CCP2/SEG31<br>RE7<br>CCP2 <sup>(2)</sup><br>SEG31                                                                                                                                                                                                                                                                                                          | 73         | I/O<br>I/O<br>O | ST<br>ST<br>Analog | Digital I/O.<br>Capture 2 input/Compare 2 output/PWM2 output.<br>SEG31 output for LCD. |  |  |  |  |

| Legend:       TTL = TTL compatible input       CMOS = CMOS compatible input or output         ST = Schmitt Trigger input with CMOS levels       Analog = Analog input         I = Input       O = Output         P = Power       OD = Open-Drain (no P diode to VDD)         Note 1:       Default assignment for CCP2 when Configuration bit, CCP2MX, is set. |            |                 |                    |                                                                                        |  |  |  |  |

| <b>TABLE 1-3</b> : | PIC18F8X90 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|--------------------|------------------------------------------------|

|--------------------|------------------------------------------------|

efault assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

#### 2.6.5.1 Compensating with the AUSART

An adjustment may be required when the AUSART begins to generate framing errors or receives data with errors while in Asynchronous mode. Framing errors indicate that the device clock frequency is too high. To adjust for this, decrement the value in OSTUNE to reduce the clock frequency. On the other hand, errors in data may suggest that the clock speed is too low. To compensate, increment OSTUNE to increase the clock frequency.

#### 2.6.5.2 Compensating with the Timers

This technique compares device clock speed to some reference clock. Two timers may be used; one timer is clocked by the peripheral clock, while the other is clocked by a fixed reference source, such as the Timer1 oscillator.

Both timers are cleared, but the timer clocked by the reference generates interrupts. When an interrupt occurs, the internally clocked timer is read and both timers are cleared. If the internally clocked timer value

is greater than expected, then the internal oscillator block is running too fast. To adjust for this, decrement the OSCTUNE register.

#### 2.6.5.3 Compensating with the Timers

A CCP module can use free-running Timer1 (or Timer3), clocked by the internal oscillator block and an external event with a known period (i.e., AC power frequency). The time of the first event is captured in the CCPRxH:CCPRxL registers and is recorded. When the second event causes a capture, the time of the first event is subtracted from the time of the second event. Since the period of the external event is known, the time difference between events can be calculated.

If the measured time is much greater than the calculated time, then the internal oscillator block is running too fast. To compensate, decrement the OSTUNE register. If the measured time is much less than the calculated time, then the internal oscillator block is running too slow. To compensate, increment the OSTUNE register.

#### REGISTER 2-1: OSCTUNE: OSCILLATOR TUNING REGISTER

| R/W-0  | R/W-0 <sup>(1)</sup> | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|----------------------|-----|-------|-------|-------|-------|-------|

| INTSRC | PLLEN <sup>(1)</sup> | —   | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7  |                      |     |       |       |       |       | bit 0 |

| Legend:    |                 |                                                                       |                                                                                            |                    |

|------------|-----------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|

| R = Reada  | able bit        | W = Writable bit                                                      | U = Unimplemented bit                                                                      | , read as '0'      |

| -n = Value | at POR          | '1' = Bit is set                                                      | '0' = Bit is cleared                                                                       | x = Bit is unknown |

| bit 7      | 1 = <b>31.2</b> |                                                                       | uency Source Select bit<br>rom 8 MHz INTOSC source (di<br>ctly from INTRC internal oscilla | •                  |

| bit 6      |                 | Frequency Multiplier PLL for<br>enabled for INTOSC (4 MHz<br>disabled |                                                                                            |                    |

| bit 5      | Unimple         | mented: Read as '0'                                                   |                                                                                            |                    |

bit 4-0 **TUN4:TUN0:** Frequency Tuning bits

```

01111 = Maximum frequency

00001

00000 = Center frequency. Oscillator module is running at the calibrated frequency.

11111

10000 = Minimum frequency

```

Note 1: Available only in certain oscillator configurations; otherwise, this bit is unavailable and read as '0'. See Section 2.6.4 "PLL in INTOSC Modes" for details.

| Register | Applicable<br>Devices |      | Power-on Reset,<br>Brown-out Reset | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets | Wake-up via WDT<br>or Interrupt |  |  |

|----------|-----------------------|------|------------------------------------|---------------------------------------------------------------|---------------------------------|--|--|

| ADRESH   | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | นนนน นนนน                       |  |  |

| ADRESL   | 6X90                  | 8X90 | XXXX XXXX                          | uuuu uuuu                                                     | uuuu uuuu                       |  |  |

| ADCON0   | 6X90                  | 8X90 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |  |

| ADCON1   | 6X90                  | 8X90 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |  |

| ADCON2   | 6X90                  | 8X90 | 0-00 0000                          | 0-00 0000                                                     | u-uu uuuu                       |  |  |

| CCPR1H   | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | นนนน นนนน                       |  |  |

| CCPR1L   | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | սսսս սսսս                       |  |  |

| CCP1CON  | 6X90                  | 8X90 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |  |

| CCPR2H   | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | นนนน นนนน                       |  |  |

| CCPR2L   | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | սսսս սսսս                       |  |  |

| CCP2CON  | 6X90                  | 8X90 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |  |

| CVRCON   | 6X90                  | 8X90 | 000- 0000                          | 000- 0000                                                     | uuu- uuuu                       |  |  |

| CMCON    | 6X90                  | 8X90 | 0000 0111                          | 0000 0111                                                     | นนนน นนนน                       |  |  |

| TMR3H    | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | นนนน นนนน                       |  |  |

| TMR3L    | 6X90                  | 8X90 | XXXX XXXX                          | นนนน นนนน                                                     | սսսս սսսս                       |  |  |

| T3CON    | 6X90                  | 8X90 | 0000 0000                          | սսսս սսսս                                                     | սսսս սսսս                       |  |  |

| SPBRG1   | 6X90                  | 8X90 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |  |

| RCREG1   | 6X90                  | 8X90 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |  |

| TXREG1   | 6X90                  | 8X90 | 0000 0000                          | 0000 0000                                                     | սսսս սսսս                       |  |  |

| TXSTA1   | 6X90                  | 8X90 | 0000 0010                          | 0000 0010                                                     | սսսս սսսս                       |  |  |

| RCSTA1   | 6X90                  | 8X90 | 0000 000x                          | 0000 000x                                                     | սսսս սսսս                       |  |  |

| IPR3     | 6X90                  | 8X90 | -111                               | -111                                                          | -uuu                            |  |  |

| PIR3     | 6X90                  | 8X90 | -000                               | -000                                                          | -uuu <b>(1)</b>                 |  |  |

| PIE3     | 6X90                  | 8X90 | -000                               | -000                                                          | -uuu                            |  |  |

| IPR2     | 6X90                  | 8X90 | 11 1111                            | 11 1111                                                       | uu uuuu                         |  |  |

| PIR2     | 6X90                  | 8X90 | 00 0000                            | 00 0000                                                       | uu uuuu <b>(1)</b>              |  |  |

| PIE2     | 6X90                  | 8X90 | 00 0000                            | 00 0000                                                       | uu uuuu                         |  |  |

| IPR1     | 6X90                  | 8X90 | -111 1111                          | -111 1111                                                     | -uuu uuuu                       |  |  |

| PIR1     | 6X90                  | 8X90 | -000 0000                          | -000 0000                                                     | -uuu uuuu <b>(1)</b>            |  |  |

| PIE1     | 6X90                  | 8X90 | -000 0000                          | -000 0000                                                     | -uuu uuuu                       |  |  |

| OSCTUNE  | 6X90                  | 8X90 | 00-0 0000                          | 00-0 0000                                                     | uu-u uuuu                       |  |  |

| TABLE 4-4: | INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |

|------------|---------------------------------------------------------|

|------------|---------------------------------------------------------|

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

**3:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

4: See Table 4-3 for Reset value for specific condition.

**5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read '0'.

**6:** These registers are cleared on POR and unchanged on BOR.

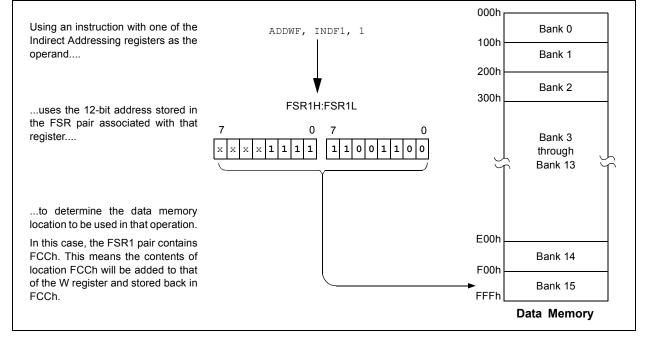

## 5.4.3.1 FSR Registers and the INDF Operand

At the core of Indirect Addressing are three sets of registers: FSR0, FSR1 and FSR2. Each represents a pair of 8-bit registers, FSRnH and FSRnL. The four upper bits of the FSRnH register are not used, so each FSR pair holds a 12-bit value. This represents a value that can address the entire range of the data memory in a linear fashion. The FSR register pairs, then, serve as pointers to data memory locations.

Indirect Addressing is accomplished with a set of Indirect File Operands, INDF0 through INDF2. These can be thought of as "virtual" registers: they are mapped in the SFR space but are not physically implemented. Reading or writing to a particular INDF register actually accesses its corresponding FSR register pair. A read from INDF1, for example, reads the data at the address indicated by FSR1H:FSR1L. Instructions that use the INDF registers as operands actually use the contents of their corresponding FSR as a pointer to the instruction's target. The INDF operand is just a convenient way of using the pointer.

Because Indirect Addressing uses a full 12-bit address, data RAM banking is not necessary. Thus, the current contents of the BSR and the Access RAM bit have no effect on determining the target address.

#### FIGURE 5-7: INDIRECT ADDRESSING

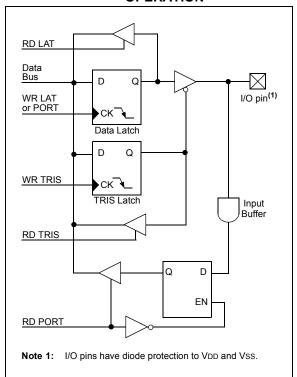

#### 9.0 I/O PORTS

Depending on the device selected and features enabled, there are up to nine ports available. Some pins of the I/O ports are multiplexed with an alternate function from the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

Each port has three registers for its operation. These registers are:

- TRIS register (data direction register)

- PORT register (reads the levels on the pins of the device)

- LAT register (output latch)

The Data Latch (LAT register) is useful for read-modify-write operations on the value that the I/O pins are driving.

A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 9-1.

FIGURE 9-1: GENERIC I/O PORT OPERATION

#### 9.1 PORTA, TRISA and LATA Registers

PORTA is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISA. Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., put the contents of the output latch on the selected pin).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch.

The Data Latch register (LATA) is also memory mapped. Read-modify-write operations on the LATA register read and write the latched output value for PORTA.

The RA4 pin is multiplexed with the Timer0 module clock input and the LCD segment drive to become the RA4/T0CKI/SEG14 pin. Pins RA6 and RA7 are multiplexed with the main oscillator pins; they are enabled as oscillator or I/O pins by the selection of the main oscillator in the Configuration register (see **Section 23.1 "Configuration Bits"** for details). When they are not used as port pins, RA6 and RA7 and their associated TRIS and LAT bits are read as '0'.

The other PORTA pins are multiplexed with analog inputs and the analog VREF+ and VREF- inputs. The operation of pins RA3:RA0 and RA5 as A/D converter inputs is selected by clearing or setting the control bits in the ADCON1 register (A/D Control Register 1).

The RA4/T0CKI/SEG14 pin is a Schmitt Trigger input and an open-drain output. All other PORTA pins have TTL input levels and full CMOS output drivers.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs.

RA5:RA2 are also multiplexed with LCD segment drives controlled by bits in the LCDSE1 and LCDSE2 registers. I/O port functions are only available when the segments are disabled.

| CLRF  | PORTA  | ; Initialize PORTA by<br>; clearing output |

|-------|--------|--------------------------------------------|

|       |        | , creating output                          |

|       |        | ; data latches                             |

| CLRF  | LATA   | ; Alternate method                         |

|       |        | ; to clear output                          |

|       |        | ; data latches                             |

| MOVLW | 07h    | ; Configure A/D                            |

| MOVWF | ADCON1 | ; for digital inputs                       |

| MOVWF | 07h    | ; Configure comparators                    |

| MOVWF | CMCON  | ; for digital input                        |

| MOVLW | OCFh   | ; Value used to                            |

|       |        | ; initialize data                          |

|       |        | ; direction                                |

| MOVWF | TRISA  | ; Set RA<3:0> as inputs                    |

|       |        | ; RA<5:4> as outputs                       |

|       |        |                                            |

#### 15.4.2 OPERATION

The MSSP module functions are enabled by setting MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the  $I^2C$  operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following  $I^2C$  modes to be selected:

- I<sup>2</sup>C Master mode, clock = (Fosc/4) x (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 15.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The  $I^2C$  Slave mode hardware will always generate an interrupt on an address match. Through the mode select bits, the user can also choose to interrupt on Start and Stop bits

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this ACK pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but the SSPIF bit (PIR1<3>) is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low time for proper operation. The high and low times of the  $I^2C$  specification, as well as the requirement of the MSSP module, are shown in timing parameter #100 and parameter #101.

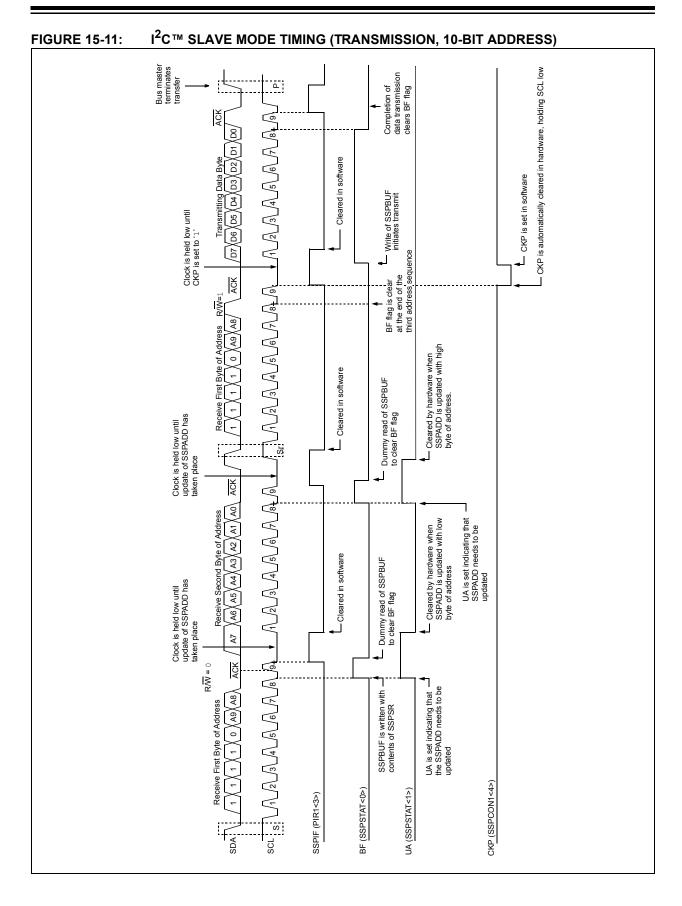

#### 15.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- 1. The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- 4. MSSP Interrupt Flag bit, SSPIF (PIR1<3>), is set (interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Addressing mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit R/W (SSPSTAT<2>) must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-Bit Addressing mode is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive first (high) byte of address (bits SSPIF, BF and UA (SSPSTAT<1>) are set).

- 2. Update the SSPADD register with second (low) byte of address (clears bit UA and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 4. Receive second (low) byte of address (bits SSPIF, BF and UA are set).

- 5. Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear bit, UA.

- 6. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (SSPIF and BF bits are set).

- 9. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

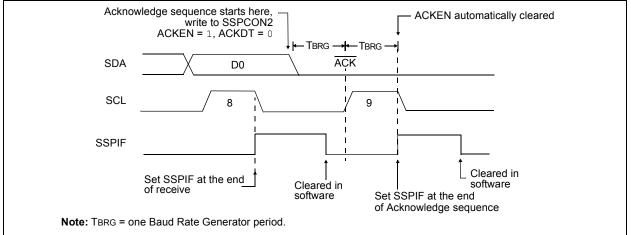

#### 15.4.12 ACKNOWLEDGE SEQUENCE TIMING

An Acknowledge sequence is enabled by setting the Acknowledge Sequence Enable bit. ACKEN (SSPCON2<4>). When this bit is set, the SCL pin is pulled low and the contents of the Acknowledge data bit are presented on the SDA pin. If the user wishes to generate an Acknowledge, then the ACKDT bit should be cleared. If not, the user should set the ACKDT bit before starting an Acknowledge sequence. The Baud Rate Generator then counts for one rollover period (TBRG) and the SCL pin is deasserted (pulled high). When the SCL pin is sampled high (clock arbitration), the Baud Rate Generator counts for TBRG. The SCL pin is then pulled low. Following this, the ACKEN bit is automatically cleared, the Baud Rate Generator is turned off and the MSSP module then goes into Idle mode (Figure 15-23).

#### 15.4.12.1 WCOL Status Flag

If the user writes the SSPBUF when an Acknowledge sequence is in progress, then WCOL is set and the contents of the buffer are unchanged (the write doesn't occur).

#### 15.4.13 STOP CONDITION TIMING

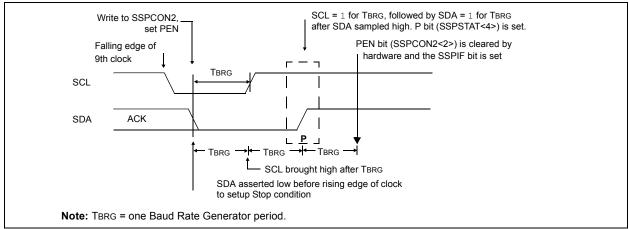

A Stop bit is asserted on the SDA pin at the end of a receive/transmit by setting the Stop Sequence Enable bit, PEN (SSPCON2<2>). At the end of a receive/ transmit, the SCL line is held low after the falling edge of the ninth clock. When the PEN bit is set, the master will assert the SDA line low. When the SDA line is sampled low, the Baud Rate Generator is reloaded and counts down to '0'. When the Baud Rate Generator times out, the SCL pin will be brought high and one TBRG (Baud Rate Generator rollover count) later, the SDA pin will be deasserted. When the SDA pin is sampled high while SCL is high, the P bit (SSPSTAT<4>) is set. A TBRG later, the PEN bit is cleared and the SSPIF bit is set (Figure 15-24).

#### 15.4.13.1 WCOL Status Flag

If the user writes the SSPBUF when a Stop sequence is in progress, then the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

#### FIGURE 15-23: ACKNOWLEDGE SEQUENCE WAVEFORM

#### FIGURE 15-24: STOP CONDITION RECEIVE OR TRANSMIT MODE

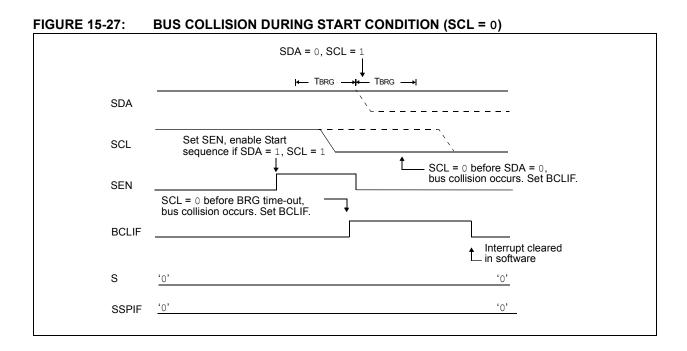

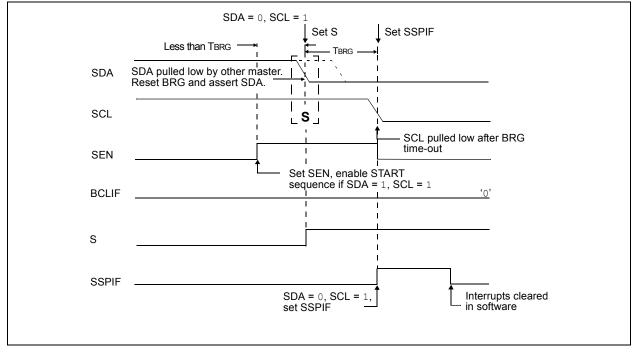

#### FIGURE 15-28: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

#### 16.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (EUSART)

PIC18F6390/6490/8390/8490 devices have three serial I/O modules: the MSSP module, discussed in the previous chapter and two Universal Synchronous Asynchronous Receiver Transmitter (USART) modules. (Generically, the USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

There are two distinct implementations of the USART module in these devices: the Enhanced USART (EUSART) discussed here and the Addressable USART discussed in the next chapter. For this device family, USART1 always refers to the EUSART, while USART2 is always the AUSART.

The EUSART and AUSART modules implement the same core features for serial communications; their basic operation is essentially the same. The EUSART module provides additional features, including Automatic Baud Rate Detection (ABD) and calibration, automatic wake-up on Sync Break reception and 12-bit Break character transmit. These features make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

The EUSART can be configured in the following modes:

- Asynchronous (full-duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit Break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

The pins of the EUSART are multiplexed with the functions of PORTC (RC6/TX1/CK1 and RC7/RX1/DT1). In order to configure these pins as an EUSART:

- bit SPEN (RCSTA1<7>) must be set (= 1)

- bit TRISC<7> must be set (= 1)

- bit TRISC<6> must be set (= 1)

- **Note:** The USART control will automatically reconfigure the pin from input to output as needed.

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control Register 1 (TXSTA1)

- Receive Status and Control Register 1 (RCSTA1)

- Baud Rate Control Register 1 (BAUDCON1)

The registers are described in Register 16-1, Register 16-2 and Register 16-3.

|              | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                    |            |                             |                    |            |                             |                    |            |                             |

|--------------|-------------------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz             |            |                             | Fosc = 20.000 MHz  |            |                             | Fosc = 10.000 MHz  |            |                             | Fosc = 8.000 MHz   |            |                             |

| (K)          | Actual<br>Rate (K)            | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          |                               |            |                             | _                  |            |                             | _                  |            |                             | _                  |            | _                           |

| 1.2          | —                             | —          | —                           | 1.221              | 1.73       | 255                         | 1.202              | 0.16       | 129                         | 1.201              | -0.16      | 103                         |

| 2.4          | 2.441                         | 1.73       | 255                         | 2.404              | 0.16       | 129                         | 2.404              | 0.16       | 64                          | 2.403              | -0.16      | 51                          |

| 9.6          | 9.615                         | 0.16       | 64                          | 9.766              | 1.73       | 31                          | 9.766              | 1.73       | 15                          | 9.615              | -0.16      | 12                          |

| 19.2         | 19.531                        | 1.73       | 31                          | 19.531             | 1.73       | 15                          | 19.531             | 1.73       | 7                           | _                  | _          | _                           |

| 57.6         | 56.818                        | -1.36      | 10                          | 62.500             | 8.51       | 4                           | 52.083             | -9.58      | 2                           | —                  | _          | _                           |

| 115.2        | 125.000                       | 8.51       | 4                           | 104.167            | -9.58      | 2                           | 78.125             | -32.18     | 1                           | —                  | _          | _                           |

#### TABLE 16-3: BAUD RATES FOR ASYNCHRONOUS MODES

|             | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                    |            |                             |                    |            |                             |

|-------------|-------------------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD        | Fos                           | c = 4.000  | MHz                         | Fos                | c = 2.000  | MHz                         | Fos                | c = 1.000  | MHz                         |

| RATE<br>(K) | Actual<br>Rate (K)            | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                         | 0.16       | 207                         | 0.300              | -0.16      | 103                         | 0.300              | -0.16      | 51                          |

| 1.2         | 1.202                         | 0.16       | 51                          | 1.201              | -0.16      | 25                          | 1.201              | -0.16      | 12                          |

| 2.4         | 2.404                         | 0.16       | 25                          | 2.403              | -0.16      | 12                          | —                  |            | _                           |

| 9.6         | 8.929                         | -6.99      | 6                           | _                  | _          | _                           | _                  | _          | _                           |

| 19.2        | 20.833                        | 8.51       | 2                           | _                  | _          | _                           | _                  | _          | _                           |

| 57.6        | 62.500                        | 8.51       | 0                           | —                  | _          | _                           | —                  | _          | _                           |

| 115.2       | 62.500                        | -45.75     | 0                           | —                  | —          |                             | —                  | —          | —                           |

|             |                    | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                    |            |                             |                    |            |                             |                    |            |                             |

|-------------|--------------------|-------------------------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD        | Foso               | : = 40.000                    | ) MHz                       | Fosc               | = 20.00    | 0 MHz                       | Fosc               | = 10.00    | 0 MHz                       | Fosc = 8.000 MHz   |            |                             |

| RATE<br>(K) | Actual<br>Rate (K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         |                    | _                             |                             | _                  |            | _                           | _                  |            |                             | _                  | _          | _                           |

| 1.2         | —                  | —                             | —                           | —                  | —          | _                           | —                  | —          | _                           | —                  | —          | —                           |

| 2.4         | _                  | _                             | _                           | —                  | _          | _                           | 2.441              | 1.73       | 255                         | 2.403              | -0.16      | 207                         |

| 9.6         | 9.766              | 1.73                          | 255                         | 9.615              | 0.16       | 129                         | 9.615              | 0.16       | 64                          | 9.615              | -0.16      | 51                          |

| 19.2        | 19.231             | 0.16                          | 129                         | 19.231             | 0.16       | 64                          | 19.531             | 1.73       | 31                          | 19.230             | -0.16      | 25                          |

| 57.6        | 58.140             | 0.94                          | 42                          | 56.818             | -1.36      | 21                          | 56.818             | -1.36      | 10                          | 55.555             | 3.55       | 8                           |

| 115.2       | 113.636            | -1.36                         | 21                          | 113.636            | -1.36      | 10                          | 125.000            | 8.51       | 4                           | _                  | _          | —                           |

|       | SYNC = 0, BRGH = 1, BRG16 = 0 |            |                             |                    |            |                             |                    |            |                             |

|-------|-------------------------------|------------|-----------------------------|--------------------|------------|-----------------------------|--------------------|------------|-----------------------------|

| BAUD  | Fos                           | c = 4.000  | MHz                         | Fos                | c = 2.000  | MHz                         | Fos                | c = 1.000  | MHz                         |

| (K)   | Actual<br>Rate (K)            | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate (K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3   | _                             |            |                             | _                  | _          |                             | 0.300              | -0.16      | 207                         |

| 1.2   | 1.202                         | 0.16       | 207                         | 1.201              | -0.16      | 103                         | 1.201              | -0.16      | 51                          |

| 2.4   | 2.404                         | 0.16       | 103                         | 2.403              | -0.16      | 51                          | 2.403              | -0.16      | 25                          |

| 9.6   | 9.615                         | 0.16       | 25                          | 9615               | -0.16      | 12                          | —                  |            | —                           |

| 19.2  | 19.231                        | 0.16       | 12                          | —                  | _          | _                           | —                  | _          | _                           |

| 57.6  | 62.500                        | 8.51       | 3                           | —                  |            | _                           | —                  |            | —                           |

| 115.2 | 125.000                       | 8.51       | 1                           | —                  | _          | —                           | —                  | _          | —                           |

#### REGISTER 18-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-q | R/W-q | R/W-q | R/W-q |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | VCFG1 | VCFG0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6 | <b>Unimplemented:</b> Read as '0' |

|---------|-----------------------------------|

|         |                                   |

| bit 5 | <b>VCFG1:</b> Voltage Reference Configuration bit (VREF- source)<br>1 = VREF- (AN2)      |

|-------|------------------------------------------------------------------------------------------|

|       | 0 = AVss                                                                                 |

| bit 4 | VCFG0: Voltage Reference Configuration bit (VREF+ source)<br>1 = VREF+ (AN3)<br>0 = AVDD |

bit 3-0 **PCFG3:PCFG0:** A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN11 | AN10 | AN9 | AN8 | AN7 | ANG | AN5 | AN4 | AN3 | AN2 | AN1 | ANO |

|-----------------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0000            | Α    | Α    | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0001            | А    | Α    | Α   | Α   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0010            | А    | Α    | Α   | Α   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0011            | А    | Α    | Α   | Α   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0100            | D    | Α    | Α   | Α   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0101            | D    | D    | Α   | Α   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0110            | D    | D    | D   | Α   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 0111            | D    | D    | D   | D   | Α   | А   | Α   | Α   | Α   | Α   | Α   | Α   |

| 1000            | D    | D    | D   | D   | D   | А   | Α   | А   | Α   | Α   | Α   | А   |

| 1001            | D    | D    | D   | D   | D   | D   | Α   | Α   | Α   | Α   | Α   | Α   |

| 1010            | D    | D    | D   | D   | D   | D   | D   | Α   | Α   | Α   | Α   | Α   |

| 1011            | D    | D    | D   | D   | D   | D   | D   | D   | Α   | Α   | Α   | Α   |

| 1100            | D    | D    | D   | D   | D   | D   | D   | D   | D   | Α   | Α   | А   |

| 1101            | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | Α   | Α   |

| 1110            | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | А   |

| 1111            | D    | D    | D   | D   | D   | D   | D   | D   | D   | D   | D   | D   |

A = Analog input

D = Digital I/O

#### **19.2** Comparator Operation

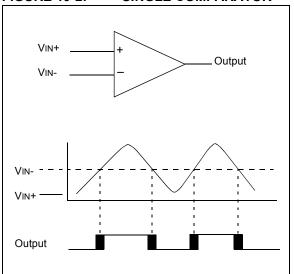

A single comparator is shown in Figure 19-2, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 19-2 represent the uncertainty, due to input offsets and response time.

#### **19.3 Comparator Reference**

Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly (Figure 19-2).

FIGURE 19-2: SINGLE COMPARATOR

#### 19.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same, or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between Vss and VDD and can be applied to either pin of the comparator(s).

#### 19.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference from the comparator voltage reference module. This module is described in more detail in **Section 20.0 "Comparator Voltage Reference Module"**.

The internal reference is only available in the mode where four inputs are multiplexed to two comparators (CM2:CM0 = 110). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 19.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (see Section 26.0 "Electrical Characteristics").

#### **19.5 Comparator Outputs**

The comparator outputs are read through the CMCON register. These bits are read-only. The comparator outputs may also be directly output to the RF2 and RF1 I/O pins. When enabled, multiplexers in the output path of the RF2 and RF1 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 19-3 shows the comparator output block diagram.

The TRISF bits will still function as an output enable/ disable for the RF2 and RF1 pins while in this mode.

The polarity of the comparator outputs can be changed using the C2INV and C1INV bits (CMCON<5:4>).

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin defined as a digital input may cause the input buffer to consume more current than is specified.

#### 22.6 Pixel Control

The LCDDATAx registers contain bits which define the state of each pixel. Each bit defines one unique pixel.

Table 22-2 shows the correlation of each bit in the LCDDATAx registers to the respective common and segment signals.

Any LCD pixel location not being used for display can be used as general purpose RAM.

#### 22.7 LCD Frame Frequency

The rate at which the COM and SEG outputs changes is called the LCD frame frequency

#### TABLE 22-4: FRAME FREQUENCY FORMULAS

| Multiplex | Frame Frequency =                    |  |  |  |  |

|-----------|--------------------------------------|--|--|--|--|

| Static    | Clock Source/(4 x 1 x (LP3:LP0 + 1)) |  |  |  |  |

| 1/2       | Clock Source/(2 x 2 x (LP3:LP0 + 1)) |  |  |  |  |

| 1/3       | Clock Source/(1 x 3 x (LP3:LP0 + 1)) |  |  |  |  |

| 1/4       | Clock Source/(1 x 4 x (LP3:LP0 + 1)) |  |  |  |  |

Note: Clock source is (Fosc/4)/8192, Timer1 Osc/32 or INTRC/32.

# TABLE 22-5:APPROXIMATE FRAME<br/>FREQUENCY (IN Hz) USING<br/>Fosc @ 32 MHz,<br/>TIMER1 @ 32.768 kHz OR<br/>INTRC OSCILLATOR

| LP3:LP0 | Static | 1/2 | 1/3 | 1/4 |

|---------|--------|-----|-----|-----|

| 1       | 125    | 125 | 167 | 125 |

| 2       | 83     | 83  | 111 | 83  |

| 3       | 62     | 62  | 83  | 62  |

| 4       | 50     | 50  | 67  | 50  |

| 5       | 42     | 42  | 56  | 42  |

| 6       | 36     | 36  | 48  | 36  |

| 7       | 31     | 31  | 42  | 31  |

#### 22.8 LCD Waveform Generation

LCD waveform generation is based on the philosophy that the net AC voltage across the dark pixel should be maximized and the net AC voltage across the clear pixel should be minimized. The net DC voltage across any pixel should be zero.

The COM signal represents the time slice for each common, while the SEG contains the pixel data.

The pixel signal (COM-SEG) will have no DC component and it can take only one of the two rms values. The higher rms value will create a dark pixel and a lower rms value will create a clear pixel.

As the number of commons increases, the delta between the two rms values decreases. The delta represents the maximum contrast that the display can have.

The LCDs can be driven by two types of waveform: Type-A and Type-B. In Type-A waveform, the phase changes within each common type, whereas in Type-B waveform, the phase changes on each frame boundary. Thus, Type-A waveform maintains 0 VDc over a single frame, whereas Type-B waveform takes two frames.

| Note 1: | If Sleep has to be executed with LCD     |

|---------|------------------------------------------|

|         | Sleep enabled (LCDCON <slpen> is</slpen> |

|         | '1'), then care must be taken to execute |

|         | Sleep only when VDC on all the pixels is |

|         | ʻ0'.                                     |

2: When the LCD clock source is (Fosc/4)/8192, if Sleep is executed irrespective of the LCDCON<SLPEN> setting, the LCD goes into Sleep. Thus, take care to see that VDc on all pixels is '0' when Sleep is executed.

Figure 22-4 through Figure 22-14 provide waveforms for static, half-multiplex, one-third-multiplex and quarter-multiplex drives for Type-A and Type-B waveforms.

| BTG                                                | Bit Toggle f                                                                                             | BOV                                                                                         | Branch if Overflow                                                                                                                                          |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                            | BTG f, b {,a}                                                                                            | Syntax:                                                                                     | BOV n                                                                                                                                                       |

| Operands:                                          | $0 \le f \le 255$                                                                                        | Operands:                                                                                   | $-128 \le n \le 127$                                                                                                                                        |

|                                                    | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                   | Operation:                                                                                  | if Overflow bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                   |

| Operation:                                         | $(\overline{f}\overline{b}) \to f\overline{s}$                                                           | Status Affected:                                                                            | None                                                                                                                                                        |

| Status Affected:                                   | None                                                                                                     | Encoding:                                                                                   | 1110 0100 nnnn nnnn                                                                                                                                         |

| Encoding:<br>Description:                          | 0111 bbba ffff fff<br>Bit 'b' in data memory location 'f' is<br>inverted.                                | Description:                                                                                | If the Overflow bit is '1', then the program will branch.<br>The 2's complement number '2n' is                                                              |

|                                                    | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank. |                                                                                             | added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a |

|                                                    | If 'a' is '0' and the extended instruction set is enabled, this instruction operates                     |                                                                                             | two-cycle instruction.                                                                                                                                      |

|                                                    | in Indexed Literal Offset Addressing                                                                     | Words:                                                                                      | 1                                                                                                                                                           |

|                                                    | mode whenever $f \le 95$ (5Fh). See<br>Section 24.2.3 "Byte-Oriented and                                 | Cycles:                                                                                     | 1(2)                                                                                                                                                        |

|                                                    | Bit-Oriented Instructions in Indexed                                                                     | Q Cycle Activity:                                                                           |                                                                                                                                                             |

|                                                    | Literal Offset Mode" for details.                                                                        | If Jump:                                                                                    |                                                                                                                                                             |

| Words:                                             | 1                                                                                                        | Q1                                                                                          | Q2 Q3 Q4                                                                                                                                                    |

| Cycles:                                            | 1                                                                                                        | Decode                                                                                      | Read literalProcessWrite to PC'n'Data                                                                                                                       |

| Q Cycle Activity:<br>Q1                            | Q2 Q3 Q4                                                                                                 | No                                                                                          | No No No                                                                                                                                                    |

| Decode                                             | Read Process Write                                                                                       | operation                                                                                   | operation operation operation                                                                                                                               |

| Decoue                                             | register 'f' Data register 'f'                                                                           | If No Jump:                                                                                 |                                                                                                                                                             |

|                                                    |                                                                                                          | Q1                                                                                          | Q2 Q3 Q4                                                                                                                                                    |

| Example:                                           | BTG PORTC, 4, 0                                                                                          | Decode                                                                                      | Read literal Process No<br>'n' Data operation                                                                                                               |

| Before Instru<br>PORTC<br>After Instructi<br>PORTC | = 0111 0101 <b>[75h]</b><br>on:                                                                          | Example:<br>Before Instruc<br>PC<br>After Instructi<br>If Overfit<br>PC<br>If Overfit<br>PC | HERE BOV Jump<br>ction<br>= address (HERE)<br>on<br>bw = 1;<br>= address (Jump)<br>bw = 0;                                                                  |

| ΒZ                                         |                          | Branch if                                               | Zero                                                                                                                                                                                                                       |         |                |  |  |

|--------------------------------------------|--------------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|--|--|

| Syntax:                                    |                          | BZ n                                                    | BZ n                                                                                                                                                                                                                       |         |                |  |  |

| Operands:                                  |                          | -128 ≤ n ≤ ′                                            | 127                                                                                                                                                                                                                        |         |                |  |  |

| Operation:                                 |                          |                                                         | if Zero bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                      |         |                |  |  |

| Status Affected:                           |                          | None                                                    | None                                                                                                                                                                                                                       |         |                |  |  |

| Encoding:                                  |                          | 1110                                                    | 0000                                                                                                                                                                                                                       | nnnn    | nnnn           |  |  |

| Description:                               |                          | will branch.                                            | If the Zero bit is '1', then the program will branch.                                                                                                                                                                      |         |                |  |  |

|                                            |                          | added to th<br>incremente<br>instruction,<br>PC + 2 + 2 | The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |         |                |  |  |

| Word                                       | ls:                      | 1                                                       | 1                                                                                                                                                                                                                          |         |                |  |  |

| Cycles:                                    |                          | 1(2)                                                    | 1(2)                                                                                                                                                                                                                       |         |                |  |  |

| QC                                         | ycle Activity:           |                                                         |                                                                                                                                                                                                                            |         |                |  |  |

| lf Ju                                      | imp:                     |                                                         |                                                                                                                                                                                                                            |         |                |  |  |

|                                            | Q1                       | Q2                                                      | Q3                                                                                                                                                                                                                         |         | Q4             |  |  |

|                                            | Decode                   | Read literal<br>'n'                                     | Proces<br>Data                                                                                                                                                                                                             | s Wr    | ite to PC      |  |  |

|                                            | No                       | No                                                      | No                                                                                                                                                                                                                         |         | No             |  |  |

|                                            | operation                | operation                                               | operatio                                                                                                                                                                                                                   | on o    | peration       |  |  |

| lf No                                      | o Jump:                  |                                                         |                                                                                                                                                                                                                            |         |                |  |  |

|                                            | Q1                       | Q2                                                      | Q3                                                                                                                                                                                                                         |         | Q4             |  |  |

|                                            | Decode                   | Read literal<br>'n'                                     | Proces<br>Data                                                                                                                                                                                                             | -       | No<br>peration |  |  |

|                                            |                          |                                                         | Data                                                                                                                                                                                                                       | 0       | Scration       |  |  |