Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | Coldfire V3                                                             |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 240MHz                                                                  |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, SSI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, LCD, PWM, WDT                                                      |

| Number of I/O              | 94                                                                      |

| Program Memory Size        | -                                                                       |

| Program Memory Type        | ROMIess                                                                 |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.4V ~ 3.6V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 256-LBGA                                                                |

| Supplier Device Package    | 256-MAPBGA (17x17)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcf5328cvm240j  |

# **Table of Contents**

| 1 | MCF   | 532x Family Comparison3                             |   |          | 5.7.2 DDR SDRAM AC Timing Characteristics           | 25 |

|---|-------|-----------------------------------------------------|---|----------|-----------------------------------------------------|----|

| 2 |       | ring Information                                    |   | 5.8      | General Purpose I/O Timing                          | 28 |

| 3 | Hard  | ware Design Considerations5                         |   |          | Reset and Configuration Override Timing             |    |

|   | 3.1   | PLL Power Filtering5                                |   |          | LCD Controller Timing Specifications                |    |

|   | 3.2   | USB Power Filtering                                 |   |          | USB On-The-Go                                       |    |

|   | 3.3   | Supply Voltage Sequencing and Separation Cautions 5 |   | 5.12 l   | ULPI Timing Specification                           | 33 |

|   |       | 3.3.1 Power Up Sequence                             |   |          | SSI Timing Specifications                           |    |

|   |       | 3.3.2 Power Down Sequence 6                         |   | 5.14 I   | I <sup>2</sup> C Input/Output Timing Specifications | 35 |

| 4 | Pin A | ssignments and Reset States6                        |   | 5.15 F   | Fast Ethernet AC Timing Specifications              | 37 |

|   | 4.1   | Signal Multiplexing6                                |   | 5        | 5.15.1 MII Receive Signal Timing                    | 37 |

|   | 4.2   | Pinout—256 MAPBGA                                   |   |          | 5.15.2 MII Transmit Signal Timing                   |    |

|   | 4.3   | Pinout—196 MAPBGA                                   |   |          | 5.15.3 MII Async Inputs Signal Timing               | 38 |

| 5 | Elect | rical Characteristics15                             |   |          | 5.15.4 MII Serial Management Channel Timing         | 38 |

|   | 5.1   | Maximum Ratings                                     |   | 5.16     | 32-Bit Timer Module Timing Specifications           | 39 |

|   | 5.2   | Thermal Characteristics                             |   | 5.17     | QSPI Electrical Specifications                      | 39 |

|   | 5.3   | ESD Protection                                      |   | 5.18     | JTAG and Boundary Scan Timing                       | 40 |

|   | 5.4   | DC Electrical Specifications                        |   | 5.19     | Debug AC Timing Specifications                      | 42 |

|   | 5.5   | Oscillator and PLL Electrical Characteristics       | 6 | Curren   | nt Consumption                                      | 42 |

|   | 5.6   | External Interface Timing Characteristics           | 7 | Packag   | ge Information                                      | 45 |

|   |       | 5.6.1 FlexBus                                       |   | 7.1 F    | Package Dimensions—256 MAPBGA                       | 45 |

|   | 5.7   | SDRAM Bus                                           |   | 7.2      | Package Dimensions—196 MAPBGA                       | 46 |

|   |       | 5.7.1 SDR SDRAM AC Timing Characteristics 23        | 8 | Revision | on History                                          | 47 |

## 3 Hardware Design Considerations

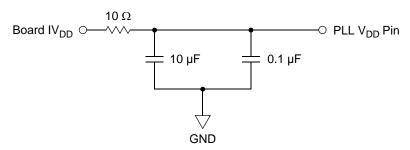

### 3.1 PLL Power Filtering

To further enhance noise isolation, an external filter is strongly recommended for PLL analog  $V_{DD}$  pins. The filter shown in Figure 2 should be connected between the board  $V_{DD}$  and the PLLV<sub>DD</sub> pins. The resistor and capacitors should be placed as close to the dedicated PLLV<sub>DD</sub> pin as possible.

Figure 2. System PLL  $V_{\rm DD}$  Power Filter

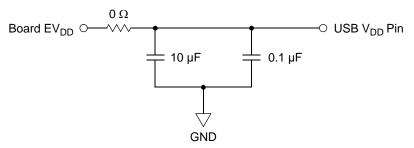

### 3.2 USB Power Filtering

To minimize noise, external filters are required for each of the USB power pins. The filter shown in Figure 3 should be connected between the board  $EV_{DD}$  or  $IV_{DD}$  and each of the USB $V_{DD}$  pins. The resistor and capacitors should be placed as close to the dedicated USB $V_{DD}$  pin as possible.

Figure 3. USB V<sub>DD</sub> Power Filter

#### **NOTE**

In addition to the above filter circuitry, a 0.01 F capacitor is also recommended in parallel with those shown.

## 3.3 Supply Voltage Sequencing and Separation Cautions

The relationship between  $SDV_{DD}$  and  $EV_{DD}$  is non-critical during power-up and power-down sequences.  $SDV_{DD}$  (2.5V or 3.3V) and  $EV_{DD}$  are specified relative to  $IV_{DD}$ .

### 3.3.1 Power Up Sequence

If  $EV_{DD}/SDV_{DD}$  are powered up with  $IV_{DD}$  at 0 V, the sense circuits in the I/O pads cause all pad output drivers connected to the  $EV_{DD}/SDV_{DD}$  to be in a high impedance state. There is no limit on how long after  $EV_{DD}/SDV_{DD}$  powers up before  $IV_{DD}$  must powered up.  $IV_{DD}$  should not lead the  $EV_{DD}$ ,  $SDV_{DD}$ , or  $PLLV_{DD}$  by more than 0.4 V during power ramp-up or there is

#### Pin Assignments and Reset States

high current in the internal ESD protection diodes. The rise times on the power supplies should be slower than 500 us to avoid turning on the internal ESD protection clamp diodes.

### 3.3.2 Power Down Sequence

If  $IV_{DD}/PLLV_{DD}$  are powered down first, sense circuits in the I/O pads cause all output drivers to be in a high impedance state. There is no limit on how long after  $IV_{DD}$  and  $PLLV_{DD}$  power down before  $EV_{DD}$  or  $SDV_{DD}$  must power down.  $IV_{DD}$  should not lag  $EV_{DD}$ ,  $SDV_{DD}$ , or  $PLLV_{DD}$  going low by more than 0.4 V during power down or there is undesired high current in the ESD protection diodes. There are no requirements for the fall times of the power supplies.

The recommended power down sequence is as follows:

- 1. Drop IV<sub>DD</sub>/PLLV<sub>DD</sub> to 0 V.

- 2. Drop EV<sub>DD</sub>/SDV<sub>DD</sub> supplies.

## 4 Pin Assignments and Reset States

### 4.1 Signal Multiplexing

The following table lists all the MCF532*x* pins grouped by function. The Dir column is the direction for the primary function of the pin only. Refer to Section 7, "Package Information," for package diagrams. For a more detailed discussion of the MCF532*x* signals, consult the *MCF5329 Reference Manual* (MCF5329RM).

#### NOTE

In this table and throughout this document, a single signal within a group is designated without square brackets (i.e., A23), while designations for multiple signals within a group use brackets (i.e., A[23:21]) and is meant to include all signals within the two bracketed numbers when these numbers are separated by a colon.

#### NOTE

The primary functionality of a pin is not necessarily its default functionality. Pins that are muxed with GPIO default to their GPIO functionality.

Table 3. MCF5327/8/9 Signal Information and Muxing

| Signal Name        | GPIO  | Alternate 1 | Alternate 2 | Dir.1 | Voltage<br>Domain | MCF5327<br>196<br>MAPBGA | MCF5328<br>256<br>MAPBGA | MCF53281<br>MCF5329<br>256<br>MAPBGA |  |  |  |

|--------------------|-------|-------------|-------------|-------|-------------------|--------------------------|--------------------------|--------------------------------------|--|--|--|

|                    | Reset |             |             |       |                   |                          |                          |                                      |  |  |  |

| RESET <sup>2</sup> | _     | _           | _           | I     | EVDD              | J11                      | N15                      | N15                                  |  |  |  |

| RSTOUT             | _     | _           | _           | 0     | EVDD              | P14                      | P14                      | P14                                  |  |  |  |

|                    |       |             | Clock       |       |                   |                          |                          |                                      |  |  |  |

| EXTAL              | _     | _           | _           | I     | EVDD              | L14                      | P16                      | P16                                  |  |  |  |

| XTAL <sup>2</sup>  | _     | _           | _           | 0     | EVDD              | K14                      | N16                      | N16                                  |  |  |  |

| EXTAL32K           | _     | _           | _           | I     | EVDD              | M11                      | P13                      | P13                                  |  |  |  |

| XTAL32K            | _     | _           | _           | 0     | EVDD              | N11                      | R13                      | R13                                  |  |  |  |

| FB_CLK             | _     | _           | _           | 0     | SDVDD             | L1                       | T2                       | T2                                   |  |  |  |

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

Table 3. MCF5327/8/9 Signal Information and Muxing (continued)

| Signal Name       | GPIO           | Alternate 1              | Alternate 2 | Dir.1 | Voltage<br>Domain | MCF5327<br>196<br>MAPBGA                                     | MCF5328<br>256<br>MAPBGA                                 | MCF53281<br>MCF5329<br>256<br>MAPBGA                     |  |  |  |

|-------------------|----------------|--------------------------|-------------|-------|-------------------|--------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--|--|--|

|                   | Mode Selection |                          |             |       |                   |                                                              |                                                          |                                                          |  |  |  |

| RCON <sup>2</sup> | _              | _                        | _           | I     | EVDD              | M7                                                           | M8                                                       | M8                                                       |  |  |  |

| DRAMSEL           | _              | _                        | _           | I     | EVDD              | G11                                                          | H12                                                      | H12                                                      |  |  |  |

|                   |                |                          | FlexBus     |       |                   |                                                              |                                                          |                                                          |  |  |  |

| A[23:22]          | _              | FB_CS[5:4]               | _           | 0     | SDVDD             | B11,C11                                                      | C13, D13                                                 | C13, D13                                                 |  |  |  |

| A[21:16]          | _              | _                        | _           | 0     | SDVDD             | B12, A12,<br>D11, C12,<br>B13, A13                           | E13, A14,<br>B14, C14,<br>A15, B15                       | E13, A14,<br>B14, C14,<br>A15, B15                       |  |  |  |

| A[15:14]          | _              | SD_BA[1:0] <sup>3</sup>  | _           | 0     | SDVDD             | A14, B14                                                     | D14, B16                                                 | D14, B16                                                 |  |  |  |

| A[13:11]          | _              | SD_A[13:11] <sup>3</sup> | _           | 0     | SDVDD             | C13, C14,<br>D12                                             | C15, C16,<br>D15                                         | C15, C16,<br>D15                                         |  |  |  |

| A10               | _              | _                        | _           | 0     | SDVDD             | D13                                                          | D16                                                      | D16                                                      |  |  |  |

| A[9:0]            | _              | SD_A[9:0] <sup>3</sup>   | _           | 0     | SDVDD             | D14,<br>E11–14,<br>F11–F14,<br>G14                           | E14–E16,<br>F13–F16,<br>G16– G14                         | E14–E16,<br>F13–F16,<br>G16– G14                         |  |  |  |

| D[31:16]          | _              | SD_D[31:16] <sup>4</sup> | _           | I/O   | SDVDD             | H3-H1,<br>J4-J1, K1,<br>L4, M2, M3,<br>N1, N2, P1,<br>P2, N3 | M1–M4,<br>N1–N4, T3,<br>P4, R4, T4,<br>N5, P5, R5,<br>T5 | M1–M4,<br>N1–N4, T3,<br>P4, R4, T4,<br>N5, P5, R5,<br>T5 |  |  |  |

| D[15:1]           | _              | FB_D[31:17] <sup>4</sup> | _           | I/O   | SDVDD             | F4–F1,<br>G5–G2, L5,<br>N4, P4, M5,<br>N5, P5, L6            | J3–J1,<br>K4–K1, L2,<br>R6, N7, P7,<br>R7, T7, P8,<br>R8 | J3–J1,<br>K4–K1, L2,<br>R6, N7, P7,<br>R7, T7, P8,<br>R8 |  |  |  |

| D0 <sup>2</sup>   | _              | FB_D[16] <sup>4</sup>    | _           | I/O   | SDVDD             | M6                                                           | Т8                                                       | T8                                                       |  |  |  |

| BE/BWE[3:0]       | PBE[3:0]       | SD_DQM[3:0] <sup>3</sup> | _           | 0     | SDVDD             | H4, P3, G1,<br>M4                                            | L4, P6, L3,<br>N6                                        | L4, P6, L3,<br>N6                                        |  |  |  |

| ŌĒ                | PBUSCTL3       | _                        | _           | 0     | SDVDD             | P6                                                           | R9                                                       | R9                                                       |  |  |  |

| TA <sup>2</sup>   | PBUSCTL2       | _                        | _           | I     | SDVDD             | G13                                                          | G13                                                      | G13                                                      |  |  |  |

| R/W               | PBUSCTL1       | _                        | _           | 0     | SDVDD             | N6                                                           | N8                                                       | N8                                                       |  |  |  |

| TS                | PBUSCTL0       | DACK0                    | _           | 0     | SDVDD             | D2                                                           | H4                                                       | H4                                                       |  |  |  |

|                   |                |                          | Chip Selec  | ts    |                   |                                                              |                                                          |                                                          |  |  |  |

| FB_CS[5:4]        | PCS[5:4]       | _                        | _           | 0     | SDVDD             | _                                                            | B13, A13                                                 | B13, A13                                                 |  |  |  |

| FB_CS[3:1]        | PCS[3:1]       |                          |             | 0     | SDVDD             | A11, D10,<br>C10                                             | A12, B12,<br>C12                                         | A12, B12,<br>C12                                         |  |  |  |

| FB_CS0            | _              | _                        | _           | 0     | SDVDD             | B10                                                          | D12                                                      | D12                                                      |  |  |  |

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

#### Pin Assignments and Reset States

Table 3. MCF5327/8/9 Signal Information and Muxing (continued)

| Signal Name           | GPIO | Alternate 1 | Alternate 2 | Dir.1 | Voltage<br>Domain | MCF5327<br>196<br>MAPBGA                        | MCF5328<br>256<br>MAPBGA                                                 | MCF53281<br>MCF5329<br>256<br>MAPBGA                                     |

|-----------------------|------|-------------|-------------|-------|-------------------|-------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|

| PST[3:0]              | _    |             | _           | 0     | EVDD              | N8, P8, L9,<br>M9                               | R10, T10,<br>R11, T11                                                    | R10, T10,<br>R11, T11                                                    |

|                       |      |             | Test        |       |                   |                                                 |                                                                          |                                                                          |

| TEST <sup>7</sup>     | _    | _           | _           | I     | EVDD              | E10                                             | A16                                                                      | A16                                                                      |

| PLL_TEST <sup>8</sup> | _    | _           | _           | I     | EVDD              | _                                               | N13                                                                      | N13                                                                      |

|                       |      |             | Power Suppl | lies  |                   |                                                 |                                                                          |                                                                          |

| EVDD                  | _    | _           | _           | _     | _                 | E6, E7,<br>F5–F7, H9,<br>J8, J9, K8,<br>K9, K11 | E8, F5–F8,<br>G5, G6, H5,<br>H6, J11,<br>K11, K12,<br>L9–L11, M9,<br>M10 | E8, F5–F8,<br>G5, G6, H5,<br>H6, J11,<br>K11, K12,<br>L9–L11, M9,<br>M10 |

| IVDD                  | _    |             | _           | _     | _                 | E5, K5, K10,<br>J10                             | E5, G12, M5,<br>M11, M12                                                 | E5, G12, M5,<br>M11, M12                                                 |

| PLL_VDD               | _    | _           | _           | _     | _                 | H10                                             | J12                                                                      | J12                                                                      |

| SD_VDD                | -    | _           | _           | _     | _                 | – E8, E9,<br>F8–F10,<br>J5–J7, K7               | E9, F9–F11,<br>G11, H11,<br>J5, J6, K5,<br>K6, L5–L8,<br>M6, M7          | E9, F9-F11,<br>G11, H11,<br>J5, J6, K5,<br>K6, L5-L8,<br>M6, M7          |

| USB_VDD               | _    | _           | _           | _     | _                 | G10                                             | L14                                                                      | L14                                                                      |

| VSS                   | _    | _           | _           | _     | _                 | G6–G9,<br>H6–H8, P9                             | G7-G10,<br>H7-H10,<br>J7-10,<br>K7-K10,<br>L12, L13                      | G7-G10,<br>H7-H10,<br>J7-10,<br>K7-K10,<br>L12, L13                      |

| PLL_VSS               | _    | _           | _           | _     | _                 | H11                                             | K13                                                                      | K13                                                                      |

| USB_VSS               |      | _           | _           | _     |                   | H12                                             | M14                                                                      | M14                                                                      |

<sup>&</sup>lt;sup>1</sup> Refers to pin's primary function.

### MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

<sup>&</sup>lt;sup>2</sup> Pull-up enabled internally on this signal for this mode.

<sup>&</sup>lt;sup>3</sup> The SDRAM functions of these signals are not programmable by the user. They are dynamically switched by the processor when accessing SDRAM memory space and are included here for completeness.

Primary functionality selected by asserting the DRAMSEL signal (SDR mode). Alternate functionality selected by negating the DRAMSEL signal (DDR mode). The GPIO module is not responsible for assigning these pins.

<sup>&</sup>lt;sup>5</sup> GPIO functionality is determined by the edge port module. The GPIO module is only responsible for assigning the alternate functions.

<sup>&</sup>lt;sup>6</sup> If JTAG\_EN is asserted, these pins default to Alternate 1 (JTAG) functionality. The GPIO module is not responsible for assigning these pins.

<sup>&</sup>lt;sup>7</sup> Pull-down enabled internally on this signal for this mode.

<sup>&</sup>lt;sup>8</sup> Must be left floating for proper operation of the PLL.

**Table 7. DC Electrical Specifications (continued)**

| Characteristic                                                                                                                                                                                                     | Symbol            | Min                                    | Max               | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------|-------------------|------|

| SDRAM and FlexBus Output High Voltage Mobile DDR/Bus Input High Voltage (nominal 1.8V) DDR/Bus Pad Supply Voltage (nominal 2.5V) SDR/Bus Pad Supply Voltage (nominal 3.3V) I <sub>OH</sub> = -5.0 mA for all modes | SDV <sub>OH</sub> | SDV <sub>DD</sub> - 0.35<br>2.1<br>2.4 | = =               | V    |

| SDRAM and FlexBus Output Low Voltage Mobile DDR/Bus Input High Voltage (nominal 1.8V) DDR/Bus Pad Supply Voltage (nominal 2.5V) SDR/Bus Pad Supply Voltage (nominal 3.3V) I <sub>OL</sub> = 5.0 mA for all modes   | SDV <sub>OL</sub> | _<br>_<br>_                            | 0.3<br>0.3<br>0.5 | V    |

| Input Leakage Current V <sub>in</sub> = V <sub>DD</sub> or V <sub>SS</sub> , Input-only pins                                                                                                                       | I <sub>in</sub>   | -1.0                                   | 1.0               | μА   |

| Weak Internal Pull-Up Device Current, tested at V <sub>IL</sub> Max. <sup>1</sup>                                                                                                                                  | I <sub>APU</sub>  | -10                                    | -130              | μΑ   |

| Input Capacitance <sup>2</sup> All input-only pins All input/output (three-state) pins                                                                                                                             | C <sub>in</sub>   | _                                      | 7<br>7            | pF   |

#### **Oscillator and PLL Electrical Characteristics** 5.5

**Table 8. PLL Electrical Characteristics**

| Num | Characteristic                                                                            | Symbol                                           | Min.<br>Value                                        | Max.<br>Value                                        | Unit       |

|-----|-------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------|

| 1   | PLL Reference Frequency Range Crystal reference External reference                        | f <sub>ref_crystal</sub><br>f <sub>ref_ext</sub> | 12<br>12                                             | 25 <sup>1</sup><br>40 <sup>1</sup>                   | MHz<br>MHz |

| 2   | Core frequency<br>CLKOUT Frequency <sup>2</sup>                                           | f <sub>sys</sub><br>f <sub>sys/3</sub>           | 488 x 10 <sup>-6</sup><br>163 x 10 <sup>-6</sup>     | 240<br>80                                            | MHz<br>MHz |

| 3   | Crystal Start-up Time <sup>3, 4</sup>                                                     | t <sub>cst</sub>                                 | _                                                    | 10                                                   | ms         |

| 4   | EXTAL Input High Voltage<br>Crystal Mode <sup>5</sup><br>All other modes (External, Limp) | V <sub>IHEXT</sub><br>V <sub>IHEXT</sub>         | V <sub>XTAL</sub> + 0.4<br>E <sub>VDD</sub> /2 + 0.4 | _<br>_                                               | V<br>V     |

| 5   | EXTAL Input Low Voltage<br>Crystal Mode <sup>5</sup><br>All other modes (External, Limp)  | V <sub>ILEXT</sub><br>V <sub>ILEXT</sub>         | _                                                    | V <sub>XTAL</sub> – 0.4<br>E <sub>VDD</sub> /2 – 0.4 | V<br>V     |

| 7   | PLL Lock Time <sup>3, 6</sup>                                                             | t <sub>lpII</sub>                                | _                                                    | 50000                                                | CLKIN      |

| 8   | Duty Cycle of reference <sup>3</sup>                                                      | t <sub>dc</sub>                                  | 40                                                   | 60                                                   | %          |

| 9   | XTAL Current                                                                              | I <sub>XTAL</sub>                                | 1                                                    | 3                                                    | mA         |

| 10  | Total on-chip stray capacitance on XTAL                                                   | C <sub>S_XTAL</sub>                              |                                                      | 1.5                                                  | pF         |

| 11  | Total on-chip stray capacitance on EXTAL                                                  | C <sub>S_EXTAL</sub>                             |                                                      | 1.5                                                  | pF         |

Refer to the signals section for pins having weak internal pull-up devices. This parameter is characterized before qualification rather than 100% tested.

**Table 8. PLL Electrical Characteristics (continued)**

| Num | Characteristic                                                                                                                                        | Symbol               | Min.<br>Value | Max.<br>Value                                                                     | Unit                                         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|-----------------------------------------------------------------------------------|----------------------------------------------|

| 12  | Crystal capacitive load                                                                                                                               | C <sub>L</sub>       |               | See crystal spec                                                                  |                                              |

| 13  | Discrete load capacitance for XTAL                                                                                                                    | C <sub>L_XTAL</sub>  |               | 2*C <sub>L</sub> -<br>C <sub>S_XTAL</sub> -<br>C <sub>PCB_XTAL</sub> <sup>7</sup> | pF                                           |

| 14  | Discrete load capacitance for EXTAL                                                                                                                   | C <sub>L_EXTAL</sub> |               | 2*C <sub>L</sub><br>C <sub>S_EXTAL</sub> -<br>C <sub>PCB_EXTAL</sub> <sup>7</sup> | pF                                           |

| 17  | CLKOUT Period Jitter, <sup>3, 4, 7, 8, 9</sup> Measured at f <sub>SYS</sub> Max<br>Peak-to-peak Jitter (Clock edge to clock edge)<br>Long Term Jitter | C <sub>jitter</sub>  |               | 10<br>TBD                                                                         | % f <sub>sys/3</sub><br>% f <sub>sys/3</sub> |

| 18  | Frequency Modulation Range Limit <sup>3, 10, 11</sup> (f <sub>sys</sub> Max must not be exceeded)                                                     | C <sub>mod</sub>     | 0.8           | 2.2                                                                               | %f <sub>sys/3</sub>                          |

| 19  | VCO Frequency. f <sub>vco</sub> = (f <sub>ref *</sub> PFD)/4                                                                                          | f <sub>vco</sub>     | 350           | 540                                                                               | MHz                                          |

The maximum allowable input clock frequency when booting with the PLL enabled is 24MHz. For higher input clock frequencies the processor must boot in LIMP mode to avoid violating the maximum allowable CPU frequency.

## 5.6 External Interface Timing Characteristics

Table 9 lists processor bus input timings.

#### NOTE

All processor bus timings are synchronous; that is, input setup/hold and output delay with respect to the rising edge of a reference clock. The reference clock is the FB\_CLK output.

All other timing relationships can be derived from these values. Timings listed in Table 9 are shown in Figure 7 and Figure 8.

<sup>&</sup>lt;sup>2</sup> All internal registers retain data at 0 Hz.

<sup>&</sup>lt;sup>3</sup> This parameter is guaranteed by characterization before qualification rather than 100% tested.

Proper PC board layout procedures must be followed to achieve specifications.

<sup>&</sup>lt;sup>5</sup> This parameter is guaranteed by design rather than 100% tested.

<sup>&</sup>lt;sup>6</sup> This specification is the PLL lock time only and does not include oscillator start-up time.

$<sup>^{7}</sup>$  C<sub>PCB EXTAL</sub> and C<sub>PCB\_XTAL</sub> are the measured PCB stray capacitances on EXTAL and XTAL, respectively.

Jitter is the average deviation from the programmed frequency measured over the specified interval at maximum f<sub>sys</sub>. Measurements are made with the device powered by filtered supplies and clocked by a stable external clock signal. Noise injected into the PLL circuitry via PLL V<sub>DD</sub>, EV<sub>DD</sub>, and V<sub>SS</sub> and variation in crystal oscillator frequency increase the Cjitter percentage for a given interval.

<sup>&</sup>lt;sup>9</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of Cjitter+Cmod.

<sup>&</sup>lt;sup>10</sup> Modulation percentage applies over an interval of 10 μs, or equivalently the modulation rate is 100 KHz.

<sup>&</sup>lt;sup>11</sup> Modulation range determined by hardware design.

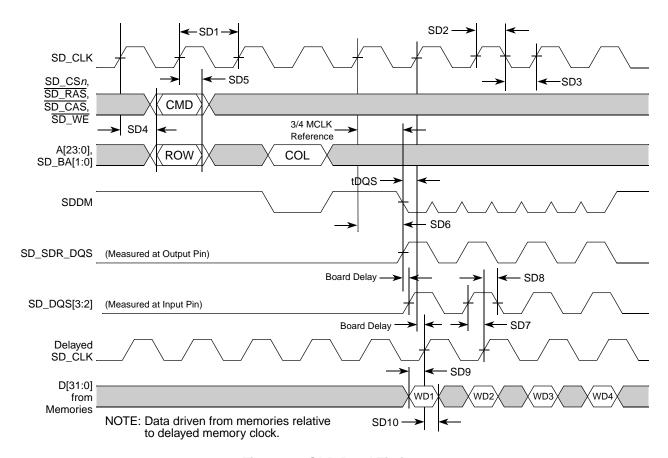

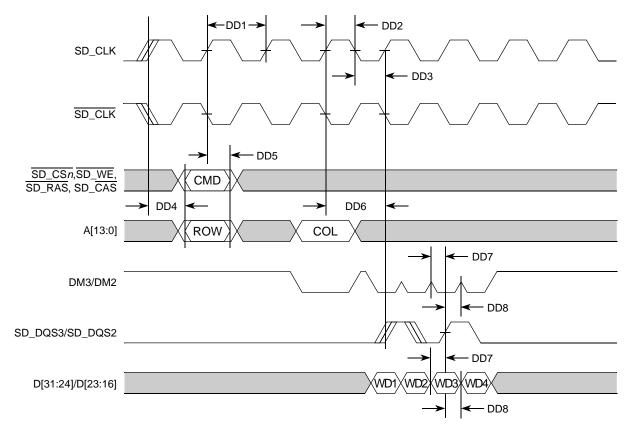

Figure 10. SDR Read Timing

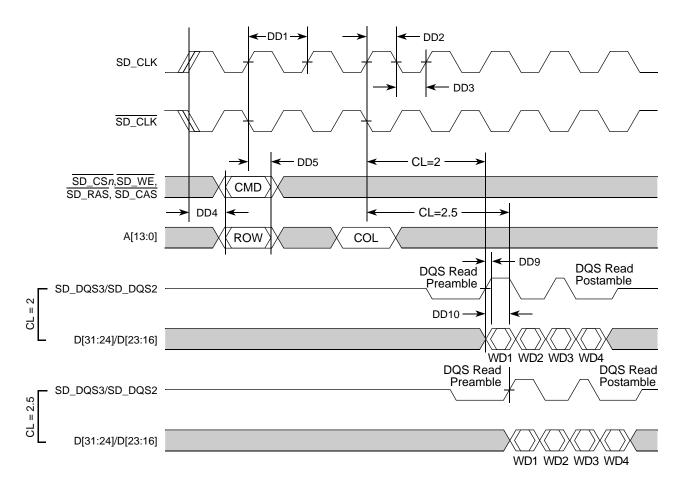

### 5.7.2 DDR SDRAM AC Timing Characteristics

When using the SDRAM controller in DDR mode, the following timing numbers must be followed to properly latch or drive data onto the memory bus. All timing numbers are relative to the four DQS byte lanes.

| Num | Characteristic                                                                            | Symbol               | Min  | Max                   | Unit   |

|-----|-------------------------------------------------------------------------------------------|----------------------|------|-----------------------|--------|

| •   | Frequency of Operation                                                                    | t <sub>DDCK</sub>    | 60   | 80                    | Mhz    |

| DD1 | Clock Period <sup>1</sup>                                                                 | t <sub>DDSK</sub>    | 12.5 | 16.67                 | ns     |

| DD2 | Pulse Width High <sup>2</sup>                                                             | t <sub>DDCKH</sub>   | 0.45 | 0.55                  | SD_CLK |

| DD3 | Pulse Width Low <sup>3</sup>                                                              | t <sub>DDCKL</sub>   | 0.45 | 0.55                  | SD_CLK |

| DD4 | Address, SD_CKE, SD_CAS, SD_RAS, SD_WE, SD_CS[1:0] - Output Valid <sup>3</sup>            | t <sub>SDCHACV</sub> | _    | 0.5 × SD_CLK<br>+ 1.0 | ns     |

| DD5 | Address, SD_CKE, SD_CAS, SD_RAS, SD_WE, SD_CS[1:0] - Output Hold                          | t <sub>SDCHACI</sub> | 2.0  | _                     | ns     |

| DD6 | Write Command to first DQS Latching Transition                                            | t <sub>CMDVDQ</sub>  | _    | 1.25                  | SD_CLK |

| DD7 | Data and Data Mask Output Setup (DQ>DQS) Relative to DQS (DDR Write Mode) <sup>4, 5</sup> | t <sub>DQDMV</sub>   | 1.5  | _                     | ns     |

**Table 11. DDR Timing Specifications**

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

Figure 11. DDR Write Timing

Figure 12. DDR Read Timing

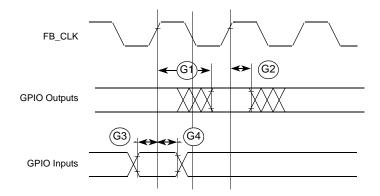

## 5.8 General Purpose I/O Timing

Table 12. GPIO Timing<sup>1</sup>

| Num | Characteristic                     | Symbol             | Min | Max | Unit |

|-----|------------------------------------|--------------------|-----|-----|------|

| G1  | FB_CLK High to GPIO Output Valid   | t <sub>CHPOV</sub> | _   | 10  | ns   |

| G2  | FB_CLK High to GPIO Output Invalid | t <sub>CHPOI</sub> | 1.5 | _   | ns   |

| G3  | GPIO Input Valid to FB_CLK High    | t <sub>PVCH</sub>  | 9   | _   | ns   |

| G4  | FB_CLK High to GPIO Input Invalid  | t <sub>CHPI</sub>  | 1.5 | 1   | ns   |

$<sup>\</sup>overline{}^1$  GPIO pins include:  $\overline{IRQn}$ , PWM, UART, FlexCAN, and Timer pins.

Figure 13. GPIO Timing

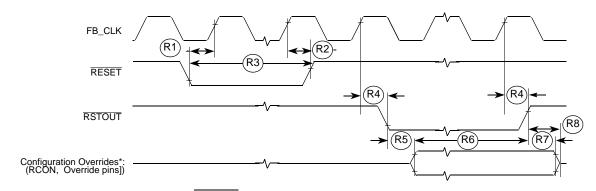

## 5.9 Reset and Configuration Override Timing

**Table 13. Reset and Configuration Override Timing**

| Num | Characteristic                                          | Symbol             | Min | Max | Unit             |

|-----|---------------------------------------------------------|--------------------|-----|-----|------------------|

| R1  | RESET Input valid to FB_CLK High                        | t <sub>RVCH</sub>  | 9   | _   | ns               |

| R2  | FB_CLK High to RESET Input invalid                      | t <sub>CHRI</sub>  | 1.5 | _   | ns               |

| R3  | RESET Input valid Time <sup>1</sup>                     | t <sub>RIVT</sub>  | 5   | _   | t <sub>CYC</sub> |

| R4  | FB_CLK High to RSTOUT Valid                             | t <sub>CHROV</sub> | _   | 10  | ns               |

| R5  | RSTOUT valid to Config. Overrides valid                 | t <sub>ROVCV</sub> | 0   | _   | ns               |

| R6  | Configuration Override Setup Time to RSTOUT invalid     | t <sub>cos</sub>   | 20  | _   | t <sub>CYC</sub> |

| R7  | Configuration Override Hold Time after RSTOUT invalid   | t <sub>COH</sub>   | 0   | _   | ns               |

| R8  | RSTOUT invalid to Configuration Override High Impedance | t <sub>ROICZ</sub> | _   | 1   | t <sub>CYC</sub> |

During low power STOP, the synchronizers for the RESET input are bypassed and RESET is asserted asynchronously to the system. Thus, RESET must be held a minimum of 100 ns.

Figure 14. RESET and Configuration Override Timing

### **NOTE**

Refer to the CCM chapter of the MCF5329 Reference Manual for more information.

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

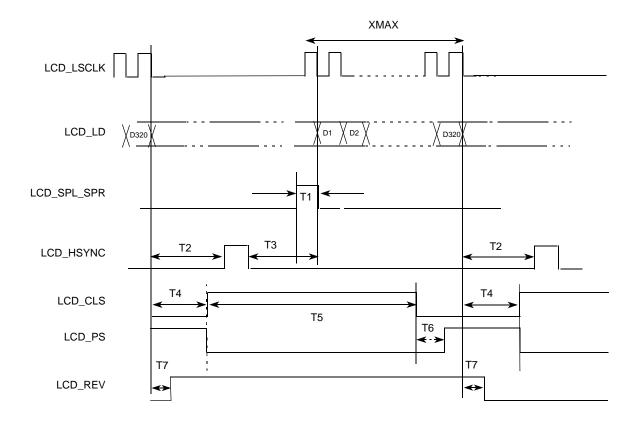

| Number | Description                             | Minimum    | Value                  | Unit |

|--------|-----------------------------------------|------------|------------------------|------|

| T1     | End of LCD_OE to beginning of LCD_VSYNC | T5+T6+T7-1 | (VWAIT1·T2)+T5+T6+T7-1 | Ts   |

| T2     | LCD_HSYNC period                        | _          | XMAX+T5+T6+T7          | Ts   |

| Т3     | LCD_VSYNC pulse width                   | T2         | VWIDTH-T2              | Ts   |

| T4     | End of LCD_VSYNC to beginning of LCD_OE | 1          | (VWAIT2·T2)+1          | Ts   |

| T5     | LCD_HSYNC pulse width                   | 1          | HWIDTH+1               | Ts   |

| T6     | End of LCD_HSYNC to beginning to LCD_OE | 3          | HWAIT2+3               | Ts   |

| T7     | End of LCD_OE to beginning of LCD_HSYNC | 1          | HWAIT1+1               | Ts   |

Note: Ts is the LCD\_LSCLK period. LCD\_VSYNC, LCD\_HSYNC and LCD\_OE can be programmed as active high or active low. In Figure 16, all 3 signals are active low. LCD\_LSCLK can be programmed to be deactivated during the LCD\_VSYNC pulse or the LCD\_OE deasserted period. In Figure 16, LCD\_LSCLK is always active.

Note: XMAX is defined in number of pixels in one line.

Figure 17. Sharp TFT Panel Timing

### 5.11 USB On-The-Go

The MCF5329 device is compliant with industry standard USB 2.0 specification.

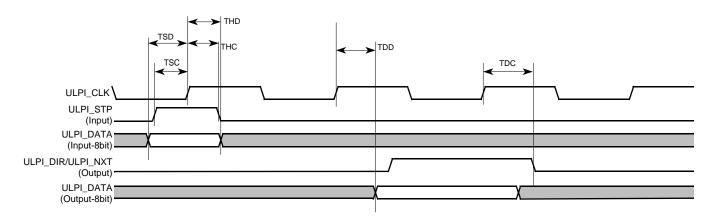

### 5.12 ULPI Timing Specification

Control and data timing requirements for the ULPI pins are given in Table 18. These timings apply in synchronous mode only. All timings are measured with either a 60 MHz input clock from the USB\_CLKIN pin. The USB\_CLKIN needs to maintain a 50% duty cycle. Control signals and 8-bit data are always clocked on the rising edge.

The ULPI interface on the MCF5329 processor is compliant with the industry standard definition.

Figure 19. ULPI Timing Diagram

**Table 18. ULPI Interface Timing**

| Parameter                                  | Symbol   | Min  | Max | Units |

|--------------------------------------------|----------|------|-----|-------|

| Setup time (control in, 8-bit data in)     | TSC, TSD | _    | 3.0 | ns    |

| Hold time (control in, 8-bit data in)      | THC, THD | -1.5 | _   | ns    |

| Output delay (control out, 8-bit data out) | TDC, TDD | _    | 6.0 | ns    |

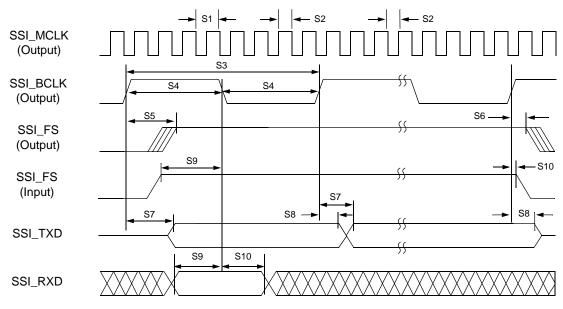

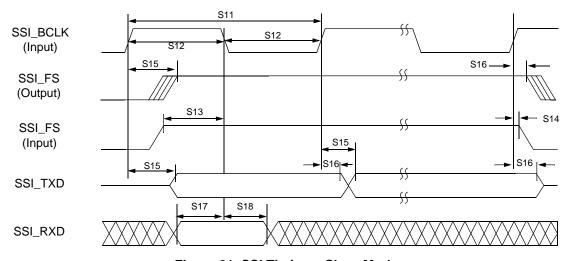

## 5.13 SSI Timing Specifications

This section provides the AC timings for the SSI in master (clocks driven) and slave modes (clocks input). All timings are given for non-inverted serial clock polarity (SSI\_TCR[TSCKP] = 0, SSI\_RCR[RSCKP] = 0) and a non-inverted frame sync (SSI\_TCR[TFSI] = 0, SSI\_RCR[RFSI] = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timings remain valid by inverting the clock signal (SSI\_BCLK) and/or the frame sync (SSI\_FS) shown in the figures below.

Table 19. SSI Timing – Master Modes<sup>1</sup>

| Num | Description                      | Symbol            | Min                | Max | Units             |

|-----|----------------------------------|-------------------|--------------------|-----|-------------------|

| S1  | SSI_MCLK cycle time <sup>2</sup> | t <sub>MCLK</sub> | $8 \times t_{SYS}$ | _   | ns                |

| S2  | SSI_MCLK pulse width high / low  |                   | 45%                | 55% | t <sub>MCLK</sub> |

| S3  | SSI_BCLK cycle time <sup>3</sup> | t <sub>BCLK</sub> | $8 \times t_{SYS}$ | _   | ns                |

| S4  | SSI_BCLK pulse width             |                   | 45%                | 55% | t <sub>BCLK</sub> |

| S5  | SSI_BCLK to SSI_FS output valid  |                   | _                  | 15  | ns                |

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

Figure 20. SSI Timing - Master Modes

Figure 21. SSI Timing - Slave Modes

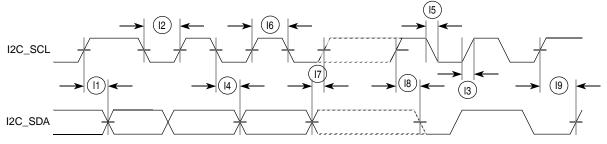

# 5.14 I<sup>2</sup>C Input/Output Timing Specifications

Table 21 lists specifications for the I<sup>2</sup>C input timing parameters shown in Figure 22.

Table 21. I<sup>2</sup>C Input Timing Specifications between SCL and SDA

| Num | Characteristic                                                                    | Min | Max | Units            |

|-----|-----------------------------------------------------------------------------------|-----|-----|------------------|

| I1  | Start condition hold time                                                         | 2   | _   | t <sub>cyc</sub> |

| 12  | Clock low period                                                                  | 8   | _   | t <sub>cyc</sub> |

| 13  | I2C_SCL/I2C_SDA rise time ( $V_{IL} = 0.5 \text{ V to } V_{IH} = 2.4 \text{ V}$ ) | _   | 1   | ms               |

| 14  | Data hold time                                                                    | 0   |     | ns               |

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

Table 21. I<sup>2</sup>C Input Timing Specifications between SCL and SDA (continued)

| Num | Characteristic                                                                    | Min | Max | Units            |

|-----|-----------------------------------------------------------------------------------|-----|-----|------------------|

| 15  | I2C_SCL/I2C_SDA fall time ( $V_{IH} = 2.4 \text{ V to } V_{IL} = 0.5 \text{ V}$ ) | _   | 1   | ms               |

| 16  | Clock high time                                                                   | 4   | _   | t <sub>cyc</sub> |

| 17  | Data setup time                                                                   | 0   | _   | ns               |

| 18  | Start condition setup time (for repeated start condition only)                    | 2   | _   | t <sub>cyc</sub> |

| 19  | Stop condition setup time                                                         | 2   | _   | t <sub>cyc</sub> |

Table 22 lists specifications for the I<sup>2</sup>C output timing parameters shown in Figure 22.

Table 22. I<sup>2</sup>C Output Timing Specifications between SCL and SDA

| Num             | Characteristic                                                                    | Min | Max | Units            |

|-----------------|-----------------------------------------------------------------------------------|-----|-----|------------------|

| 11 <sup>1</sup> | Start condition hold time                                                         | 6   | _   | t <sub>cyc</sub> |

| I2 <sup>1</sup> | Clock low period                                                                  | 10  | _   | t <sub>cyc</sub> |

| I3 <sup>2</sup> | I2C_SCL/I2C_SDA rise time ( $V_{IL} = 0.5 \text{ V to } V_{IH} = 2.4 \text{ V}$ ) | _   | _   | μs               |

| I4 <sup>1</sup> | Data hold time                                                                    | 7   | _   | t <sub>cyc</sub> |

| I5 <sup>3</sup> | I2C_SCL/I2C_SDA fall time ( $V_{IH} = 2.4 \text{ V to } V_{IL} = 0.5 \text{ V}$ ) | _   | 3   | ns               |

| I6 <sup>1</sup> | Clock high time                                                                   | 10  | _   | t <sub>cyc</sub> |

| I7 <sup>1</sup> | Data setup time                                                                   | 2   | _   | t <sub>cyc</sub> |

| I8 <sup>1</sup> | Start condition setup time (for repeated start condition only)                    | 20  | _   | t <sub>cyc</sub> |

| I9 <sup>1</sup> | Stop condition setup time                                                         | 10  | _   | t <sub>cyc</sub> |

Output numbers depend on the value programmed into the IFDR; an IFDR programmed with the maximum frequency (IFDR = 0x20) results in minimum output timings as shown in Table 22. The I<sup>2</sup>C interface is designed to scale the actual data transition time to move it to the middle of the SCL low period. The actual position is affected by the prescale and division values programmed into the IFDR; however, the numbers given in Table 22 are minimum values.

Figure 22 shows timing for the values in Table 22 and Table 21.

Figure 22. I<sup>2</sup>C Input/Output Timings

MCF532x ColdFire® Microprocessor Data Sheet, Rev. 5

Because I2C\_SCL and I2C\_SDA are open-collector-type outputs, which the processor can only actively drive low, the time I2C\_SCL or I2C\_SDA take to reach a high level depends on external signal capacitance and pull-up resistor values.

<sup>&</sup>lt;sup>3</sup> Specified at a nominal 50-pF load.

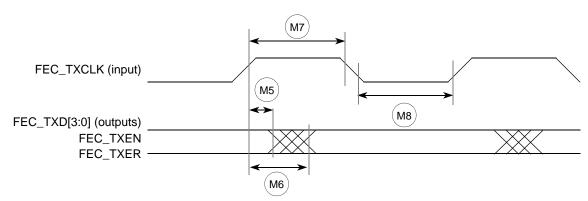

Figure 24. MII Transmit Signal Timing Diagram

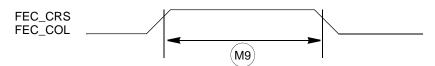

### 5.15.3 MII Async Inputs Signal Timing

Table 25 lists MII asynchronous inputs signal timing.

**Table 25. MII Async Inputs Signal Timing**

|   | Num | Characteristic                       | Min | Max | Unit             |

|---|-----|--------------------------------------|-----|-----|------------------|

| Ī | M9  | FEC_CRS, FEC_COL minimum pulse width | 1.5 | _   | FEC_TXCLK period |

Figure 25. MII Async Inputs Timing Diagram

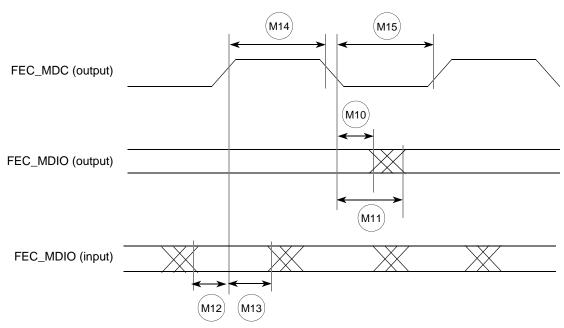

## 5.15.4 MII Serial Management Channel Timing

Table 26 lists MII serial management channel timings. The FEC functions correctly with a maximum MDC frequency of 2.5 MHz.

**Table 26. MII Serial Management Channel Timing**

| Num | Characteristic                                                              | Min | Max | Unit           |

|-----|-----------------------------------------------------------------------------|-----|-----|----------------|

| M10 | FEC_MDC falling edge to FEC_MDIO output invalid (minimum propagation delay) | 0   | _   | ns             |

| M11 | FEC_MDC falling edge to FEC_MDIO output valid (max prop delay)              | _   | 25  | ns             |

| M12 | FEC_MDIO (input) to FEC_MDC rising edge setup                               | 10  | _   | ns             |

| M13 | FEC_MDIO (input) to FEC_MDC rising edge hold                                | 0   | _   | ns             |

| M14 | FEC_MDC pulse width high                                                    | 40% | 60% | FEC_MDC period |

| M15 | FEC_MDC pulse width low                                                     | 40% | 60% | FEC_MDC period |

Figure 26. MII Serial Management Channel Timing Diagram

### 5.16 32-Bit Timer Module Timing Specifications

Table 27 lists timer module AC timings.

**Table 27. Timer Module AC Timing Specifications**

| Name | Characteristic                            | Min | Max | Unit             |

|------|-------------------------------------------|-----|-----|------------------|

| T1   | DT0IN / DT1IN / DT2IN / DT3IN cycle time  | 3   | _   | t <sub>CYC</sub> |

| T2   | DT0IN / DT1IN / DT2IN / DT3IN pulse width | 1   | _   | t <sub>CYC</sub> |

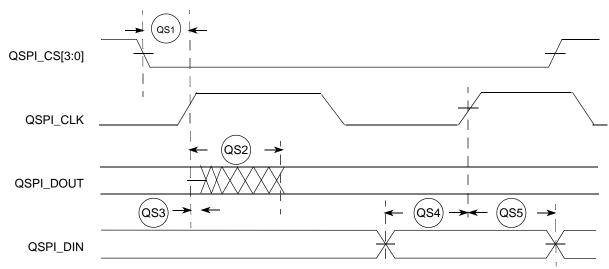

## 5.17 QSPI Electrical Specifications

Table 28 lists QSPI timings.

**Table 28. QSPI Modules AC Timing Specifications**

| Name | Characteristic                                    | Min | Max | Unit             |

|------|---------------------------------------------------|-----|-----|------------------|

| QS1  | QSPI_CS[3:0] to QSPI_CLK                          | 1   | 510 | t <sub>CYC</sub> |

| QS2  | QSPI_CLK high to QSPI_DOUT valid.                 | _   | 10  | ns               |

| QS3  | QSPI_CLK high to QSPI_DOUT invalid. (Output hold) | 2   | _   | ns               |

| QS4  | QSPI_DIN to QSPI_CLK (Input setup)                | 9   | _   | ns               |

| QS5  | QSPI_DIN to QSPI_CLK (Input hold)                 | 9   | _   | ns               |

Figure 27. QSPI Timing

# 5.18 JTAG and Boundary Scan Timing

**Table 29. JTAG and Boundary Scan Timing**

| Num | Characteristics <sup>1</sup>                       | Symbol              | Min | Max | Unit               |

|-----|----------------------------------------------------|---------------------|-----|-----|--------------------|

| J1  | TCLK Frequency of Operation                        | f <sub>JCYC</sub>   | DC  | 1/4 | f <sub>sys/3</sub> |

| J2  | TCLK Cycle Period                                  | t <sub>JCYC</sub>   | 4   | _   | t <sub>CYC</sub>   |

| J3  | TCLK Clock Pulse Width                             | t <sub>JCW</sub>    | 26  | _   | ns                 |

| J4  | TCLK Rise and Fall Times                           | t <sub>JCRF</sub>   | 0   | 3   | ns                 |

| J5  | Boundary Scan Input Data Setup Time to TCLK Rise   | t <sub>BSDST</sub>  | 4   | _   | ns                 |

| J6  | Boundary Scan Input Data Hold Time after TCLK Rise | t <sub>BSDHT</sub>  | 26  | _   | ns                 |

| J7  | TCLK Low to Boundary Scan Output Data Valid        | t <sub>BSDV</sub>   | 0   | 33  | ns                 |

| J8  | TCLK Low to Boundary Scan Output High Z            | t <sub>BSDZ</sub>   | 0   | 33  | ns                 |

| J9  | TMS, TDI Input Data Setup Time to TCLK Rise        | t <sub>TAPBST</sub> | 4   | _   | ns                 |

| J10 | TMS, TDI Input Data Hold Time after TCLK Rise      | t <sub>TAPBHT</sub> | 10  | _   | ns                 |

| J11 | TCLK Low to TDO Data Valid                         | t <sub>TDODV</sub>  | 0   | 26  | ns                 |

| J12 | TCLK Low to TDO High Z                             | t <sub>TDODZ</sub>  | 0   | 8   | ns                 |

| J13 | TRST Assert Time                                   | t <sub>TRSTAT</sub> | 100 |     | ns                 |

| J14 | TRST Setup Time (Negation) to TCLK High            | t <sub>TRSTST</sub> | 10  |     | ns                 |

<sup>&</sup>lt;sup>1</sup> JTAG\_EN is expected to be a static signal. Hence, specific timing is not associated with it.

# **8** Revision History

Table 33. MCF5329DS Document Revision History

| Rev. No. | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Date of Release |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11/2005         |

| 0.1      | <ul> <li>Added not to Section 7, "Package Information."</li> <li>Added top view and bottom view where appropriate in mechanical drawings and pinout figures.</li> <li>Figure 6: Corrected "FB_CLK (75MHz)" label to "FB_CLK (80MHz)"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3/2006          |

| 1        | <ul> <li>Corrected MCF5327 196MAPBGA ball map locations in Table 5 for the following signals: RCON, D1, D0, OE, R/W, SD_DQS2, PSTCLK, DDATA[3:0], PST[3:0], EVDD, IVDD, and SD_VDD. Figure 5 was correct.</li> <li>Updated thermal characteristic values in Table 5.</li> <li>Updated DC electricals values in Table 7.</li> <li>Updated Section 3.3, "Supply Voltage Sequencing and Separation Cautions" and subsections.</li> <li>Updated and added Oscillator/PLL characteristics in Table 8.</li> <li>Table 9: Swapped min/max for FB1; Removed FB8 &amp; FB9.</li> <li>Updated SDRAM write timing diagram, Figure 9.</li> <li>Table 11: Added values for frequency of operation and DD1.</li> <li>Reworded first paragraph in Section 5.12, "ULPI Timing Specification."</li> <li>Updated Figure 19.</li> <li>Replaced figure &amp; table Section 5.13, "SSI Timing Specifications," with slave &amp; master mode versions.</li> <li>Removed second sentence from Section 5.15.2, "MII Transmit Signal Timing," regarding no minimum frequency requirement for TXCLK.</li> <li>Removed third and fourth paragraphs from Section 5.15.2, "MII Transmit Signal Timing," as this feature is not supported on this device.</li> <li>Updated figure &amp; table Section 5.19, "Debug AC Timing Specifications."</li> <li>Renamed &amp; moved previous version's Section 5.5 "Power Consumption" to Section 6, "Current Consumption." Added additional real-world data to this section as well.</li> </ul> | 7/2007          |

| 2        | <ul> <li>Added MCF53281 device information throughout: features list, family configuration table, ordering information table, signals description table, and relevant package diagram titles</li> <li>Remove Footnote 1 from Table 11.</li> <li>Changed document type from Advance Information to Technical Data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8/2007          |

| 3        | <ul> <li>Corrected MCF53281 in features list table. This device contains CAN, but does not feature the cryptography accelerators.</li> <li>In pin-multiplexing table, moved MCF53281 label from the MCF5328 column to the MCF5329 column, because this device contains CAN output signals.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10/2007         |