Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | UART/USART, USB                                                 |

| Peripherals                | POR                                                             |

| Number of I/O              | 15                                                              |

| Program Memory Size        | 16KB (16K × 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | ·                                                               |

| RAM Size                   | 1.5K x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | ·                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f327-gmr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 7.5. Flash Error Reset                                          | 60 |

|----|-----------------------------------------------------------------|----|

|    | 7.6. Software Reset                                             |    |

|    | 7.7. USB Reset                                                  |    |

| 8  | Flash Memory                                                    |    |

| 0. | 8.1. Programming The Flash Memory                               |    |

|    | 8.1.1. Flash Lock and Key Functions                             |    |

|    | 8.1.2. Flash Erase Procedure                                    |    |

|    | 8.1.3. Flash Write Procedure                                    |    |

|    | 8.2. Non-volatile Data Storage                                  | -  |

|    | 8.3. Security Options                                           |    |

| ٩  | External RAM                                                    |    |

| э. | 9.1. Accessing User XRAM                                        |    |

|    | 9.2. Accessing USB FIFO Space                                   |    |

| 10 | . Oscillators                                                   |    |

| 10 | 10.1.Programmable Internal Oscillator                           |    |

|    | 10.1.1.Adjusting the Internal Oscillator on C8051F326/7 Devices |    |

|    | 10.1.2. Internal Oscillator Suspend Mode                        |    |

|    | 10.2.Internal Low-Frequency (L-F) Oscillator                    |    |

|    | 10.3.CMOS External Clock Input.                                 |    |

|    | 10.4.4x Clock Multiplier                                        |    |

|    | 10.5.System and USB Clock Selection                             |    |

|    | 10.5.1.System Clock Selection                                   |    |

|    | 10.5.2.USB Clock Selection                                      |    |

| 11 | .Port Input/Output                                              |    |

|    | 11.1.Port I/O Initialization                                    |    |

|    | 11.2.General Purpose Port I/O                                   |    |

| 12 | Universal Serial Bus Controller (USB0)                          |    |

|    | 12.1.Endpoint Addressing                                        |    |

|    | 12.2.USB Transceiver                                            |    |

|    | 12.3.USB Register Access                                        |    |

|    | 12.4.USB Clock Configuration                                    |    |

|    | 12.5.FIFO Management                                            |    |

|    | 12.5.1.FIFO Šplit Mode                                          |    |

|    | 12.5.2.FIFO Double Buffering                                    | 95 |

|    | 12.5.3.FIFO Access                                              |    |

|    | 12.6.Function Addressing                                        | 97 |

|    | 12.7.Function Configuration and Control                         |    |

|    | 12.8.Interrupts                                                 |    |

|    | 12.9.The Serial Interface Engine 1                              |    |

|    | 12.10. Endpoint0 1                                              |    |

|    | 12.10.1.Endpoint0 SETUP Transactions 1                          | 04 |

|    | 12.10.2.Endpoint0 IN Transactions1                              |    |

|    | 12.10.3.Endpoint0 OUT Transactions1                             |    |

|    | 12.11.Configuring Endpoint1 1                                   |    |

# **List of Tables**

| 1.  | System Overview                                                                                                                       |     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | Table 1.1. Product Selection Guide                                                                                                    | 13  |

| 2.  | Absolute Maximum Ratings                                                                                                              |     |

|     | Table 2.1. Absolute Maximum Ratings                                                                                                   | 23  |

| 3.  | Global DC Electrical Characteristics                                                                                                  |     |

|     | Table 3.1. Global DC Electrical Characteristics                                                                                       | 24  |

| 4.  | Pinout and Package Definitions                                                                                                        |     |

|     | Table 4.1. Pin Definitions for the C8051F326/7                                                                                        | 25  |

|     | Table 4.2. QFN-28 Package Dimensions                                                                                                  |     |

|     | Table 4.3. QFN-28 PCB Land Pattern Dimesions                                                                                          | 30  |

| 5.  | Voltage Regulator (REG0)                                                                                                              |     |

|     | Table 5.1. Voltage Regulator Electrical Specifications                                                                                | 31  |

| 6.  | CIP-51 Microcontroller                                                                                                                |     |

|     | Table 6.1. CIP-51 Instruction Set Summary                                                                                             |     |

|     | Table 6.2. Special Function Register (SFR) Memory Map                                                                                 |     |

|     | Table 6.3. Special Function Registers                                                                                                 |     |

|     | Table 6.4. TMOD.3 Control of /INT0                                                                                                    |     |

| _   | Table 6.5. Interrupt Summary                                                                                                          | 50  |

| 7.  | Reset Sources                                                                                                                         | ~ ~ |

| _   | Table 7.1. Reset Electrical Characteristics                                                                                           | 62  |

| 8.  | Flash Memory                                                                                                                          | ~ . |

| •   | Table 8.1. Flash Electrical Characteristics                                                                                           | 64  |

| -   | External RAM                                                                                                                          |     |

| 10  | Oscillators                                                                                                                           | 70  |

|     | Table 10.1. Typical USB Full Speed Clock Settings                                                                                     |     |

|     | Table 10.2. Typical USB Low Speed Clock Settings                                                                                      |     |

| 44  | Table 10.3. Internal Oscillator Electrical Characteristics         Part Input/Output                                                  | 18  |

| 11. | <b>Port Input/Output</b><br>Table 11.1. Port I/O DC Electrical Characteristics (C8051F326)                                            | 95  |

|     | Table 11.2. Port I/O DC Electrical Characteristics (C8051F320)         Table 11.2. Port I/O DC Electrical Characteristics (C8051F327) |     |

| 12  | .Universal Serial Bus Controller (USB0)                                                                                               | 00  |

| 12  | Table 12.1. Endpoint Addressing Scheme                                                                                                | 88  |

|     | Table 12.2. USB0 Controller Registers                                                                                                 |     |

|     | Table 12.3. FIFO Configurations                                                                                                       |     |

|     | Table 12.4. USB Transceiver Electrical Characteristics       1                                                                        |     |

| 13  | .UARTO                                                                                                                                | 10  |

| 10  | Table 13.1. Baud Rate Generator Settings for Standard Baud Rates 1                                                                    | 19  |

| 14  | Timers                                                                                                                                | 10  |

|     | Table 14.1. Timer Modes 1                                                                                                             | 27  |

|     | Table 14.2. Timer 0 Operation                                                                                                         |     |

| 15  | .C2 Interface                                                                                                                         |     |

#### 1.2. On-Chip Memory

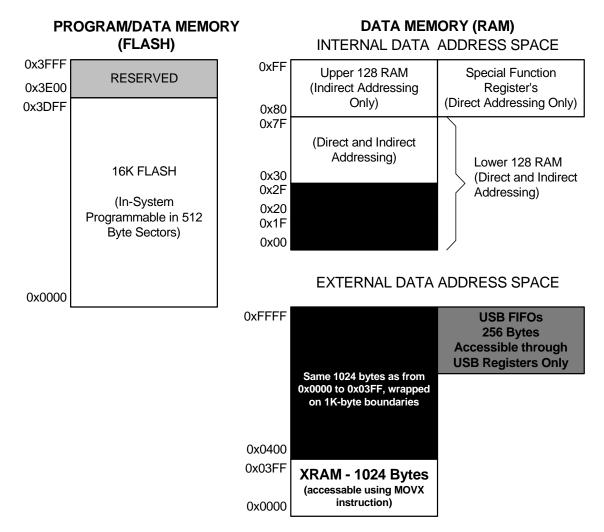

The CIP-51 has a standard 8051 program and data address configuration. It includes 256 bytes of data RAM, with the upper 128 bytes dual-mapped. Indirect addressing accesses the upper 128 bytes of general purpose RAM, and direct addressing accesses the 128 byte SFR address space. The lower 128 bytes of RAM are accessible via direct and indirect addressing. The first 32 bytes are addressable as four banks of general purpose registers, and the next 16 bytes can be byte addressable or bit addressable.

Program memory consists of 16k bytes of Flash. This memory may be reprogrammed in-system in 512 byte sectors, and requires no special off-chip programming voltage. See Figure 1.7 for the MCU system memory map.

Figure 1.7. On-Board Memory Map

# 4. Pinout and Package Definitions

| Nome  | Pin Numbers |       | Turne        | Description                                                                                                                                                                                        |  |  |  |  |

|-------|-------------|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name  | 'F326       | 'F327 | Туре         | Description                                                                                                                                                                                        |  |  |  |  |

| VDD   | 6           | 6     | Power<br>In  | 2.7–3.6 V Core Supply Voltage Input.                                                                                                                                                               |  |  |  |  |

|       | 0           | 0     | Power<br>Out | 3.3 V Voltage Regulator Output. See Section 5.                                                                                                                                                     |  |  |  |  |

| VIO   | 5           |       | Power<br>In  | V I/O Supply Voltage Input. The voltage at this pin must be less than or equal to the Core Supply Voltage ( $V_{DD}$ ) for the 'F326. On the 'F327, this pin is internally connected to $V_{DD}$ . |  |  |  |  |

| GND   | 2           | 3     |              | Ground.                                                                                                                                                                                            |  |  |  |  |

| RST/  | 9           | 9     | D I/O        | Device Reset. Open-drain output of internal POR or VDI monitor. An external source can initiate a system reset b driving this pin low for at least 15 µs. See Section 7.                           |  |  |  |  |

| C2CK  |             |       | D I/O        | Clock signal for the C2 Debug Interface.                                                                                                                                                           |  |  |  |  |

| P3.0/ | 4.0         | 4.0   | D I/O        | Port 3.0. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

| C2D   | 10          | 10    | D I/O        | Bi-directional data signal for the C2 Debug Interface.                                                                                                                                             |  |  |  |  |

| REGIN | 7           | 7     | Power<br>In  | 5 V Regulator Input. This pin is the input to the on-chip volt-<br>age regulator.                                                                                                                  |  |  |  |  |

| VBUS  | 8           | 8     | D In         | VBUS Sense Input. This pin should be connected to the VBUS signal of a USB network. A 5 V signal on this pin indicates a USB network connection.                                                   |  |  |  |  |

| D+    | 3           | 4     | D I/O        | USB D+.                                                                                                                                                                                            |  |  |  |  |

| D     | 4           | 5     | D I/O        | USB D–.                                                                                                                                                                                            |  |  |  |  |

| P0.0  | 1           | 2     | D I/O        | Port 0.0. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

| P0.1  | 28          | 1     | D I/O        | Port 0.1. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

| P0.2  | 27          | 28    | D I/O        | Port 0.2. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

| P0.3/ |             |       | D I/O        | Port 0.3. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

| XTAL2 | 26          | 27    | D In         | External Clock Input. See Section 10 for a complete description.                                                                                                                                   |  |  |  |  |

| P0.4  | 25          | 26    | D I/O        | Port 0.4. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

| P0.5  | 24          | 25    | D I/O        | Port 0.5. See Section 11 for a complete description.                                                                                                                                               |  |  |  |  |

# 5. Voltage Regulator (REG0)

C8051F326/7 devices include a voltage regulator (REG0). When enabled, the REG0 output appears on the VDD pin and can be used to power external devices. REG0 can be enabled/disabled by software using bit REGEN in register REG0CN. See Table 5.1 for REG0 electrical characteristics.

The voltage regulator is enabled on reset. When the device is self-powered from a 3V supply net, the regulator may be disabled in order to save power. Important Note: If the voltage at the regulator input (REGIN) is greater than the Core Supply Voltage (VDD), the voltage regulator should not be disabled. Otherwise, permanent damage to the device may occur.

Note that the VBUS signal must be connected to the VBUS pin when using the device in a USB network. The VBUS signal should only be connected to the REGIN pin when operating the device as a bus-powered function. REG0 configuration options are shown in Figure 5.1 - Figure 5.4.

#### 5.1. Regulator Mode Selection

REG0 offers a low power mode intended for use when the device is in suspend mode. In this low power mode, the REG0 output remains as specified; however the REG0 dynamic performance (response time) is degraded. See Table 5.1 for normal and low power mode supply current specifications. The REG0 mode selection is controlled via the REGMOD bit in register REG0CN.

### 5.2. VBUS Detection

When the USB Function Controller is used (see section Section "12. Universal Serial Bus Controller (USB0)" on page 87), the VBUS signal should be connected to the VBUS pin. The VBSTAT bit (register REGOCN) indicates the current logic level of the VBUS signal. If enabled, a VBUS interrupt will be generated when the VBUS signal matches the polarity selected by the VBPOL bit in register REGOCN. The VBUS interrupt is level-sensitive, and has no associated interrupt pending flag. The VBUS interrupt will be active as long as the VBUS signal matches the polarity selected by VBPOL. See Table 5.1 for VBUS input parameters.

**Important Note:** When USB is selected as a reset source, a system reset will be generated when the VBUS signal matches the polarity selected by the VBPOL bit. See Section "7. Reset Sources" on page 57 for details on selecting USB as a reset source.

#### Table 5.1. Voltage Regulator Electrical Specifications

$V_{DD} = 3.0 \text{ V}; -40 \text{ to } +85 \text{ °C}$  unless otherwise specified.

| Parameter                                                                                                         | Conditions                                                  | Min | Тур      | Max       | Units |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|----------|-----------|-------|--|--|--|

| Input Voltage Range                                                                                               |                                                             | 2.7 |          | 5.25      | V     |  |  |  |

| Output Voltage                                                                                                    | Output Current = 1 to 100 mA                                | 3.0 | 3.3      | 3.6       | V     |  |  |  |

| VBUS Detection Input Threshold                                                                                    |                                                             | 1.0 | 1.8      | 2.9       | V     |  |  |  |

| Bias Current                                                                                                      | Normal Mode (REGMOD = '0')<br>Low Power Mode (REGMOD = '1') | _   | 75<br>41 | 111<br>61 | μA    |  |  |  |

| Dropout Voltage (V <sub>DO</sub> )*                                                                               | IDD = 1 to 100 mA                                           | —   | 1        | —         | mV/mA |  |  |  |

| *Note: The minimum input voltage is 2.70 V or V <sub>DD</sub> + V <sub>DO</sub> (max load), whichever is greater. |                                                             |     |          |           |       |  |  |  |

# C8051F326/7

### 6.3. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting a total of 8 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source, with the exception of USB0, has one or more associated interrupt-pending flag(s) located in an SFR. USB0 interrupt sources are located in the USB registers. See Section "12.8. Interrupts" on page 101 for more details about the USB interrupt. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE-EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

**Note:** Any instruction which clears the EA bit should be immediately followed by an instruction which has two or more opcode bytes. For example:

// in 'C':

EA = 0; // clear EA bit

EA = 0; // ... followed by another 2-byte opcode

; in assembly:

CLR EA ; clear EA bit

CLR EA ; ... followed by another 2-byte opcode

If an interrupt is posted during the execution phase of a "CLR EA" opcode (or any instruction that clears the EA bit), and the instruction is followed by a single-cycle instruction, the interrupt may be taken. If the EA bit is read inside the interrupt service routine, it will return a '0'. When the "CLR EA" opcode is followed by a multi-cycle instruction, the interrupt will not be taken.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 6.3.1. MCU Interrupt Sources and Vectors

The MCU supports 8 interrupt sources. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 6.5 on page 50. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

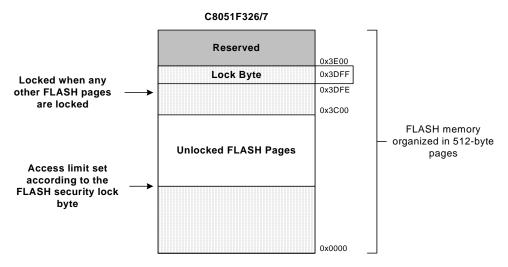

Figure 8.1. Flash Program Memory Map and Security Byte

## SFR Definition 8.1. PSCTL: Program Store R/W Control

## SFR Definition 8.2. FLKEY: Flash Lock and Key

| R/W      | R/W                                                  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |  |  |  |

|----------|------------------------------------------------------|------|------|------|------|------|------|--------------|--|--|--|--|

|          |                                                      |      |      |      |      |      |      | 00000000     |  |  |  |  |

| Bit7     | Bit6                                                 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |  |  |  |

|          |                                                      |      |      |      |      |      |      | 0xB7         |  |  |  |  |

| Bits7–0: | Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address: |      |      |      |      |      |      |              |  |  |  |  |

## SFR Definition 8.3. FLSCL: Flash Scale

| R/W                | R/W                                                                                                                                                                                                                                                                                                                                                                                                      | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      | Reset Value  |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|--------------|--|--|--|--|

| FOSE               | Reserved                                                                                                                                                                                                                                                                                                                                                                                                 | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | 10000000     |  |  |  |  |

| Bit7               | Bit6                                                                                                                                                                                                                                                                                                                                                                                                     | Bit5     | Bit4     | Bit3     | Bit2     | Bit1     | Bit0     | SFR Address: |  |  |  |  |

|                    |                                                                                                                                                                                                                                                                                                                                                                                                          |          |          |          |          |          |          | 0xB6         |  |  |  |  |

| Bits7:<br>Bits6–0: | <ul> <li>FOSE: Flash One-shot Enable</li> <li>This bit enables the Flash read one-shot. When the Flash one-shot disabled, the Flash sense amps are enabled for a full clock cycle during Flash reads. At system clock frequencies below 10 MHz, disabling the Flash one-shot will increase system power consumption.</li> <li>0: Flash one-shot disabled.</li> <li>1: Flash one-shot enabled.</li> </ul> |          |          |          |          |          |          |              |  |  |  |  |

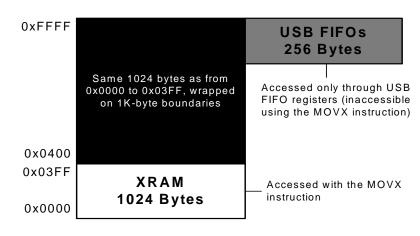

# 9. External RAM

The C8051F326/7 devices include 1280 bytes of on-chip XRAM. This XRAM space is split into user RAM (addresses 0x0000–0x03FF) and USB0 FIFO space. The USB0 FIFO space is only accessible through the USB FIFO registers.

#### Figure 9.1. External Ram Memory Map

#### 9.1. Accessing User XRAM

User XRAM can be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN as shown in Figure 9.1). Note: the MOVX instruction is also used for writes to the Flash memory. See Section "8. Flash Memory" on page 63 for details. The MOVX instruction accesses XRAM by default.

For any of the addressing modes, the upper 6 bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style over the entire 64k external data memory address range. For example, the XRAM byte at address 0x0000 is also at address 0x0400, 0x0800, 0x0C00, 0x1000, etc.

# C8051F326/7

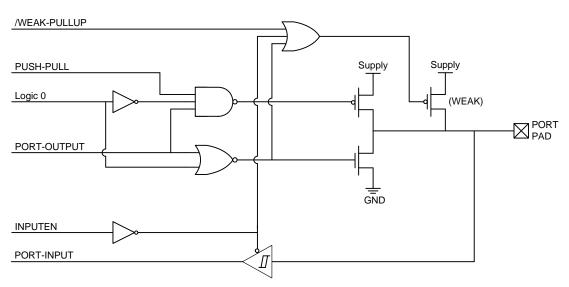

Figure 11.2. Port I/O Cell Block Diagram

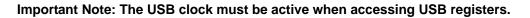

#### 12.3. USB Register Access

The USB0 controller registers listed in Table 12.2 are accessed through two SFRs: USB0 Address (USB0ADR) and USB0 Data (USB0DAT). The USB0ADR register selects which USB register is targeted by reads/writes of the USB0DAT register. See Figure 12.2.

Endpoint control/status registers are accessed by first writing the USB register INDEX with the target endpoint number. Once the target endpoint number is written to the INDEX register, the control/status registers associated with the target endpoint may be accessed. See the "Indexed Registers" section of Table 12.2 for a list of endpoint control/status registers.

Figure 12.2. USB0 Register Access Scheme

| <b>USB</b> Register Definition | 12.8. | <b>POWER:</b> | USB0 Power |

|--------------------------------|-------|---------------|------------|

|--------------------------------|-------|---------------|------------|

| R/W      | R/W                                                                                                                                         | R/W          | R/W           | R/W            | R/W          | R                            | R/W           | Reset Value          |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------|----------------|--------------|------------------------------|---------------|----------------------|--|--|--|--|

| ISOUD    | -                                                                                                                                           | -            | USBINH        | USBRST         | RESUME       | SUSMD                        | SUSEN         | 00010000             |  |  |  |  |

| Bit7     | Bit6                                                                                                                                        | Bit5         | Bit4          | Bit3           | Bit2         | Bit1                         | Bit0          | USB Address:<br>0x01 |  |  |  |  |

| Bit7:    | ISOUD: ISO                                                                                                                                  |              |               |                |              |                              |               |                      |  |  |  |  |

|          | This bit affects all IN Isochronous endpoints.<br>0: When software writes INPRDY = '1', USB0 will send the packet when the next IN token is |              |               |                |              |                              |               |                      |  |  |  |  |

|          | 0: When software writes INPRDY = '1', USB0 will send the packet when the next IN token is received.                                         |              |               |                |              |                              |               |                      |  |  |  |  |

|          | 1: When soft                                                                                                                                |              |               |                |              |                              |               |                      |  |  |  |  |

|          | packet. If an packet.                                                                                                                       | IN TOKEN IS  | received b    | efore a SOI    | - token, US  | BU WIII Send                 | a zero-ler    | igth data            |  |  |  |  |

| Bits6–5: | Unused. Rea                                                                                                                                 |              | /rite = don't | care.          |              |                              |               |                      |  |  |  |  |

| Bit4:    | USBINH: US<br>This bit is se                                                                                                                |              | wing a pow    | er-on reset    | (POR) or a   | n asvnchroi                  | nous USB0     | reset (see           |  |  |  |  |

|          | Bit3: RESET                                                                                                                                 | ). Software  | should cle    | ar this bit af |              |                              |               |                      |  |  |  |  |

|          | complete. So<br>0: USB0 ena                                                                                                                 |              | not set this  | bit to '1'.    |              |                              |               |                      |  |  |  |  |

|          | 1: USB0 inhi                                                                                                                                |              | SB traffic is | ignored.       |              |                              |               |                      |  |  |  |  |

| Bit3:    | USBRST: Re                                                                                                                                  |              |               | -              |              | <b>D</b> a a dline ar dhe in |               | - h                  |  |  |  |  |

|          | Writing '1' to status inform                                                                                                                |              | es an asyn    | chronous U     | SBU reset. F | Reading this                 | s bit provide | es dus reset         |  |  |  |  |

|          | Read:                                                                                                                                       |              |               |                |              |                              |               |                      |  |  |  |  |

|          | 0: Reset sign<br>1: Reset sign                                                                                                              |              |               |                |              |                              |               |                      |  |  |  |  |

| Bit2:    | RESUME: F                                                                                                                                   | orce Resur   | ne            |                |              |                              |               |                      |  |  |  |  |

|          | Software car<br>a '1' to this b                                                                                                             |              |               |                |              |                              |               |                      |  |  |  |  |

|          | naling on the                                                                                                                               | e bus (a ren | note Wakeu    | up event). S   | oftware sho  | uld write R                  | ESUME = '     | 0' after             |  |  |  |  |

|          | 10 ms to15 r<br>SUSMD, wh                                                                                                                   |              |               |                |              | s generated                  | d, and hard   | ware clears          |  |  |  |  |

| Bit1:    | SUSMD; WI                                                                                                                                   |              |               | 3000 = 0       |              |                              |               |                      |  |  |  |  |

|          | Set to '1' by<br>ware writes I                                                                                                              |              |               |                |              |                              |               |                      |  |  |  |  |

|          | ing on the bu                                                                                                                               |              |               | ig a remote    | wakeup) oi   |                              |               | ume signal-          |  |  |  |  |

|          | 0: USB0 not                                                                                                                                 |              |               |                |              |                              |               |                      |  |  |  |  |

| Bit0:    | 1: USB0 in s<br>SUSEN: Sus                                                                                                                  |              |               | е              |              |                              |               |                      |  |  |  |  |

|          | 0: Suspend                                                                                                                                  | detection di | sabled. US    | B0 will igno   |              |                              |               |                      |  |  |  |  |

|          | 1: Suspend on the bus.                                                                                                                      | detection er | nabled. USE   | 30 will enter  | suspend m    | ode if it det                | ects susper   | nd signaling         |  |  |  |  |

|          |                                                                                                                                             |              |               |                |              |                              |               |                      |  |  |  |  |

### 12.9. The Serial Interface Engine

The Serial Interface Engine (SIE) performs all low level USB protocol tasks, interrupting the processor when data has successfully been transmitted or received. When receiving data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been received; appropriate handshaking signals are automatically generated by the SIE. When transmitting data, the SIE will interrupt the processor when a complete data packet has been transmitted and the appropriate handshake signal has been received.

The SIE will not interrupt the processor when corrupted/erroneous packets are received.

#### 12.10. Endpoint0

Endpoint0 is managed through the USB register E0CSR (Figure 12.17). The INDEX register must be loaded with 0x00 to access the E0CSR register.

An Endpoint0 interrupt is generated when:

- 1. A data packet (OUT or SETUP) has been received and loaded into the Endpoint0 FIFO. The OPRDY bit (E0CSR.0) is set to '1' by hardware.

- 2. An IN data packet has successfully been unloaded from the Endpoint0 FIFO and transmitted to the host; INPRDY is reset to '0' by hardware.

- 3. An IN transaction is completed (this interrupt generated during the status stage of the transaction).

- 4. Hardware sets the STSTL bit (E0CSR.2) after a control transaction ended due to a protocol violation.

- 5. Hardware sets the SUEND bit (E0CSR.4) because a control transfer ended before firmware sets the DATAEND bit (E0CSR.3).

The E0CNT register (Figure 12.18) holds the number of received data bytes in the Endpoint0 FIFO.

Hardware will automatically detect protocol errors and send a STALL condition in response. Firmware may force a STALL condition to abort the current transfer. When a STALL condition is generated, the STSTL bit will be set to '1' and an interrupt generated. The following conditions will cause hardware to generate a STALL condition:

- 1. The host sends an OUT token during a OUT data phase after the DATAEND bit has been set to '1'.

- 2. The host sends an IN token during an IN data phase after the DATAEND bit has been set to '1'.

- 3. The host sends a packet that exceeds the maximum packet size for Endpoint0.

4. The host sends a non-zero length DATA1 packet during the status phase of an IN transaction. Firmware sets the SDSTL bit (E0CSR.5) to '1'.

#### 12.10.1.Endpoint0 SETUP Transactions

All control transfers must begin with a SETUP packet. SETUP packets are similar to OUT packets, containing an 8-byte data field sent by the host. Any SETUP packet containing a command field of anything other than 8 bytes will be automatically rejected by USB0. An Endpoint0 interrupt is generated when the data from a SETUP packet is loaded into the Endpoint0 FIFO. Software should unload the command from the Endpoint0 FIFO, decode the command, perform any necessary tasks, and set the SOPRDY bit to indicate that it has serviced the OUT packet.

#### 12.10.2.Endpoint0 IN Transactions

When a SETUP request is received that requires USB0 to transmit data to the host, one or more IN requests will be sent by the host. For the first IN transaction, firmware should load an IN packet into the Endpoint0 FIFO, and set the INPRDY bit (E0CSR.1). An interrupt will be generated when an IN packet is transmitted successfully. Note that no interrupt will be generated if an IN request is received before firmware has loaded a packet into the Endpoint0 FIFO. If the requested data exceeds the maximum packet size for Endpoint0 (as reported to the host), the data should be split into multiple packets; each packet should be of the maximum packet size excluding the last (residual) packet. If the requested data is an integer multiple of the maximum packet size for Endpoint0, the last data packet should be a zero-length packet signaling the end of the transfer. Firmware should set the DATAEND bit to '1' after loading into the Endpoint0 FIFO the last data packet for a transfer.

Upon reception of the first IN token for a particular control transfer, Endpoint0 is said to be in Transmit Mode. In this mode, only IN tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to '1' if a SETUP or OUT token is received while Endpoint0 is in Transmit Mode.

Endpoint0 will remain in Transmit Mode until any of the following occur:

- 1. USB0 receives an Endpoint0 SETUP or OUT token.

- 2. Firmware sends a packet less than the maximum Endpoint0 packet size.

- 3. Firmware sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to '1' when performing (2) and (3) above.

The SIE will transmit a NAK in response to an IN token if there is no packet ready in the IN FIFO (INPRDY =  $0^{\circ}$ ).

#### 12.10.3.Endpoint0 OUT Transactions

When a SETUP request is received that requires the host to transmit data to USB0, one or more OUT requests will be sent by the host. When an OUT packet is successfully received by USB0, hardware will set the OPRDY bit (E0CSR.0) to '1' and generate an Endpoint0 interrupt. Following this interrupt, firmware should unload the OUT packet from the Endpoint0 FIFO and set the SOPRDY bit (E0CSR.6) to '1'.

If the amount of data required for the transfer exceeds the maximum packet size for Endpoint0, the data will be split into multiple packets. If the requested data is an integer multiple of the maximum packet size for Endpoint0 (as reported to the host), the host will send a zero-length data packet signaling the end of the transfer.

Upon reception of the first OUT token for a particular control transfer, Endpoint0 is said to be in Receive Mode. In this mode, only OUT tokens should be sent by the host to Endpoint0. The SUEND bit (E0CSR.4) is set to '1' if a SETUP or IN token is received while Endpoint0 is in Receive Mode.

Endpoint0 will remain in Receive mode until:

- 1. The SIE receives a SETUP or IN token.

- 2. The host sends a packet less than the maximum Endpoint0 packet size.

- 3. The host sends a zero-length packet.

Firmware should set the DATAEND bit (E0CSR.3) to '1' when the expected amount of data has been received. The SIE will transmit a STALL condition if the host sends an OUT packet after the DATAEND bit has been set by firmware. An interrupt will be generated with the STSTL bit (E0CSR.2) set to '1' after the STALL is transmitted.

## USB Register Definition 12.19. EINCSRL: USB0 IN Endpoint Control Low Byte

| R     | W                                                                                                                          | R/W            | R/W            | R/W            | R/W           | R/W           | R/W           | Reset Value          |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------|----------------|---------------|---------------|---------------|----------------------|--|--|--|--|--|

| _     | CLRDT                                                                                                                      | STSTL          | SDSTL          | FLUSH          | UNDRUN        | FIFONE        | INPRDY        | 00000000             |  |  |  |  |  |

| Bit7  | Bit6                                                                                                                       | Bit5           | Bit4           | Bit3           | Bit2          | Bit1          | Bit0          | USB Address:<br>0x11 |  |  |  |  |  |

| Bit7: |                                                                                                                            |                |                |                |               |               |               |                      |  |  |  |  |  |

| Bit6: | CLRDT: Clear Data Toggle.                                                                                                  |                |                |                |               |               |               |                      |  |  |  |  |  |

|       | Write: Software should write '1' to this bit to reset the IN Endpoint data toggle to '0'. Read: This bit always reads '0'. |                |                |                |               |               |               |                      |  |  |  |  |  |

| Bit5: | STSTL: Sen                                                                                                                 |                | eads '0'.      |                |               |               |               |                      |  |  |  |  |  |

| DID.  | Hardware se                                                                                                                |                | oʻ1' when a    | STALL hai      | ndshake siq   | nal is trans  | mitted The    | FIFO is              |  |  |  |  |  |

|       | flushed, and                                                                                                               |                |                |                |               |               |               |                      |  |  |  |  |  |

| Bit4: | SDSTL: Sen                                                                                                                 |                |                |                |               |               |               |                      |  |  |  |  |  |

|       | Software sho                                                                                                               |                |                | •              |               |               |               |                      |  |  |  |  |  |

|       | token. Softw<br>effect in ISO                                                                                              |                | write '0' to t | this bit to te | rminate the   | STALL sign    | nal. This bit | has no               |  |  |  |  |  |

| Bit3: | FLUSH: FIF                                                                                                                 |                |                |                |               |               |               |                      |  |  |  |  |  |

|       | Writing a '1'                                                                                                              | to this bit fl | ushes the n    | ext packet     | to be transm  | nitted from t | the IN Endp   | oint FIFO.           |  |  |  |  |  |

|       | The FIFO po                                                                                                                |                |                |                |               |               |               |                      |  |  |  |  |  |

|       | ets, software                                                                                                              |                |                | SH for each    | packet. Har   | dware rese    | ets the FLU   | SH bit to '0'        |  |  |  |  |  |

| Bit2: | when the FIF<br>UNDRUN: D                                                                                                  |                | •              |                |               |               |               |                      |  |  |  |  |  |

| DILZ. | The function                                                                                                               |                |                | the IN End     | point mode:   |               |               |                      |  |  |  |  |  |

|       | ISO: Set whe                                                                                                               |                | •              |                | •             |               | ed while bit  | INPRDY =             |  |  |  |  |  |

|       | ʻ0'.                                                                                                                       |                |                |                |               |               |               |                      |  |  |  |  |  |

|       | Interrupt/Bul<br>This bit must                                                                                             |                |                |                | response to   | an IN tokei   | า.            |                      |  |  |  |  |  |

| Bit1: | FIFONE: FIF                                                                                                                |                |                | е.             |               |               |               |                      |  |  |  |  |  |

| BRIT  | 0: The IN En                                                                                                               |                |                |                |               |               |               |                      |  |  |  |  |  |

|       | 1. The IN En                                                                                                               |                |                | one or more    | e packets.    |               |               |                      |  |  |  |  |  |

| Bit0: | INPRDY: In                                                                                                                 |                |                | <i>6</i> 1 1   |               |               |               |                      |  |  |  |  |  |

|       | Software sho<br>Hardware clo                                                                                               |                |                |                |               | cket into the | e IN Enapoi   | nt FIFO.             |  |  |  |  |  |

|       | 1. A data pa                                                                                                               |                |                |                | iowing.       |               |               |                      |  |  |  |  |  |

|       | 2. Double bu                                                                                                               |                |                | IEN = '1') a   | nd there is a | an open FIF   | O packet s    | lot.                 |  |  |  |  |  |

|       | 3. If the endp                                                                                                             |                |                | Mode (ISO      | = '1') and IS | SOUD = '1'    | , INPRDY v    | vill read '0'        |  |  |  |  |  |

|       | until the next                                                                                                             |                |                | unarated v     | whon hardy    | aro cloare    |               | e a rocult           |  |  |  |  |  |

|       | of a packet                                                                                                                | •              | , .            | Jeneraleu V    |               | ait citals    |               | ο αισουπ             |  |  |  |  |  |

|       |                                                                                                                            | J              |                |                |               |               |               |                      |  |  |  |  |  |

| R/W     | R/W                                                                                                 | R          | R           | R/W     | R    | R    | R    | Reset Value |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------|------------|-------------|---------|------|------|------|-------------|--|--|--|

| DBIEN   | ISO                                                                                                 |            | _           | FCDT    | _    | _    |      | 00000000    |  |  |  |

| Bit7    | Bit6                                                                                                | Bit5       | Bit4        | Bit3    | Bit2 | Bit1 | Bit0 | USB Address |  |  |  |

|         |                                                                                                     |            |             |         |      |      |      | 0x12        |  |  |  |

| Bit7:   | DBIEN: IN EI                                                                                        | ndpoint Do | uble-buffer | Enable. |      |      |      |             |  |  |  |

|         | 0: Double-buffering disabled for the selected IN endpoint.                                          |            |             |         |      |      |      |             |  |  |  |

|         | 1: Double-buffering enabled for the selected IN endpoint.                                           |            |             |         |      |      |      |             |  |  |  |

| Bit6:   | ISO: Isochronous Transfer Enable.                                                                   |            |             |         |      |      |      |             |  |  |  |

|         | This bit enables/disables isochronous transfers on the current endpoint.                            |            |             |         |      |      |      |             |  |  |  |

|         | 0: Endpoint configured for bulk/interrupt transfers.                                                |            |             |         |      |      |      |             |  |  |  |

|         | 1: Endpoint configured for isochronous transfers.                                                   |            |             |         |      |      |      |             |  |  |  |

| Bit5–4: |                                                                                                     |            |             |         |      |      |      |             |  |  |  |

| Bit3:   | FCDT: Force Data Toggle.                                                                            |            |             |         |      |      |      |             |  |  |  |

|         | 0: Endpoint data toggle switches only when an ACK is received following a data packet transmission. |            |             |         |      |      |      |             |  |  |  |

|         | 1: Endpoint data toggle forced to switch after every data packet is transmitted, regardless of      |            |             |         |      |      |      |             |  |  |  |

|         | ACK reception.                                                                                      |            |             |         |      |      |      |             |  |  |  |

|         | ACK reception                                                                                       | n.         |             |         |      |      |      |             |  |  |  |

### USB Register Definition 12.20. EINCSRH: USB0 IN Endpoint Control High Byte

## Table 12.4. USB Transceiver Electrical Characteristics

$V_{DD}$  = 3.0 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters                                | Symbol           | Conditions                    | Min         | Тур  | Max   | Units |

|-------------------------------------------|------------------|-------------------------------|-------------|------|-------|-------|

| USB Operating Current                     |                  | Full Speed                    | _           | 5.7  |       | mA    |

|                                           |                  | Low Speed                     | —           | 1.5  |       |       |

| Transmitter                               |                  |                               | 1           | 1    |       |       |

| Output High Voltage                       | V <sub>OH</sub>  |                               | 2.8         | —    |       | V     |

| Output Low Voltage                        | V <sub>OL</sub>  |                               | _           |      | 0.8   | V     |

| Output Crossover Point                    | V <sub>CRS</sub> |                               | 1.3         |      | 2.0   | V     |

| Output Impedance                          | Z <sub>DRV</sub> | Driving High                  | _           | 38   |       | W     |

|                                           |                  | Driving Low                   | —           | 38   |       |       |

| Pullup Resistance                         | R <sub>PU</sub>  | Full Speed (D+ Pullup)        | 1.425       | 1.5  | 1.575 | kW    |

|                                           | -                | Low Speed (D– Pullup)         | —           | —    |       |       |

| Output Rise Time                          | Τ <sub>R</sub>   | Low Speed                     | 75          |      | 300   | ns    |

|                                           |                  | Full Speed                    | 4           | —    | 20    |       |

| Output Fall Time                          | Τ <sub>F</sub>   | Low Speed                     | 75          |      | 300   | ns    |

|                                           |                  | Full Speed                    | 4           | —    | 20    |       |

| Receiver                                  |                  |                               | 1           | 1    |       |       |

| Differential Input Sensitiv-<br>ity       | V <sub>DI</sub>  | (D+) – (D–)                   | 0.2         | —    | —     | V     |

| Differential Input Com-<br>mon Mode Range | V <sub>CM</sub>  |                               | 0.8         | —    | 2.5   | V     |

| Input Leakage Current                     | ١ <sub>L</sub>   | Pullups Disabled              | —           | <1.0 | —     | μA    |

| Note: Refer to the USB Spec               | ification for t  | timing diagrams and symbol de | efinitions. | 1    | 1     | 1     |

# C8051F326/7

|         | Target Baud<br>Rate (bps) | Actual Baud<br>Rate (bps) | Baud Rate<br>Error | Oscillator<br>Divide | SB1PS[1:0]<br>(Prescaler Bits) | Reload Value in<br>SBRLH1:SBRLL1 |

|---------|---------------------------|---------------------------|--------------------|----------------------|--------------------------------|----------------------------------|

|         | Rute (Bp5)                |                           | LIIOI              | Factor               | (i resouler bits)              | OBILEITIOBILEET                  |

| MHz     | 230400                    | 230769                    | 0.16%              | 52                   | 11                             | 0xFFE6                           |

|         | 115200                    | 115385                    | 0.16%              | 104                  | 11                             | 0xFFCC                           |

|         | 57600                     | 57692                     | 0.16%              | 208                  | 11                             | 0xFF98                           |

| 12      | 28800                     | 28846                     | 0.16%              | 416                  | 11                             | 0xFF30                           |

| <br>    | 14400                     | 14388                     | 0.08%              | 834                  | 11                             | 0xFE5F                           |

| Clock   | 9600                      | 9600                      | 0.0%               | 1250                 | 11                             | 0xFD8F                           |

| 0<br>0  | 2400                      | 2400                      | 0.0%               | 5000                 | 11                             | 0xF63C                           |

| BRG     | 1200                      | 1200                      | 0.0%               | 10000                | 11                             | 0xEC78                           |

|         | 230400                    | 230769                    | 0.16%              | 104                  | 11                             | 0xFFCC                           |

| N       | 115200                    | 115385                    | 0.16%              | 208                  | 11                             | 0xFF98                           |

| 24 MHz  | 57600                     | 57692                     | 0.16%              | 416                  | 11                             | 0xFF30                           |

| 24      | 28800                     | 28777                     | 0.08%              | 834                  | 11                             | 0xFE5F                           |

| <br>    | 14400                     | 14406                     | 0.04%              | 1666                 | 11                             | 0xFCBF                           |

| Clock = | 9600                      | 9600                      | 0.0%               | 2500                 | 11                             | 0xFB1E                           |

| С<br>С  | 2400                      | 2400                      | 0.0%               | 10000                | 11                             | 0xEC78                           |

| BRG     | 1200                      | 1200                      | 0.0%               | 20000                | 11                             | 0xD8F0                           |

|         | 230400                    | 230769                    | 0.16%              | 208                  | 11                             | 0xFF98                           |

| N       | 115200                    | 115385                    | 0.16%              | 416                  | 11                             | 0xFF30                           |

| 48 MHz  | 57600                     | 57554                     | 0.08%              | 834                  | 11                             | 0xFE5F                           |

| 48      | 28800                     | 28812                     | 0.04%              | 1666                 | 11                             | 0xFCBF                           |

| 王<br>王  | 14400                     | 14397                     | 0.02%              | 3334                 | 11                             | 0xF97D                           |

| Clock   | 9600                      | 9600                      | 0.0%               | 5000                 | 11                             | 0xF63C                           |

| 0<br>0  | 2400                      | 2400                      | 0.0%               | 20000                | 11                             | 0xD8F0                           |

| BRG     | 1200                      | 1200                      | 0.0%               | 40000                | 11                             | 0xB1E0                           |

# Table 13.1. Baud Rate Generator Settings for Standard Baud Rates

#### 14.1.2. Mode 1: 16-bit Timer

Mode 1 operation is the same as Mode 0, except that the timer registers use all 16 bits. The timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

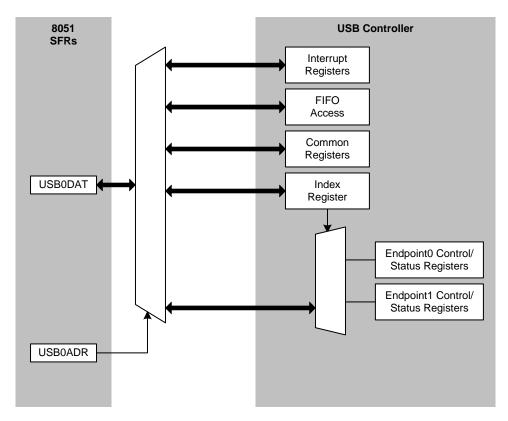

#### 14.1.3. Mode 2: 8-bit Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when GATE0 (TMOD.3) is logic 0 or when GATE0 is logic 1 and the input signal /INT0 is active (see Section "6.3.2. External Interrupts" on page 49 for details on the external input signals /INT0 and /INT1).

Figure 14.2. T0 Mode 2 Block Diagram