Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 12KB (6K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 640 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf4439t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

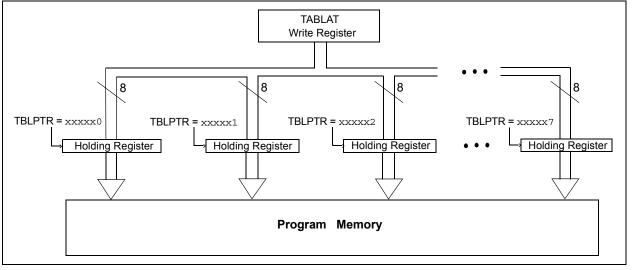

## 5.5 Writing to FLASH Program Memory

The minimum programming block is 4 words or 8 bytes. Word or byte programming is not supported.

Table Writes are used internally to load the holding registers needed to program the FLASH memory. There are 8 holding registers used by the Table Writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction has to be executed 8 times for each programming operation. All of the Table Write operations will essentially be short writes, because only the holding registers are written. At the end of updating 8 registers, the EECON1 register must be written to, to start the programming operation with a long write.

The long write is necessary for programming the internal FLASH. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The EEPROM on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump rated to operate over the voltage range of the device for byte or word operations.

## FIGURE 5-5: TABLE WRITES TO FLASH PROGRAM MEMORY

## 5.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 64 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer with address being erased.

- 4. Do the row erase procedure.

- 5. Load Table Pointer with address of first byte being written.

- 6. Write the first 8 bytes into the holding registers with auto-increment (TBLWT\*+ or TBLWT+\*).

- 7. Set EEPGD bit to point to program memory, clear the CFGS bit to access program memory, and set WREN to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write AAh to EECON2.

- 11. Set the WR bit. This will begin the write cycle.

- 12. The CPU will stall for duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Repeat steps 6-14 seven times, to write 64 bytes.

- 15. Verify the memory (Table Read).

This procedure will require about 18 ms to update one row of 64 bytes of memory. An example of the required code is given in Example 5-3.

**Note:** Before setting the WR bit, the table pointer address needs to be within the intended address range of the 8 bytes in the holding registers.

## 8.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are two Peripheral Interrupt Flag registers (PIR1, PIR2).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt, and after servicing that interrupt.

## REGISTER 8-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1

|               | R/W-0                   | R/W-0                                                                               | R-0           | R-0           | R/W-0                         | U-0          | R/W-0                 | R/W-0  |  |  |  |

|---------------|-------------------------|-------------------------------------------------------------------------------------|---------------|---------------|-------------------------------|--------------|-----------------------|--------|--|--|--|

|               | PSPIF <sup>(1)</sup>    | ADIF                                                                                | RCIF          | TXIF          | SSPIF                         | _            | TMR2IF <sup>(2)</sup> | TMR1IF |  |  |  |

|               | bit 7                   |                                                                                     |               |               |                               |              |                       | bit 0  |  |  |  |

| L '1 <b>-</b> |                         |                                                                                     |               |               |                               |              |                       |        |  |  |  |

| bit 7         |                         |                                                                                     |               |               | rupt Flag bit<br>e (must be c | loared in a  | oftwara               |        |  |  |  |

|               |                         | d or write ha                                                                       |               | s laken plac  | e (musi be c                  |              | ulwale)               |        |  |  |  |

| bit 6         | ADIF: A/D               | Converter Ir                                                                        | nterrupt Flac | a bit         |                               |              |                       |        |  |  |  |

|               |                         |                                                                                     |               |               | eared in soft                 | ware)        |                       |        |  |  |  |

|               | 0 = The A/I             | D conversion                                                                        | n is not com  | plete         |                               |              |                       |        |  |  |  |

| bit 5         |                         | RT Receive                                                                          |               |               |                               |              |                       |        |  |  |  |

|               |                         |                                                                                     |               |               | (cleared who                  | en RCREG     | is read)              |        |  |  |  |

|               |                         | SART receiv                                                                         |               |               |                               |              |                       |        |  |  |  |

| bit 4         |                         |                                                                                     |               |               |                               |              | on TXIF fund          | • ·    |  |  |  |

|               |                         | SART transm                                                                         |               |               | ipty (cleared                 | when IXF     | REG is written        | )      |  |  |  |

| bit 3         |                         | ster Synchro                                                                        |               | ••••          | upt Flag bit                  |              |                       |        |  |  |  |

|               |                         | •                                                                                   |               |               | ust be clear                  | ed in softw  | are)                  |        |  |  |  |

|               | 0 = Waiting             | g to transmit                                                                       | /receive      |               |                               |              | ,                     |        |  |  |  |

| bit 2         | Unimplem                | ented: Read                                                                         | d as '0'      |               |                               |              |                       |        |  |  |  |

| bit 1         | TMR2IF <sup>(2)</sup> : | TMR2 to P                                                                           | R2 Match Ir   | nterrupt Flag | j bit                         |              |                       |        |  |  |  |

|               |                         |                                                                                     |               | •             | eared in soft                 | ware)        |                       |        |  |  |  |

|               |                         | R2 to PR2 n                                                                         |               |               |                               |              |                       |        |  |  |  |

| bit 0         |                         | MR1 Overflo                                                                         |               | •             |                               | ,            |                       |        |  |  |  |

|               |                         | register over<br>egister did n                                                      | · ·           | st be cleare  | d in software                 | e)           |                       |        |  |  |  |

|               | 0 - 1000000             |                                                                                     | or overnow    |               |                               |              |                       |        |  |  |  |

|               | Note 1: 7               | Note 1: This bit is reserved on PIC18F2X39 devices; always maintain this bit clear. |               |               |                               |              |                       |        |  |  |  |

|               | <b>2</b> : 1            | This bit is res                                                                     | served for us | se by the Pr  | oMPT kerne                    | l; do not al | ter its value.        |        |  |  |  |

|               | Legend:                 |                                                                                     |               |               |                               |              |                       |        |  |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|         | U-0               | U-0           | U-0           | R/W-0         | R/W-0         | R/W-0      | R/W-0        | U-0     |

|---------|-------------------|---------------|---------------|---------------|---------------|------------|--------------|---------|

|         |                   |               |               | EEIF          | BCLIF         | LVDIF      | TMR3IF       | _       |

|         | bit 7             |               |               |               |               |            |              | bit 0   |

|         |                   |               |               |               |               |            |              |         |

| bit 7-5 | Unimplem          | ented: Rea    | d as '0'      |               |               |            |              |         |

| bit 4   | EEIF: Data        | EEPROM/I      | LASH Write    | e Operation   | Interrupt Fla | g bit      |              |         |

|         | 1 = The wr        | ite operatior | n is complete | e (must be c  | leared in sof | ftware)    |              |         |

|         | 0 = The wr        | ite operatior | n is not com  | plete, or has | not been st   | arted      |              |         |

| bit 3   | BCLIF: Bu         | s Collision I | nterrupt Flag | g bit         |               |            |              |         |

|         |                   |               | •             | be cleared i  | n software)   |            |              |         |

|         | 0 <b>= No bus</b> | collision oc  | curred        |               |               |            |              |         |

| bit 2   | LVDIF: Lov        | v Voltage De  | etect Interru | pt Flag bit   |               |            |              |         |

|         |                   | •             |               | ed (must be   |               | ,          |              |         |

|         | 0 = The de        | vice voltage  | is above th   | e Low Volta   | ge Detect tri | p point    |              |         |

| bit 1   |                   | MR3 Overflo   | •             | •             |               |            |              |         |

|         |                   | •             |               | st be cleared | d in software | e)         |              |         |

|         |                   | register did  |               | 1             |               |            |              |         |

| bit 0   | Unimplem          | ented: Rea    | d as '0'      |               |               |            |              |         |

|         |                   |               |               |               |               |            |              |         |

|         | Legend:           |               |               |               |               |            |              |         |

|         | R = Reada         | ble bit       | W = Wr        | itable bit    | U = Unin      | nplemented | bit, read as | '0'     |

|         | - n = Value       | at POR        | '1' = Bit     | is set        | '0' = Bit i   | s cleared  | x = Bit is ( | unknown |

## REGISTER 8-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2

## 8.6 INT0 Interrupt

External interrupts on the RB0/INT0, RB1/INT1 and RB2/INT2 pins are edge triggered: either rising, if the corresponding INTEDGx bit is set in the INTCON2 register, or falling, if the INTEDGx bit is clear. When a valid edge appears on the RBx/INTx pin, the corresponding flag bit INTxF is set. This interrupt can be disabled by clearing the corresponding enable bit INTxE. Flag bit INTxF must be cleared in software in the Interrupt Service Routine before re-enabling the interrupt. All external interrupts (INT0, INT1 and INT2) can wake-up the processor from SLEEP, if bit INTxE was set prior to going into SLEEP. If the global interrupt enable bit GIE is set, the processor will branch to the interrupt vector following wake-up.

The INT0 interrupt is always configured as a high priority interrupt, and cannot be reconfigured. Interrupt priority for INT1 and INT2 is determined by the value contained in the interrupt priority bits, INT1IP (INTCON3<6>) and INT2IP (INTCON3<7>).

Because it is always configured as a high priority interrupt, INTO cannot be used in conjunction with the ProMPT kernel; it must always be disabled (INTCON<4> = 0). Failure to do this may result in erratic operation of the motor control.

## 8.7 TMR0 Interrupt

In 8-bit mode (which is the default), an overflow in the TMR0 register (FFh  $\rightarrow$  00h) will set flag bit TMR0IF. In 16-bit mode, an overflow in the TMR0H:TMR0L register pair (FFFFh  $\rightarrow$  0000h) will set flag bit TMR0IF. The interrupt can be enabled or disabled by setting or clearing enable bit TMR0IE (INTCON<5>). Interrupt priority for Timer0 is determined by the value contained in the interrupt priority bit TMR0IP (INTCON2<2>). See Section 10.0 for further details on the Timer0 module.

## 8.8 PORTB Interrupt-on-Change

An input change on PORTB<7:4> sets flag bit RBIF (INTCON<0>). The interrupt can be enabled or disabled by setting or clearing the enable bit RBIE (INTCON<3>). Interrupt priority for PORTB interrupton-change is determined by the value contained in the interrupt priority bit RBIP (INTCON2<0>).

# 8.9 Context Saving During Interrupts

During an interrupt, the return PC value is saved on the stack. Additionally, the WREG, STATUS and BSR registers are saved on the fast return stack. If a fast return from interrupt is not used (see Section 4.3), the user may need to save the WREG, STATUS and BSR registers in software. Depending on the user's application, other registers may also need to be saved. Example 8-1 saves and restores the WREG, STATUS and BSR registers during an Interrupt Service Routine.

| EXAMPLE 8-1: | SAVING STATUS, | WREG AND BSR | <b>REGISTERS IN RAM</b> |

|--------------|----------------|--------------|-------------------------|

|              |                |              |                         |

|        | •                   |                                |

|--------|---------------------|--------------------------------|

| MOVWF  | W_TEMP              | ; W_TEMP is in virtual bank    |

| MOVFF  | STATUS, STATUS_TEMP | ; STATUS_TEMP located anywhere |

| MOVFF  | BSR, BSR_TEMP       | ; BSR located anywhere         |

| ;      |                     |                                |

| ; USER | ISR CODE            |                                |

| ;      |                     |                                |

| MOVFF  | BSR_TEMP, BSR       | ; Restore BSR                  |

| MOVF   | W_TEMP, W           | ; Restore WREG                 |

| MOVFF  | STATUS_TEMP, STATUS | ; Restore STATUS               |

|        |                     |                                |

## **REGISTER 9-1:** TRISE REGISTER

|       | R-0                     | R-0                         | R/W-0       | R/W-0             | U-0          | R/W-1     | R/W-1        | R/W-1  |

|-------|-------------------------|-----------------------------|-------------|-------------------|--------------|-----------|--------------|--------|

|       | IBF                     | OBF                         | IBOV        | PSPMODE           | —            | TRISE2    | TRISE1       | TRISE0 |

|       | bit 7                   |                             |             |                   |              |           |              | bit 0  |

|       |                         |                             |             |                   |              |           |              |        |

| bit 7 |                         | Buffer Full S               |             | -1                |              |           |              |        |

|       |                         | rd has been r               |             | d waiting to be   | read by the  | e CPU     |              |        |

| bit 6 |                         | out Buffer Fu               |             | t                 |              |           |              |        |

|       |                         |                             |             | previously writ   | ten word     |           |              |        |

|       | 0 = The ou              | utput buffer h              | has been re | ead               |              |           |              |        |

| bit 5 |                         |                             |             | ect bit (in Micro |              | ,         |              |        |

|       |                         | be cleared in               | •           | iously input wo   | nu nas not   | Deen reau |              |        |

|       | · ·                     | erflow occur                | ,           |                   |              |           |              |        |

| bit 4 |                         |                             |             | lode Select bit   |              |           |              |        |

|       |                         | el Slave Port               |             |                   |              |           |              |        |

| bit 3 |                         | al Purpose I<br>nented: Rea |             |                   |              |           |              |        |

| bit 2 | •                       | RE2 Direction               |             | it                |              |           |              |        |

| DIL Z | 1 = Input               |                             | Control D   | it.               |              |           |              |        |

|       | 0 = Output              | t                           |             |                   |              |           |              |        |

| bit 1 | -                       | RE1 Direction               | n Control b | it                |              |           |              |        |

|       | 1 = Input<br>0 = Output | +                           |             |                   |              |           |              |        |

| bit 0 |                         | RE0 Direction               | n Control h | it                |              |           |              |        |

| DIT U | 1 = Input               |                             |             | it i              |              |           |              |        |

|       | 0 = Output              | t                           |             |                   |              |           |              |        |

|       |                         |                             |             |                   |              |           |              |        |

|       | Legend:                 |                             |             |                   |              |           |              |        |

|       | R = Reada               | able bit                    | VV =        | Writable bit      | U = Unim     | plemented | bit, read as | 0'     |

|       | - n = Value             | e at POR                    | '1' =       | Bit is set        | '0' = Bit is | s cleared | x = Bit is u | nknown |

NOTES:

# 14.3 Software Interface

A sine table, stored in the ProMPT kernel, is used as the basis for synthesizing the DC bus using the PWM modules. The table values are accessed in sequence and scaled based on the frequency or the speed at which the motor is intended to run. The intended frequency input can be from an A/D channel or a digital value.

Parameters in the ProMPT modules can be accessed using the pre-defined Application Program Interface (API) methods. A list of the APIs is given in Section 14.3.3.

For example, to run the motor at 40 Hz, the user would invoke the PromMPT SetFrequency API:

i = ProMPT SetFrequency(40);

where i is an unsigned character variable. In this case, if i = 0 on return, the command has been successfully executed. If the frequency input is out of range, or if there is an error in setting the frequency, i is returned with a value of FFh.

Similarly, to check the frequency set by the ProMPT kernel, use the ProMPT\_GetFrequency API:

i = ProMPT\_GetFrequency(void);

where i is an unsigned character variable. Upon return from the ProMPT kernel, i will contain the frequency value in the ProMPT kernel.

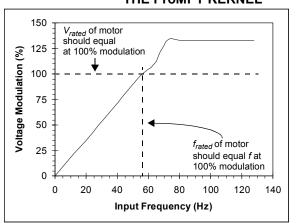

## 14.3.1 THE V/F CURVE

The ProMPT kernel contains a default V/F curve stored in memory. The default curve is linear, as shown in Figure 14-2. Table 14-1 shows the data points used to construct the curve.

Users may require a different V/F curve for their application, based on the load on the motor, or based on the characteristics of the motor used. The curve can be changed in the application program using the API method SetVFCurve (X, Y), where X is the frequency and Y is the level of modulation of the DC bus voltage. As a rule, in customizing the curve, the input frequency corresponding to the point on the V/F curve that gives 100% modulation should match the motor's rated frequency. Similarly, full modulation should occur at the motor's rated input voltage. (See Figure 14-2 for details.)

Examples of the characteristics for V/F curves for typical motor applications are shown in Section 14-2 (page 115).

## 14.3.2 PARAMETERS DEFINED BY THE ProMPT API METHODS

**Frequency:** The frequency (in Hz) of the supply current for steady state motor operation.

**Modulation:** The level of modulation (in percentage) applied to the DC supply voltage by the PWM through the H-bridge to produce AC drive current.

Acceleration rate: The rate of increase of motor speed, achieved by ramping up the supply frequency. Expressed in Hz/s.

**Deceleration rate:** The rate of decrease of motor speed, achieved by ramping down the supply frequency. Expressed in Hz/s.

**Boost:** The mode for starting a stopped motor by varying the supply current frequency and modulation until steady state speed is reached. Boost is defined in terms of a frequency, a starting and ending modulation, and a time interval for the transition between the two.

**PWM Frequency:** The sampling rate (in kHz) at which the PWM module operates.

### FIGURE 14-2: DEFAULT V/F CURVE FOR THE ProMPT KERNEL

| TABLE 14-1: | DATA POINTS FOR THE |

|-------------|---------------------|

|             | DEFAULT V/F CURVE   |

| Frequency (Hz) | % Modulation |

|----------------|--------------|

| 0              | 0            |

| 8              | 14           |

| 16             | 28           |

| 24             | 42           |

| 32             | 57           |

| 40             | 71           |

| 48             | 86           |

| 56             | 100          |

| 64             | 110          |

| 72             | 133          |

| 80             | 133          |

| 88             | 133          |

| 96             | 133          |

| 104            | 133          |

| 112            | 133          |

| 120            | 133          |

| 128            | 133          |

unsigned char ProMPT\_GetBoostTime() Resources used: 1 stack level Range of values: 0 to 255 Description: Returns the time in seconds for Boost mode.

unsigned char ProMPT\_GetDecelRate() Resources used: 1 stack level Range of values: 0 to 255 Description: Returns the current deceleration rate in Hz/second.

#### unsigned char ProMPT\_GetFrequency(void)

Resources used: 1 stack level

Range of values: 0 to 127

**Description:** Returns the current output frequency in Hz. This may not be the frequency commanded due to Boost or Accel/Decel logic.

unsigned char ProMPT\_GetModulation(void)

Resources used: Hardware Multiplier; 1 stack level

Range of values: 0 to 200

**Description:** Returns the current output modulation in %.

#### unsigned char ProMPT\_GetParameter(unsigned char parameter)

Resources used: 1 stack level

**Description:** In addition to its pre-defined API methods, the ProMPT kernel allows the user to custom define up to 16 functions for control or communication purposes not covered by the ProMPT APIs. These parameters are used to communicate with motor control GUI evaluation tools, such as Microchip's DashDriveMP<sup>TM</sup>. This method returns the current value of any one of the parameters.

#### unsigned char ProMPT\_GetVFCurve(unsigned char point)

Resources used: Hardware Multiplier; 1 stack level

**Description:** This function returns one of the 17 modulation values (in %) of the V/F curve. Each point represents a frequency increment of 8 Hz, ranging from point 0 (0 Hz) to point 16 (128 Hz).

#### void ProMPT\_Init(unsigned char PWMfrequency)

**Resources used:** 64 Bytes RAM; Timer2; PWM1 and PWM2; High Priority Interrupt Vector; Hardware Multiplier; fast call/return; FSR 0; TBLPTR; 2 stack levels

PWMfrequency values: 0 or 1

**Description:** This function must be called before all other ProMPT methods, and it must be called only once. This routine configures Timer2 and the PWM outputs.

When PWMfrequency is '0', the module's operating frequency is 9.75 kHz. When PWMfrequency is '1', the module's operating frequency is 19.53 kHz.

**Note:** Since the high priority interrupt is used, the fast call/return cannot be used by other routines.

#### void ProMPT\_SetLineVoltage(unsigned char voltage)

Resources used: Hardware Multiplier; 0 stack levels

#### voltage range: 0 to 255

**Description:** Sets the line voltage for Automatic Voltage Compensation. The units for SetLineVoltage and SetMotorVoltage must be the same for accurate operation. The values passed to SetMotorVoltage and SetLineVoltage can be the same to disable voltage compensation.

#### void ProMPT\_SetMotorVoltage(unsigned char voltage)

Resources used: Hardware Multiplier; 0 stack levels

#### voltage range: 0 to 255

**Description:** Sets the motor rating for Automatic Voltage Compensation. The units for SetLineVoltage and SetMotorVoltage must be the same for accurate operation. The values passed to SetMotorVoltage and SetLineVoltage can be the same to disable voltage compensation.

#### void ProMPT SetParameter (unsigned char parameter, unsigned char value)

Resources used: 0 stack levels

#### parameter range:

**Description:** In addition to its pre-defined API methods, the ProMPT kernel allows the user to custom define up to 16 functions for control or communication purposes not covered by the ProMPT APIs. This function sets the value of the specified user defined function.

#### void ProMPT\_SetPWMfrequency(unsigned char PWMfrequency)

PWMfrequency values: 0 or 1

#### Resources used: Timer2; 1 stack level

**Description:** This sets and changes the PWM switching frequency. Typically, this is set with the Init() function. When PWMfrequency is '0', the module's operating frequency is 9.75 kHz. When PWMfrequency is '1', the module's operating frequency is 19.53 kHz.

#### void ProMPT\_SetVFCurve(unsigned char point, unsigned char value)

**Resources used:** Hardware Multiplier; 0 stack level

point range: 0 to 16 (0 = 0 Hz, 1 = 8 Hz, 2 = 16 Hz..... 17 = 128 Hz)

value range: 0 to 200

**Description:** This sets one of the 17 modulation values (in %) for the V/F curve. Each point represents a frequency increment of 8 Hz, ranging from point 0 (0 Hz) to point 16 (128 Hz).

#### unsigned char ProMPT\_Tick(void)

Resources used: 1 stack level

**Description:** The value of the Tick timer flag becomes '1' every 62.5 ms (1/16 second). This can be used for timing applications. clearTick must be called in the timing routine when this is serviced.

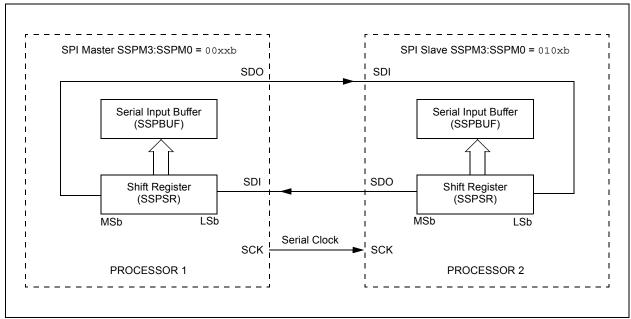

### 16.3.3 ENABLING SPI I/O

To enable the serial port, SSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON registers, and then set the SSPEN bit. This configures the SDI, SDO, SCK, and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed. That is:

- SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISC<4> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

## 16.3.4 TYPICAL CONNECTION

Figure 16-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge, and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- Master sends data Slave sends dummy data

- Master sends data Slave sends data

- Master sends dummy data Slave sends data

### FIGURE 16-2: SPI MASTER/SLAVE CONNECTION

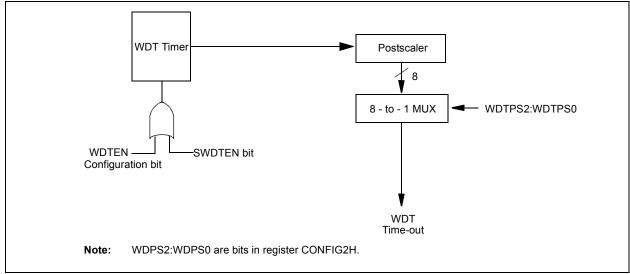

## 20.2.2 WDT POSTSCALER

The WDT has a postscaler that can extend the WDT Reset period. The postscaler is selected at the time of the device programming, by the value written to the CONFIG2H configuration register.

FIGURE 20-1: WATCHDOG TIMER BLOCK DIAGRAM

## TABLE 20-2: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|-------|--------|--------|--------|--------|

| CONFIG2H | _     | _     |       | —     | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | _     | _     | RI    | TO     | PD     | POR    | BOR    |

| WDTCON   | —     | _     | _     | —     | —      | _      | _      | SWDTEN |

Legend: Shaded cells are not used by the Watchdog Timer.

# 21.0 INSTRUCTION SET SUMMARY

The PIC18FXXX instruction set adds many enhancements to the previous PICmicro instruction sets, while maintaining an easy migration from these PICmicro instruction sets.

Most instructions are a single program memory word (16-bits), but there are three instructions that require two program memory locations.

Each single word instruction is a 16-bit word divided into an OPCODE, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18FXXX instruction set summary in Table 21-2 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 21-1 shows the opcode field descriptions.

Most byte-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction.

The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All **bit-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located.

The **literal** instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The **control** instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the Call or Return instructions (specified by 's')

- The mode of the Table Read and Table Write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for three double-word instructions. These three instructions were made double-word instructions, so that all the required information is available in these 32 bits. In the second word, the 4 MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 21-1 shows the general formats that the instructions can have.

All examples use the format `nnh' to represent a hexadecimal number, where `h' signifies a hexadecimal digit.

The Instruction Set Summary, shown in Table 21-2, lists the instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>).

Section 21.1 provides a description of each instruction.

## TABLE 21-2: PIC18FXXX INSTRUCTION SET

| Mnemonic,<br>Operands |                                 | Description                              | Cycles     | 16-Bit Instruction Word |       |      |      | Status          | Notes      |

|-----------------------|---------------------------------|------------------------------------------|------------|-------------------------|-------|------|------|-----------------|------------|

|                       |                                 | Description                              | Cycles     | MSb                     |       |      | LSb  | Affected        | Notes      |

| BYTE-ORI              | ENTED F                         | ILE REGISTER OPERATIONS                  |            |                         |       |      |      |                 |            |

| ADDWF                 | f, d, a                         | Add WREG and f                           | 1          | 0010                    | 01da0 | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f              | 1          | 0010                    | 0da   | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| ANDWF                 | f, d, a                         | AND WREG with f                          | 1          | 0001                    | 01da  | ffff | ffff | Z, N            | 1,2        |

| CLRF                  | f, a                            | Clear f                                  | 1          | 0110                    | 101a  | ffff | ffff | Z               | 2          |

| COMF                  | f, d, a                         | Complement f                             | 1          | 0001                    | 11da  | ffff | ffff | Z, N            | 1, 2       |

| CPFSEQ                | f, a                            | Compare f with WREG, skip =              | 1 (2 or 3) | 0110                    | 001a  | ffff | ffff | None            | 4          |

| CPFSGT                | f, a                            | Compare f with WREG, skip >              | 1 (2 or 3) | 0110                    | 010a  | ffff | ffff | None            | 4          |

| CPFSLT                | f, a                            | Compare f with WREG, skip <              | 1 (2 or 3) | 0110                    | 000a  | ffff | ffff | None            | 1, 2       |

| DECF                  | f, d, a                         | Decrement f                              | 1 ΄        | 0000                    | 01da  | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3) | 0010                    | 11da  | ffff | ffff | None            | 1, 2, 3, 4 |

| DCFSNZ                | f.d.a                           | Decrement f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 11da  | ffff | ffff | None            | 1, 2       |

| INCF                  | f, d, a                         | Increment f                              | 1          | 0010                    | 10da  | ffff | ffff | C, DC, Z, OV, N | 1, 2, 3, 4 |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3) | 0011                    | 11da  | ffff | ffff | None            | 4          |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3) | 0100                    | 10da  | ffff | ffff | None            | 1, 2       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                 | 1          | 0001                    | 00da  | ffff | ffff | Z, N            | 1, 2       |

| MOVF                  | f, d, a                         | Move f                                   | 1          | 0101                    | 00da  | ffff | ffff | Z, N            | 1          |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2          | 1100                    | ffff  | ffff | ffff | None            |            |

|                       | ·s, ·u                          | f <sub>d</sub> (destination) 2nd word    | -          | 1111                    | ffff  | ffff | ffff |                 |            |

| MOVWF                 | f, a                            | Move WREG to f                           | 1          | 0110                    | 111a  | ffff | ffff | None            |            |

| MULWF                 | f, a                            | Multiply WREG with f                     | 1          | 0000                    | 001a  | ffff | ffff | None            |            |

| NEGF                  | f, a                            | Negate f                                 | 1          | 0110                    | 110a  | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| RLCF                  | f, d, a                         | Rotate Left f through Carry              | 1          | 0011                    | 01da  | ffff | ffff | C, Z, N         | ., _       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                 | 1          | 0100                    | 01da  | ffff | ffff | Z, N            | 1, 2       |

| RRCF                  | f, d, a                         | Rotate Right f through Carry             | 1          | 0011                    | 00da  | ffff | ffff | C, Z, N         | 1, 2       |

| RRNCF                 | f, d, a                         | Rotate Right f (No Carry)                | 1          | 0100                    | 00da  | ffff | ffff | Z, N            |            |

| SETF                  | f, a                            | Set f                                    | 1          | 0110                    | 100a  | ffff | ffff | None            |            |

| SUBFWB                | f, d, a                         | Subtract f from WREG with borrow         | 1          | 0101                    | 01da  | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SUBWF                 | f, d, a                         | Subtract WREG from f                     | 1          | 0101                    | 11da  | ffff | ffff | C, DC, Z, OV, N |            |

| SUBWFB                | f, d, a                         | Subtract WREG from f with<br>borrow      | 1          | 0101                    | 10da  | ffff | ffff | C, DC, Z, OV, N | 1, 2       |

| SWAPF                 | f, d, a                         | Swap nibbles in f                        | 1          | 0011                    | 10da  | ffff | ffff | None            | 4          |

| TSTFSZ                | f, a                            | Test f, skip if 0                        | 1 (2 or 3) | 0110                    | 011a  | ffff | ffff | None            | 1, 2       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                 | 1          | 0001                    | 10da  | ffff | ffff | Z, N            | ., -       |

|                       | , ,                             | E REGISTER OPERATIONS                    |            | 0001                    | Ioda  |      |      | 2,11            |            |

| BCF                   | f, b, a                         | Bit Clear f                              | 1          | 1001                    | bbb - | ffe  | fff  | None            | 1, 2       |

| BSF                   | , ,                             |                                          | 1          | 1001                    | bbba  | ffff | ffff |                 | 1, 2       |

|                       | f, b, a                         | Bit Set f                                | 1 (0 0)    | 1000                    | bbba  | ffff | ffff | None            |            |

| BTFSC                 | f, b, a                         | Bit Test f, Skip if Clear                | 1 (2 or 3) | 1011                    | bbba  | ffff | ffff | None            | 3, 4       |

| BTFSS                 | f,b,a                           | Bit Test f, Skip if Set                  | 1 (2 or 3) | 1010                    | bbba  | ffff | ffff | None            | 3, 4       |

| BTG                   | f, d, a                         | Bit Toggle f                             | 1          | 0111                    | bbba  | ffff | ffff | None            | 1, 2       |

**Note** 1: When a PORT register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**4:** Some instructions are 2-word instructions. The second word of these instructions will be executed as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

5: If the Table Write starts the write cycle to internal memory, the write will continue until terminated.

=

= =

=

address (HERE)

1; address (HERE+12) 0; address (HERE+2)

PC

After Instruction

If Carry PC

If Carry PC

| ANDWF              | AND W with f                                                                                                                                                                                                                                                                      | BC               | Branch if Carry                                                                                                                                                                                                                                |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:            | [ <i>label</i> ] ANDWF f[,d[,a]                                                                                                                                                                                                                                                   | Syntax:          | [ <i>label</i> ] BC n                                                                                                                                                                                                                          |

| Operands:          | $0 \leq f \leq 255$                                                                                                                                                                                                                                                               | Operands:        | $-128 \le n \le 127$                                                                                                                                                                                                                           |

|                    | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                            | Operation:       | if carry bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                          |

| Operation:         | (W) .AND. (f) $\rightarrow$ dest                                                                                                                                                                                                                                                  | Status Affected: | None                                                                                                                                                                                                                                           |

| Status Affected:   | N,Z                                                                                                                                                                                                                                                                               | Encoding:        | 1110 0010 nnnn nnnn                                                                                                                                                                                                                            |

| Encoding:          | 0001 01da ffff ffff                                                                                                                                                                                                                                                               | Description:     | If the Carry bit is '1', then the                                                                                                                                                                                                              |

| Description:       | The contents of W are AND'ed with<br>register 'f'. If 'd' is 0, the result is<br>stored in W. If 'd' is 1, the result is<br>stored back in register 'f' (default). If<br>'a' is 0, the Access Bank will be<br>selected. If 'a' is 1, the BSR will not<br>be overridden (default). |                  | program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will<br>have incremented to fetch the next<br>instruction, the new address will be<br>PC+2+2n. This instruction is then<br>a two-cycle instruction. |

| Words:             | 1                                                                                                                                                                                                                                                                                 | Words:           | 1                                                                                                                                                                                                                                              |

| Cycles:            | 1                                                                                                                                                                                                                                                                                 | Cycles:          | 1(2)                                                                                                                                                                                                                                           |

| Q Cycle Activity:  |                                                                                                                                                                                                                                                                                   | Q Cycle Activity | :                                                                                                                                                                                                                                              |

| Q1                 | Q2 Q3 Q4                                                                                                                                                                                                                                                                          | If Jump:         |                                                                                                                                                                                                                                                |

| Decode             | Read Process Write to                                                                                                                                                                                                                                                             | Q1               | Q2 Q3 Q4                                                                                                                                                                                                                                       |

|                    | register 'f' Data destination                                                                                                                                                                                                                                                     | Decode           | Read literal Process Write to PC<br>'n' Data                                                                                                                                                                                                   |

| Example:           | ANDWF REG, 0, 0                                                                                                                                                                                                                                                                   | No<br>operation  | No No No<br>operation operation                                                                                                                                                                                                                |

| Before Instru<br>W |                                                                                                                                                                                                                                                                                   | If No Jump:      |                                                                                                                                                                                                                                                |

| REG                | = 0x17<br>= 0xC2                                                                                                                                                                                                                                                                  | Q1               | Q2 Q3 Q4                                                                                                                                                                                                                                       |

| After Instruct     | ion                                                                                                                                                                                                                                                                               | Decode           | Read literal Process No                                                                                                                                                                                                                        |

| W                  | = 0x02                                                                                                                                                                                                                                                                            |                  | 'n' Data operation                                                                                                                                                                                                                             |

| REG                | = 0xC2                                                                                                                                                                                                                                                                            | Example:         | HERE BC 5                                                                                                                                                                                                                                      |

|                    |                                                                                                                                                                                                                                                                                   | Before Instru    | uction                                                                                                                                                                                                                                         |

| COMF                                                 | Complement f                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                              | [ <i>label</i> ] COMF f[,d[,a]                                                                                                                                                                                                                                                                                                         |

| Operands:                                            | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                     |

| Operation:                                           | $(\overline{f}) \rightarrow dest$                                                                                                                                                                                                                                                                                                      |

| Status Affected:                                     | N, Z                                                                                                                                                                                                                                                                                                                                   |

| Encoding:                                            | 0001 11da ffff ffff                                                                                                                                                                                                                                                                                                                    |

| Description:                                         | The contents of register 'f' are com-<br>plemented. If 'd' is 0, the result is<br>stored in W. If 'd' is 1, the result is<br>stored back in register 'f' (default). If<br>'a' is 0, the Access Bank will be<br>selected, overriding the BSR value.<br>If 'a' = 1, then the bank will be<br>selected as per the BSR value<br>(default). |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                                                      |

| Cycles:                                              | 1                                                                                                                                                                                                                                                                                                                                      |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                                                                                                                                        |

| Q1                                                   | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                               |

| Decode                                               | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                         |

| Example:                                             | COMF REG, 0, 0                                                                                                                                                                                                                                                                                                                         |

| Before Instruc<br>REG<br>After Instructi<br>REG<br>W | = 0x13                                                                                                                                                                                                                                                                                                                                 |

| CPFSE                                                       | Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Compare f with W, skip if f = W                                                                                                                                                                   |                                                                                                   |  |  |  |  |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | [label] (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CPFSEQ f[                                                                                                                                                                                         | ,a]                                                                                               |  |  |  |  |

| Operand                                                     | ds:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $0 \le f \le 255$<br>$a \in [0,1]$                                                                                                                                                                |                                                                                                   |  |  |  |  |