Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 508                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 40MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 39                                                                      |

| Program Memory Size        | 60KB (60K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | External                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s08dz60f2mlfr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

**Section Number**

Page

### Chapter 1 Device Overview

| 1.1 | Devices in the MC9S08DZ60 Series | .21 |

|-----|----------------------------------|-----|

| 1.2 | MCU Block Diagram                | .22 |

| 1.3 | System Clock Distribution        | .24 |

## Chapter 2 Pins and Connections

| 2.1 | Device | Pin Assignment                                              | 27 |

|-----|--------|-------------------------------------------------------------|----|

|     |        | nended System Connections                                   |    |

|     |        | Power                                                       |    |

|     | 2.2.2  | Oscillator                                                  | 31 |

|     | 2.2.3  | RESET                                                       | 31 |

|     | 2.2.4  | Background / Mode Select (BKGD/MS)                          | 32 |

|     |        | ADC Reference Pins (V <sub>REFH</sub> , V <sub>REFL</sub> ) |    |

|     |        | General-Purpose I/O and Peripheral Ports                    |    |

|     |        |                                                             |    |

# Chapter 3 Modes of Operation

| Introduc        | ction                                                                  | 35                                                                                                                                                                                  |

|-----------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features        | 5                                                                      | 35                                                                                                                                                                                  |

| Run Mo          | de                                                                     | 35                                                                                                                                                                                  |

| Active <b>E</b> | Background Mode                                                        | 35                                                                                                                                                                                  |

|                 |                                                                        |                                                                                                                                                                                     |

| Stop Mo         | odes                                                                   |                                                                                                                                                                                     |

| 3.6.1           | Stop3 Mode                                                             |                                                                                                                                                                                     |

| 3.6.2           | Stop2 Mode                                                             |                                                                                                                                                                                     |

|                 |                                                                        |                                                                                                                                                                                     |

|                 | Features<br>Run Mo<br>Active H<br>Wait Mo<br>Stop Mo<br>3.6.1<br>3.6.2 | Introduction<br>Features<br>Run Mode<br>Active Background Mode<br>Wait Mode<br>Stop Modes<br>3.6.1 Stop3 Mode<br>3.6.2 Stop2 Mode<br>3.6.3 On-Chip Peripheral Modules in Stop Modes |

## Chapter 4 Memory

| 4.1 | MC9S08DZ60 Series Memory Map           | 41 |

|-----|----------------------------------------|----|

| 4.2 | Reset and Interrupt Vector Assignments | 42 |

| 4.3 | Register Addresses and Bit Assignments |    |

|     | RĂM                                    |    |

| 4.5 | Flash and EEPROM                       |    |

|     | 4.5.1 Features                         |    |

|     |                                        |    |

# Chapter 1 Device Overview

MC9S08DZ60 Series devices provide significant value to customers looking to combine Controller Area Network (CAN) and embedded EEPROM in their applications. This combination will provide lower costs, enhanced performance, and higher quality.

# 1.1 Devices in the MC9S08DZ60 Series

This data sheet covers members of the MC9S08DZ60 Series of MCUs:

- MC9S08DZ60

- MC9S08DZ48

- MC9S08DZ32

- MC9S08DZ16

Table 1-1 summarizes the feature set available in the MC9S08DZ60 Series.

# 6.5.5 Port E Registers

Port E is controlled by the registers listed below.

### 6.5.5.1 Port E Data Register (PTED)

| _      | 7     | 6     | 5     | 4     | 3     | 2     | 1                  | 0     |

|--------|-------|-------|-------|-------|-------|-------|--------------------|-------|

| R<br>W | PTED7 | PTED6 | PTED5 | PTED4 | PTED3 | PTED2 | PTED1 <sup>1</sup> | PTED0 |

| Reset: | 0     | 0     | 0     | 0     | 0     | 0     | 0                  | 0     |

#### Figure 6-32. Port E Data Register (PTED)

<sup>1</sup> Reads of this bit always return the pin value of the associated pin, regardless of the value stored in the port data direction bit.

#### Table 6-30. PTED Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTED[7:0] | Port E Data Register Bits — For port E pins that are inputs, reads return the logic level on the pin. For port E pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port E pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTED to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

### 6.5.5.2 Port E Data Direction Register (PTEDD)

| _      | 7      | 6      | 5      | 4      | 3      | 2      | 1                   | 0      |

|--------|--------|--------|--------|--------|--------|--------|---------------------|--------|

| R<br>W | PTEDD7 | PTEDD6 | PTEDD5 | PTEDD4 | PTEDD3 | PTEDD2 | PTEDD1 <sup>1</sup> | PTEDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0                   | 0      |

#### Figure 6-33. Port E Data Direction Register (PTEDD)

<sup>1</sup> PTEDD1 has no effect on the input-only PTE1 pin.

#### Table 6-31. PTEDD Register Field Descriptions

| Field             | Description                                                                                                                                                                         |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTEDD[7:0] | <b>Data Direction for Port E Bits</b> — These read/write bits control the direction of port E pins and what is read for PTED reads.                                                 |

|                   | <ul> <li>0 Input (output driver disabled) and reads return the pin value.</li> <li>1 Output driver enabled for port E bit n and PTED reads return the contents of PTEDn.</li> </ul> |

**Chapter 6 Parallel Input/Output Control**

# 6.5.6 Port F Registers

Port F is controlled by the registers listed below.

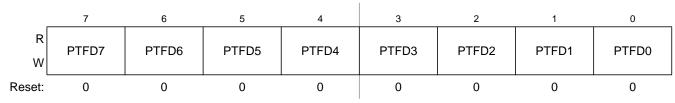

### 6.5.6.1 Port F Data Register (PTFD)

#### Figure 6-37. Port F Data Register (PTFD)

#### Table 6-35. PTFD Register Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTFD[7:0] | Port F Data Register Bits — For port F pins that are inputs, reads return the logic level on the pin. For port F pins that are configured as outputs, reads return the last value written to this register. Writes are latched into all bits of this register. For port F pins that are configured as outputs, the logic level is driven out the corresponding MCU pin. Reset forces PTFD to all 0s, but these 0s are not driven out the corresponding pins because reset also configures all port pins as high-impedance inputs with pull-ups disabled. |

## 6.5.6.2 Port F Data Direction Register (PTFDD)

|        | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| R<br>W | PTFDD7 | PTFDD6 | PTFDD5 | PTFDD4 | PTFDD3 | PTFDD2 | PTFDD1 | PTFDD0 |

| Reset: | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

#### Figure 6-38. Port F Data Direction Register (PTFDD)

#### Table 6-36. PTFDD Register Field Descriptions

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <b>Data Direction for Port F Bits</b> — These read/write bits control the direction of port F pins and what is read for PTFD reads.                                             |

|       | <ol> <li>Input (output driver disabled) and reads return the pin value.</li> <li>Output driver enabled for port F bit n and PTFD reads return the contents of PTFDn.</li> </ol> |

#### Chapter 7 Central Processor Unit (S08CPUV3)

| Source<br>Form                                                                                                   | Operation                                                                                                                                                                                                                                                           | Address<br>Mode<br>O                                                                                     | Object Code                                                                                  | Cycles                                    | Cyc-by-Cyc                                                           | Affect<br>on CCR      |         |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------|-----------------------|---------|

| Form                                                                                                             | -                                                                                                                                                                                                                                                                   | PdA                                                                                                      | -                                                                                            |                                           | Details                                                              | <b>V</b> 1 1 <b>H</b> | INZC    |

| BPL rel                                                                                                          | Branch if Plus (if N = 0)                                                                                                                                                                                                                                           | REL                                                                                                      | 2A rr                                                                                        | 3                                         | qqq                                                                  | - 1 1 -               |         |

| BRA rel                                                                                                          | Branch Always (if I = 1)                                                                                                                                                                                                                                            | REL                                                                                                      | 20 rr                                                                                        | 3                                         | qqq                                                                  | - 1 1 -               |         |

| BRCLR n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Clear (if (Mn) = 0)                                                                                                                                                                                                                | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 01 dd rr<br>03 dd rr<br>05 dd rr<br>07 dd rr<br>09 dd rr<br>0B dd rr<br>0D dd rr<br>0F dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5      | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp                   | - 1 1 -               | \$      |

| BRN rel                                                                                                          | Branch Never (if I = 0)                                                                                                                                                                                                                                             | REL                                                                                                      | 21 rr                                                                                        | 3                                         | qqq                                                                  | - 1 1 -               |         |

| BRSET n,opr8a,rel                                                                                                | Branch if Bit <i>n</i> in Memory Set (if (Mn) = 1)                                                                                                                                                                                                                  | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 00 dd rr<br>02 dd rr<br>04 dd rr<br>06 dd rr<br>08 dd rr<br>0A dd rr<br>0C dd rr<br>0E dd rr | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp<br>rpppp          | - 1 1 -               | \$      |

| BSET <i>n,opr8a</i>                                                                                              | Set Bit <i>n</i> in Memory (Mn ← 1)                                                                                                                                                                                                                                 | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 10 dd<br>12 dd<br>14 dd<br>16 dd<br>18 dd<br>1A dd<br>1C dd<br>1E dd                         | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp<br>rfwpp | - 1 1 -               |         |

| BSR rel                                                                                                          | $\begin{array}{c} \text{Branch to Subroutine} \\ \text{PC} \leftarrow (\text{PC}) + \$0002 \\ \text{push (PCL); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{push (PCH); SP} \leftarrow (\text{SP}) - \$0001 \\ \text{PC} \leftarrow (\text{PC}) + rel \end{array}$ | REL                                                                                                      | AD rr                                                                                        | 5                                         | gqqaa                                                                | - 1 1 -               |         |

| CBEQ opr8a,rel<br>CBEQA #opr8i,rel<br>CBEQX #opr8i,rel<br>CBEQ oprx8,X+,rel<br>CBEQ ,X+,rel<br>CBEQ oprx8,SP,rel | Compare and Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(X) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$<br>Branch if $(A) = (M)$                                                                                                      | DIR<br>IMM<br>IX1+<br>IX+<br>SP1                                                                         | 31 dd rr<br>41 ii rr<br>51 ii rr<br>61 ff rr<br>71 rr<br>9E 61 ff rr                         | 5<br>4<br>5<br>5<br>6                     | rpppp<br>pppp<br>pppp<br>rpppp<br>rfppp<br>prpppp                    | - 1 1 -               |         |

| CLC                                                                                                              | Clear Carry Bit (C $\leftarrow$ 0)                                                                                                                                                                                                                                  | INH                                                                                                      | 98                                                                                           | 1                                         | q                                                                    | - 1 1 -               | 0       |

| CLI                                                                                                              | Clear Interrupt Mask Bit (I $\leftarrow$ 0)                                                                                                                                                                                                                         | INH                                                                                                      | 9A                                                                                           | 1                                         | p                                                                    | - 1 1 -               | 0       |

| CLR opr8a<br>CLRA<br>CLRX<br>CLRH<br>CLR oprx8,X<br>CLR ,X<br>CLR oprx8,SP                                       | Clear $M \leftarrow \$00$<br>$A \leftarrow \$00$<br>$X \leftarrow \$00$<br>$H \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$<br>$M \leftarrow \$00$                                                                                                 | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                                    | 3F dd<br>4F<br>5F<br>8C<br>6F ff<br>7F<br>9E 6F ff                                           | 5<br>1<br>1<br>5<br>4<br>6                | rfwpp<br>p<br>p<br>rfwpp<br>rfwp<br>prfwpp                           | 011-                  | - 0 1 - |

#### Table 7-2. Instruction Set Summary (Sheet 3 of 9)

### 9.1.2 Features

The ACMP has the following features:

- Full rail to rail supply operation.

- Selectable interrupt on rising edge, falling edge, or either rising or falling edges of comparator output.

- Option to compare to fixed internal bandgap reference voltage.

- Option to allow comparator output to be visible on a pin, ACMPxO.

### 9.1.3 Modes of Operation

This section defines the ACMP operation in wait, stop, and background debug modes.

#### 9.1.3.1 ACMP in Wait Mode

The ACMP continues to run in wait mode if enabled before executing the appropriate instruction. Therefore, the ACMP can be used to bring the MCU out of wait mode if the ACMP interrupt is enabled (ACIE is set). For lowest possible current consumption, the ACMP should be disabled by software if not required as an interrupt source during wait mode.

### 9.1.3.2 ACMP in Stop Modes

The ACMP is disabled in all stop modes, regardless of the settings before executing the stop instruction. Therefore, the ACMP cannot be used as a wake up source from stop modes.

During stop2 mode, the ACMP module is fully powered down. Upon wake-up from stop2 mode, the ACMP module is in the reset state.

During stop3 mode, clocks to the ACMP module are halted. No registers are affected. In addition, the ACMP comparator circuit enters a low-power state. No compare operation occurs while in stop3.

If stop3 is exited with a reset, the ACMP is put into its reset state. If stop3 is exited with an interrupt, the ACMP continues from the state it was in when stop3 was entered.

#### 9.1.3.3 ACMP in Active Background Mode

When the microcontroller is in active background mode, the ACMP continues to operate normally.

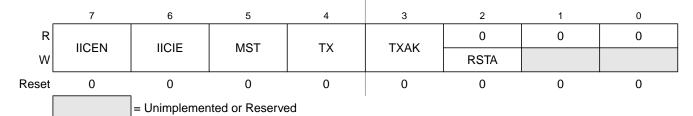

# 11.3.3 IIC Control Register (IICC1)

Figure 11-5. IIC Control Register (IICC1)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                      |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IICEN | IIC Enable. The IICEN bit determines whether the IIC module is enabled.         0 IIC is not enabled         1 IIC is enabled                                                                                                                                                                                                                                                    |

| 6<br>IICIE | IIC Interrupt Enable. The IICIE bit determines whether an IIC interrupt is requested.         0 IIC interrupt request not enabled         1 IIC interrupt request enabled                                                                                                                                                                                                        |

| 5<br>MST   | <ul> <li>Master Mode Select. The MST bit changes from a 0 to a 1 when a start signal is generated on the bus and master mode is selected. When this bit changes from a 1 to a 0 a stop signal is generated and the mode of operation changes from master to slave.</li> <li>0 Slave mode</li> <li>1 Master mode</li> </ul>                                                       |

| 4<br>TX    | Transmit Mode Select. The TX bit selects the direction of master and slave transfers. In master mode, this bit<br>should be set according to the type of transfer required. Therefore, for address cycles, this bit is always high.<br>When addressed as a slave, this bit should be set by software according to the SRW bit in the status register.<br>0 Receive<br>1 Transmit |

| 3<br>TXAK  | Transmit Acknowledge Enable. This bit specifies the value driven onto the SDA during data acknowledge<br>cycles for master and slave receivers.0An acknowledge signal is sent out to the bus after receiving one data byte<br>11No acknowledge signal response is sent                                                                                                           |

| 2<br>RSTA  | <b>Repeat start.</b> Writing a 1 to this bit generates a repeated start condition provided it is the current master. This bit is always read as cleared. Attempting a repeat at the wrong time results in loss of arbitration.                                                                                                                                                   |

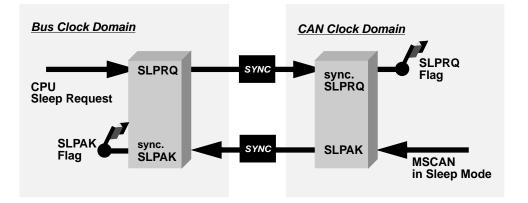

## 12.5.5.4 MSCAN Sleep Mode

The CPU can request the MSCAN to enter this low power mode by asserting the SLPRQ bit in the CANCTL0 register. The time when the MSCAN enters sleep mode depends on a fixed synchronization delay and its current activity:

- If there are one or more message buffers scheduled for transmission (TXEx = 0), the MSCAN will continue to transmit until all transmit message buffers are empty (TXEx = 1, transmitted successfully or aborted) and then goes into sleep mode.

- If the MSCAN is receiving, it continues to receive and goes into sleep mode as soon as the CAN bus next becomes idle.

- If the MSCAN is neither transmitting nor receiving, it immediately goes into sleep mode.

Figure 12-44. Sleep Request / Acknowledge Cycle

#### NOTE

The application software must avoid setting up a transmission (by clearing one or more TXEx flag(s)) and immediately request sleep mode (by setting SLPRQ). Whether the MSCAN starts transmitting or goes into sleep mode directly depends on the exact sequence of operations.

If sleep mode is active, the SLPRQ and SLPAK bits are set (Figure 12-44). The application software must use SLPAK as a handshake indication for the request (SLPRQ) to go into sleep mode.

When in sleep mode (SLPRQ = 1 and SLPAK = 1), the MSCAN stops its internal clocks. However, clocks that allow register accesses from the CPU side continue to run.

If the MSCAN is in bus-off state, it stops counting the 128 occurrences of 11 consecutive recessive bits due to the stopped clocks. The TXCAN pin remains in a recessive state. If RXF = 1, the message can be read and RXF can be cleared. Shifting a new message into the foreground buffer of the receiver FIFO (RxFG) does not take place while in sleep mode.

It is possible to access the transmit buffers and to clear the associated TXE flags. No message abort takes place while in sleep mode.

# Chapter 13 Serial Peripheral Interface (S08SPIV3)

# 13.1 Introduction

The serial peripheral interface (SPI) module provides for full-duplex, synchronous, serial communication between the MCU and peripheral devices. These peripheral devices can include other microcontrollers, analog-to-digital converters, shift registers, sensors, memories, etc.

The SPI runs at a baud rate up to the bus clock divided by two in master mode and bus clock divided by four in slave mode.

All devices in the MC9S08DZ60 Series MCUs contain one SPI module, as shown in the following block diagram.

#### NOTE

Ensure that the SPI should not be disabled (SPE=0) at the same time as a bit change to the CPHA bit. These changes should be performed as separate operations or unexpected behavior may occur.

## 14.1.2 Features

Features of SCI module include:

- Full-duplex, standard non-return-to-zero (NRZ) format

- Double-buffered transmitter and receiver with separate enables

- Programmable baud rates (13-bit modulo divider)

- Interrupt-driven or polled operation:

- Transmit data register empty and transmission complete

- Receive data register full

- Receive overrun, parity error, framing error, and noise error

- Idle receiver detect

- Active edge on receive pin

- Break detect supporting LIN

- Hardware parity generation and checking

- Programmable 8-bit or 9-bit character length

- Receiver wakeup by idle-line or address-mark

- Optional 13-bit break character generation / 11-bit break character detection

- Selectable transmitter output polarity

### 14.1.3 Modes of Operation

See Section 14.3, "Functional Description," For details concerning SCI operation in these modes:

- 8- and 9-bit data modes

- Stop mode operation

- Loop mode

- Single-wire mode

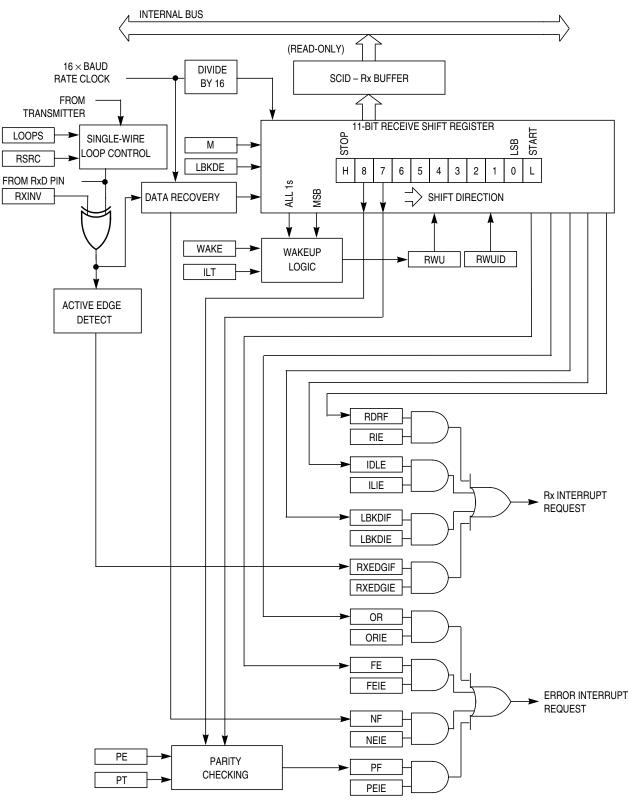

Figure 14-3 shows the receiver portion of the SCI.

Figure 14-3. SCI Receiver Block Diagram

MC9S08DZ60 Series Data Sheet, Rev. 4

| Field                   | Description                                                                                                                                                                                                                                      |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>TXINV <sup>1</sup> | <ul> <li>Transmit Data Inversion — Setting this bit reverses the polarity of the transmitted data output.</li> <li>0 Transmit data not inverted</li> <li>1 Transmit data inverted</li> </ul>                                                     |

| 3<br>ORIE               | <ul> <li>Overrun Interrupt Enable — This bit enables the overrun flag (OR) to generate hardware interrupt requests.</li> <li>0 OR interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when OR = 1.</li> </ul>             |

| 2<br>NEIE               | <ul> <li>Noise Error Interrupt Enable — This bit enables the noise flag (NF) to generate hardware interrupt requests.</li> <li>0 NF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when NF = 1.</li> </ul>           |

| 1<br>FEIE               | <ul> <li>Framing Error Interrupt Enable — This bit enables the framing error flag (FE) to generate hardware interrupt requests.</li> <li>0 FE interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when FE = 1.</li> </ul> |

| 0<br>PEIE               | <ul> <li>Parity Error Interrupt Enable — This bit enables the parity error flag (PF) to generate hardware interrupt requests.</li> <li>0 PF interrupts disabled (use polling).</li> <li>1 Hardware interrupt requested when PF = 1.</li> </ul>   |

#### Table 14-8. SCIxC3 Field Descriptions (continued)

Setting TXINV inverts the TxD output for all cases: data bits, start and stop bits, break, and idle.

## 14.2.7 SCI Data Register (SCIxD)

This register is actually two separate registers. Reads return the contents of the read-only receive data buffer and writes go to the write-only transmit data buffer. Reads and writes of this register are also involved in the automatic flag clearing mechanisms for the SCI status flags.

|       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------|----|----|----|----|----|----|----|----|

| R     | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 |

| W     | T7 | Т6 | T5 | T4 | Т3 | T2 | T1 | Т0 |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Figure 14-11. SCI Data Register (SCIxD)

## 14.3 Functional Description

The SCI allows full-duplex, asynchronous, NRZ serial communication among the MCU and remote devices, including other MCUs. The SCI comprises a baud rate generator, transmitter, and receiver block. The transmitter and receiver operate independently, although they use the same baud rate generator. During normal operation, the MCU monitors the status of the SCI, writes the data to be transmitted, and processes received data. The following describes each of the blocks of the SCI.

### 14.3.1 Baud Rate Generation

As shown in Figure 14-12, the clock source for the SCI baud rate generator is the bus-rate clock.

| Chapter 15 Real-Time Counter (S08RTCV1) |      |      |      |      |      |      |  |

|-----------------------------------------|------|------|------|------|------|------|--|

| Internal 1-kHz<br>Clock Source          |      |      |      |      |      |      |  |

| RTC Clock<br>(RTCPS = 0xA)              |      |      |      |      |      |      |  |

| RTCCNT                                  | 0x52 | 0x53 | 0x54 | 0x55 | 0x00 | 0x01 |  |

|                                         |      |      |      |      |      |      |  |

| RTIF                                    |      |      |      |      |      |      |  |

|                                         |      |      |      |      |      |      |  |

| RTCMOD                                  |      |      | 0x   | 55   |      |      |  |

Figure 15-6. RTC Counter Overflow Example

In the example of Figure 15-6, the selected clock source is the 1-kHz internal oscillator clock source. The prescaler (RTCPS) is set to 0xA or divide-by-4. The modulo value in the RTCMOD register is set to 0x55. When the counter, RTCCNT, reaches the modulo value of 0x55, the counter overflows to 0x00 and continues counting. The real-time interrupt flag, RTIF, sets when the counter value changes from 0x55 to 0x00. A real-time interrupt is generated when RTIF is set, if RTIE is set.

# 15.5 Initialization/Application Information

This section provides example code to give some basic direction to a user on how to initialize and configure the RTC module. The example software is implemented in C language.

The example below shows how to implement time of day with the RTC using the 1-kHz clock source to achieve the lowest possible power consumption. Because the 1-kHz clock source is not as accurate as a crystal, software can be added for any adjustments. For accuracy without adjustments at the expense of additional power consumption, the external clock (ERCLK) or the internal clock (IRCLK) can be selected with appropriate prescaler and modulo values.

#### Chapter 16 Timer/PWM Module (S08TPMV3)

The TPM channels are programmable independently as input capture, output compare, or edge-aligned PWM channels. Alternately, the TPM can be configured to produce CPWM outputs on all channels. When the TPM is configured for CPWMs, the counter operates as an up/down counter; input capture, output compare, and EPWM functions are not practical.

If a channel is configured as input capture, an internal pullup device may be enabled for that channel. The details of how a module interacts with pin controls depends upon the chip implementation because the I/O pins and associated general purpose I/O controls are not part of the module. Refer to the discussion of the I/O port logic in a full-chip specification.

Because center-aligned PWMs are usually used to drive 3-phase AC-induction motors and brushless DC motors, they are typically used in sets of three or six channels.

# 16.2 Signal Description

Table 16-1 shows the user-accessible signals for the TPM. The number of channels may be varied from one to eight. When an external clock is included, it can be shared with the same pin as any TPM channel; however, it could be connected to a separate input pin. Refer to the I/O pin descriptions in full-chip specification for the specific chip implementation.

| Name                 | Function                                                              |

|----------------------|-----------------------------------------------------------------------|

| EXTCLK <sup>1</sup>  | External clock source which may be selected to drive the TPM counter. |

| TPMxCHn <sup>2</sup> | I/O pin associated with TPM channel n                                 |

| Table | 16-1. | Signal  | <b>Properties</b> |

|-------|-------|---------|-------------------|

| labic | 10-11 | orginar | rioperties        |

<sup>1</sup> When preset, this signal can share any channel pin; however depending upon full-chip implementation, this signal could be connected to a separate external pin.

<sup>2</sup> n=channel number (1 to 8)

Refer to documentation for the full-chip for details about reset states, port connections, and whether there is any pullup device on these pins.

TPM channel pins can be associated with general purpose I/O pins and have passive pullup devices which can be enabled with a control bit when the TPM or general purpose I/O controls have configured the associated pin as an input. When no TPM function is enabled to use a corresponding pin, the pin reverts to being controlled by general purpose I/O controls, including the port-data and data-direction registers. Immediately after reset, no TPM functions are enabled, so all associated pins revert to general purpose I/O control.

## 16.2.1 Detailed Signal Descriptions

This section describes each user-accessible pin signal in detail. Although Table 16-1 grouped all channel pins together, any TPM pin can be shared with the external clock source signal. Since I/O pin logic is not part of the TPM, refer to full-chip documentation for a specific derivative for more details about the interaction of TPM pin functions and general purpose I/O controls including port data, data direction, and pullup controls.

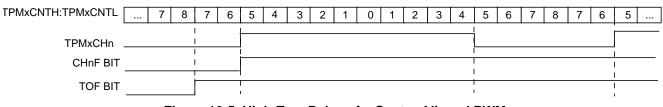

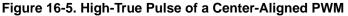

When the TPM is configured for center-aligned PWM (and ELSnB:ELSnA not = 0:0), the data direction for all channels in this TPM are overridden, the TPMxCHn pins are forced to be outputs controlled by the TPM, and the ELSnA bits control the polarity of each TPMxCHn output. If ELSnB:ELSnA=1:0, the corresponding TPMxCHn pin is cleared when the timer counter is counting up, and the channel value register matches the timer counter; the TPMxCHn pin is set when the timer counter is counting down, and the channel value register matches the timer counter. If ELSnA=1, the corresponding TPMxCHn pin is set when the timer counter; the TPMxCHn pin is cleared when the channel value register matches the timer counter is counting up and the channel value register matches the timer counter; the TPMxCHn pin is cleared when the timer counter is the timer counter; the timer counter is counting up and the channel value register matches the timer counter is counting the timer counter; the timer counter is counter is counter is counter; the timer counter is counter is counter is counter is counter.

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

TPMxMODH:TPMxMODL = 0x0008 TPMxCnVH:TPMxCnVL = 0x0005

Figure 16-6. Low-True Pulse of a Center-Aligned PWM

• Non-intrusive commands can be executed at any time even while the user's program is running. Non-intrusive commands allow a user to read or write MCU memory locations or access status and control registers within the background debug controller.

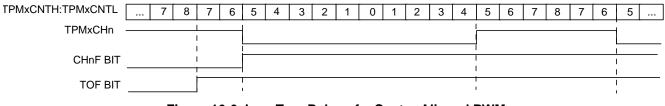

Typically, a relatively simple interface pod is used to translate commands from a host computer into commands for the custom serial interface to the single-wire background debug system. Depending on the development tool vendor, this interface pod may use a standard RS-232 serial port, a parallel printer port, or some other type of communications such as a universal serial bus (USB) to communicate between the host PC and the pod. The pod typically connects to the target system with ground, the BKGD pin, RESET, and sometimes  $V_{DD}$ . An open-drain connection to reset allows the host to force a target system reset, which is useful to regain control of a lost target system or to control startup of a target system before the on-chip nonvolatile memory has been programmed. Sometimes  $V_{DD}$  can be used to allow the pod to use power from the target system to avoid the need for a separate power supply. However, if the pod is powered separately, it can be connected to a running target system without forcing a target system reset or otherwise disturbing the running application program.

Figure 17-1. BDM Tool Connector

## 17.2.1 BKGD Pin Description

BKGD is the single-wire background debug interface pin. The primary function of this pin is for bidirectional serial communication of active background mode commands and data. During reset, this pin is used to select between starting in active background mode or starting the user's application program. This pin is also used to request a timed sync response pulse to allow a host development tool to determine the correct clock frequency for background debug serial communications.

BDC serial communications use a custom serial protocol first introduced on the M68HC12 Family of microcontrollers. This protocol assumes the host knows the communication clock rate that is determined by the target BDC clock rate. All communication is initiated and controlled by the host that drives a high-to-low edge to signal the beginning of each bit time. Commands and data are sent most significant bit first (MSB first). For a detailed description of the communications protocol, refer to Section 17.2.2, "Communication Details."

If a host is attempting to communicate with a target MCU that has an unknown BDC clock rate, a SYNC command may be sent to the target MCU to request a timed sync response signal from which the host can determine the correct communication speed.

BKGD is a pseudo-open-drain pin and there is an on-chip pullup so no external pullup resistor is required. Unlike typical open-drain pins, the external RC time constant on this pin, which is influenced by external capacitance, plays almost no role in signal rise time. The custom protocol provides for brief, actively driven speedup pulses to force rapid rise times on this pin without risking harmful drive level conflicts. Refer to Section 17.2.2, "Communication Details," for more detail.

**Chapter 17 Development Support**

# 17.2.3 BDC Commands

BDC commands are sent serially from a host computer to the BKGD pin of the target HCS08 MCU. All commands and data are sent MSB-first using a custom BDC communications protocol. Active background mode commands require that the target MCU is currently in the active background mode while non-intrusive commands may be issued at any time whether the target MCU is in active background mode or running a user application program.

Table 17-1 shows all HCS08 BDC commands, a shorthand description of their coding structure, and the meaning of each command.

### **Coding Structure Nomenclature**

This nomenclature is used in Table 17-1 to describe the coding structure of the BDC commands.

Commands begin with an 8-bit hexadecimal command code in the host-to-target direction (most significant bit first)

- / = separates parts of the command

- d = delay 16 target BDC clock cycles

- AAAA = a 16-bit address in the host-to-target direction

- RD = 8 bits of read data in the target-to-host direction

- WD = 8 bits of write data in the host-to-target direction

- RD16 = 16 bits of read data in the target-to-host direction

- WD16 = 16 bits of write data in the host-to-target direction

- SS = the contents of BDCSCR in the target-to-host direction (STATUS)

- CC = 8 bits of write data for BDCSCR in the host-to-target direction (CONTROL)

- RBKP = 16 bits of read data in the target-to-host direction (from BDCBKPT breakpoint register)

- WBKP = 16 bits of write data in the host-to-target direction (for BDCBKPT breakpoint register)

## 17.3.6 Hardware Breakpoints

The BRKEN control bit in the DBGC register may be set to 1 to allow any of the trigger conditions described in Section 17.3.5, "Trigger Modes," to be used to generate a hardware breakpoint request to the CPU. TAG in DBGC controls whether the breakpoint request will be treated as a tag-type breakpoint or a force-type breakpoint. A tag breakpoint causes the current opcode to be marked as it enters the instruction queue. If a tagged opcode reaches the end of the pipe, the CPU executes a BGND instruction to go to active background mode rather than executing the tagged opcode. A force-type breakpoint causes the CPU to finish the current instruction and then go to active background mode.

If the background mode has not been enabled (ENBDM = 1) by a serial WRITE\_CONTROL command through the BKGD pin, the CPU will execute an SWI instruction instead of going to active background mode.

# 17.4 Register Definition

This section contains the descriptions of the BDC and DBG registers and control bits.

Refer to the high-page register summary in the device overview chapter of this data sheet for the absolute address assignments for all DBG registers. This section refers to registers and control bits only by their names. A Freescale-provided equate or header file is used to translate these names into the appropriate absolute addresses.

# 17.4.1 BDC Registers and Control Bits

The BDC has two registers:

- The BDC status and control register (BDCSCR) is an 8-bit register containing control and status bits for the background debug controller.

- The BDC breakpoint match register (BDCBKPT) holds a 16-bit breakpoint match address.

These registers are accessed with dedicated serial BDC commands and are not located in the memory space of the target MCU (so they do not have addresses and cannot be accessed by user programs).

Some of the bits in the BDCSCR have write limitations; otherwise, these registers may be read or written at any time. For example, the ENBDM control bit may not be written while the MCU is in active background mode. (This prevents the ambiguous condition of the control bit forbidding active background mode while the MCU is already in active background mode.) Also, the four status bits (BDMACT, WS, WSF, and DVF) are read-only status indicators and can never be written by the WRITE\_CONTROL serial BDC command. The clock switch (CLKSW) control bit may be read or written at any time.

Chapter 17 Development Support

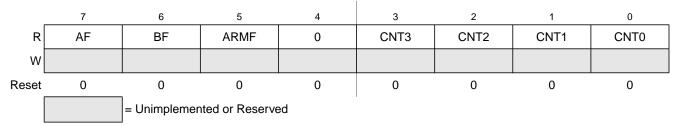

# 17.4.3.9 Debug Status Register (DBGS)

This is a read-only status register.

#### Figure 17-9. Debug Status Register (DBGS)

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>AF         | <ul> <li>Trigger Match A Flag — AF is cleared at the start of a debug run and indicates whether a trigger match A condition was met since arming.</li> <li>0 Comparator A has not matched</li> <li>1 Comparator A match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6<br>BF         | <ul> <li>Trigger Match B Flag — BF is cleared at the start of a debug run and indicates whether a trigger match B condition was met since arming.</li> <li>0 Comparator B has not matched</li> <li>1 Comparator B match</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5<br>ARMF       | Arm Flag — While DBGEN = 1, this status bit is a read-only image of ARM in DBGC. This bit is set by writing 1 to the ARM control bit in DBGC (while DBGEN = 1) and is automatically cleared at the end of a debug run. A debug run is completed when the FIFO is full (begin trace) or when a trigger event is detected (end trace). A debug run can also be ended manually by writing 0 to ARM or DBGEN in DBGC.<br>0 Debugger not armed<br>1 Debugger armed                                                                                                                                                                                                                                                             |

| 3:0<br>CNT[3:0] | FIFO Valid Count — These bits are cleared at the start of a debug run and indicate the number of words of valid data in the FIFO at the end of a debug run. The value in CNT does not decrement as data is read out of the FIFO. The external debug host is responsible for keeping track of the count as information is read out of the FIFO. 0000 Number of valid words in FIFO = No valid data 0001 Number of valid words in FIFO = 1 0010 Number of valid words in FIFO = 2 0011 Number of valid words in FIFO = 3 0100 Number of valid words in FIFO = 4 0101 Number of valid words in FIFO = 5 0110 Number of valid words in FIFO = 6 0111 Number of valid words in FIFO = 7 1000 Number of valid words in FIFO = 8 |

# Appendix B Timer Pulse-Width Modulator (TPMV2)

#### NOTE

This chapter refers to S08TPM version 2, which applies to the 3M05C and older mask sets of this device. )M74K and newer mask set devices use S08TPM version 3. If your device uses mask 0M74K or newer, please refer to Chapter 16, "Timer Pulse-Width Modulator (S08TPMV3) for information pertaining to that module.

The TPM uses one input/output (I/O) pin per channel, TPMxCHn where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–4). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

### B.0.1 Features

The TPM has the following features:

- Each TPM may be configured for buffered, center-aligned pulse-width modulation (CPWM) on all channels

- Clock sources independently selectable per TPM (multiple TPMs device)

- Selectable clock sources (device dependent): bus clock, fixed system clock, external pin

- Clock prescaler taps for divide by 1, 2, 4, 8, 16, 32, 64, or 128

- 16-bit free-running or up/down (CPWM) count operation

- 16-bit modulus register to control counter range

- Timer system enable

- One interrupt per channel plus a terminal count interrupt for each TPM module (multiple TPMs device)

- Channel features:

- Each channel may be input capture, output compare, or buffered edge-aligned PWM

- Rising-edge, falling-edge, or any-edge input capture trigger

- Set, clear, or toggle output compare action

- Selectable polarity on PWM outputs

## B.0.2 Block Diagram

Figure B-1 shows the structure of a TPM. Some MCUs include more than one TPM, with various numbers of channels.

MC9S08DZ60 Series Data Sheet, Rev. 4