#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

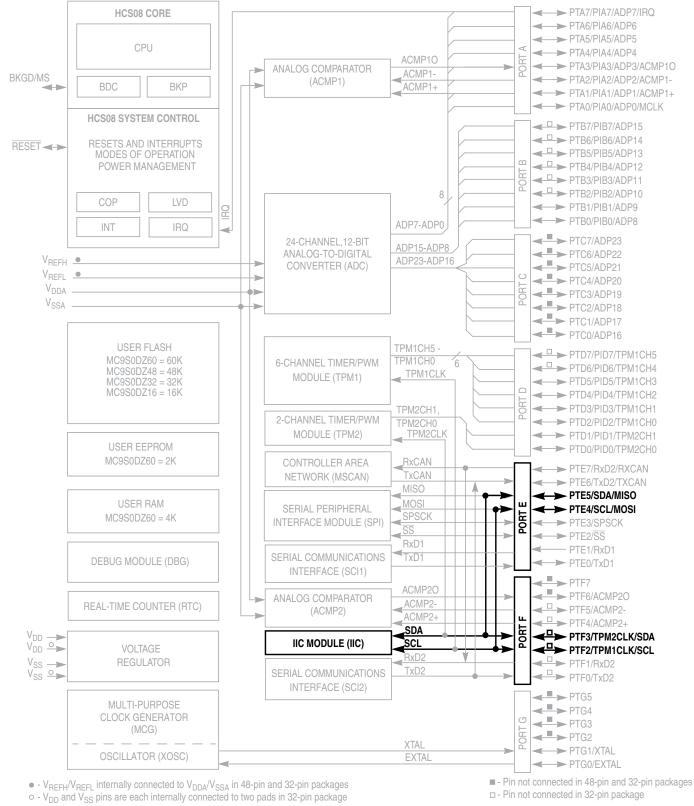

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | S08                                                          |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 40MHz                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                   |

| Peripherals                | LVD, POR, PWM, WDT                                           |

| Number of I/O              | 53                                                           |

| Program Memory Size        | 60KB (60K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | 2K x 8                                                       |

| RAM Size                   | 4K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 24x12b                                                   |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 64-LQFP                                                      |

| Supplier Device Package    | 64-LQFP (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=s9s08dz60f2mlhr |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Section Number**

Title

### Page

| 17.4 | Register Definition                                         |  |

|------|-------------------------------------------------------------|--|

|      | 17.4.1 BDC Registers and Control Bits                       |  |

|      | 17.4.2 System Background Debug Force Reset Register (SBDFR) |  |

|      | 17.4.3 DBG Registers and Control Bits                       |  |

### Appendix A Electrical Characteristics

| A.1  | Introduction                               |     |

|------|--------------------------------------------|-----|

| A.2  | Parameter Classification                   | 369 |

| A.3  | Absolute Maximum Ratings                   | 369 |

| A.4  | Thermal Characteristics                    | 370 |

| A.5  | ESD Protection and Latch-Up Immunity       | 372 |

| A.6  | DC Characteristics                         | 373 |

| A.7  | Supply Current Characteristics             | 375 |

| A.8  | Analog Comparator (ACMP) Electricals       | 376 |

| A.9  | ADC Characteristics                        | 376 |

| A.10 | External Oscillator (XOSC) Characteristics | 380 |

| A.11 | MCG Specifications                         | 381 |

|      | AC Characteristics                         |     |

|      | A.12.1 Control Timing                      | 383 |

|      | A.12.2 Timer/PWM                           |     |

|      | A.12.3 MSCAN                               | 385 |

|      | A.12.4 SPI                                 | 386 |

| A.13 | Flash and EEPROM                           |     |

| A.14 | EMC Performance                            |     |

|      | A.14.1 Radiated Emissions                  |     |

### Appendix B Timer Pulse-Width Modulator (TPMV2)

|             | <b>B.0.1</b>  | Features                                               | 391 |

|-------------|---------------|--------------------------------------------------------|-----|

|             | B.0.2         | Block Diagram                                          | 391 |

| <b>B</b> .1 | Externa       | l Signal Description                                   | 393 |

|             | <b>B</b> .1.1 | External TPM Clock Sources                             | 393 |

|             | B.1.2         | TPMxCHn — TPMx Channel n I/O Pins                      | 393 |

| B.2         | Register      | r Definition                                           | 393 |

|             | B.2.1         | Timer Status and Control Register (TPMxSC)             | 394 |

|             | B.2.2         | Timer Counter Registers (TPMxCNTH:TPMxCNTL)            | 395 |

|             | B.2.3         | Timer Counter Modulo Registers (TPMxMODH:TPMxMODL)     | 396 |

|             | <b>B.2.4</b>  | Timer Channel n Status and Control Register (TPMxCnSC) | 397 |

|             | B.2.5         | Timer Channel Value Registers (TPMxCnVH:TPMxCnVL)      | 398 |

| <b>B.3</b>  | Function      | nal Description                                        | 399 |

|             | <b>B</b> .3.1 | Counter                                                | 399 |

|             |               |                                                        |     |

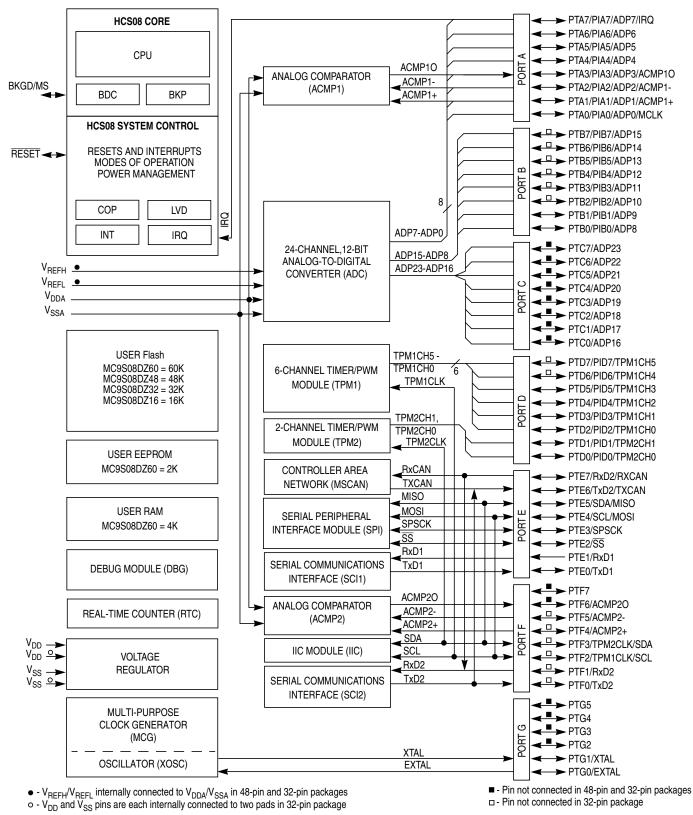

**Chapter 1 Device Overview**

MC9S08DZ60 Series Data Sheet, Rev. 4

# Chapter 2 Pins and Connections

This section describes signals that connect to package pins. It includes pinout diagrams, recommended system connections, and detailed discussions of signals.

# 2.1 Device Pin Assignment

This section shows the pin assignments for MC9S08DZ60 Series MCUs in the available packages.

Figure 2-1. 64-Pin LQFP

MC9S08DZ60 Series Data Sheet, Rev. 4

# Chapter 4 Memory

# 4.1 MC9S08DZ60 Series Memory Map

On-chip memory in the MC9S08DZ60 Series consists of RAM, EEPROM, and Flash program memory for nonvolatile data storage, and I/O and control/status registers. The registers are divided into three groups:

- Direct-page registers (0x0000 through 0x007F)

- High-page registers (0x1800 through 0x18FF)

- Nonvolatile registers (0xFFB0 through 0xFFBF)

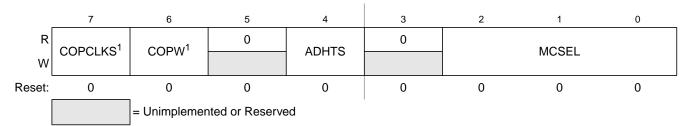

### 5.8.5 System Options Register 2 (SOPT2)

This high page register contains bits to configure MCU specific features on the MC9S08DZ60 Series devices.

#### Figure 5-6. System Options Register 2 (SOPT2)

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

| Field        | Description                                                                                                                                                                                                                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>COPCLKS | <ul> <li>COP Watchdog Clock Select — This write-once bit selects the clock source of the COP watchdog. See Table 5-6 for details.</li> <li>0 Internal 1-kHz clock is source to COP.</li> <li>1 Bus clock is source to COP.</li> </ul>                                                                                                                              |

| 6<br>COPW    | <ul> <li>COP Window — This write-once bit selects the COP operation mode. When set, the 0x55-0xAA write sequence to the SRS register must occur in the last 25% of the selected period. Any write to the SRS register during the first 75% of the selected period will reset the MCU.</li> <li>0 Normal COP operation.</li> <li>1 Window COP operation.</li> </ul> |

| 4<br>ADHTS   | <ul> <li>ADC Hardware Trigger Select — This bit selects which hardware trigger initiates conversion for the analog to digital converter when the ADC hardware trigger is enabled (ADCTRG is set in ADCSC2 register).</li> <li>0 Real Time Counter (RTC) overflow.</li> <li>1 External Interrupt Request (IRQ) pin.</li> </ul>                                      |

| 2:0<br>MCSEL | MCLK Divide Select— These bits enable the MCLK output on PTA0 pin and select the divide ratio for the MCLK output according to the formula below when the MCSEL bits are not equal to all zeroes. In case that the MCSEL bits are all zeroes, the MCLK output is disabled.<br>MCLK frequency = Bus Clock frequency ÷ (2 * MCSEL)                                   |

#### Table 5-7. SOPT2 Register Field Descriptions

### 7.3.6.7 SP-Relative, 16-Bit Offset (SP2)

This variation of indexed addressing uses the 16-bit value in the stack pointer (SP) plus a 16-bit offset included in the instruction as the address of the operand needed to complete the instruction.

# 7.4 Special Operations

The CPU performs a few special operations that are similar to instructions but do not have opcodes like other CPU instructions. In addition, a few instructions such as STOP and WAIT directly affect other MCU circuitry. This section provides additional information about these operations.

### 7.4.1 Reset Sequence

Reset can be caused by a power-on-reset (POR) event, internal conditions such as the COP (computer operating properly) watchdog, or by assertion of an external active-low reset pin. When a reset event occurs, the CPU immediately stops whatever it is doing (the MCU does not wait for an instruction boundary before responding to a reset event). For a more detailed discussion about how the MCU recognizes resets and determines the source, refer to the Resets, Interrupts, and System Configuration chapter.

The reset event is considered concluded when the sequence to determine whether the reset came from an internal source is done and when the reset pin is no longer asserted. At the conclusion of a reset event, the CPU performs a 6-cycle sequence to fetch the reset vector from 0xFFFE and 0xFFFF and to fill the instruction queue in preparation for execution of the first program instruction.

### 7.4.2 Interrupt Sequence

When an interrupt is requested, the CPU completes the current instruction before responding to the interrupt. At this point, the program counter is pointing at the start of the next instruction, which is where the CPU should return after servicing the interrupt. The CPU responds to an interrupt by performing the same sequence of operations as for a software interrupt (SWI) instruction, except the address used for the vector fetch is determined by the highest priority interrupt that is pending when the interrupt sequence started.

The CPU sequence for an interrupt is:

- 1. Store the contents of PCL, PCH, X, A, and CCR on the stack, in that order.

- 2. Set the I bit in the CCR.

- 3. Fetch the high-order half of the interrupt vector.

- 4. Fetch the low-order half of the interrupt vector.

- 5. Delay for one free bus cycle.

- 6. Fetch three bytes of program information starting at the address indicated by the interrupt vector to fill the instruction queue in preparation for execution of the first instruction in the interrupt service routine.

After the CCR contents are pushed onto the stack, the I bit in the CCR is set to prevent other interrupts while in the interrupt service routine. Although it is possible to clear the I bit with an instruction in the

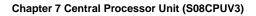

Chapter 8 Multi-Purpose Clock Generator (S08MCGV1)

Figure 8-13. Trim Procedure

In this particular case, the MCU has been attached to a PCB and the entire assembly is undergoing final test with automated test equipment. A separate signal or message is provided to the MCU operating under user provided software control. The MCU initiates a trim procedure as outlined in Figure 8-13 while the tester supplies a precision reference signal.

If the intended bus frequency is near the maximum allowed for the device, it is recommended to trim using a reference divider value (RDIV setting) of twice the final value. After the trim procedure is complete, the reference divider can be restored. This will prevent accidental overshoot of the maximum clock frequency.

## 10.3.2 Status and Control Register 2 (ADCSC2)

The ADCSC2 register controls the compare function, conversion trigger, and conversion active of the ADC module.

Figure 10-4. Status and Control Register 2 (ADCSC2)

#### Table 10-5. ADCSC2 Register Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ADACT | Conversion Active. Indicates that a conversion is in progress. ADACT is set when a conversion is initiated and cleared when a conversion is completed or aborted.<br>0 Conversion not in progress<br>1 Conversion in progress                                                                                                                                                                                                                                                 |

| 6<br>ADTRG | Conversion Trigger Select. Selects the type of trigger used for initiating a conversion. Two types of triggers are selectable: software trigger and hardware trigger. When software trigger is selected, a conversion is initiated following a write to ADCSC1. When hardware trigger is selected, a conversion is initiated following the assertion of the ADHWT input.<br>0 Software trigger selected<br>1 Hardware trigger selected                                        |

| 5<br>ACFE  | Compare Function Enable. Enables the compare function.<br>0 Compare function disabled<br>1 Compare function enabled                                                                                                                                                                                                                                                                                                                                                           |

| 4<br>ACFGT | Compare Function Greater Than Enable. Configures the compare function to trigger when the result of the conversion of the input being monitored is greater than or equal to the compare value. The compare function defaults to triggering when the result of the compare of the input being monitored is less than the compare value.<br>0 Compare triggers when input is less than compare value<br>1 Compare triggers when input is greater than or equal to compare value |

### 10.3.3 Data Result High Register (ADCRH)

In 12-bit operation, ADCRH contains the upper four bits of the result of a 12-bit conversion. In 10-bit mode, ADCRH contains the upper two bits of the result of a 10-bit conversion. When configured for 10-bit mode, ADR[11:10] are cleared. When configured for 8-bit mode, ADR[11:8] are cleared.

In 12-bit and 10-bit mode, ADCRH is updated each time a conversion completes except when automatic compare is enabled and the compare condition is not met. When a compare event does occur, the value is the addition of the conversion result and the two's complement of the compare value. In 12-bit and 10-bit mode, reading ADCRH prevents the ADC from transferring subsequent conversion results into the result registers until ADCRL is read. If ADCRL is not read until after the next conversion is completed, the intermediate conversion result is lost. In 8-bit mode, there is no interlocking with ADCRL.

#### Chapter 10 Analog-to-Digital Converter (S08ADC12V1)

When a conversion is aborted, the contents of the data registers, ADCRH and ADCRL, are not altered. However, they continue to be the values transferred after the completion of the last successful conversion. If the conversion was aborted by a reset, ADCRH and ADCRL return to their reset states.

### 10.4.4.4 Power Control

The ADC module remains in its idle state until a conversion is initiated. If ADACK is selected as the conversion clock source, the ADACK clock generator is also enabled.

Power consumption when active can be reduced by setting ADLPC. This results in a lower maximum value for  $f_{ADCK}$  (see the electrical specifications).

### 10.4.4.5 Sample Time and Total Conversion Time

The total conversion time depends on the sample time (as determined by ADLSMP), the MCU bus frequency, the conversion mode (8-bit, 10-bit or 12-bit), and the frequency of the conversion clock ( $f_{ADCK}$ ). After the module becomes active, sampling of the input begins. ADLSMP selects between short (3.5 ADCK cycles) and long (23.5 ADCK cycles) sample times. When sampling is complete, the converter is isolated from the input channel and a successive approximation algorithm is performed to determine the digital value of the analog signal. The result of the conversion is transferred to ADCRH and ADCRL upon completion of the conversion algorithm.

If the bus frequency is less than the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when short sample is enabled (ADLSMP=0). If the bus frequency is less than 1/11th of the  $f_{ADCK}$  frequency, precise sample time for continuous conversions cannot be guaranteed when long sample is enabled (ADLSMP=1).

The maximum total conversion time for different conditions is summarized in Table 10-13.

| Conversion Type                                                          | ADICLK | ADLSMP | Max Total Conversion Time           |

|--------------------------------------------------------------------------|--------|--------|-------------------------------------|

| Single or first continuous 8-bit                                         | 0x, 10 | 0      | 20 ADCK cycles + 5 bus clock cycles |

| Single or first continuous 10-bit or 12-bit                              | 0x, 10 | 0      | 23 ADCK cycles + 5 bus clock cycles |

| Single or first continuous 8-bit                                         | 0x, 10 | 1      | 40 ADCK cycles + 5 bus clock cycles |

| Single or first continuous 10-bit or 12-bit                              | 0x, 10 | 1      | 43 ADCK cycles + 5 bus clock cycles |

| Single or first continuous 8-bit                                         | 11     | 0      | 5 μs + 20 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit or 12-bit                              | 11     | 0      | 5 μs + 23 ADCK + 5 bus clock cycles |

| Single or first continuous 8-bit                                         | 11     | 1      | 5 μs + 40 ADCK + 5 bus clock cycles |

| Single or first continuous 10-bit or 12-bit                              | 11     | 1      | 5 μs + 43 ADCK + 5 bus clock cycles |

| Subsequent continuous 8-bit;<br>$f_{BUS} \ge f_{ADCK}$                   | XX     | 0      | 17 ADCK cycles                      |

| Subsequent continuous 10-bit or 12-bit; $f_{BUS} \geq f_{ADCK}$          | XX     | 0      | 20 ADCK cycles                      |

| Subsequent continuous 8-bit;<br>f <sub>BUS</sub> ≥ f <sub>ADCK</sub> /11 | xx     | 1      | 37 ADCK cycles                      |

Chapter 11 Inter-Integrated Circuit (S08IICV2)

MC9S08DZ60 Series Data Sheet, Rev. 4

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SDA Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 00           | 20             | 7                 | 6                            | 11                          |

| 01           | 22             | 7                 | 7                            | 12                          |

| 02           | 24             | 8                 | 8                            | 13                          |

| 03           | 26             | 8                 | 9                            | 14                          |

| 04           | 28             | 9                 | 10                           | 15                          |

| 05           | 30             | 9                 | 11                           | 16                          |

| 06           | 34             | 10                | 13                           | 18                          |

| 07           | 40             | 10                | 16                           | 21                          |

| 08           | 28             | 7                 | 10                           | 15                          |

| 09           | 32             | 7                 | 12                           | 17                          |

| 0A           | 36             | 9                 | 14                           | 19                          |

| 0B           | 40             | 9                 | 16                           | 21                          |

| 0C           | 44             | 11                | 18                           | 23                          |

| 0D           | 48             | 11                | 20                           | 25                          |

| 0E           | 56             | 13                | 24                           | 29                          |

| 0F           | 68             | 13                | 30                           | 35                          |

| 10           | 48             | 9                 | 18                           | 25                          |

| 11           | 56             | 9                 | 22                           | 29                          |

| 12           | 64             | 13                | 26                           | 33                          |

| 13           | 72             | 13                | 30                           | 37                          |

| 14           | 80             | 17                | 34                           | 41                          |

| 15           | 88             | 17                | 38                           | 45                          |

| 16           | 104            | 21                | 46                           | 53                          |

| 17           | 128            | 21                | 58                           | 65                          |

| 18           | 80             | 9                 | 38                           | 41                          |

| 19           | 96             | 9                 | 46                           | 49                          |

| 1A           | 112            | 17                | 54                           | 57                          |

| 1B           | 128            | 17                | 62                           | 65                          |

| 1C           | 144            | 25                | 70                           | 73                          |

| 1D           | 160            | 25                | 78                           | 81                          |

| 1E           | 192            | 33                | 94                           | 97                          |

| 1F           | 240            | 33                | 118                          | 121                         |

| ICR<br>(hex) | SCL<br>Divider | SDA Hold<br>Value | SCL Hold<br>(Start)<br>Value | SCL Hold<br>(Stop)<br>Value |

|--------------|----------------|-------------------|------------------------------|-----------------------------|

| 20           | 160            | 17                | 78                           | 81                          |

| 21           | 192            | 17                | 94                           | 97                          |

| 22           | 224            | 33                | 110                          | 113                         |

| 23           | 256            | 33                | 126                          | 129                         |

| 24           | 288            | 49                | 142                          | 145                         |

| 25           | 320            | 49                | 158                          | 161                         |

| 26           | 384            | 65                | 190                          | 193                         |

| 27           | 480            | 65                | 238                          | 241                         |

| 28           | 320            | 33                | 158                          | 161                         |

| 29           | 384            | 33                | 190                          | 193                         |

| 2A           | 448            | 65                | 222                          | 225                         |

| 2B           | 512            | 65                | 254                          | 257                         |

| 2C           | 576            | 97                | 286                          | 289                         |

| 2D           | 640            | 97                | 318                          | 321                         |

| 2E           | 768            | 129               | 382                          | 385                         |

| 2F           | 960            | 129               | 478                          | 481                         |

| 30           | 640            | 65                | 318                          | 321                         |

| 31           | 768            | 65                | 382                          | 385                         |

| 32           | 896            | 129               | 446                          | 449                         |

| 33           | 1024           | 129               | 510                          | 513                         |

| 34           | 1152           | 193               | 574                          | 577                         |

| 35           | 1280           | 193               | 638                          | 641                         |

| 36           | 1536           | 257               | 766                          | 769                         |

| 37           | 1920           | 257               | 958                          | 961                         |

| 38           | 1280           | 129               | 638                          | 641                         |

| 39           | 1536           | 129               | 766                          | 769                         |

| 3A           | 1792           | 257               | 894                          | 897                         |

| 3B           | 2048           | 257               | 1022                         | 1025                        |

| 3C           | 2304           | 385               | 1150                         | 1153                        |

| 3D           | 2560           | 385               | 1278                         | 1281                        |

| 3E           | 3072           | 513               | 1534                         | 1537                        |

| 3F           | 3840           | 513               | 1918                         | 1921                        |

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AM[7:0] | Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.<br>0 Match corresponding acceptance code register and identifier bits<br>1 Ignore corresponding acceptance code register bit (don't care) |

#### Table 12-22. CANIDMR0–CANIDMR3 Register Field Descriptions

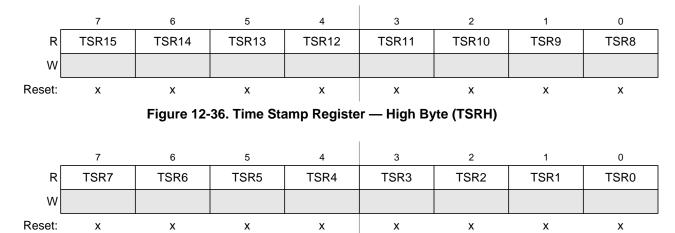

| _      | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | AM7 | AM6 | AM5 | AM4 | AM3 | AM2 | AM1 | AM0 |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Figure 12-22. MSCAN Identifier Mask Registers (Second Bank) — CANIDMR4–CANIDMR7

Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

#### Table 12-23. CANIDMR4–CANIDMR7 Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>AM[7:0] | <ul> <li>Acceptance Mask Bits — If a particular bit in this register is cleared, this indicates that the corresponding bit in the identifier acceptance register must be the same as its identifier bit before a match is detected. The message is accepted if all such bits match. If a bit is set, it indicates that the state of the corresponding bit in the identifier acceptance register does not affect whether or not the message is accepted.</li> <li>Match corresponding acceptance code register and identifier bits</li> <li>Ignore corresponding acceptance code register bit (don't care)</li> </ul> |

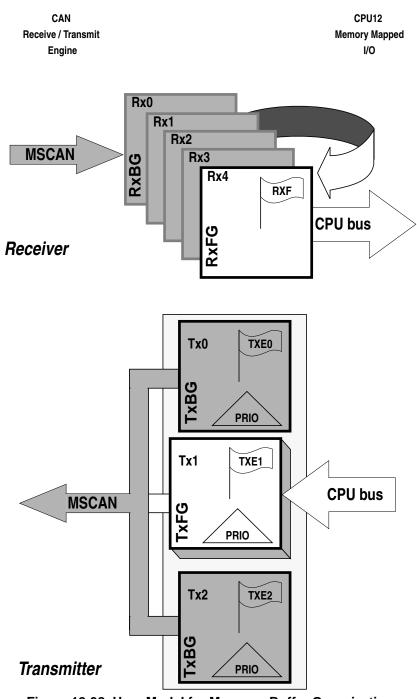

### 12.4 Programmer's Model of Message Storage

The following section details the organization of the receive and transmit message buffers and the associated control registers.

To simplify the programmer interface, the receive and transmit message buffers have the same outline. Each message buffer allocates 16 bytes in the memory map containing a 13 byte data structure.

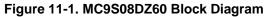

An additional transmit buffer priority register (TBPR) is defined for the transmit buffers. Within the last two bytes of this memory map, the MSCAN stores a special 16-bit time stamp, which is sampled from an internal timer after successful transmission or reception of a message. This feature is only available for transmit and receiver buffers if the TIME bit is set (see Section 12.3.1, "MSCAN Control Register 0 (CANCTL0)").

The time stamp register is written by the MSCAN. The CPU can only read these registers.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

Section 12.3.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

Figure 12-37. Time Stamp Register — Low Byte (TSRL)

Read: Anytime when TXEx flag is set (see Section 12.3.6, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 12.3.10, "MSCAN Transmit Buffer Selection Register (CANTBSEL)").

Write: Unimplemented

# 12.5 Functional Description

### 12.5.1 General

This section provides a complete functional description of the MSCAN. It describes each of the features and modes listed in the introduction.

Chapter 12 Freescale's Controller Area Network (S08MSCANV1)

# 12.5.2 Message Storage

Figure 12-38. User Model for Message Buffer Organization

MSCAN facilitates a sophisticated message storage system which addresses the requirements of a broad range of network applications.

### 12.5.3.2 Protocol Violation Protection

The MSCAN protects the user from accidentally violating the CAN protocol through programming errors. The protection logic implements the following features:

- The receive and transmit error counters cannot be written or otherwise manipulated.

- All registers which control the configuration of the MSCAN cannot be modified while the MSCAN is on-line. The MSCAN has to be in Initialization Mode. The corresponding INITRQ/INITAK handshake bits in the CANCTL0/CANCTL1 registers (see Section 12.3.1, "MSCAN Control Register 0 (CANCTL0)") serve as a lock to protect the following registers:

- MSCAN control 1 register (CANCTL1)

- MSCAN bus timing registers 0 and 1 (CANBTR0, CANBTR1)

- MSCAN identifier acceptance control register (CANIDAC)

- MSCAN identifier acceptance registers (CANIDAR0–CANIDAR7)

- MSCAN identifier mask registers (CANIDMR0–CANIDMR7)

- The TXCAN pin is immediately forced to a recessive state when the MSCAN goes into the power down mode or initialization mode (see Section 12.5.5.6, "MSCAN Power Down Mode," and Section 12.5.5.5, "MSCAN Initialization Mode").

- The MSCAN enable bit (CANE) is writable only once in normal system operation modes, which provides further protection against inadvertently disabling the MSCAN.

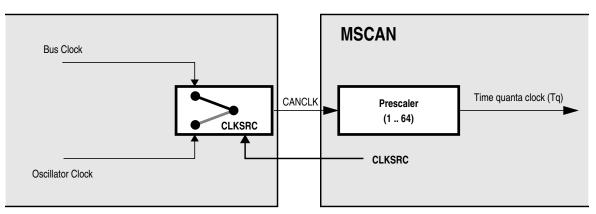

### 12.5.3.3 Clock System

Figure 12-42 shows the structure of the MSCAN clock generation circuitry.

Figure 12-42. MSCAN Clocking Scheme

The clock source bit (CLKSRC) in the CANCTL1 register (12.3.2/-226) defines whether the internal CANCLK is connected to the output of a crystal oscillator (oscillator clock) or to the bus clock.

The clock source has to be chosen such that the tight oscillator tolerance requirements (up to 0.4%) of the CAN protocol are met. Additionally, for high CAN bus rates (1 Mbps), a 45% to 55% duty cycle of the clock is required.

# Chapter 16 Timer Pulse-Width Modulator (S08TPMV3)

#### NOTE

This chapter refers to S08TPM version 3, which applies to the 0M74K and newer mask sets of this device. 3M05C and older mask set devices use S08TPM version 2. If your device uses mask 3M05C or older, please refer to Appendix B, "Timer Pulse-Width Modulator (TPMV2) on page 391 for information pertaining to that module.

### 16.1 Introduction

The TPM is a one-to-eight-channel timer system which supports traditional input capture, output compare, or edge-aligned PWM on each channel. A control bit allows the TPM to be configured such that all channels may be used for center-aligned PWM functions. Timing functions are based on a 16-bit counter with prescaler and modulo features to control frequency and range (period between overflows) of the time reference. This timing system is ideally suited for a wide range of control applications, and the center-aligned PWM capability extends the field of application to motor control in small appliances.

The TPM uses one input/output (I/O) pin per channel, TPMxCHn, where x is the TPM number (for example, 1 or 2) and n is the channel number (for example, 0–5). The TPM shares its I/O pins with general-purpose I/O port pins (refer to the Pins and Connections chapter for more information).

MC9S08DZ60 Series MCUs have two TPM modules. In all packages, TPM2 is 2-channel. The number of channels available on external pins in TPM1 depends on the package:

- Six channels in 64-pin and 48-pin packages

- Four channels in 32-pin packages.

The following sections describe the main counter and each of the timer operating modes (input capture, output compare, edge-aligned PWM, and center-aligned PWM). Because details of pin operation and interrupt activity depend upon the operating mode, these topics will be covered in the associated mode explanation sections.

## 16.4.1 Counter

All timer functions are based on the main 16-bit counter (TPMxCNTH:TPMxCNTL). This section discusses selection of the clock source, end-of-count overflow, up-counting vs. up/down counting, and manual counter reset.

### 16.4.1.1 Counter Clock Source

The 2-bit field, CLKSB:CLKSA, in the timer status and control register (TPMxSC) selects one of three possible clock sources or OFF (which effectively disables the TPM). See Table 16-3. After any MCU reset, CLKSB:CLKSA=0:0 so no clock source is selected, and the TPM is in a very low power state. These control bits may be read or written at any time and disabling the timer (writing 00 to the CLKSB:CLKSA field) does not affect the values in the counter or other timer registers.

| Command<br>Mnemonic | Active BDM/<br>Non-intrusive | Coding<br>Structure | Description                                                                              |

|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------|

| SYNC                | Non-intrusive                | n/a <sup>1</sup>    | Request a timed reference pulse to determine target BDC communication speed              |

| ACK_ENABLE          | Non-intrusive                | D5/d                | Enable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.       |

| ACK_DISABLE         | Non-intrusive                | D6/d                | Disable acknowledge protocol. Refer to<br>Freescale document order no. HCS08RMv1/D.      |

| BACKGROUND          | Non-intrusive                | 90/d                | Enter active background mode if enabled (ignore if ENBDM bit equals 0)                   |

| READ_STATUS         | Non-intrusive                | E4/SS               | Read BDC status from BDCSCR                                                              |

| WRITE_CONTROL       | Non-intrusive                | C4/CC               | Write BDC controls in BDCSCR                                                             |

| READ_BYTE           | Non-intrusive                | E0/AAAA/d/RD        | Read a byte from target memory                                                           |

| READ_BYTE_WS        | Non-intrusive                | E1/AAAA/d/SS/RD     | Read a byte and report status                                                            |

| READ_LAST           | Non-intrusive                | E8/SS/RD            | Re-read byte from address just read and report status                                    |

| WRITE_BYTE          | Non-intrusive                | C0/AAAA/WD/d        | Write a byte to target memory                                                            |

| WRITE_BYTE_WS       | Non-intrusive                | C1/AAAA/WD/d/SS     | Write a byte and report status                                                           |

| READ_BKPT           | Non-intrusive                | E2/RBKP             | Read BDCBKPT breakpoint register                                                         |

| WRITE_BKPT          | Non-intrusive                | C2/WBKP             | Write BDCBKPT breakpoint register                                                        |

| GO                  | Active BDM                   | 08/d                | Go to execute the user application program starting at the address currently in the PC   |

| TRACE1              | Active BDM                   | 10/d                | Trace 1 user instruction at the address in the PC, then return to active background mode |

| TAGGO               | Active BDM                   | 18/d                | Same as GO but enable external tagging<br>(HCS08 devices have no external tagging pin)   |

| READ_A              | Active BDM                   | 68/d/RD             | Read accumulator (A)                                                                     |

| READ_CCR            | Active BDM                   | 69/d/RD             | Read condition code register (CCR)                                                       |

| READ_PC             | Active BDM                   | 6B/d/RD16           | Read program counter (PC)                                                                |

| READ_HX             | Active BDM                   | 6C/d/RD16           | Read H and X register pair (H:X)                                                         |

| READ_SP             | Active BDM                   | 6F/d/RD16           | Read stack pointer (SP)                                                                  |

| READ_NEXT           | Active BDM                   | 70/d/RD             | Increment H:X by one then read memory byte located at H:X                                |

| READ_NEXT_WS        | Active BDM                   | 71/d/SS/RD          | Increment H:X by one then read memory byte located at H:X. Report status and data.       |

| WRITE_A             | Active BDM                   | 48/WD/d             | Write accumulator (A)                                                                    |

| WRITE_CCR           | Active BDM                   | 49/WD/d             | Write condition code register (CCR)                                                      |

| WRITE_PC            | Active BDM                   | 4B/WD16/d           | Write program counter (PC)                                                               |

| WRITE_HX            | Active BDM                   | 4C/WD16/d           | Write H and X register pair (H:X)                                                        |

| WRITE_SP            | Active BDM                   | 4F/WD16/d           | Write stack pointer (SP)                                                                 |

| WRITE_NEXT          | Active BDM                   | 50/WD/d             | Increment H:X by one, then write memory byte located at H:X                              |

| WRITE_NEXT_WS       | Active BDM                   | 51/WD/d/SS          | Increment H:X by one, then write memory byte located at H:X. Also report status.         |

| Table 17-1. BDC Command Summary | Table | 17-1. | BDC | Command | Summary | v |

|---------------------------------|-------|-------|-----|---------|---------|---|

|---------------------------------|-------|-------|-----|---------|---------|---|

<sup>1</sup> The SYNC command is a special operation that does not have a command code.

Because the HCS08 is a family of 8-bit MCUs, the settings in the timer channel registers are buffered to ensure coherent 16-bit updates and to avoid unexpected PWM pulse widths. Writes to any of the registers, TPMxMODH, TPMxMODL, TPMxCnVH, and TPMxCnVL, actually write to buffer registers. Values are transferred to the corresponding timer channel registers only after both 8-bit bytes of a 16-bit register have been written and the timer counter overflows (reverses direction from up-counting to down-counting at the end of the terminal count in the modulus register). This TPMxCNT overflow requirement only applies to PWM channels, not output compares.

Optionally, when TPMxCNTH:TPMxCNTL = TPMxMODH:TPMxMODL, the TPM can generate a TOF interrupt at the end of this count. The user can choose to reload any number of the PWM buffers, and they will all update simultaneously at the start of a new period.

Writing to TPMxSC cancels any values written to TPMxMODH and/or TPMxMODL and resets the coherency mechanism for the modulo registers. Writing to TPMxCnSC cancels any values written to the channel value registers and resets the coherency mechanism for TPMxCnVH:TPMxCnVL.

# B.4 TPM Interrupts

The TPM generates an optional interrupt for the main counter overflow and an interrupt for each channel. The meaning of channel interrupts depends on the mode of operation for each channel. If the channel is configured for input capture, the interrupt flag is set each time the selected input capture edge is recognized. If the channel is configured for output compare or PWM modes, the interrupt flag is set each time the main timer counter matches the value in the 16-bit channel value register. See the Resets, Interrupts, and System Configuration chapter for absolute interrupt vector addresses, priority, and local interrupt mask control bits.

For each interrupt source in the TPM, a flag bit is set on recognition of the interrupt condition such as timer overflow, channel input capture, or output compare events. This flag may be read (polled) by software to verify that the action has occurred, or an associated enable bit (TOIE or CHnIE) can be set to enable hardware interrupt generation. While the interrupt enable bit is set, a static interrupt will be generated whenever the associated interrupt flag equals 1. It is the responsibility of user software to perform a sequence of steps to clear the interrupt flag before returning from the interrupt service routine.

# B.4.1 Clearing Timer Interrupt Flags

TPM interrupt flags are cleared by a 2-step process that includes a read of the flag bit while it is set (1) followed by a write of 0 to the bit. If a new event is detected between these two steps, the sequence is reset and the interrupt flag remains set after the second step to avoid the possibility of missing the new event.

# B.4.2 Timer Overflow Interrupt Description

The conditions that cause TOF to become set depend on the counting mode (up or up/down). In up-counting mode, the 16-bit timer counter counts from 0x0000 through 0xFFFF and overflows to 0x0000on the next counting clock. TOF becomes set at the transition from 0xFFFF to 0x0000. When a modulus limit is set, TOF becomes set at the transition from the value set in the modulus register to 0x0000. When the counter is operating in up-/down-counting mode, the TOF flag gets set as the counter changes direction