Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 201010                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | XC800                                                                         |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 86MHz                                                                         |

| Connectivity               | LINbus, SSI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                         |

| Number of I/O              | 27                                                                            |

| Program Memory Size        | 8KB (8K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 768 × 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                   |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 140°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 38-TFSOP (0.173", 4.40mm Width)                                               |

| Supplier Device Package    | PG-TSSOP-38                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saa-xc866l-2fra-be |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

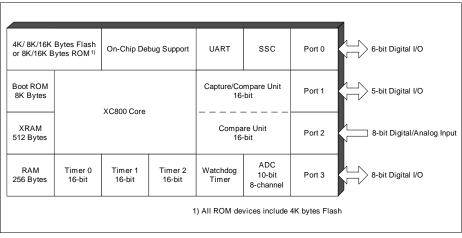

# 8-Bit Single-Chip Microcontroller XC800 Family

SAA-XC866

# 1 Summary of Features

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 512 bytes of XRAM

- 4/8/16 Kbytes of Flash; or

8/16 Kbytes of ROM, with additional 4 Kbytes of Flash (includes memory protection strategy)

- I/O port supply at 3.3 V/5.0 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

(further features are on next page)

## **General Device Information**

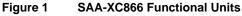

## 2.2 Logic Symbol

Figure 3 SAA-XC866 Logic Symbol

#### **General Device Information**

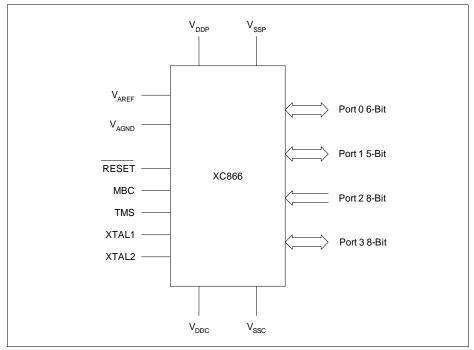

## 2.3 Pin Configuration

Figure 4 SAA-XC866 Pin Configuration, PG-TSSOP-38 Package (top view)

#### Table 7 System Control Register Overview (cont'd)

| Addr            | Register Name                                                          |                                                                | Bit       | 7               | 6                      | 5      | 4                | 3           | 2           | 1           | 0            |  |

|-----------------|------------------------------------------------------------------------|----------------------------------------------------------------|-----------|-----------------|------------------------|--------|------------------|-------------|-------------|-------------|--------------|--|

| B3 <sub>H</sub> | ID                                                                     | Reset: 01 <sub>H</sub>                                         | Bit Field |                 |                        | PRODID |                  |             |             | VERID       | 1            |  |

|                 | Identity Register                                                      |                                                                | Туре      |                 | r                      |        |                  |             |             | r           |              |  |

| B4 <sub>H</sub> | PMCON0<br>Power Mode Control Re                                        | PMCON0 Reset: 00 <sub>H</sub><br>Power Mode Control Register 0 |           | 0               | WDT WKRS WK<br>RST SEL |        |                  | SD          | PD          | D WS        |              |  |

|                 |                                                                        |                                                                | Туре      | r               | rwh                    | rwh    | rw               | rw          | rwh         | r           | w            |  |

| B5 <sub>H</sub> | PMCON1 Reset: 00 <sub>H</sub><br>Power Mode Control Register 1         |                                                                | Bit Field | 0               |                        |        |                  | T2_DIS      | CCU<br>_DIS | SSC<br>_DIS | ADC<br>_DIS  |  |

|                 |                                                                        |                                                                | Туре      |                 |                        | r      |                  | rw          | rw          | rw          | rw           |  |

| B6 <sub>H</sub> | OSC_CON Reset: 08 <sub>H</sub><br>OSC Control Register                 |                                                                | Bit Field |                 | 0                      |        | OSC<br>PD        | XPD         | OSC<br>SS   | ORD<br>RES  | OSCR         |  |

|                 |                                                                        |                                                                | Туре      |                 | r                      |        | rw               | rw          | rw          | rwh         | rh           |  |

| B7 <sub>H</sub> | PLL_CON<br>PLL Control Register                                        | Reset: 20 <sub>H</sub>                                         | Bit Field |                 | NDIV                   |        | VCO<br>BYP       | OSC<br>DISC | RESLD       | LOCK        |              |  |

|                 |                                                                        |                                                                | Туре      |                 | r                      | w      |                  | rw          | rw          | rwh         | rh           |  |

| ΒΑ <sub>Η</sub> | BA <sub>H</sub> CMCON Reset: 00 <sub>H</sub><br>Clock Control Register |                                                                | Bit Field | VCO 0<br>SEL    |                        |        | CLKREL           |             |             |             |              |  |

|                 |                                                                        |                                                                | Туре      | rw r            |                        |        |                  |             | r           | w           |              |  |

| BB <sub>H</sub> | PASSWD<br>Password Register                                            | Reset: 07 <sub>H</sub>                                         | Bit Field | PASS            |                        |        | PROTE MO<br>CT_S |             | DE          |             |              |  |

|                 |                                                                        |                                                                | Туре      | w               |                        |        |                  |             | rh rw       |             |              |  |

| BCH             | FEAL                                                                   | Reset: 00 <sub>H</sub>                                         | Bit Field | ECCERRADDR[7:0] |                        |        |                  |             |             |             |              |  |

|                 | Flash Error Address Reg                                                | gister Low                                                     | Туре      | rh              |                        |        |                  |             |             |             |              |  |

| BD <sub>H</sub> | FEAH                                                                   | Reset: 00 <sub>H</sub>                                         | Bit Field |                 |                        | EC     | CCERRA           | ADDR[15     | :8]         |             |              |  |

|                 | Flash Error Address Reg                                                | gister High                                                    | Туре      |                 |                        |        |                  | 'n          |             |             |              |  |

| BE <sub>H</sub> | COCON<br>Clock Output Control Re                                       | Reset: 00 <sub>H</sub><br>egister                              | Bit Field | (               | )                      | TLEN   | COUT<br>S        | COREL       |             |             |              |  |

|                 |                                                                        |                                                                | Туре      |                 | r                      | rw     | rw               |             | r           | w           |              |  |

| E9 <sub>H</sub> | MISC_CON<br>Miscellaneous Control R                                    | Reset: 00 <sub>H</sub><br>Register                             | Bit Field |                 |                        |        | 0                |             |             |             | DFLAS<br>HEN |  |

|                 |                                                                        |                                                                | Туре      |                 |                        |        | r                |             |             |             | rwh          |  |

| RMAP =          | 0, Page 3                                                              |                                                                |           |                 |                        |        |                  |             |             |             |              |  |

| B3 <sub>H</sub> | XADDRH                                                                 | Reset: F0 <sub>H</sub>                                         | Bit Field |                 |                        |        | AD               | DRH         |             |             |              |  |

|                 |                                                                        |                                                                | Туре      | rw              |                        |        |                  |             |             |             |              |  |

The WDT SFRs can be accessed in the mapped memory area (RMAP = 1).

## Table 8 WDT Register Overview

| Addr            | Register Name                                                                   | Bit       | 7      | 6 | 5          | 4         | 3      | 2         | 1         | 0         |  |

|-----------------|---------------------------------------------------------------------------------|-----------|--------|---|------------|-----------|--------|-----------|-----------|-----------|--|

| RMAP =          | 1                                                                               |           | 1      |   | 1          |           |        |           | 1         |           |  |

| BB <sub>H</sub> | WDTCON Reset: 00 <sub>1</sub><br>Watchdog Timer Control Register                | Bit Field |        | 0 | WINB<br>EN | WDT<br>PR | 0      | WDT<br>EN | WDT<br>RS | WDT<br>IN |  |

|                 |                                                                                 | Туре      |        | r | rw         | rh        | r      | rw        | rwh       | rw        |  |

| BC <sub>H</sub> | WDTREL Reset: 00                                                                | Bit Field | WDTREL |   |            |           |        |           |           |           |  |

|                 | Watchdog Timer Reload Register                                                  |           | rw     |   |            |           |        |           |           |           |  |

| BD <sub>H</sub> | D <sub>H</sub> WDTWINB Reset: 00 <sub>H</sub><br>Watchdog Window-Boundary Count |           |        |   |            | WDT       | WINB   |           |           |           |  |

|                 | Register                                                                        | Туре      | rw     |   |            |           |        |           |           |           |  |

| BE <sub>H</sub> | WDTL Reset: 00                                                                  | Bit Field |        |   |            | WDT       | [7:0]  |           |           |           |  |

|                 | Watchdog Timer Register Low                                                     | Туре      | rh     |   |            |           |        |           |           |           |  |

| BF <sub>H</sub> | WDTH Reset: 00                                                                  | Bit Field |        |   |            | WDT       | [15:8] |           |           |           |  |

|                 | Watchdog Timer Register High                                                    | Туре      | rh     |   |            |           |        |           |           |           |  |

#### Table 9 Port Register Overview (cont'd)

| Addr            | Register Name                     | Bit       | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-----------------|-----------------------------------|-----------|----|----|----|----|----|----|----|----|

| B1 <sub>H</sub> | P3_ALTSEL1 Reset: 00 <sub>H</sub> | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Alternate Select 1 Register    | Туре      | rw |

| RMAP =          | RMAP = 0, Page 3                  |           |    |    |    |    |    |    |    |    |

| 80 <sub>H</sub> | P0_OD Reset: 00 <sub>H</sub>      | Bit Field | (  | C  | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P0 Open Drain Control Register    | Туре      |    | r  | rw | rw | rw | rw | rw | rw |

| 90 <sub>H</sub> | P1_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | 0  |    |    | P1 | P0 |

|                 | P1 Open Drain Control Register    | Туре      | rw | rw | rw |    | r  |    | rw | rw |

| B0 <sub>H</sub> | P3_OD Reset: 00 <sub>H</sub>      | Bit Field | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 |

|                 | P3 Open Drain Control Register    | Туре      | rw |

The ADC SFRs can be accessed in the standard memory area (RMAP = 0).

## Table 10 ADC Register Overview

| Addr            | Register Name                                           | Bit                       | 7          | 6          | 5       | 4    | 3         | 2     | 1          | 0    |  |

|-----------------|---------------------------------------------------------|---------------------------|------------|------------|---------|------|-----------|-------|------------|------|--|

| RMAP =          | 0                                                       |                           |            |            |         | 1    |           |       |            |      |  |

| D1 <sub>H</sub> | ADC_PAGE Reset: 0                                       | 0 <sub>H</sub> Bit Field  | C          | P          | ST      | NR   | 0         | PAGE  |            |      |  |

|                 | Page Register for ADC                                   | Туре                      | ,          | N          |         | w    | r         | rwh   |            |      |  |

| RMAP =          | 0, Page 0                                               |                           |            |            |         |      |           |       |            |      |  |

| CA <sub>H</sub> | ADC_GLOBCTR Reset: 3                                    | 0 <sub>H</sub> Bit Field  | ANON       | DW         | CTC     |      |           | 0     |            |      |  |

|                 | Global Control Register                                 | Туре                      | rw         | rw rw      |         |      |           | r     |            |      |  |

| CB <sub>H</sub> | ADC_GLOBSTR Reset: 0<br>Global Status Register          | 00 <sub>H</sub> Bit Field |            | 0          |         | CHNR |           | 0     | SAM<br>PLE | BUSY |  |

|                 |                                                         | Туре                      |            | r          |         | rh   |           | r     | rh         | rh   |  |

| CCH             | ADC_PRAR Reset: 0                                       | 0 <sub>H</sub> Bit Field  | ASEN1      | ASEN0      | 0       | ARBM | CSM1      | PRIO1 | CSM0       | PRIO |  |

|                 | Priority and Arbitration Register                       | Туре                      | rw         | rw         | r       | rw   | rw        | rw    | rw         | rw   |  |

| CD <sub>H</sub> | ADC_LCBR Reset: B                                       | 7 <sub>H</sub> Bit Field  |            | BOU        | ND1     |      |           | BOL   | JND0       |      |  |

|                 | Limit Check Boundary Register                           | Туре                      |            | ۲١         | v       |      |           | rw    |            |      |  |

| CEH             | ADC_INPCR0 Reset: 0                                     | 0 <sub>H</sub> Bit Field  |            | STC        |         |      |           |       |            |      |  |

|                 | Input Class Register 0                                  | Туре                      |            | rw         |         |      | w         |       |            |      |  |

| CF <sub>H</sub> | ADC_ETRCR Reset: 0<br>External Trigger Control Register | 00 <sub>H</sub> Bit Field | SYNEN<br>1 | SYNEN<br>0 | ETRSEL1 |      | 1 ETRSELO |       | 0          |      |  |

|                 |                                                         | Туре                      | rw         | rw         | rw      |      |           |       | rw         |      |  |

| RMAP =          | 0, Page 1                                               |                           |            |            |         |      |           |       |            |      |  |

| CA <sub>H</sub> | ADC_CHCTR0 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          | LCC        |         | 0    |           | RES   | RSEL       |      |  |

|                 | Channel Control Register 0                              | Туре                      | r          | rw         |         | r    |           | r     | w          |      |  |

| CBH             | ADC_CHCTR1 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          |            | LCC     |      | LCC 0     |       | RESRSEL    |      |  |

|                 | Channel Control Register 1                              | Туре                      | r          |            | rw      |      |           | rw    |            | w    |  |

| CCH             | ADC_CHCTR2 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          |            | LCC     |      | 0         |       | RESRSEL    |      |  |

|                 | Channel Control Register 2                              | Туре                      | r          |            | rw      |      |           | r     | rw         |      |  |

| CD <sub>H</sub> | ADC_CHCTR3 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          |            | LCC     |      |           | 0     | RES        | RSEL |  |

|                 | Channel Control Register 3                              | Туре                      | r          |            | rw      |      |           | r     |            | w    |  |

| CEH             | ADC_CHCTR4 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          |            | LCC     |      |           | 0     | RES        | RSEL |  |

|                 | Channel Control Register 4                              | Туре                      | r          |            | rw      |      |           | r     | r          | w    |  |

| CF <sub>H</sub> | ADC_CHCTR5 Reset: 0                                     |                           | 0          |            | LCC     |      |           | 0     | RES        | RSEL |  |

|                 | Channel Control Register 5                              | Туре                      | r          |            | rw      |      |           | r     | r          | w    |  |

| D2 <sub>H</sub> | ADC_CHCTR6 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          |            | LCC     |      |           | 0     | RES        | RSEL |  |

|                 | Channel Control Register 6                              | Туре                      | r          |            | rw      |      |           | r     | r          | w    |  |

| D3 <sub>H</sub> | ADC_CHCTR7 Reset: 0                                     | 0 <sub>H</sub> Bit Field  | 0          |            | LCC     |      |           | 0     | RES        | RSEL |  |

|                 | Channel Control Register 7                              | Type                      | r          | r rw       |         |      | r rw      |       |            |      |  |

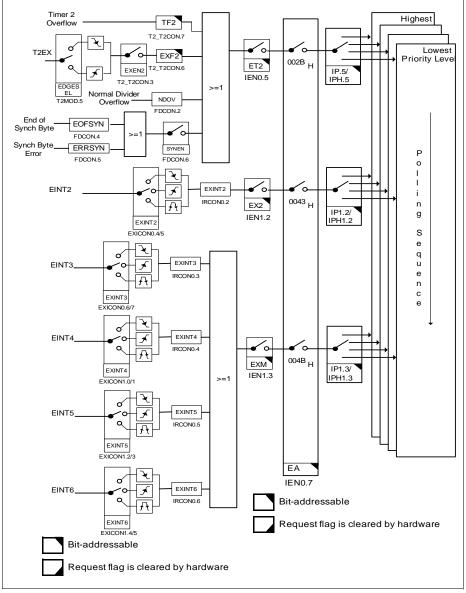

Figure 15 Interrupt Request Sources (Part 2)

## SAA-XC866

#### **Functional Description**

Figure 17 Interrupt Request Sources (Part 4)

## 3.7.1 Module Reset Behavior

**Table 18** shows how the functions of the SAA-XC866 are affected by the various reset types. A "∎" means that this function is reset to its default state.

| Module/<br>Function   | Wake-Up<br>Reset                     | Watchdog<br>Reset      | Hardware<br>Reset      | Power-On<br>Reset         | Brownout<br>Reset         |

|-----------------------|--------------------------------------|------------------------|------------------------|---------------------------|---------------------------|

| CPU Core              |                                      |                        |                        |                           |                           |

| Peripherals           |                                      |                        |                        |                           |                           |

| On-Chip<br>Static RAM | Not affected, reliable               | Not affected, reliable | Not affected, reliable | Affected, un-<br>reliable | Affected, un-<br>reliable |

| Oscillator,<br>PLL    |                                      | Not affected           |                        |                           |                           |

| Port Pins             |                                      |                        |                        |                           |                           |

| EVR                   | The voltage regulator is switched on | Not affected           |                        |                           |                           |

| FLASH                 |                                      |                        |                        |                           |                           |

| NMI                   | Disabled                             | Disabled               |                        |                           |                           |

Table 18 Effect of Reset on Device Functions

## 3.7.2 Booting Scheme

When the SAA-XC866 is reset, it must identify the type of configuration with which to start the different modes once the reset sequence is complete. Thus, boot configuration information that is required for activation of special modes and conditions needs to be applied by the external world through input pins. After power-on reset or hardware reset, the pins MBC, TMS and P0.0 collectively select the different boot options. **Table 19** shows the available boot options in the SAA-XC866.

| MBC | TMS | P0.0 | Type of Mode                                                                      | PC Start Value    |

|-----|-----|------|-----------------------------------------------------------------------------------|-------------------|

| 1   | 0   | х    | User Mode; on-chip OSC/PLL non-bypassed                                           | 0000 <sub>H</sub> |

| 0   | 0   | х    | BSL Mode; on-chip OSC/PLL non-bypassed                                            | 0000 <sub>H</sub> |

| 0   | 1   | 0    | OCDS Mode <sup>1)</sup> ; on-chip OSC/PLL non-<br>bypassed                        | 0000 <sub>H</sub> |

| 1   | 1   | 0    | Standalone User (JTAG) Mode <sup>2)</sup> ; on-chip OSC/PLL non-bypassed (normal) | 0000 <sub>H</sub> |

Table 19 SAA-XC866 Boot Selection

<sup>1)</sup> The OCDS mode is not accessible if Flash is protected.

<sup>2)</sup> Normal user mode with standard JTAG (TCK,TDI,TDO) pins for hot-attach purpose.

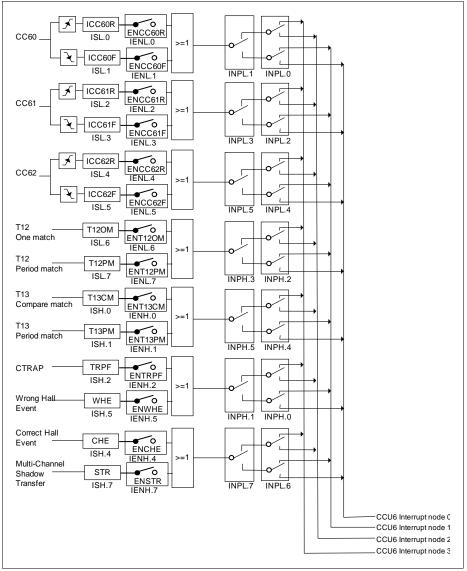

If the WDT is not serviced before the timer overflow, a system malfunction is assumed. As a result, the WDT NMI is triggered (assert WDTTO) and the reset prewarning is entered. The prewarning period lasts for  $30_{\rm H}$  count, after which the system is reset (assert WDTRST).

The WDT has a "programmable window boundary" which disallows any refresh during the WDT's count-up. A refresh during this window boundary constitutes an invalid access to the WDT, causing the reset prewarning to be entered but without triggering the WDT NMI. The system will still be reset after the prewarning period is over. The window boundary is from  $0000_{\rm H}$  to the value obtained from the concatenation of WDTWINB and  $00_{\rm H}$ .

After being serviced, the WDT continues counting up from the value (<WDTREL>  $* 2^8$ ). The time period for an overflow of the WDT is programmable in two ways:

- the input frequency to the WDT can be selected to be either f<sub>PCLK</sub>/2 or f<sub>PCLK</sub>/128

- the reload value WDTREL for the high byte of WDT can be programmed in register WDTREL

The period,  $P_{WDT}$ , between servicing the WDT and the next overflow can be determined by the following formula:

$$P_{WDT} = \frac{2^{(1+WDTIN \times 6)} \times (2^{16} - WDTREL \times 2^8)}{f_{PCLK}}$$

If the Window-Boundary Refresh feature of the WDT is enabled, the period  $P_{WDT}$  between servicing the WDT and the next overflow is shortened if WDTWINB is greater than WDTREL, see **Figure 28**. This period can be calculated using the same formula by replacing WDTREL with WDTWINB. For this feature to be useful, WDTWINB should not be smaller than WDTREL.

Figure 28 WDT Timing Diagram

**Table 24** lists the possible watchdog time range that can be achieved for different module clock frequencies. Some numbers are rounded to 3 significant digits.

| Reload value<br>in WDTREL | Prescaler for f <sub>PCLK</sub> |                 |  |  |  |  |

|---------------------------|---------------------------------|-----------------|--|--|--|--|

|                           | 2 (WDTIN = 0)                   | 128 (WDTIN = 1) |  |  |  |  |

|                           | 26.7 MHz                        | 26.7 MHz        |  |  |  |  |

| FF <sub>H</sub>           | 19.2 μs                         | 1.23 ms         |  |  |  |  |

| 7F <sub>H</sub>           | 2.48 ms                         | 159 ms          |  |  |  |  |

| 00 <sub>H</sub>           | 4.92 ms                         | 315 ms          |  |  |  |  |

Table 24 Watchdog Time Ranges

## 3.14 High-Speed Synchronous Serial Interface

The High-Speed Synchronous Serial Interface (SSC) supports full-duplex and half-duplex synchronous communication. The serial clock signal can be generated by the SSC internally (master mode), using its own 16-bit baud-rate generator, or can be received from an external master (slave mode). Data width, shift direction, clock polarity and phase are programmable. This allows communication with SPI-compatible devices or devices using other synchronous serial interfaces.

#### Features:

- Master and slave mode operation

- Full-duplex or half-duplex operation

- Transmit and receive buffered

- Flexible data format

- Programmable number of data bits: 2 to 8 bits

- Programmable shift direction: LSB or MSB shift first

- Programmable clock polarity: idle low or high state for the shift clock

- Programmable clock/data phase: data shift with leading or trailing edge of the shift clock

- Variable baud rate

- · Compatible with Serial Peripheral Interface (SPI)

- Interrupt generation

- On a transmitter empty condition

- On a receiver full condition

- On an error condition (receive, phase, baud rate, transmit error)

## 3.15 Timer 0 and Timer 1

Timers 0 and 1 are count-up timers which are incremented every machine cycle, or in terms of the input clock, every 2 PCLK cycles. They are fully compatible and can be configured in four different operating modes for use in a variety of applications, see **Table 28**. In modes 0, 1 and 2, the two timers operate independently, but in mode 3, their functions are specialized.

| Mode | Operation                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | <b>13-bit timer</b><br>The timer is essentially an 8-bit counter with a divide-by-32 prescaler.<br>This mode is included solely for compatibility with Intel 8048 devices. |

| 1    | <b>16-bit timer</b><br>The timer registers, TLx and THx, are concatenated to form a 16-bit counter.                                                                        |

| 2    | <b>8-bit timer with auto-reload</b><br>The timer register TLx is reloaded with a user-defined 8-bit value in THx upon overflow.                                            |

| 3    | Timer 0 operates as two 8-bit timersThe timer registers, TL0 and TH0, operate as two separate 8-bit counters.Timer 1 is halted and retains its count even if enabled.      |

#### Table 28 Timer 0 and Timer 1 Modes

infineon

#### **Functional Description**

## 3.19 On-Chip Debug Support

The On-Chip Debug Support (OCDS) provides the basic functionality required for the software development and debugging of XC800-based systems.

The OCDS design is based on these principles:

- use the built-in debug functionality of the XC800 Core

- add a minimum of hardware overhead

- provide support for most of the operations by a Monitor Program

- use standard interfaces to communicate with the Host (a Debugger)

#### Features:

- Set breakpoints on instruction address and within a specified address range

- Set breakpoints on internal RAM address

- · Support unlimited software breakpoints in Flash/RAM code region

- Process external breaks

- Step through the program code

The OCDS functional blocks are shown in **Figure 35**. The Monitor Mode Control (MMC) block at the center of OCDS system brings together control signals and supports the overall functionality. The MMC communicates with the XC800 Core, primarily via the Debug Interface, and also receives reset and clock signals. After processing memory address and control signals from the core, the MMC provides proper access to the dedicated extra-memories: a Monitor ROM (holding the code) and a Monitor RAM (for work-data and Monitor-stack). The OCDS system is accessed through the JTAG<sup>1</sup>, which is an interface dedicated exclusively for testing and debugging activities and is not normally used in an application. The dedicated MBC pin is used for external configuration and debugging control.

Note: All the debug functionality described here can normally be used only after SAA-XC866 has been started in OCDS mode.

<sup>&</sup>lt;sup>1)</sup> The pins of the JTAG port can be assigned to either Port 0 (primary) or Ports 1 and 2 (secondary). User must set the JTAG pins (TCK and TDI) as input during connection with the OCDS system.

## 4 Electrical Parameters

**Chapter 4** provides the characteristics of the electrical parameters which are implementation-specific for the SAA-XC866.

#### 4.1 General Parameters

The general parameters are described here to aid the users in interpreting the parameters mainly in **Section 4.2** and **Section 4.3**.

#### 4.1.1 Parameter Interpretation

The parameters listed in this section represent partly the characteristics of the SAA-XC866 and partly its requirements on the system. To aid interpreting the parameters easily when evaluating them for a design, they are indicated by the abbreviations in the "Symbol" column:

• CC

These parameters indicate **C**ontroller **C**haracteristics, which are distinctive features of the SAA-XC866 and must be regarded for a system design.

• SR

These parameters indicate **S**ystem **R**equirements, which must be provided by the microcontroller system in which the SAA-XC866 is designed in.

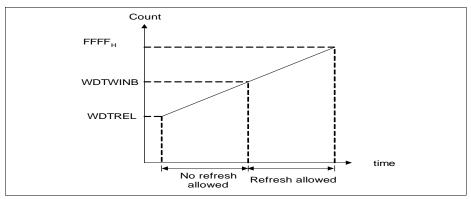

## 4.2.2 Supply Threshold Characteristics

Figure 36 Supply Threshold Parameters

#### Table 35 Supply Threshold Parameters (Operating Conditions apply)

| Parameters                                                         | Symbol               |    | l    | ues  | Unit |   |

|--------------------------------------------------------------------|----------------------|----|------|------|------|---|

|                                                                    |                      |    | min. | typ. | max. |   |

| V <sub>DDC</sub> prewarning voltage <sup>1)</sup>                  | V <sub>DDCPW</sub>   | СС | 2.2  | 2.3  | 2.4  | V |

| $V_{\text{DDC}}$ brownout voltage in active mode <sup>1)</sup>     | V <sub>DDCBO</sub>   | СС | 2.0  | 2.1  | 2.2  | V |

| RAM data retention voltage                                         | V <sub>DDCRDR</sub>  | СС | 0.9  | 1.0  | 1.1  | V |

| $V_{\text{DDC}}$ brownout voltage in power-down mode <sup>2)</sup> | V <sub>DDCBOPD</sub> | CC | 1.3  | 1.5  | 1.7  | V |

| V <sub>DDP</sub> prewarning voltage <sup>3)</sup>                  | V <sub>DDPPW</sub>   | СС | 3.3  | 4.0  | 4.65 | V |

| Power-on reset voltage <sup>2)4)</sup>                             | VDDCPOR              | СС | 1.3  | 1.5  | 1.7  | V |

<sup>1)</sup> Detection is disabled in power-down mode.

<sup>2)</sup> Detection is enabled in both active and power-down mode.

<sup>3)</sup> Detection is enabled for external power supply of 5.0V Detection must be disabled for external power supply of 3.3V.

<sup>4)</sup> The reset of EVR is extended by 300 µs typically after the VDDC reaches the power-on reset voltage.

| Table 36         ADC Characteristics (Operating Conditions apply; V <sub>DDP</sub> = 5V Ran |

|---------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------|

| Parameter                                                    | Symbol                    | Li   | mit Valu | es                        | Unit | Test Conditions/       |

|--------------------------------------------------------------|---------------------------|------|----------|---------------------------|------|------------------------|

|                                                              |                           | min. | typ.     | max.                      |      | Remarks                |

| Overload current coupling factor for                         | K <sub>OVD</sub> CC       | -    | -        | 5.0 x<br>10 <sup>-3</sup> | -    | $I_{\rm OV} > 0^{1/3}$ |

| digital I/O pins                                             |                           | -    | -        | 1.0 x<br>10 <sup>-2</sup> | -    | $I_{\rm OV} < 0^{1/3}$ |

| Switched<br>capacitance at the<br>reference voltage<br>input | C <sub>AREFSW</sub><br>CC | -    | 10       | 20                        | pF   | 1)4)                   |

| Switched<br>capacitance at the<br>analog voltage<br>inputs   | C <sub>AINSW</sub><br>CC  | -    | 5        | 7                         | pF   | 1)5)                   |

| Input resistance of the reference input                      | R <sub>AREF</sub> CC      | -    | 1        | 2                         | kΩ   | 1)                     |

| Input resistance of the selected analog channel              | R <sub>AIN</sub> CC       | -    | 1        | 1.5                       | kΩ   | 1)                     |

<sup>1)</sup> Not subject to production test, verified by design/characterization.

<sup>2)</sup> TUE is tested at  $V_{AREF} = 5.0 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ ,  $V_{DDP} = 5.0 \text{ V}$ .

- <sup>3)</sup> An overload current ( $I_{OV}$ ) through a pin injects a certain error current ( $I_{INJ}$ ) into the adjacent pins. This error current adds to the respective pin's leakage current ( $I_{OZ}$ ). The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ1}| + (|I_{OV}| \times K_{OV})$ . The additional error current may distort the input voltage on analog inputs.

- <sup>4)</sup> This represents an equivalent switched capacitance. This capacitance is not switched to the reference voltage at once. Instead of this, smaller capacitances are successively switched to the reference voltage.

- <sup>5)</sup> The sampling capacity of the conversion C-Network is pre-charged to V<sub>AREF</sub>/2 before connecting the input to the C-Network. Because of the parasitic elements, the voltage measured at ANx is lower than V<sub>AREF</sub>/2.

#### 4.3.2 Output Rise/Fall Times

#### Table 39 Output Rise/Fall Times Parameters (Operating Conditions apply)

| Parameter                     | Symbol                          | Limit<br>Values |      | Unit | Test Conditions      |  |

|-------------------------------|---------------------------------|-----------------|------|------|----------------------|--|

|                               |                                 | min.            | max. |      |                      |  |

| $V_{\text{DDP}}$ = 5V Range   |                                 |                 |      |      |                      |  |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10   | ns   | 20 pF. <sup>3)</sup> |  |

| V <sub>DDP</sub> = 3.3V Range |                                 |                 |      |      |                      |  |

| Rise/fall times 1) 2)         | t <sub>R</sub> , t <sub>F</sub> | -               | 10   | ns   | 20 pF. <sup>4)</sup> |  |

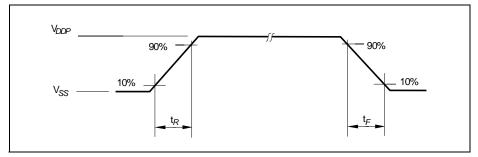

<sup>1)</sup> Rise/Fall time measurements are taken with 10% - 90% of the pad supply.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

<sup>3)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF$  @ 0.125 ns/pF.

<sup>4)</sup> Additional rise/fall time valid for  $C_L = 20pF - 100pF$  @ 0.225 ns/pF.

Figure 41 Rise/Fall Times Parameters

## 4.3.3 Power-on Reset and PLL Timing

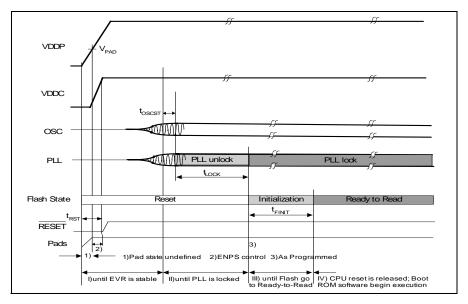

#### Table 40 Power-On Reset and PLL Timing (Operating Conditions apply)

| Parameter                           | Symbol                | Limit Values |      |      | Unit | <b>Test Conditions</b>                                                    |  |

|-------------------------------------|-----------------------|--------------|------|------|------|---------------------------------------------------------------------------|--|

|                                     |                       | min.         | typ. | max. |      |                                                                           |  |

| Pad operating voltage               | V <sub>PAD</sub> CC   | 2.3          | -    | -    | V    | 1)                                                                        |  |

| On-Chip Oscillator<br>start-up time | toscst<br>CC          | _            | -    | 500  | ns   | 1)                                                                        |  |

| Flash initialization time           | t <sub>FINIT</sub> CC | -            | 160  | -    | μs   | 1)                                                                        |  |

| RESET hold time                     | t <sub>RST</sub> SR   | _            | 500  | _    | μs   | $V_{\text{DDP}}$ rise time<br>(10% - 90%) $\leq$<br>500µs <sup>1)2)</sup> |  |

| PLL lock-in in time                 | t <sub>LOCK</sub> CC  | -            | -    | 200  | μs   | 1)                                                                        |  |

| PLL accumulated jitter              | D <sub>P</sub>        | -            | -    | 0.7  | ns   | 1)3)                                                                      |  |

<sup>1)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

<sup>2)</sup> RESET signal has to be active (low) until  $V_{\text{DDC}}$  has reached 90% of its maximum value (typ. 2.5V).

<sup>3)</sup> PLL lock at 80 MHz using a 4 MHz external oscillator. The PLL Divider settings are K = 2, N = 40 and P = 1.

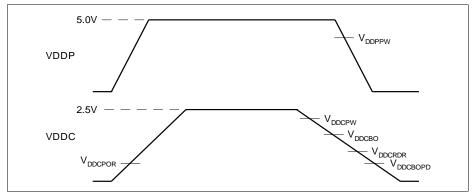

#### Figure 42 Power-on Reset Timing

## 4.3.5 JTAG Timing

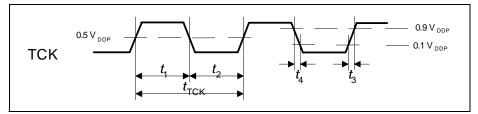

## Table 42TCK Clock Timing (Operating Conditions apply; CL = 50 pF)

| Parameter                         | Symbol              | Limits |     | Unit |

|-----------------------------------|---------------------|--------|-----|------|

|                                   |                     | min    | max |      |

| TCK clock period <sup>1)</sup>    | t <sub>TCK</sub> SR | 50     | -   | ns   |

| TCK high time <sup>1)</sup>       | t <sub>1</sub> SR   | 20     | -   | ns   |

| TCK low time <sup>1)</sup>        | t <sub>2</sub> SR   | 20     | -   | ns   |

| TCK clock rise time <sup>1)</sup> | t <sub>3</sub> SR   | -      | 4   | ns   |

| TCK clock fall time <sup>1)</sup> | t <sub>4</sub> SR   | -      | 4   | ns   |

<sup>1)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.

Figure 43 TCK Clock Timing

#### Package and Reliability

# 5 Package and Reliability

## 5.1 Package Parameters (PG-TSSOP-38)

Table 45 provides the thermal characteristics of the package.

| Parameter                                        | Symbol           |    | Limit | Values | Unit | Notes |

|--------------------------------------------------|------------------|----|-------|--------|------|-------|

|                                                  |                  |    | Min.  | Max.   |      |       |

| Thermal resistance junction case <sup>1)2)</sup> | R <sub>TJC</sub> | CC | -     | 15.7   | K/W  | -     |

| Thermal resistance junction lead <sup>1)2)</sup> | R <sub>TJL</sub> | CC | -     | 39.2   | K/W  | -     |

<sup>1)</sup> The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) are to be combined with the thermal resistances between the junction and the case (R<sub>TJC</sub>), the junction and the lead (R<sub>TJL</sub>) given above, in order to calculate the total thermal resistance between the junction and the ambient (R<sub>TLA</sub>). The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) given above, in order to calculate the total thermal resistance between the junction and the ambient (R<sub>TLA</sub>). The thermal resistances between the case and the ambient (R<sub>TCA</sub>), the lead and the ambient (R<sub>TLA</sub>) depend on the external system (PCB, case) characteristics, and are under user responsibility.

The junction temperature can be calculated using the following equation:  $T_J=T_A + R_{TJA} \times P_D$ , where the  $R_{TJA}$  is the total thermal resistance between the junction and the ambient. This total junction ambient resistance  $R_{TJA}$  can be obtained from the upper four partial thermal resistances, by

a) simply adding only the two thermal resistances (junction lead and lead ambient), or

b) by taking all four resistances into account, depending on the precision needed.

<sup>2)</sup> Not all parameters are 100% tested, but are verified by design/characterization and test correlation.