Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

#### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

#### Details

| Details                 |                                                                       |

|-------------------------|-----------------------------------------------------------------------|

| Product Status          | Active                                                                |

| Applications            | I/O Controller                                                        |

| Core Processor          | 8042 Keyboard Controller                                              |

| Program Memory Type     | ROM (2kB)                                                             |

| Controller Series       | · ·                                                                   |

| RAM Size                | 256 x 8                                                               |

| Interface               | IrDA, LPC, Parallel, Serial, UART                                     |

| Number of I/O           | 40                                                                    |

| Voltage - Supply        | · ·                                                                   |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                     |

| Mounting Type           | Surface Mount                                                         |

| Package / Case          | 144-WFBGA                                                             |

| Supplier Device Package | 144-WFBGA (9x9)                                                       |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/sch3227i-sz |

|                         |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Note     | Name                     | Description                                                                                                                                                                             | VCC<br>Power<br>Plane    | VTR-POWER<br>Plane       | VCC=0<br>Operation<br>(Note 2-14) | Buffer<br>Modes<br>(Note 2-1)                    |

|----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------|-----------------------------------|--------------------------------------------------|

| 2-12     | nPCIRST1 /<br>GP45       | PCI Reset output 1<br>GPIO with Schmitt trigger<br>input                                                                                                                                | nPCIRST1                 | GP45                     | NO GATE                           | (O8/OD8) /<br>(IS/O8/OD8)                        |

| 2-12     | nIDE_RSTDRV<br>/<br>GP44 | IDE Reset output<br>GPIO with Schmitt trigger<br>input                                                                                                                                  | nIDE_RST<br>DRV          | GP44                     | NO GATE                           | (O4/OD4) /<br>(IS/O4/OD4)                        |

|          |                          | GLUI                                                                                                                                                                                    | E LOGIC                  |                          |                                   |                                                  |

|          | PB_IN#                   | Power Button In is used to detect a power button event                                                                                                                                  |                          | PB_IN#                   | NO GATE                           | I                                                |

| 2-9      | SLP_SX#                  | Sx Sleep State Input Pin.                                                                                                                                                               |                          | SLP_SX#                  | NO GATE                           | I                                                |

|          | PB_OUT#                  | Power Button Out                                                                                                                                                                        |                          | PB_OUT#                  | NO GATE                           | O8                                               |

|          | PS_ON#                   | Power supply On                                                                                                                                                                         |                          | PS_ON#                   | NO GATE                           | 012                                              |

|          | -                        | MISCELLA                                                                                                                                                                                | NEOUS PINS               | 8                        |                                   |                                                  |

|          | GP42/<br>nIO_PME         | General Purpose I/O.<br>Power Management Event<br>Output. This active low<br>Power Management Event<br>signal allows this device to<br>request wake-up in either<br>S3 or S5 and below. |                          | GP42/<br>nIO_PME         | NO GATE                           | (I/O12/OD12)<br>/(O12/OD12)                      |

| 2-8, 2-9 | GP60<br>/nLED1<br>/WDT   | General Purpose I/O<br>/nLED1<br>Watchdog Timer Output                                                                                                                                  |                          | GP60<br>/nLED1<br>/WDT   | NO GATE                           | (I/O12/OD12)<br>/(O12/OD12)<br>/(O12/OD12)       |

|          | nFPRST /<br>GP30         | Front Panel Reset /<br>General Purpose IO                                                                                                                                               |                          | nFPRST /<br>GP30         | NO GATE                           | ISPU_400 /<br>(I/O4/OD4)                         |

|          | PWRGD_PS                 | Power Good Input from<br>Power Supply                                                                                                                                                   |                          | PWRGD_PS                 | NO GATE                           | ISPU_400                                         |

|          | PWRGD_OUT                | Power Good Output –<br>Open Drain                                                                                                                                                       |                          | PWRGD_OU<br>T            | NO GATE                           | OD8                                              |

|          | nRSMRST                  | Resume Reset Output                                                                                                                                                                     |                          | nRSMRST                  | NO GATE                           | OD24                                             |

| 2-8, 2-9 | GP61<br>/nLED2 /<br>CLKO | General Purpose I/O<br>/nLED2<br>/ Programmable Clock<br>Output                                                                                                                         |                          | GP61<br>/nLED2 /<br>CLKO | NO GATE                           | (I/O12/OD12)<br>/ (O12/OD12)<br>/ (O12/OD12)     |

| 2-9      | GP27/nIO_SMI<br>/P17     | General Purpose I/O<br>/System Mgt. Interrupt<br>/8042 P17 I/O                                                                                                                          | GP27<br>/nIO_SMI<br>/P17 | GP27                     | /<br>HI-Z                         | (I/O12/OD12)<br>/(O12/OD12)<br>/(I/O12/OD12<br>) |

|          |                          | HARDWARE MC                                                                                                                                                                             | NITORING B               | BLOCK                    |                                   | -                                                |

|          | nHWM_INT                 | Interrupt output for<br>Hardware monitor                                                                                                                                                |                          | nHWM_INT                 |                                   | OD8                                              |

| 2-10     | +5V_IN                   | Analog input for +5V                                                                                                                                                                    | HVTR                     |                          |                                   | I <sub>AN</sub>                                  |

| 2-10     | +2.5_IN                  | Analog input for +2.5V                                                                                                                                                                  | HVTR                     |                          |                                   | I <sub>AN</sub>                                  |

| 2-10     | VCCP_IN                  | Analog input for +Vccp<br>(processor voltage: 1.5 V<br>nominal).                                                                                                                        | HVTR                     |                          |                                   | I <sub>AN</sub>                                  |

| 2-10     | +12V_IN                  | Analog input for +12V                                                                                                                                                                   | HVTR                     |                          |                                   | I <sub>AN</sub>                                  |

#### TABLE 2-5: SCH322X PIN FUNCTIONS DESCRIPTION (CONTINUED)

# 6.0 SERIAL PORT (UART)

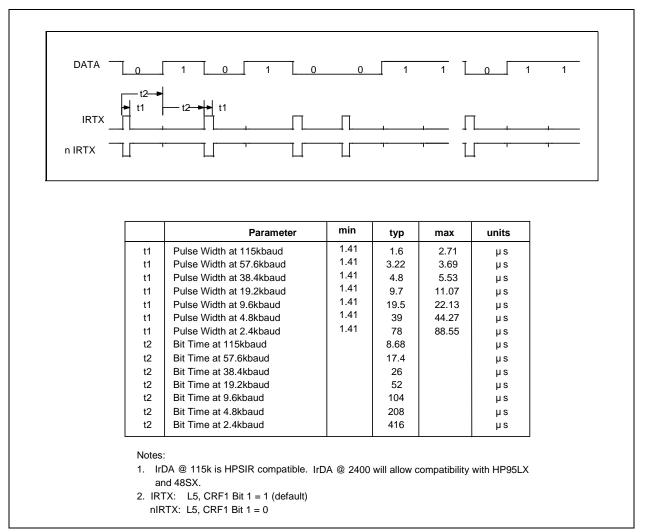

The SCH3227/SCH3226/SCH3224/SCH3222 family incorporates up to four full function UARTs and up to two 4 pin UARTS, for a total of 6 available. They are register compatible with the ACE architecture (NS16450, NS16C550A). The UARTS perform serial-to-parallel conversion on received characters and parallel-to-serial conversion on transmit characters. The data rates are independently programmable from 460.8K baud down to 50 baud. The character options are programmable for 1 start; 1, 1.5 or 2 stop bits; even, odd, sticky or no parity; and prioritized interrupts. The UARTs each contain a programmable baud rate generator that is capable of dividing the input clock or crystal by a number from 1 to 65535. The UARTs are also capable of supporting the MIDI data rate. Refer to the Configuration Registers for information on disabling, power down and changing the base address of the UARTs. The interrupt from a UART is enabled by programming OUT2 of that UART to a logic "1". OUT2 being a logic "0" disables that UART's interrupt. The second UART also supports IrDA, HP-SIR and ASK-IR modes of operation.

### 6.1 Register Description

Addressing of the accessible registers of the Serial Port is shown below. The base addresses of the serial ports are defined by the configuration registers (see Section 23.0, "Configuration Registers," on page 194). The Serial Port registers are located at sequentially increasing addresses above these base addresses. The register set of the UARTS are described below.

| DLAB* | A2 | A1 | A0                           | A0 Register Name                |  |  |

|-------|----|----|------------------------------|---------------------------------|--|--|

| 0     | 0  | 0  | 0                            | 0 Receive Buffer (read)         |  |  |

| 0     | 0  | 0  | 0                            | Transmit Buffer (write)         |  |  |

| 0     | 0  | 0  | 1                            | Interrupt Enable (read/write)   |  |  |

| Х     | 0  | 1  | 0                            | Interrupt Identification (read) |  |  |

| Х     | 0  | 1  | 0                            | FIFO Control (write)            |  |  |

| Х     | 0  | 1  | 1 Line Control (read/write)  |                                 |  |  |

| Х     | 1  | 0  | 0 Modem Control (read/write) |                                 |  |  |

| Х     | 1  | 0  | 1 Line Status (read/write)   |                                 |  |  |

| Х     | 1  | 1  | 0                            | Modem Status (read/write)       |  |  |

| Х     | 1  | 1  | 1                            | 1 Scratchpad (read/write)       |  |  |

| 1     | 0  | 0  | 0                            |                                 |  |  |

| 1     | 0  | 0  | 1                            | 1 Divisor MSB (read/write       |  |  |

TABLE 6-1: ADDRESSING THE SERIAL PORT

Note: \*DLAB is Bit 7 of the Line Control Register

The following section describes the operation of the registers.

### 6.1.1 RECEIVE BUFFER REGISTER (RB)

#### Address Offset = 0H, DLAB = 0, READ ONLY

This register holds the received incoming data byte. Bit 0 is the least significant bit, which is transmitted and received first. Received data is double buffered; this uses an additional shift register to receive the serial data stream and convert it to a parallel 8 bit word which is transferred to the Receive Buffer register. The shift register is not accessible.

### 6.1.2 TRANSMIT BUFFER REGISTER (TB)

### Address Offset = 0H, DLAB = 0, WRITE ONLY

This register contains the data byte to be transmitted. The transmit buffer is double buffered, utilizing an additional shift register (not accessible) to convert the 8 bit data word to a serial format. This shift register is loaded from the Transmit Buffer when the transmission of the previous byte is complete.

| ()                      |

|-------------------------|

| ~                       |

|                         |

|                         |

|                         |

|                         |

| с U                     |

| N N                     |

|                         |

| N                       |

|                         |

|                         |

|                         |

| $\overline{\mathbf{O}}$ |

|                         |

| ö                       |

|                         |

| T                       |

|                         |

| ;H322                   |

| N)                      |

| Ň                       |

| N                       |

| Õ                       |

| Ň                       |

|                         |

|                         |

| S                       |

| Ω                       |

|                         |

|                         |

| 1.1                     |

| ω                       |

| N                       |

|                         |

| N                       |

| 4                       |

| Ţ                       |

|                         |

| U)                      |

| Ċ                       |

|                         |

|                         |

|                         |

| (.)                     |

| <b>W</b>                |

| 22                      |

| ŇŇ                      |

| Ι.Ύ                     |

| N                       |

|                         |

#### TABLE 6-7: REGISTER SUMMARY FOR AN INDIVIDUAL UART CHANNEL (CONTINUED)

| Register<br>Address<br>(Note 6-4) | Register Name      | Register<br>Symbol | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

|-----------------------------------|--------------------|--------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| ADDR = 0<br>DLAB = 1              | Divisor Latch (LS) | DDL                | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| ADDR = 1<br>DLAB = 1              | Divisor Latch (MS) | DLM                | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

**Note 6-4** DLAB is Bit 7 of the Line Control Register (ADDR = 3).

**Note 6-5** Bit 0 is the least significant bit. It is the first bit serially transmitted or received.

**Note 6-6** When operating in the XT mode, this bit will be set any time that the transmitter shift register is empty.

**Note 6-7** This bit no longer has a pin associated with it.

Note 6-8 When operating in the XT mode, this register is not available.

**Note 6-9** These bits are always zero in the non-FIFO mode.

Note 6-10 Writing a one to this bit has no effect. DMA modes are not supported in this chip.

Note 6-11 The UARTS FCR's are shadowed UART FIFO Control Shadow Registers. See Section 24.0, "Runtime Register" for more details.

|                                                                          |                                                                                                                                                                                                                                   |          | ,              |                                  |  |  |  |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|----------------------------------|--|--|--|

| Host Connector                                                           | Pin Number                                                                                                                                                                                                                        | Standard | EPP            | ECP                              |  |  |  |

| 15                                                                       | 81                                                                                                                                                                                                                                | nERROR   | (User Defined) | nFault (1)<br>nPeriphRequest (3) |  |  |  |

| 16                                                                       | 66                                                                                                                                                                                                                                | nINIT    | nRESET         | nInit(1)<br>nReverseRqst(3)      |  |  |  |

| 17                                                                       | 67                                                                                                                                                                                                                                | nSLCTIN  | nAddrstrb      | nSelectIn(1,3)                   |  |  |  |

| <ul> <li>(1) = Compatible Mode</li> <li>(3) = High Speed Mode</li> </ul> |                                                                                                                                                                                                                                   |          |                |                                  |  |  |  |

|                                                                          | <b>Note:</b> For the cable interconnection required for ECP support and the Slave Connector pin numbers, refer to the<br>IEEE 1284 Extended Capabilities Port Protocol and ISA Standard, Rev. 1, 14, July 14, 1993. This document |          |                |                                  |  |  |  |

#### TABLE 7-1: PARALLEL PORT CONNECTOR (CONTINUED)

### 7.1 IBM XT/AT Compatible, Bi-Directional and EPP Modes

#### 7.1.1 DATA PORT

is available from Microsoft.

#### ADDRESS OFFSET = 00H

The Data Port is located at an offset of '00H' from the base address. The data register is cleared at initialization by RESET. During a WRITE operation, the Data Register latches the contents of the internal data bus. The contents of this register are buffered (non inverting) and output onto the PD0 - PD7 ports. During a READ operation in SPP mode, PD0 - PD7 ports are buffered (not latched) and output to the host CPU.

#### 7.1.2 STATUS PORT

#### ADDRESS OFFSET = 01H

The Status Port is located at an offset of '01H' from the base address. The contents of this register are latched for the duration of a read cycle. The bits of the Status Port are defined as follows:

#### Bit 0 TMOUT - TIME OUT

This bit is valid in EPP mode only and indicates that a 10 usec time out has occurred on the EPP bus. A logic O means that no time out error has occurred; a logic 1 means that a time out error has been detected. This bit is cleared by a RESET. If the TIMEOUT\_SELECT bit (bit 4 of the Parallel Port Mode Register 2, 0xF1 in Logical Device 3 Configuration Registers) is '0', writing a one to this bit clears the TMOUT status bit. Writing a zero to this bit has no effect. If the TIMEOUT\_SELECT bit (bit 4 of the Parallel Port Mode Register 2, 0xF1 in Logical Device 3 Configuration Registers) is '0', writing a one to this bit clears the TMOUT status bit. Writing a zero to this bit has no effect. If the TIMEOUT\_SELECT bit (bit 4 of the Parallel Port Mode Register 2, 0xF1 in Logical Device 3 Configuration Registers) is '1', the TMOUT bit is cleared on the trailing edge of a read of the EPP Status Register.

Bits 1, 2 - are not implemented as register bits, during a read of the Printer Status Register these bits are a low level.

#### Bit 3 nERR – nERROR

The level on the nERROR input is read by the CPU as bit 3 of the Printer Status Register. A logic 0 means an error has been detected; a logic 1 means no error has been detected.

#### Bit 4 SLT - Printer Selected Status

The level on the SLCT input is read by the CPU as bit 4 of the Printer Status Register. A logic 1 means the printer is on line; a logic 0 means it is not selected.

#### Bit 5 PE - Paper End

The level on the PE input is read by the CPU as bit 5 of the Printer Status Register. A logic 1 indicates a paper end; a logic 0 indicates the presence of paper.

#### Bit 6 nACK - Acknowledge

The level on the nACK input is read by the CPU as bit 6 of the Printer Status Register. A logic 0 means that the printer has received a character and can now accept another. A logic 1 means that it is still processing the last character or has not received the data.

#### Bit 7 nBUSY - nBUSY

The complement of the level on the BUSY input is read by the CPU as bit 7 of the Printer Status Register. A logic 0 in this bit means that the printer is busy and cannot accept a new character. A logic 1 means that it is ready to accept the next character.

© 2016-2017 Microchip Technology Inc.

# SCH3227/SCH3226/SCH3224/SCH3222

The LED pins can drive a LED when the buffer type is configured to be push-pull and the part is powered by either VCC or VTR, since the buffers for these pins are powered by VTR. This means they will source their specified current from VTR even when VCC is present.

The LED control registers are defined in Section 24.0, "Runtime Register," on page 213.

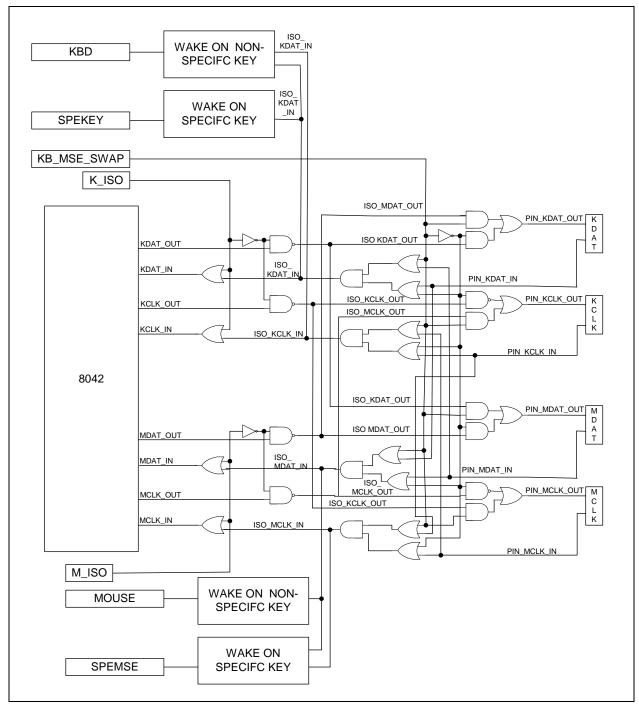

# FIGURE 13-1: 8042 ISOLATION AND KEYBOARD AND MOUSE PORT SWAP REPRESENTATION

Note: This figure is for illustration purposes only and not meant to imply specific implementation details.

## 17.0 BUFFERED PCI OUTPUTS

### 17.1 Buffered PCI Outputs Interface

The SCH322x family devices provide three software controlled PCIRST# outputs and one buffered IDE Reset. Table 17-1 describes the interface.

| Name        | Buffer | Power Well | Description               |

|-------------|--------|------------|---------------------------|

| PCI_RESET#  | PCI_I  | VCC        | PCI Reset Input           |

| nIDE_RSTDRV | OD4    | VCC        | IDE Reset Output          |

| nPCIRST1    | O8/OD8 | VCC        | Buffered PCI Reset Output |

| nPCIRST2    | O8/OD8 | VCC        | Buffered PCI Reset Output |

| nPCIRST3    | O4/OD4 | VCC        | Buffered PCI Reset Output |

#### TABLE 17-1: BUFFERED PCI OUTPUTS INTERFACE

#### 17.1.1 IDE RESET OUTPUT

nIDE\_RSTDRV is an open drain buffered copy of PCI\_RESET#. This signal requires an external 1KΩ pull-up to VCC or 5V. This pin is an output only pin which floats when VCC=0. The pin function's default state on VTR POR is the nIDE\_RST function; however the pin function can be programmed to the a GPO pin function by bit 2 in its GPIO control register.

The nIDE\_RSTDRV output has a programmable forced reset. The software control of the programmable forced reset function is located in the GP4 GPIO Data register. When the GP44 bit (bit 4) is set, the nIDE\_RSTDRV output follows the PCI\_RESET# input; this is the default state on VTR POR. When the GP44 bit is cleared, the nIDE\_RSTDRV output stays low.

See GP44 and GP4 for Runtime Register Description (Section 24.0, "Runtime Register," on page 213).

#### TABLE 17-2: NIDE\_RSTDRV TRUTH TABLE

| PCI_RESET# (Input) | nIDE_RSTDRV (Output) |

|--------------------|----------------------|

| 0                  | 0                    |

| 1                  | Hi-Z                 |

#### TABLE 17-3: NIDE\_RSTDRV TIMING

| Name   | Description                                                                        |  | TYP | MAX | Units |

|--------|------------------------------------------------------------------------------------|--|-----|-----|-------|

| Tf     | nIDE_RSTDRV high to low fall time. Measured form 90% to 10%                        |  |     | 15  | ns    |

| Tpropf | nIDE_RSTDRV high to low propagation time. Measured from PCI_RESET# to nIDE_RSTDRV. |  |     | 22  | ns    |

| СО     | Output Capacitance                                                                 |  |     | 25  | pF    |

| CL     | Load Capacitance                                                                   |  |     | 40  | pF    |

#### 17.1.2 NPCIRSTX OUTPUT LOGIC

The nPCIRST1, nPCIRST2, and nPCIRST3 outputs are 3.3V balance buffer push-pull buffered copies of PCI\_RESET# input. Each pin function's default state on VTR POR is the nPCIRSTx function; however, the pin function can be programmed to the a GPO pin (output only) function by bit 2 in the corresponding GPIO control register (GP45, GP46, GP47).

Each nPCIRSTx output has a programmable force reset. The software control of the programmable forced reset function is located in the GP4 GPIO Data register. When the corresponding (GP45, GP46 GP47) bit in the GP4 GPIO Data register is set, the nPCIRSTx output follows the PCI\_RESET# input; this is the default state on VTR POR. When the corresponding (GP45, GP46, GP47) bit in the GP4 GPIO Data register is cleared, the nPCIRSTx output stays low.

See GP4 for Runtime Register Description.

#### 18.5.1 KEYBOARD DATA FORMAT

Data transmissions from the keyboard consist of an 11-bit serial data stream. A logic 1 is sent at an active high level. The following table shows the functions of the bits.

| Bit | Function                           |

|-----|------------------------------------|

| 1   | Start bit (always 0)               |

| 2   | Data bit 0 (least significant bit) |

| 3   | Data bit 1                         |

| 4   | Data bit 2                         |

| 5   | Data bit 3                         |

| 6   | Data bit 4                         |

| 7   | Data bit 5                         |

| 8   | Data bit 6                         |

| 9   | Data bit 7 (most significant bit)  |

| 10  | Parity bit (odd parity)            |

| 11  | Stop Bit (always 1)                |

The process to find a match for the scan code stored in the Keyboard Scan Code register meets the timing constraints as defined by the IBM Personal System/2<sup>™</sup> Model 50 and 60 Technical Reference, dated April 1987. The timing for the keyboard clock and data signals are shown in Section 27.0, "Timing Diagrams," on page 260. (See Section 27.8, "Keyboard/Mouse Interface Timing," on page 274).

#### 18.5.1.1 Method for Receiving Data is as Follows

The wake on specific key logic snoops the keyboard interface for a particular incoming scan code, which is used to wake the system through a PME event. These scan codes may be comprised of a single byte or multiple bytes. To determine when the first key code is being received, the wake on specific key logic begins sampling the data at the first falling edge of the keyboard clock for the start bit. The data is sampled on each falling edge of the clock. The hardware decodes the byte received and determines if it is valid (i.e., no parity error). Valid scan code bytes received are compared to the programmed scan code as determined by bits [3:2] SPEKEY Scan Code Runtime register located at offset 0x64. If the scan code(s) received matches the value(s) programmed in the Keyboard Scan Code registers then a wake on specific key status event has occurred. The wake on specific key status event is mapped to the PME and Power Button logic.

The snooping logic always checks the incoming data byte for a parity error. The hardware samples the parity bit and checks that the 8 data bits plus the parity bit always have an odd number of 1's (odd parity). If a parity error is detected the state machine used to decode the incoming scan code is reset and begins looking for the first byte in the keyboard scan code sequence.

This process is repeated until a match is found. See Section 18.5.2, "System for Decoding Scan Code Make Bytes Received from the Keyboard," on page 114 and Section 18.5.3, "System for Decoding Scan Code Break Bytes Received from the Keyboard," on page 115.

If the scan code received matches the programmed make code stored in the Keyboard Scan Code registers and no parity error is detected, then it is considered a match. When a match is found and if the stop bit is 1, a PME wake event (KB\_PB\_STS-See Figure 18-1) will be generated within 100usec of the falling edge of clock 10 of the last byte of the sequence. This wake event may be used to generate the assertion of the nIO\_PME signal when in SX power state or below.

The state machine will reset and repeat the process until it is shut off by setting the SPEKEY\_EN bit to '1'.

The SPEKEY\_EN bit at bit 1 of the register at 0xF0 in Logical Device A is used to control the "wake-on-specific feature. This bit is used to turn the logic for this feature on and off. It will disable the 32kHz clock input to the logic. The logic will draw no power when disabled. The bit is defined as follows:

0= "Wake on specific key" logic is on (default)

1= "Wake on specific key" logic is off

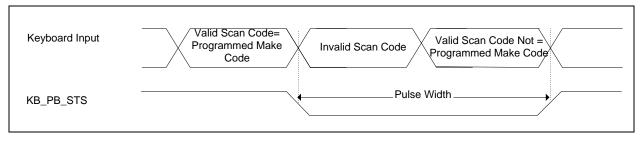

#### FIGURE 18-8: OPTION 1: KB\_PB\_STS WAKE EVENT FIXED PULSE WIDTH

| Keyboard Input | Valid Scan Code<br>(1 or 2 bytes) Scan Code |

|----------------|---------------------------------------------|

| KB_PB_STS      | ← Pulse Width=0.5sec →                      |

#### Option 2 (01): De-assert KB\_PB\_STS after Scan Code Not Equal Programmed Make Code

This option may be used by keyboards that emit single byte or multi-byte make codes for each key pressed. When a valid Scan Code is received that matches the value programmed in the Keyboard Scan Code – Make Byte Register(s), the KB\_PB\_STS wake event signal will be held asserted low until another valid Scan Code is received that is not equal to the programmed make code. Regardless of the state of the SPEKEY bits, no additional wake events will no additional wake events will occur until another valid Scan Code is received that code.

#### FIGURE 18-9: Option 2: Assert KB\_PB\_STS Wake Event Until Scan Code Not Programmed Make Code

- **Note 1:** The Valid Scan Code may be 1 or 2 bytes depending on the SPEKEY ScanCode bits in the Runtime register at offset 64h.

- 2: A Valid Scan Code for single byte codes means that no parity error exists. A Valid Scan Code for Multi-byte Scan Codes requires that no parity error exists and that the first Byte received matches the value programmed in the Keyboard Scan Code Make Byte 1 located in the Runtime Register block at offset 5Fh. This value is typically E0h for Scan 1 and Scan 2 type keyboards. (Example: The ACPI power scan 2 make code is E0h, 37h) Section 18.5.1.2, "Description Of SCAN 1 and SCAN 2," on page 114.

#### Option 3 (10): De-assert KB\_PB\_STS after Scan Code Equal Break Code

This option may be used with single byte and multi-byte scan 1 and scan 2 type keyboards. The break code can be configured for a specific break code or for any valid break code.

the KB\_PB\_STS wake event signal will be held asserted low until a valid break code is detected. The break code can be configured for a specific break code or for any valid break code. Regardless of the state of the SPEKEY bits, no additional wake events will occur until another until a valid break code is detected.

**Note:** Table 18-5 defines how the scan code will be decoded for the Break Code. Once a valid break code is detected, the keyboard power button event will be de-asserted as shown in Figure 18-10.

duty cycle will be held constant for a minimum of 18 periods (206/11.4 = 18.07) until the Ramp Logic increments/decrements the actual PWM duty cycle by '1'.

- If the period of the PWM output is greater than the step size created by the PWM Ramp Rate, the ramp rate logic will force the PWM output to increment/decrement the actual duty cycle in increments larger than 1/255. For example, if the PWM frequency is 11Hz (1/11Hz = 90.9msec) and the PWM Step time is 5msec, the PWM duty cycle output will be incremented 18 or 19 out of 255 (i.e., 90.9/5 = 18.18) until it reaches the calculated duty cycle. Note that the step size may be less if the calculated duty cycle minus the actual duty cycle is less than 18.

- **Note:** The calculated PWM Duty cycle reacts immediately to a change in the temperature reading value. The temperature reading value may be updated once in 105.8msec (default) (see Table 21-2, "ADC Conversion Sequence," on page 126). The internal PWM duty cycle generated by the Ramp Rate control logic gradually ramps up/down to the calculated duty cycle at a rate pre-determined by the value programmed in the PWM Ramp Rate Control bits. The PWM output latches the internal duty cycle generated by the Ramp Rate Control Block every 1/(PWM frequency) seconds to determine the actual duty cycle of the PWM output pin.

#### PWM Output Transition from OFF to ON

When the calculated PWM Duty cycle generated by the auto fan control logic transitions from the 'OFF' state to the 'ON' state (i.e., Current PWM duty cycle>00h), the internal PWM duty cycle in the Ramp Rate Control Logic is initialized to the calculated duty cycle without any ramp time and the PWMx Current Duty Cycle register is set to this value. The PWM output will latch the current duty cycle value in the Ramp Rate Control block to control the PWM output.

#### PWM Output Transition from ON to OFF

Each PWM output has a control bit to determine if the PWM output will transition immediately to the OFF state (default) or if it will gradually step down to Off at the programmed Ramp Rate. These control bits (SZEN) are located in the PWMx Options registers at offsets 94h-96h.

| RRx-[2:0] | PWM Ramp Time (sec)<br>(Time from 33% Duty<br>Cycle to 100% Duty<br>Cycle) | PWM Ramp Time (sec)<br>(Time from 0% Duty<br>Cycle to 100% Duty<br>Cycle) | Time per<br>PWM Step<br>(PWM Step Size =<br>1/255) | PWM<br>Ramp Rate<br>(Hz) |

|-----------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------|--------------------------|

| 000       | 35                                                                         | 52.53                                                                     | 206 msec                                           | 4.85                     |

| 001       | 17.6                                                                       | 26.52                                                                     | 104 msec                                           | 9.62                     |

| 010       | 11.8                                                                       | 17.595                                                                    | 69 msec                                            | 14.49                    |

| 011       | 7.0                                                                        | 10.455                                                                    | 41 msec                                            | 24.39                    |

| 100       | 4.4                                                                        | 6.63                                                                      | 26 msec                                            | 38.46                    |

| 101       | 3.0                                                                        | 4.59                                                                      | 18 msec                                            | 55.56                    |

| 110       | 1.6                                                                        | 2.55                                                                      | 10 msec                                            | 100                      |

| 111       | 0.8                                                                        | 1.275                                                                     | 5 msec                                             | 200                      |

#### TABLE 21-4: PWM RAMP RATE

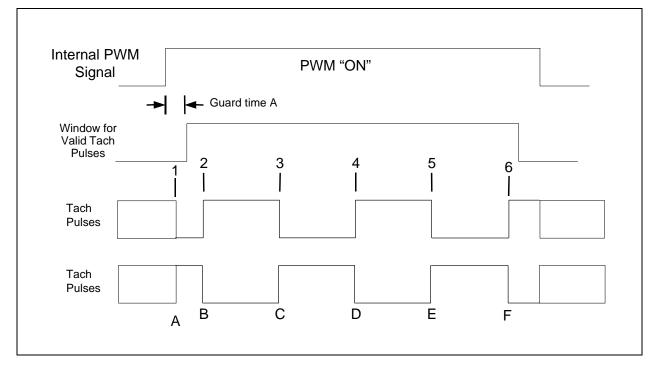

#### FIGURE 21-16: PWM AND TACHOMETER CONCEPT

#### 21.14.2.5.1 Fan Tachometer Options for Mode 2

- 2, 3, 5 or 9 "edges" to calculate the fan speed (Figure 21-16)

- Guard time A is programmable (8-63 clocks) to account for delays in the system (Figure 21-16)

- Suggested PWM frequencies for mode 2 are: 11.0 Hz, 14.6 Hz, 21.9 Hz, 29.3 Hz, 35.2 Hz, 44.0 Hz, 58.6 Hz, 87.7Hz

- · Option to ignore first 3 tachometer edges after guard time

- Option to force tach reading register to FFFEh to indicate a slow fan.

#### 21.14.2.6 Fan Tachometer Reading Registers:

The Tachometer Reading registers are 16 bits, unsigned. When one byte of a 16-bit register is read, the other byte latches the current value until it is read, in order to ensure a valid reading. The order is LSB first, MSB second. The value FFFFh indicates that the fan is not spinning, or the tachometer input is not connected to a valid signal (this could be triggered by a counter overflow). These registers are read only – a write to these registers has no effect.

- **Note 1:** The Fan Tachometer Reading registers always return an accurate fan tachometer measurement, even when a fan is disabled or non-functional.

- **2:** FFFFh indicates that the fan is not spinning, or the tachometer input is not connected to a valid signal (This could be triggered by a counter overflow).

- 3: The Tachometer registers are read only a write to these registers has no effect.

- 4: Mode 1 should be enabled and the tachometer limit register should be set to FFFFh if a tachometer input is left unconnected.

#### 21.14.2.7 Programming Options for Each Tachometer Input

The features defined in this section are programmable via the TACHx Option registers located at offsets 90h-92h and the PWMx Option registers located at offsets 94h-96h.

#### 21.14.2.7.1 Tach Reading Update Time

In Mode 1, the Fan Tachometer Reading registers are continuously updated. In Mode 2, the fan tachometer registers are updated every 300ms, 500msec, or 1000msec. This option is programmed via bits[1:0] in the PWMx Option register. The PWM associated with a particular TACH(s) determines the TACH update time.

#### 21.14.2.7.2 Programmed Number Of Tach Edges

In modes 1 & 2, the number of edges is programmable for 2, 3, 5 or 9 edges (i.e., ½ tachometer pulse, 1 tachometer pulse, 2 tachometer pulses). This option is programmed via bits[2:1] in the TachX Option register.

**Note:** The "5 edges" case corresponds to two tachometer pulses, or 1 RPM for most fans. Using the other edge options will require software to scale the values in the reading register to correspond to the count for 1 RPM.

#### 21.14.2.7.3 Guard Time (Mode 2 Only)

The guard time is programmable from 8 to 63 clocks (90kHz). This option is programmed via bits[4:3] in the TachX Option register.

#### 21.14.2.7.4 Ignore first 3 tachometer edges (Mode 2 Only)

Option to ignore first 3 tachometer edges after guard time. This option is programmed for each tachometer via bits[2:0] in the TACHx Option register. Default is do not ignore first 3 tachometer edges after guard time.

#### 21.14.2.8 Summary of Operation for Modes 1 & 2

#### The following summarizes the detection cases:

- No edge occurs during the PWM 'ON' time: indicate this condition as a stalled fan

- The tachometer reading register contains FFFFh.

- One edge (or less than programmed number of edges) occurs during the PWM 'ON' time: indicate this condition as a slow fan.

- If the SLOW bit is enabled, the tachometer reading register will be set to FFFEh to indicate that this is a slow fan instead of a seized fan. Note that this operation also pertains to the case where the tachometer counter reaches FFFFh before the programmed number of edges occurs.

- If the SLOW bit is disabled, the tachometer reading register will be set to FFFFh. In this case, no distinction is made between a slow or seized fan.

**Note:** The Slow Interrupt Enable feature (SLOW) is configured in the TACHx Options registers at offsets 90h to 93h.

- The programmed number of edges occurs:

- Mode 1: If the programmed number of edges occurs before the counter reaches FFFFh latch the tachometer count

- Mode 2: If the programmed number of edges occurs during the PWM 'ON' time: latch the tachometer count (see **Note** below).

- **Note 1:** Whenever the programmed number of edges is detected, the edge detection ends and the state machine is reset. The tachometer reading register is updated with the tachometer count value at this time. See Detection of a Stalled Fan on page 154 for the exception to this behavior.

- 2: In the case where the programmed number of edges occurs during the "on", the tachometer value is latched when the last required edge is detected.

|             | TABLE 22-1: REGISTER SUMMARY (CONTINUED) |                                                        |      |              |            |            |               |                      |                      |                      |                         |                               |           |   |

|-------------|------------------------------------------|--------------------------------------------------------|------|--------------|------------|------------|---------------|----------------------|----------------------|----------------------|-------------------------|-------------------------------|-----------|---|

| Reg<br>Addr | Read/<br>Write                           | Reg Name                                               |      | Bit 7<br>MSb | Bit 6      | Bit 5      | Bit 4         | Bit 3                | Bit 2                | Bit 1                | Bit 0<br>LSb            | Default<br>Value              | Lock      |   |

| 9Ch         | R/W                                      | VTR Limit Hi                                           |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | FFh                           | No        |   |

| 9Dh         | R/W                                      | VBAT Limit Low                                         |      |              |            |            |               |                      |                      |                      |                         | 00h                           | No        |   |

| 9Eh         | R/W                                      | VBAT Limit Hi                                          |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | FFh                           | No        |   |

| 9Fh         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| A0h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| A1h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| A2h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| A3h         | R/W                                      | MCHP Test Register                                     |      | TST7         | TST6       | TST5       | TST4          | TST3                 | TST2                 | TST1                 | TST0                    | 00h<br>N/A                    | Yes       |   |

| A4h         | R                                        | MCHP Test Register                                     |      | TST7         | TST6       | TST5       | TST4          | TST3                 | TST2                 | TST1                 | TST0                    | 02h                           | No        |   |

| A5h         | R/WC                                     | Interrupt Status 1 Secondary                           |      | INT23        | D2         | AMB        | D1            | 5V                   | VCC                  | Vccp                 | 2.5V                    | 00h<br>Note 22-8              | No        |   |

| A6h         | R/WC                                     | Interrupt Status 2 Secondary                           |      | ERR2         | ERR1       | RES        | FAN-<br>TACH3 | FAN-<br>TACH2        | FAN-<br>TACH1        | RES                  | 12V                     | 00h<br>Note 22-8              | No        |   |

| A7h         | RWC                                      | Interrupt Status 3 Secondary                           | INS3 | RES          | RES        | RES        | RES           | RES                  | RES                  | VBAT                 | VTR                     | 00h                           | No        |   |

| A8h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| A9h         | R/W                                      | MCHP Test Register                                     |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 00h                           | Yes       | ļ |

| AAh         | R/W                                      | MCHP Test Register                                     |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 00h                           | Yes       | ļ |

| ABh         | R/W                                      | Tach 1-3 Mode                                          |      | T1M1         | T1M0       | T2M1       | T2M0          | T3M1                 | T3M0                 | RES                  | RES                     | 00h                           | No        | ļ |

| ACh         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| ADh<br>AEh  | R<br>R/W                                 | MCHP Test Register<br>Top Temperature Remote Diode 1   |      | 7<br>7       | 6<br>6     | 5<br>5     | 4             | 3<br>3               | 2                    | 1<br>1               | 0                       | 00h<br>2Dh                    | No<br>Yes |   |

| AFh         | R/W                                      | (Zone 1)<br>Top Temperature Remote Diode 2<br>(Zone 3) |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | Note 22-8<br>2Dh<br>Note 22-8 | Yes       |   |

| B0h         | R                                        | MCHP Test Register                                     |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| B1h         | R                                        | MCHP Test Register                                     |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| B2h         | R                                        | MCHP Test Register                                     |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| B3h         | R/W                                      | Top Temperature Ambient<br>(Zone 2)                    |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 2Dh<br>Note 22-8              | Yes       |   |

| B4h         | R/W                                      | Min Temp Adjust Temp RD1, RD2                          |      | R1ATP<br>1   | R1ATP<br>0 | R2ATP<br>1 | R2ATP<br>0    | RES                  | RES                  | RES                  | RES                     | 00h                           | Yes       |   |

| B5h         | R/W                                      | Min Temp Adjust Temp and Delay<br>Amb                  |      | RES          | RES        | AMATP<br>1 | AMATP<br>0    | RES                  | RES                  | AMAD1                | AMAD0                   | 00h                           | Yes       |   |

| B6h         | R/W                                      | Min Temp Adjust Delay 1-2                              |      | R1AD1        | R1AD0      | R2AD1      | R2AD0         | RES                  | RES                  | RES                  | RES                     | 00h                           | Yes       |   |

| B7h         | R/W                                      | Tmin Adjust Enable                                     |      | RES          | RES        | RES        | RES           | TMIN_<br>ADJ_<br>EN2 | TMIN_<br>ADJ_<br>EN1 | TMIN_<br>ADJ_<br>ENA | TOP_<br>INT_<br>EN      | 00h                           | Yes       |   |

| B8h         | R/WC                                     | Top Temp Exceeded Status                               |      | RES          | RES        | RES        | RES           | RES                  | STS2                 | STS1                 | STSA                    | 00h<br>Note 22-8              | No        |   |

| B9h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| BAh         | R/W                                      | MCHP Reserved                                          |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 04h                           | Yes       |   |

| BBh         | R                                        | MCHP Reserved                                          |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 00h                           | No        |   |

| BCh         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| BDh         | R                                        | MCHP Reserved                                          |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 00h                           | No        |   |

| BEh         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| BFh         | R/W                                      | MCHP Reserved                                          |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | Yes       |   |

| C0h         | R/W                                      | MCHP Reserved                                          |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | Yes       |   |

| C1h         | R/W                                      | Thermtrip Control                                      |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | THER-<br>MTRIP<br>_CTRL | 01h                           | Yes       |   |

| C2h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| C3h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

| C4h         | R/W                                      | ThermTrip Temp Limit RD1 (Zone 1)                      |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 7Fh                           | Yes       |   |

| C5h         | R/W                                      | ThermTrip Temp Limit RD2 (Zone 3)                      |      | 7            | 6          | 5          | 4             | 3                    | 2                    | 1                    | 0                       | 7Fh                           | Yes       |   |

| C6h         | R                                        | Reserved                                               |      | RES          | RES        | RES        | RES           | RES                  | RES                  | RES                  | RES                     | 00h                           | No        |   |

#### TABLE 22-1: REGISTER SUMMARY (CONTINUED)

Note 1: SOFT RESET: Bit 0 of Configuration Control register set to one.

2: All host accesses are blocked for 500µs after Vcc POR (See FIGURE 27-1: Power-Up Timing on page 260.)

### 23.1 Configuration Registers

**CAUTION:** This device contains circuits which must not be used because their pins are not brought out of the package, and are pulled to known states internally. Any features, and especially Logical Devices, that are not listed in this document must not be activated or accessed. Doing so may cause unpredictable behavior and/or excessive currents, and therefore may damage the device and/or the system.

The following table summarizes the logical device allocation for the different varieties of SCH322x devices.

| TADLE $23-2$ . |                      |                      |                                     |                                     |

|----------------|----------------------|----------------------|-------------------------------------|-------------------------------------|

| Logical Device | SCH3222              | SCH3224              | SCH3226                             | SCH3227                             |

| 0              | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

| 1              | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

| 2              | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

| 3              | RESERVED             | PARALLEL PORT        | RESERVED                            | PARALLEL PORT                       |

| 4              | SERIAL PORT 1        | SERIAL PORT 1        | SERIAL PORT 1                       | SERIAL PORT 1                       |

| 5              | SERIAL PORT 2        | SERIAL PORT 2        | SERIAL PORT 2                       | SERIAL PORT 2                       |

| 6              | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

| 7              | KEYBOARD             | KEYBOARD             | KEYBOARD                            | KEYBOARD                            |

| 8              | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

| 9              | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

| Ah             | RUNTIME<br>REGISTERS | RUNTIME<br>REGISTERS | RUNTIME<br>REGISTERS                | RUNTIME<br>REGISTERS                |

| Bh             | SERIAL PORT 3        | RESERVED             | SERIAL PORT 3                       | SERIAL PORT 3                       |

| Ch             | SERIAL PORT 4        | RESERVED             | SERIAL PORT 4                       | SERIAL PORT 4                       |

| Dh             | SERIAL PORT 5        | SERIAL PORT 5        | IF STRAPOPT=1                       | IF STRAPOPT=1                       |

| Eh             | SERIAL PORT 6        | SERIAL PORT 6        | SERIAL PORTS [5/6]<br>ELSE RESERVED | SERIAL PORTS [5/6]<br>ELSE RESERVED |

| Fh             | RESERVED             | RESERVED             | RESERVED                            | RESERVED                            |

TABLE 23-2: SCH322X LOGICAL DEVICE SUMMARY

### TABLE 23-3: CONFIGURATION REGISTER SUMMARY

| Index | Туре                           | PCI Reset       | VCC POR         | VTR POR         | Soft Reset      | Configuration Register                                                                                                                                                                                       |  |  |  |

|-------|--------------------------------|-----------------|-----------------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|       | GLOBAL CONFIGURATION REGISTERS |                 |                 |                 |                 |                                                                                                                                                                                                              |  |  |  |

| 0x02  | W                              | 0x00            | 0x00            | 0x00            | -               | Config Control                                                                                                                                                                                               |  |  |  |

| 0x03  | R                              | -               | -               | -               | -               | Reserved – reads return 0                                                                                                                                                                                    |  |  |  |

| 0x07  | R/W                            | 0x00            | 0x00            | 0x00            | 0x00            | Logical Device Number                                                                                                                                                                                        |  |  |  |

| 0x20  | R                              | 0x7D or<br>0x7F | 0x7D or<br>0x7F | 0x7D or<br>0x7F | 0x7D or<br>0x7F | Device ID - hard wired<br>SCH3222 - 0x7F<br>SCH3224 - 0x7F<br>SCH3226 - 0x7D or 0x7F<br>SCH3227 - 0x7D or 0x7F<br>STRAPOPT pin selects value for<br>SCH3226 and SCH3227.<br>See this register in Table 23-4. |  |  |  |

| 0x19  | R/W                            | -               | 0x00            | 0x00            | -               | TEST8                                                                                                                                                                                                        |  |  |  |

| 0x21  | R                              |                 | Current         | Revision        | •               | Device Rev - hard wired                                                                                                                                                                                      |  |  |  |

| Register                                                                                                          | Address | Description                                                                  |

|-------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------|

| Configuration Address Byte<br>0<br>Default<br>Sysopt0 = 0 0x2E<br>Sysopt0 = 1 0x4E<br>on VCC POR and PCI<br>RESET | 0x26    | Bit[7:1] Configuration Address Bits [7:1]<br>Bit[0] = 0<br>(Note 23-3)       |

| Configuration Address Byte<br>1<br>Default<br>Sysopt1 = 0 0x16<br>Sysopt1 = 1 0x00<br>n VCC POR and PCI<br>RESET  | 0x27    | Bit[7:0] Configuration Address Bits [15:8]<br>Bits[15:21] = 0<br>(Note 23-3) |

| Default = 0x00<br>on VCC POR,<br>SOFT RESET and<br>PCI RESET                                                      | 0x28    | Bits[7:0] Reserved - Writes are ignored, reads return 0.                     |

#### TABLE 23-4: CHIP-LEVEL (GLOBAL) CONFIGURATION REGISTERS (CONTINUED)

**Note 23-3** To allow the selection of the configuration address to a user defined location, these Configuration Address Bytes are used. There is no restriction on the address chosen, except that A0 is 0, that is, the address must be on an even byte boundary. As soon as both bytes are changed, the configuration space is moved to the specified location with no delay (**Note:** Write byte 0, then byte 1; writing CR27 changes the base address).

The configuration address is only reset to its default address upon a PCI Reset or Vcc POR.

**Note:** The default configuration address is specified in Table 23-1, "SYSOPT Strap Option Configuration Address Select," on page 194.

#### 23.1.2 TEST REGISTERS

The following test registers are used in the SCH322x devices.

#### TABLE 23-5: TEST REGISTER SUMMARY

| Register                                         | Address  | Description                                                                                            |

|--------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------|

| TEST 8<br>Default = 0x00, on VCC                 | 0x19 R/W | Test Modes: Reserved for MCHP. Users should not write to this register, may produce undesired results. |

| POR and<br>VTR POR                               |          |                                                                                                        |

| TEST 9                                           | 0x25 R/W | Test Modes: Reserved for MCHP. Users should not write to this register, may produce undesired results. |

| Default = 0x00, on VCC<br>POR and<br>VTR POR     |          |                                                                                                        |

| TEST                                             | 0x29 R/W | Test Modes: Reserved for MCHP. Users should not write to this register, may produce undesired results. |

| Default = 0x00                                   |          |                                                                                                        |

| Note on VTR_POR BIT0/7 are reset                 |          |                                                                                                        |

| BIT1-6 reset on<br>TST_PORB from resgen<br>block |          |                                                                                                        |

| TEST 6                                           | 0x2A R/W | Test Modes: Reserved for MCHP. Users should not write to this register, may produce undesired results. |

| Default = 0x00, on VCC<br>POR and<br>VTR POR     |          |                                                                                                        |

© 2016-2017 Microchip Technology Inc.

# SCH3227/SCH3226/SCH3224/SCH3222

| TABLE 24-2:              | RUNTIME REGISTER POR SUMMARY (CONTINUED) |                              |            |                                 |            |                                  |                                                                            |  |  |

|--------------------------|------------------------------------------|------------------------------|------------|---------------------------------|------------|----------------------------------|----------------------------------------------------------------------------|--|--|

| Register Offset<br>(HEX) | Туре                                     | PCI Reset                    | VCC<br>POR | VTR<br>POR                      | Soft Reset | Vbat POR                         | Register                                                                   |  |  |

| 36                       | R/W                                      | -                            | -          | 0x84                            | -          | -                                | GP33                                                                       |  |  |

| 37                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP34                                                                       |  |  |

| 38                       | R                                        | -                            | -          | -                               | -          | -                                | Reserved                                                                   |  |  |

| 39                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP36                                                                       |  |  |

| 3A                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP37                                                                       |  |  |

| 3B                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP40                                                                       |  |  |

| 3C                       | R                                        | -                            | -          | 0x00                            | -          | -                                | CLK_OUT Register                                                           |  |  |

| 3D                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP42                                                                       |  |  |

| 3E                       | R                                        | -                            | -          | -                               | -          | -                                | Reserved – reads return 0                                                  |  |  |

| 3F                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP50                                                                       |  |  |

| 40                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP51                                                                       |  |  |

| 41                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP52                                                                       |  |  |

| 42                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP53                                                                       |  |  |

| 43                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP54                                                                       |  |  |

| 44                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP55                                                                       |  |  |

| 45                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP56                                                                       |  |  |

| 46                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP57                                                                       |  |  |

| 47                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP60                                                                       |  |  |

| 48                       | R/W                                      | -                            | -          | 0x01                            | -          | -                                | GP61                                                                       |  |  |

| 49                       | Note 2                                   | 0xxxxxxxx                    |            | 0xxxxxx11                       | -          | 0x00000x                         | PWR_REC                                                                    |  |  |

| 49                       | 4-11                                     | b Note 24-<br>12             | -          | b<br>Note 24-<br>12             | -          | xb<br>Note 24-<br>12             | (SCH3227 or SCH3226, and<br>STRAPOPT=0)                                    |  |  |

| 49                       | R                                        | 0xxxxxxx<br>b Note 24-<br>12 | -          | 0xxxxx11<br>b<br>Note 24-<br>12 | -          | 0x00000x<br>xb<br>Note 24-<br>12 | RESERVED<br>(SCH3222, SCH3224, or<br>SCH3227 / SCH3226 with<br>STRAPOPT=1) |  |  |

| 4A                       | R                                        | -                            | -          | -                               | -          | 0x00                             | PS_ON Register<br>(SCH3227 or SCH3226, and<br>STRAPOPT=0)                  |  |  |

| 4A                       | R                                        | -                            | -          | -                               | -          | 0x00                             | RESERVED<br>(SCH3222, SCH3224, or<br>SCH3227 / SCH3226 with<br>STRAPOPT=1) |  |  |

| 4B                       | R/W                                      | -                            | -          | 0x00                            | -          | -                                | GP1                                                                        |  |  |

| 4C                       | R/W                                      | -                            | -          | 0x00                            | -          | -                                | GP2                                                                        |  |  |

| 4D                       | R/W                                      | -                            | -          | 0x00                            | -          | -                                | GP3                                                                        |  |  |