# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 4K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128aclh |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.6.1 Part ID Assignments

The part ID is located in two 8-bit registers PARTIDH and PARTIDL (addresses 0x001A and 0x001B). The read-only value is a unique part ID for each revision of the chip. Table 1-5 shows the assigned part ID number and Mask Set number.

| Device      | Mask Set Number    | Part ID             |

|-------------|--------------------|---------------------|

| MC9S12GA240 | 0N95B              | 0xF080              |

| MC9S12G240  | 0N95B              | 0xF080              |

| MC9S12GA192 | 0N95B              | 0xF080              |

| MC9S12G192  | 0N95B              | 0xF080              |

| MC9S12GA128 | 0N51A              | 0xF180              |

| MC9S12G128  | 0N51A              | 0xF180              |

| MC9S12GA96  | 0N51A              | 0xF180              |

| MC9S12G96   | 0N51A              | 0xF180              |

| MC9S12GA64  | 0N75C              | 0xF280              |

| MC9S12G64   | 0N75C <sup>1</sup> | 0xF280 <sup>1</sup> |

| 1009312004  | 1N75C <sup>2</sup> | 0xF281 <sup>2</sup> |

| MC9S12GA48  | 0N75C              | 0xF280              |

| MC9S12G48   | 0N75C <sup>1</sup> | 0xF280 <sup>1</sup> |

| MC9512G46   | 1N75C <sup>2</sup> | 0xF281 <sup>2</sup> |

| MC9S12GN48  | 0N75C <sup>1</sup> | 0xF280 <sup>1</sup> |

| MC9512GN46  | 1N75C <sup>2</sup> | 0xF281 <sup>2</sup> |

| MC9S12GNA32 | 0N48A              | 0xF380              |

| MC0812CN22  | 0N48A <sup>3</sup> | 0xF380 <sup>3</sup> |

| MC9S12GN32  | 1N48A <sup>4</sup> | 0xF381 <sup>4</sup> |

| MC9S12GNA16 | 0N48A              | 0xF380              |

| MORELOCAL   | 0N48A <sup>3</sup> | 0xF380 <sup>3</sup> |

| MC9S12GN16  | 1N48A <sup>4</sup> | 0xF381 <sup>4</sup> |

Table 1-5. Assigned Part ID Numbers

<sup>1</sup> Only available in 48-pin LQFP and 64-pin LQFP

<sup>2</sup> Only available in 32-pin LQFP

<sup>3</sup> Only available in 48-pin LQFP and 48-pin QFN

<sup>4</sup> Only available in 20-pin TSSOP and 32-pin LQFP

# 1.7 Signal Description and Device Pinouts

This section describes signals that connect off-chip. It includes a pinout diagram, a table of signal properties, and detailed discussion of signals. It is built from the signal description sections of the individual IP blocks on the device.

|             |       | <lowest< th=""><th>Function<br/>PRIORITY</th><th>highest:</th><th>&gt;</th><th>Power</th><th colspan="2">Internal Pull<br/>Resistor</th></lowest<> | Function<br>PRIORITY | highest:    | >           | Power            | Internal Pull<br>Resistor |                |

|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|-------------|------------------|---------------------------|----------------|

| Package Pin | Pin   | 2nd<br>Func.                                                                                                                                       | 3rd<br>Func.         | 4th<br>Func | 5th<br>Func | Supply           | CTRL                      | Reset<br>State |

| 32          | PAD11 | KWAD11                                                                                                                                             | AN11                 | ACMPM       |             | V <sub>DDA</sub> | PER0AD/PPS0AD             | Disabled       |

| 33          | PAD4  | KWAD4                                                                                                                                              | AN4                  |             | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 34          | PAD5  | KWAD5                                                                                                                                              | AN5                  |             | _           | V <sub>DDA</sub> | PER1AD/PPS0AD             | Disabled       |

| 35          | PAD6  | KWAD6                                                                                                                                              | AN6                  |             | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 36          | PAD7  | KWAD7                                                                                                                                              | AN7                  |             | _           | V <sub>DDA</sub> | PER1AD/PPS1AD             | Disabled       |

| 37          | VDDA  | VRH                                                                                                                                                | _                    |             | _           | —                | _                         | _              |

| 38          | VSSA  | _                                                                                                                                                  | _                    |             | _           | _                | _                         | _              |

| 39          | PS0   | RXD0                                                                                                                                               |                      |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 40          | PS1   | TXD0                                                                                                                                               | _                    |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 41          | PS2   | RXD1                                                                                                                                               |                      |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 42          | PS3   | TXD1                                                                                                                                               |                      |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 43          | PS4   | MISO0                                                                                                                                              | _                    |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 44          | PS5   | MOSIO                                                                                                                                              |                      |             | _           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 45          | PS6   | SCK0                                                                                                                                               |                      |             |             | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 46          | PS7   | API_EXTCLK                                                                                                                                         | ECLK                 | SS0         | -           | V <sub>DDX</sub> | PERS/PPSS                 | Up             |

| 47          | PM0   | _                                                                                                                                                  |                      | _           | -           | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

| 48          | PM1   | _                                                                                                                                                  |                      |             |             | V <sub>DDX</sub> | PERM/PPSM                 | Disabled       |

#### Table 1-13. 48-Pin LQFP Pinout for S12GN48

<sup>1</sup> The regular I/O characteristics (see Section A.2, "I/O Characteristics") apply if the EXTAL/XTAL function is disabled

#### Table 3-3. ACMPS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACIF | ACMP Interrupt Flag—<br>ACIF is set when a compare event occurs. Compare events are defined by ACMOD[1:0]. Writing a logic "1" to the<br>bit field clears the flag.<br>0 Compare event has not occurred<br>1 Compare event has occurred |

| 6<br>ACO  | ACMP Output—<br>Reading ACO returns the current value of the synchronized ACMP output. Refer to ACE description to account for initialization delay on this path.                                                                       |

# 3.7 Functional Description

The ACMP compares two analog input voltages applied to ACMPM and ACMPP. The comparator output is high when the voltage at the non-inverting input is greater than the voltage at the inverting input, and is low when the non-inverting input voltage is lower than the inverting input voltage.

The ACMP is enabled with register bit ACMPC[ACE]. When ACMPC[ACE] is set, the input pins are connected to low-pass filters. The comparator output is disconnected from the subsequent logic, which is held at its state for 63 bus clock cycles after setting ACMPC[ACE] to "1" to mask potential glitches. This initialization delay must be accounted for before the first comparison result can be expected.

The initial hold state after reset is zero, thus if input voltages are set to result in "true" result  $(V_{ACMPP} > V_{ACMPM})$  before the initialization delay has passed, a flag will be set immediately after this.

Similarly the flag will also be set when disabling the ACMP, then re-enabling it with the inputs changing to produce an opposite result to the hold state before the end of the initialization delay.

By setting the ACMPC[ACICE] bit the gated comparator output can be connected to the synchronized timer input capture channel 5 (see Figure 3-1). This feature can be used to generate time stamps and timer interrupts on ACMP events.

The comparator output signal synchronized to the bus clock is used to read the comparator output status (ACMPS[ACO]) and to set the interrupt flag (ACMPS[ACIF]).

The condition causing the interrupt flag (ACMPS[ACIF]) to assert is selected with register bits ACMPC[ACMOD1:ACMOD0]. This includes any edge configuration, that is rising, or falling, or rising and falling (toggle) edges of the comparator output. Also flag setting can be disabled.

An interrupt will be generated if the interrupt enable bit (ACMPC[ACIE]) and the interrupt flag (ACMPS[ACIF]) are both set. ACMPS[ACIF] is cleared by writing a 1.

The raw comparator output signal ACMPO can be driven out on an external pin by setting the ACMPC[ACOPE] bit.

- 4-stage state sequencer for trace buffer control

- Tracing session trigger linked to Final State of state sequencer

- Begin and End alignment of tracing to trigger

### 8.1.4 Modes of Operation

The DBG module can be used in all MCU functional modes.

During BDM hardware accesses and whilst the BDM module is active, CPU monitoring is disabled. When the CPU enters active BDM Mode through a BACKGROUND command, the DBG module, if already armed, remains armed.

The DBG module tracing is disabled if the MCU is secure, however, breakpoints can still be generated.

| BDM<br>Enable | BDM<br>Active | MCU<br>Secure | Comparator<br>Matches Enabled            | Breakpoints<br>Possible | Tagging<br>Possible | Tracing<br>Possible |

|---------------|---------------|---------------|------------------------------------------|-------------------------|---------------------|---------------------|

| х             | х             | 1             | Yes                                      | Yes                     | Yes                 | No                  |

| 0             | 0             | 0             | Yes                                      | Only SWI                | Yes                 | Yes                 |

| 0             | 1             | 0             | Active BDM not possible when not enabled |                         |                     |                     |

| 1             | 0             | 0             | Yes                                      | Yes                     | Yes                 | Yes                 |

| 1             | 1             | 0             | No                                       | No                      | No                  | No                  |

Table 8-2. Mode Dependent Restriction Summary

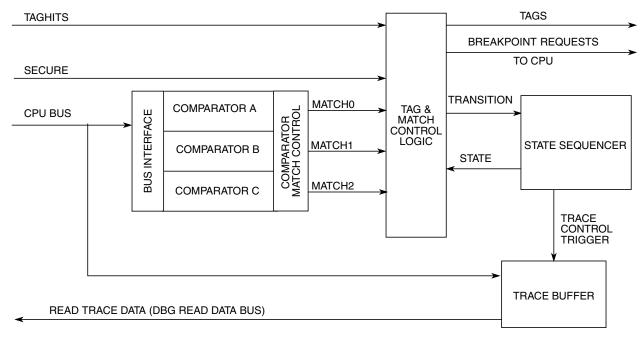

### 8.1.5 Block Diagram

Figure 8-1. Debug Module Block Diagram

Read: DBGACTL if COMRV[1:0] = 00 DBGBCTL if COMRV[1:0] = 01 DBGCCTL if COMRV[1:0] = 10

Write: DBGACTL if COMRV[1:0] = 00 and DBG not armed DBGBCTL if COMRV[1:0] = 01 and DBG not armed DBGCCTL if COMRV[1:0] = 10 and DBG not armed

#### Table 8-22. DBGXCTL Field Descriptions

| Field                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>SZE<br>(Comparators<br>A and B) | <ul> <li>Size Comparator Enable Bit — The SZE bit controls whether access size comparison is enabled for the associated comparator. This bit is ignored if the TAG bit in the same register is set.</li> <li>0 Word/Byte access size is not used in comparison</li> <li>1 Word/Byte access size is used in comparison</li> </ul>                                                                                                                                                                                                                 |

| 6<br>SZ<br>(Comparators<br>A and B)  | <ul> <li>Size Comparator Value Bit — The SZ bit selects either word or byte access size in comparison for the associated comparator. This bit is ignored if the SZE bit is cleared or if the TAG bit in the same register is set.</li> <li>0 Word access size is compared</li> <li>1 Byte access size is compared</li> </ul>                                                                                                                                                                                                                     |

| 5<br>TAG                             | <ul> <li>Tag Select— This bit controls whether the comparator match has immediate effect, causing an immediate state sequencer transition or tag the opcode at the matched address. Tagged opcodes trigger only if they reach the execution stage of the instruction queue.</li> <li>O Allow state sequencer transition immediately on match</li> <li>1 On match, tag the opcode. If the opcode is about to be executed allow a state sequencer transition</li> </ul>                                                                            |

| 4<br>BRK                             | <ul> <li>Break— This bit controls whether a comparator match terminates a debug session immediately, independent of state sequencer state. To generate an immediate breakpoint the module breakpoints must be enabled using the DBGC1 bit DBGBRK.</li> <li>0 The debug session termination is dependent upon the state sequencer and trigger conditions.</li> <li>1 A match on this channel terminates the debug session immediately; breakpoints if active are generated, tracing, if active, is terminated and the module disarmed.</li> </ul> |

| 3<br>RW                              | <ul> <li>Read/Write Comparator Value Bit — The RW bit controls whether read or write is used in compare for the associated comparator. The RW bit is not used if RWE = 0. This bit is ignored if the TAG bit in the same register is set.</li> <li>0 Write cycle is matched1Read cycle is matched</li> </ul>                                                                                                                                                                                                                                     |

| 2<br>RWE                             | <ul> <li>Read/Write Enable Bit — The RWE bit controls whether read or write comparison is enabled for the associated comparator. This bit is ignored if the TAG bit in the same register is set</li> <li>0 Read/Write is not used in comparison</li> <li>1 Read/Write is used in comparison</li> </ul>                                                                                                                                                                                                                                           |

| 1<br>NDB<br>(Comparator A)           | <ul> <li>Not Data Bus — The NDB bit controls whether the match occurs when the data bus matches the comparator register value or when the data bus differs from the register value. This bit is ignored if the TAG bit in the same register is set. This bit is only available for comparator A.</li> <li>Match on data bus equivalence to comparator register contents</li> <li>Match on data bus difference to comparator register contents</li> </ul>                                                                                         |

| 0<br>COMPE                           | Determines if comparator is enabled<br>0 The comparator is not enabled<br>1 The comparator is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                            |

Table 8-23 shows the effect for RWE and RW on the comparison conditions. These bits are ignored if the corresponding TAG bit is set since the match occurs based on the tagged opcode reaching the execution stage of the instruction queue.

### 12.1.1 Features

- 8-, 10-, or 12-bit resolution.

- Automatic return to low power after conversion sequence

- Automatic compare with interrupt for higher than or less/equal than programmable value

- Programmable sample time.

- Left/right justified result data.

- External trigger control.

- Sequence complete interrupt.

- Analog input multiplexer for 8 analog input channels.

- Special conversions for VRH, VRL, (VRL+VRH)/2.

- 1-to-8 conversion sequence lengths.

- Continuous conversion mode.

- Multiple channel scans.

- Configurable external trigger functionality on any AD channel or any of four additional trigger inputs. The four additional trigger inputs can be chip external or internal. Refer to device specification for availability and connectivity.

- Configurable location for channel wrap around (when converting multiple channels in a sequence).

# 12.1.2 Modes of Operation

### 12.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

### 12.1.2.2 MCU Operating Modes

### • Stop Mode

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

### • Wait Mode

ADC12B8C behaves same in Run and Wait Mode. For reduced power consumption continuous conversions should be aborted before entering Wait mode.

#### • Freeze Mode

In Freeze Mode the ADC12B8C will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

This buffer can be turned on or off with the ATDDIEN register for each ATD input pin. This is important so that the buffer does not draw excess current when an ATD input pin is selected as analog input to the ADC12B8C.

# 12.5 Resets

At reset the ADC12B8C is in a power down state. The reset state of each individual bit is listed within the Register Description section (see Section 12.3.2, "Register Descriptions") which details the registers and their bit-field.

# 12.6 Interrupts

The interrupts requested by the ADC12B8C are listed in Table 12-24. Refer to MCU specification for related vector address and priority.

| Interrupt Source            | CCR<br>Mask | Local Enable      |

|-----------------------------|-------------|-------------------|

| Sequence Complete Interrupt | I bit       | ASCIE in ATDCTL2  |

| Compare Interrupt           | l bit       | ACMPIE in ATDCTL2 |

### Table 12-24. ATD Interrupt Vectors

See Section 12.3.2, "Register Descriptions" for further details.

g-to-Digital Converter (ADC10B12CV2)

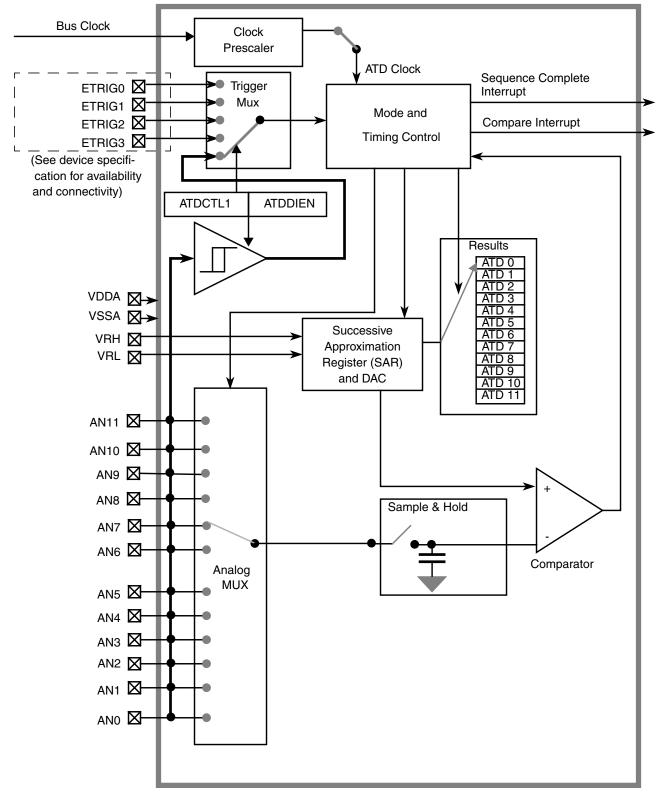

# 13.1.3 Block Diagram

# 16.1.2 Modes of Operation

### 16.1.2.1 Conversion Modes

There is software programmable selection between performing **single** or **continuous conversion** on a **single channel** or **multiple channels**.

### 16.1.2.2 MCU Operating Modes

### • Stop Mode

Entering Stop Mode aborts any conversion sequence in progress and if a sequence was aborted restarts it after exiting stop mode. This has the same effect/consequences as starting a conversion sequence with write to ATDCTL5. So after exiting from stop mode with a previously aborted sequence all flags are cleared etc.

### • Wait Mode

ADC12B16C behaves same in Run and Wait Mode. For reduced power consumption continuous conversions should be aborted before entering Wait mode.

#### • Freeze Mode

In Freeze Mode the ADC12B16C will either continue or finish or stop converting according to the FRZ1 and FRZ0 bits. This is useful for debugging and emulation.

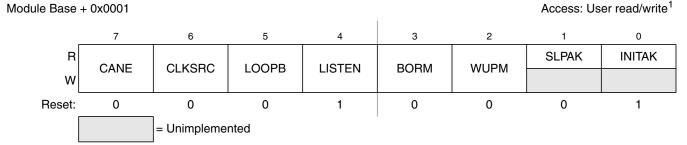

#### Figure 18-5. MSCAN Control Register 1 (CANCTL1)

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except CANE which is write once in normal and anytime in special system operation modes when the MSCAN is in initialization mode (INITRQ = 1 and INITAK = 1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CANE   | MSCAN Enable         0       MSCAN module is disabled         1       MSCAN module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6<br>CLKSRC | MSCAN Clock Source — This bit defines the clock source for the MSCAN module (only for systems with a clock generation module; Section 18.4.3.2, "Clock System," and Section Figure 18-43., "MSCAN Clocking Scheme,").<br>0 MSCAN clock source is the oscillator clock<br>1 MSCAN clock source is the bus clock                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5<br>LOOPB  | Loopback Self Test Mode — When this bit is set, the MSCAN performs an internal loopback which can be used<br>for self test operation. The bit stream output of the transmitter is fed back to the receiver internally. The RXCAN<br>input is ignored and the TXCAN output goes to the recessive state (logic 1). The MSCAN behaves as it does<br>normally when transmitting and treats its own transmitted message as a message received from a remote node.<br>In this state, the MSCAN ignores the bit sent during the ACK slot in the CAN frame acknowledge field to ensure<br>proper reception of its own message. Both transmit and receive interrupts are generated.<br>0 Loopback self test disabled<br>1 Loopback self test enabled |

| 4<br>LISTEN | Listen Only Mode — This bit configures the MSCAN as a CAN bus monitor. When LISTEN is set, all valid CAN messages with matching ID are received, but no acknowledgement or error frames are sent out (see Section 18.4.4.4, "Listen-Only Mode"). In addition, the error counters are frozen. Listen only mode supports applications which require "hot plugging" or throughput analysis. The MSCAN is unable to transmit any messages when listen only mode is active.<br>0 Normal operation<br>1 Listen only mode activated                                                                                                                                                                                                                |

| 3<br>BORM   | Bus-Off Recovery Mode — This bit configures the bus-off state recovery mode of the MSCAN. Refer to Section 18.5.2, "Bus-Off Recovery," for details.         0 Automatic bus-off recovery (see Bosch CAN 2.0A/B protocol specification)         1 Bus-off recovery upon user request                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2<br>WUPM   | <ul> <li>Wake-Up Mode — If WUPE in CANCTL0 is enabled, this bit defines whether the integrated low-pass filter is applied to protect the MSCAN from spurious wake-up (see Section 18.4.5.5, "MSCAN Sleep Mode").</li> <li>0 MSCAN wakes up on any dominant level on the CAN bus</li> <li>1 MSCAN wakes up only in case of a dominant pulse on the CAN bus that has a length of T<sub>wup</sub></li> </ul>                                                                                                                                                                                                                                                                                                                                   |

#### Table 18-4. CANCTL1 Register Field Descriptions

# Chapter 19 Pulse-Width Modulator (S12PWM8B8CV2)

# 19.1 Introduction

The Version 2 of S12 PWM module is a channel scalable and optimized implementation of S12 PWM8B8C Version 1. The channel is scalable in pairs from PWM0 to PWM7 and the available channel number is 2, 4, 6 and 8. The shutdown feature has been removed and the flexibility to select one of four clock sources per channel has improved. If the corresponding channels exist and shutdown feature is not used, the Version 2 is fully software compatible to Version 1.

### 19.1.1 Features

The scalable PWM block includes these distinctive features:

- Up to eight independent PWM channels, scalable in pairs (PWM0 to PWM7)

- Available channel number could be 2, 4, 6, 8 (refer to device specification for exact number)

- Programmable period and duty cycle for each channel

- Dedicated counter for each PWM channel

- Programmable PWM enable/disable for each channel

- Software selection of PWM duty pulse polarity for each channel

- Period and duty cycle are double buffered. Change takes effect when the end of the effective period is reached (PWM counter reaches zero) or when the channel is disabled.

- Programmable center or left aligned outputs on individual channels

- Up to eight 8-bit channel or four 16-bit channel PWM resolution

- Four clock sources (A, B, SA, and SB) provide for a wide range of frequencies

- Programmable clock select logic

### 19.1.2 Modes of Operation

There is a software programmable option for low power consumption in wait mode that disables the input clock to the prescaler.

In freeze mode there is a software programmable option to disable the input clock to the prescaler. This is useful for emulation.

Wait: The prescaler keeps on running, unless PSWAI in PWMCTL is set to 1.

Freeze: The prescaler keeps on running, unless PFRZ in PWMCTL is set to 1.

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CCIF          | <ul> <li>Command Complete Interrupt Flag — The CCIF flag indicates that a Flash command has completed. The CCIF flag is cleared by writing a 1 to CCIF to launch a command and CCIF will stay low until command completion or command violation.</li> <li>O Flash command in progress</li> <li>1 Flash command has completed</li> </ul>                                                                                                                                                                           |

| 5<br>ACCERR        | Flash Access Error Flag — The ACCERR bit indicates an illegal access has occurred to the Flash memory caused by either a violation of the command write sequence (see Section 24.4.4.2) or issuing an illegal Flash command. While ACCERR is set, the CCIF flag cannot be cleared to launch a command. The ACCERR bit is cleared by writing a 1 to ACCERR. Writing a 0 to the ACCERR bit has no effect on ACCERR.<br>0 No access error detected<br>1 Access error detected                                        |

| 4<br>FPVIOL        | <ul> <li>Flash Protection Violation Flag — The FPVIOL bit indicates an attempt was made to program or erase an address in a protected area of P-Flash or EEPROM memory during a command write sequence. The FPVIOL bit is cleared by writing a 1 to FPVIOL. Writing a 0 to the FPVIOL bit has no effect on FPVIOL. While FPVIOL is set, it is not possible to launch a command or start a command write sequence.</li> <li>0 No protection violation detected</li> <li>1 Protection violation detected</li> </ul> |

| 3<br>MGBUSY        | <ul> <li>Memory Controller Busy Flag — The MGBUSY flag reflects the active state of the Memory Controller.</li> <li>0 Memory Controller is idle</li> <li>1 Memory Controller is busy executing a Flash command (CCIF = 0)</li> </ul>                                                                                                                                                                                                                                                                              |

| 2<br>RSVD          | Reserved Bit — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1–0<br>MGSTAT[1:0] | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. See Section 24.4.6, "Flash Command Description," and Section 24.6, "Initialization" for details.                                                                                                                                                                                                                   |

### Table 24-15. FSTAT Field Descriptions

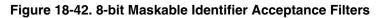

# 24.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

All flags in the FERSTAT register are readable and only writable to clear the flag.

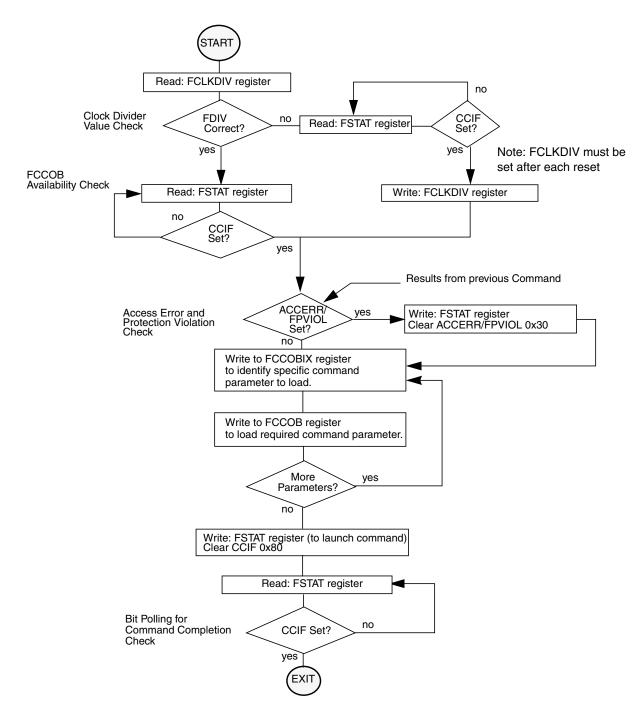

Figure 26-26. Generic Flash Command Write Sequence Flowchart

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 010         | н    | Data 0 [15:8]                             |

| 010         | LO   | Data 0 [7:0]                              |

| 011         | н    | Data 1 [15:8]                             |

| 011         | LO   | Data 1 [7:0]                              |

| 100         | Н    | Data 2 [15:8]                             |

| 100         | LO   | Data 2 [7:0]                              |

| 101         | н    | Data 3 [15:8]                             |

| 101         | LO   | Data 3 [7:0]                              |

Table 28-24. FCCOB - NVM Command Mode (Typical Usage)

### 28.3.2.12 Flash Reserved1 Register (FRSV1)

This Flash register is reserved for factory testing.

Offset Module Base + 0x000C

Offset Module Base + 0x000D

Figure 28-18. Flash Reserved1 Register (FRSV1)

All bits in the FRSV1 register read 0 and are not writable.

# 28.3.2.13 Flash Reserved2 Register (FRSV2)

This Flash register is reserved for factory testing.

Figure 28-19. Flash Reserved2 Register (FRSV2)

All bits in the FRSV2 register read 0 and are not writable.

### 28.3.2.14 Flash Reserved3 Register (FRSV3)

This Flash register is reserved for factory testing.

#### tyte Flash Module (S12FTMRG96K1V1)

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see Section 28.3.2.2), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in Section 28.4.6.11

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0x3\_FF0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0x3\_FF00-0x3\_FF07 are unaffected by the Verify Backdoor Access Key command sequence. The Verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0x3\_FF00-0x3\_FF07 in the Flash configuration field.

# 28.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode by using the following method to erase the P-Flash and EEPROM memory:

- 1. Reset the MCU into special single chip mode

- 2. Delay while the BDM executes the Erase Verify All Blocks command write sequence to check if the P-Flash and EEPROM memories are erased

- 3. Send BDM commands to disable protection in the P-Flash and EEPROM memory

- 4. Execute the Erase All Blocks command write sequence to erase the P-Flash and EEPROM memory. Alternatively the Unsecure Flash command can be executed, if so the steps 5 and 6 below are skeeped.

- 5. After the CCIF flag sets to indicate that the Erase All Blocks operation has completed, reset the MCU into special single chip mode

- 6. Delay while the BDM executes the Erase Verify All Blocks command write sequence to verify that the P-Flash and EEPROM memory are erased

If the P-Flash and EEPROM memory are verified as erased, the MCU will be unsecured. All BDM commands will now be enabled and the Flash security byte may be programmed to the unsecure state by continuing with the following steps:

7. Send BDM commands to execute the Program P-Flash command write sequence to program the Flash security byte to the unsecured state

NP

Table 31-4). The Verify Backdoor Access Key command must not be executed from the Flash block containing the backdoor comparison key to avoid code runaway.

| CCOBIX[2:0] | FCCOB Parameters |              |  |

|-------------|------------------|--------------|--|

| 000         | 0x0C             | Not required |  |

| 001         | Ke               | y 0          |  |

| 010         | Key 1            |              |  |

| 011         | Ke               | y 2          |  |

| 100         | Ke               | y 3          |  |

Table 31-52. Verify Backdoor Access Key Command FCCOB Requirements

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash configuration field with Key 0 compared to 0x3\_FF00, etc. If the backdoor keys match, security will be released. If the backdoor keys do not match, security is not released and all future attempts to execute the Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is set after the Verify Backdoor Access Key operation has completed.

Table 31-53. Verify Backdoor Access Key Command Error Handling

| Register | Error Bit | Error Condition                                                                          |  |  |

|----------|-----------|------------------------------------------------------------------------------------------|--|--|

|          |           | Set if CCOBIX[2:0] != 100 at command launch                                              |  |  |

|          |           | Set if an incorrect backdoor key is supplied                                             |  |  |

|          | ACCERR    | Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see Section 31.3.2.2) |  |  |

| FSTAT    |           | Set if the backdoor key has mismatched since the last reset                              |  |  |

|          | FPVIOL    | None                                                                                     |  |  |

|          | MGSTAT1   | None                                                                                     |  |  |

|          | MGSTAT0   | None                                                                                     |  |  |

### 31.4.6.12 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read operations of the P-Flash or EEPROM block.

| Table 31-54. Set User Margin Level Command FCCOB Requirements |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| CCOBIX[2:0] | FCCOB Parameters      |                                                   |

|-------------|-----------------------|---------------------------------------------------|

| 000         | 0x0D                  | Flash block selection code [1:0]. See Table 31-34 |

| 001         | Margin level setting. |                                                   |