# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 12V1                                                                  |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 25MHz                                                                 |

| Connectivity               | CANbus, IrDA, LINbus, SCI, SPI                                        |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 54                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | 4K x 8                                                                |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.13V ~ 5.5V                                                          |

| Data Converters            | A/D 12x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | 64-LQFP (10x10)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s9s12g128avlh |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 9 Security (S12XS9SECV2)

| 9.1 | Introduc | ction                                    | . 347 |

|-----|----------|------------------------------------------|-------|

|     | 9.1.1    | Features                                 | . 347 |

|     | 9.1.2    | Modes of Operation                       | . 347 |

|     | 9.1.3    | Securing the Microcontroller             | . 348 |

|     | 9.1.4    | Operation of the Secured Microcontroller | . 349 |

|     | 9.1.5    | Unsecuring the Microcontroller           | . 350 |

|     | 9.1.6    | Reprogramming the Security Bits          | . 350 |

|     | 9.1.7    | Complete Memory Erase (Special Modes)    | . 351 |

# Chapter 10

# S12 Clock, Reset and Power Management Unit (S12CPMU)

| 10.1 | Introduction                                               |  |

|------|------------------------------------------------------------|--|

|      | 10.1.1 Features                                            |  |

|      | 10.1.2 Modes of Operation                                  |  |

|      | 10.1.3 S12CPMU Block Diagram                               |  |

| 10.2 | Signal Description                                         |  |

|      | 10.2.1 <b>RESET</b>                                        |  |

|      | 10.2.2 EXTAL and XTAL                                      |  |

|      | 10.2.3 VDDR — Regulator Power Input Pin                    |  |

|      | 10.2.4 VSS — Ground Pin                                    |  |

|      | 10.2.5 VDDA, VSSA — Regulator Reference Supply Pins        |  |

|      | 10.2.6 VDDX, VSSX— Pad Supply Pins                         |  |

|      | 10.2.7 VDD — Internal Regulator Output Supply (Core Logic) |  |

|      | 10.2.8 VDDF — Internal Regulator Output Supply (NVM Logic) |  |

|      | 10.2.9 API_EXTCLK — API external clock output pin          |  |

| 10.3 | Memory Map and Registers                                   |  |

|      | 10.3.1 Module Memory Map                                   |  |

|      | 10.3.2 Register Descriptions                               |  |

| 10.4 | Functional Description                                     |  |

|      | 10.4.1 Phase Locked Loop with Internal Filter (PLL)        |  |

|      | 10.4.2 Startup from Reset                                  |  |

|      | 10.4.3 Stop Mode using PLLCLK as Bus Clock                 |  |

|      | 10.4.4 Full Stop Mode using Oscillator Clock as Bus Clock  |  |

|      | 10.4.5 External Oscillator                                 |  |

|      | 10.4.6 System Clock Configurations                         |  |

| 10.5 | Resets                                                     |  |

|      | 10.5.1 General                                             |  |

|      | 10.5.2 Description of Reset Operation                      |  |

|      | 10.5.3 Power-On Reset (POR)                                |  |

|      | 10.5.4 Low-Voltage Reset (LVR)                             |  |

| 10.6 | Interrupts                                                 |  |

|      | 10.6.1 Description of Interrupt Operation                  |  |

#### e Overview MC9S12G-Family

- Bus-off recovery by software intervention or automatically

- 16-bit time stamp of transmitted/received messages

### 1.3.12 Serial Communication Interface Module (SCI)

- Up to three SCI modules

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 13-bit baud rate selection

- Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wakeup

- Break detect and transmit collision detect supporting LIN 1.3, 2.0, 2.1 and SAE J2602

### **1.3.13** Serial Peripheral Interface Module (SPI)

- Up to three SPI modules

- Configurable 8- or 16-bit data size

- Full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Master or slave mode

- MSB-first or LSB-first shifting

- Serial clock phase and polarity options

# 1.3.14 Analog-to-Digital Converter Module (ADC)

Up to 16-channel, 10-bit/12-bit<sup>1</sup> analog-to-digital converter

- 3 us conversion time

- 8-/10<sup>1</sup>-bit resolution

- Left or right justified result data

- Wakeup from low power modes on analog comparison > or <= match

- Continuous conversion mode

- External triggers to initiate conversions via GPIO or peripheral outputs such as PWM or TIM

- Multiple channel scans

- Precision fixed voltage reference for ADC conversions

- Pins can also be used as digital I/O including wakeup capability

<sup>1. 12-</sup>bit resolution only available on S12GA192 and S12GA240 devices.

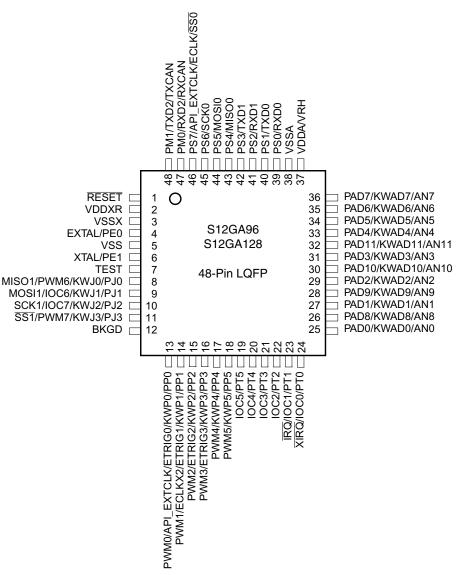

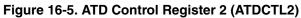

#### 1.8.7 S12GA96 and S12GA128

#### 1.8.7.1 Pinout 48-Pin LQFP

Figure 1-18. 48-Pin LQFP Pinout for S12GA96 and S12GA128

|             | Function<br><lowestpriorityhighest></lowestpriorityhighest> |              |              |             | Power       | Internal P<br>Resisto | -      |                |

|-------------|-------------------------------------------------------------|--------------|--------------|-------------|-------------|-----------------------|--------|----------------|

| Package Pin | Pin                                                         | 2nd<br>Func. | 3rd<br>Func. | 4th<br>Func | 5th<br>Func | Supply                | CTRL   | Reset<br>State |

| 1           | RESET                                                       | _            | —            | _           |             | V <sub>DDX</sub>      | PULLUF | >              |

| Table 1-37. Initial | WCOP | Configuration |

|---------------------|------|---------------|

|---------------------|------|---------------|

| NV[3] in<br>FOPT Register | WCOP in<br>CPMUCOP Register |

|---------------------------|-----------------------------|

| 1                         | 0                           |

| 0                         | 1                           |

### **1.14** Autonomous Clock (ACLK) Configuration

The autonomous clock<sup>1</sup> (ACLK) is not factory trimmed. The reset value of the autonomous clock trimming register<sup>2</sup> (CPMUACLKTR) is 0xFC.

### 1.15 ADC External Trigger Input Connection

The ADC module includes external trigger inputs ETRIG0, ETRIG1, ETRIG2, and ETRIG3. The external trigger allows the user to synchronize ADC conversion to external trigger events. Chapter 2, "Port Integration Module (S12GPIMV1)" describes the connection of the external trigger inputs. Consult the ADC section for information about the analog-to-digital converter module. References to freeze mode are equivalent to active BDM mode.

# 1.16 ADC Special Conversion Channels

Whenever the ADC's Special Channel Conversion Bit (SC) is set, it is capable of running conversion on a number of internal channels (see Table 13-15). Table 1-38 lists the internal reference voltages which are connected to these special conversion channels.

| ADC Channel | Usage                                              |

|-------------|----------------------------------------------------|

| Internal_0  | V <sub>DDF</sub> <sup>1</sup>                      |

| Internal_1  | unused                                             |

| Internal_2  | unused                                             |

| Internal_3  | unused                                             |

| Internal_4  | unused                                             |

| Internal_5  | unused                                             |

|             | unused                                             |

| Internal_6  | Temperature sense of ADC<br>hardmacro <sup>2</sup> |

| Internal_7  | unused                                             |

Table 1-38. Usage of ADC Special Conversion Channels

<sup>1</sup> See Section 1.17, "ADC Result Reference".

<sup>2</sup> The ADC temperature sensor is only available on S12GA192 and S12GA240 devices.

<sup>1.</sup> See Chapter 10, "S12 Clock, Reset and Power Management Unit (S12CPMU)"

<sup>2.</sup> See Section 10.3.2.15, "Autonomous Clock Trimming Register (CPMUACLKTR)"

| Field        | Description                                                                                                                                                                                                                                      |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7<br>PRR0P3  | <b>Pin Routing Register PWM3</b> —Select alternative routing of PWM3 output, ETRIG3 input<br>This bit programs the routing of the PWM3 channel and the ETRIG3 input to a different external pin in 20 TSSOP.<br>See Table 2-47 for more details. |  |

| 6<br>PRR0P2  | <b>Pin Routing Register PWM2</b> —Select alternative routing of PWM2 output, ETRIG2 input<br>This bit programs the routing of the PWM2 channel and the ETRIG2 input to a different external pin in 20 TSSOP.<br>See Table 2-48 for more details. |  |

| 5<br>PRR0T31 |                                                                                                                                                                                                                                                  |  |

| 4<br>PRR0T30 | See Table 2-49 for more details.                                                                                                                                                                                                                 |  |

| 3<br>PRR0T21 | <b>Pin Routing Register IOC2</b> —Select alternative routing of IOC2 output and input<br>Those two bits program the routing of the timer IOC2 channel to different external pins in 20 TSSOP.                                                    |  |

| 2<br>PRR0T20 | See Table 2-50 for more details.                                                                                                                                                                                                                 |  |

| 1<br>PRR0S1  | <b>Pin Routing Register Serial Module</b> —Select alternative routing of SCI0 pins<br>Those bits program the routing of the SCI0 module pins to different external pins in 20 TSSOP.                                                             |  |

| 0<br>PRR0S0  | See Table 2-51 for more details.                                                                                                                                                                                                                 |  |

#### Table 2-46. PRR0 Register Field Descriptions

#### Table 2-47. PWM3/ETRIG3 Routing Options

| PRR0P3 | PWM3/ETRIG3 Associated Pin |  |

|--------|----------------------------|--|

| 0      | PS7 - PWM3, ETRIG3         |  |

| 1      | PAD5 - PWM3, ETRIG3        |  |

#### Table 2-48. PWM2/ETRIG2 Routing Options

| PRR0P2 | PWM2/ETRIG2 Associated Pin |  |

|--------|----------------------------|--|

| 0      | PS4 - PWM2, ETRIG2         |  |

| 1      | PAD4 - PWM2, ETRIG2        |  |

#### Table 2-49. IOC3 Routing Options

| PRR0T31 | PRR0T30 | IOC3 Associated Pin |

|---------|---------|---------------------|

| 0       | 0       | PS6 - IOC3          |

| 0       | 1       | PE1 - IOC3          |

| 1       | 0       | PAD5 - IOC3         |

| 1       | 1       | Reserved            |

Both interrupts are capable to wake-up the device from stop mode. Means for glitch filtering are not provided on these pins.

#### 2.5.4.2 Pin Interrupts and Wakeup

Ports P, J and AD offer pin interrupt capability. The related interrupt enable (PIE) as well as the sensitivity to rising or falling edges (PPS) can be individually configured on per-pin basis. All bits/pins in a port share the same interrupt vector. Interrupts can be used with the pins configured as inputs or outputs.

An interrupt is generated when a port interrupt flag (PIF) and its corresponding port interrupt enable (PIE) are both set. The pin interrupt feature is also capable to wake up the CPU when it is in stop or wait mode.

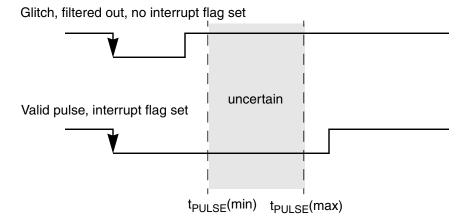

A digital filter on each pin prevents short pulses from generating an interrupt. A valid edge on an input is detected if 4 consecutive samples of a passive level are followed by 4 consecutive samples of an active level. Else the sampling logic is restarted.

In run and wait mode the filters are continuously clocked by the bus clock. Pulses with a duration of  $t_{PULSE} < n_{P\_MASK}/f_{bus}$  are assuredly filtered out while pulses with a duration of  $t_{PULSE} > n_{P\_PASS}/f_{bus}$  guarantee a pin interrupt.

In stop mode the clock is generated by an RC-oscillator. The minimum pulse length varies over process conditions, temperature and voltage (Figure 2-65). Pulses with a duration of  $t_{PULSE} < t_{P\_MASK}$  are assuredly filtered out while pulses with a duration of  $t_{PULSE} > t_{P\_PASS}$  guarantee a wakeup event.

Please refer to the appendix table "Pin Interrupt Characteristics" for pulse length limits.

To maximize current saving the RC oscillator is active only if the following condition is true on any individual pin:

Sample count <= 4 (at active or passive level) and interrupt enabled (PIE=1) and interrupt flag not set (PIF=0).

Figure 2-65. Interrupt Glitch Filter (here: active low level selected)

#### Table 3-3. ACMPS Register Field Descriptions

| Field     | Description                                                                                                                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>ACIF | ACMP Interrupt Flag—<br>ACIF is set when a compare event occurs. Compare events are defined by ACMOD[1:0]. Writing a logic "1" to the<br>bit field clears the flag.<br>0 Compare event has not occurred<br>1 Compare event has occurred |

| 6<br>ACO  | ACMP Output—<br>Reading ACO returns the current value of the synchronized ACMP output. Refer to ACE description to account for initialization delay on this path.                                                                       |

# 3.7 Functional Description

The ACMP compares two analog input voltages applied to ACMPM and ACMPP. The comparator output is high when the voltage at the non-inverting input is greater than the voltage at the inverting input, and is low when the non-inverting input voltage is lower than the inverting input voltage.

The ACMP is enabled with register bit ACMPC[ACE]. When ACMPC[ACE] is set, the input pins are connected to low-pass filters. The comparator output is disconnected from the subsequent logic, which is held at its state for 63 bus clock cycles after setting ACMPC[ACE] to "1" to mask potential glitches. This initialization delay must be accounted for before the first comparison result can be expected.

The initial hold state after reset is zero, thus if input voltages are set to result in "true" result  $(V_{ACMPP} > V_{ACMPM})$  before the initialization delay has passed, a flag will be set immediately after this.

Similarly the flag will also be set when disabling the ACMP, then re-enabling it with the inputs changing to produce an opposite result to the hold state before the end of the initialization delay.

By setting the ACMPC[ACICE] bit the gated comparator output can be connected to the synchronized timer input capture channel 5 (see Figure 3-1). This feature can be used to generate time stamps and timer interrupts on ACMP events.

The comparator output signal synchronized to the bus clock is used to read the comparator output status (ACMPS[ACO]) and to set the interrupt flag (ACMPS[ACIF]).

The condition causing the interrupt flag (ACMPS[ACIF]) to assert is selected with register bits ACMPC[ACMOD1:ACMOD0]. This includes any edge configuration, that is rising, or falling, or rising and falling (toggle) edges of the comparator output. Also flag setting can be disabled.

An interrupt will be generated if the interrupt enable bit (ACMPC[ACIE]) and the interrupt flag (ACMPS[ACIF]) are both set. ACMPS[ACIF] is cleared by writing a 1.

The raw comparator output signal ACMPO can be driven out on an external pin by setting the ACMPC[ACOPE] bit.

### **10.4 Functional Description**

#### 10.4.1 Phase Locked Loop with Internal Filter (PLL)

The PLL is used to generate a high speed PLLCLK based on a low frequency REFCLK.

The REFCLK is by default the IRCCLK which is trimmed to  $f_{IRC1M}$  TRIM=1MHz.

If using the oscillator (OSCE=1) REFCLK will be based on OSCCLK. For increased flexibility, OSCCLK can be divided in a range of 1 to 16 to generate the reference frequency REFCLK using the REFDIV[3:0] bits. Based on the SYNDIV[5:0] bits the PLL generates the VCOCLK by multiplying the reference clock by a 2, 4, 6,... 126, 128. Based on the POSTDIV[4:0] bits the VCOCLK can be divided in a range of 1,2, 3, 4, 5, 6,... to 32 to generate the PLLCLK.

If oscillator is enabled (OSCE=1)  $f_{REF} = \frac{f_{OSC}}{(REFDIV + 1)}$

If oscillator is disabled (OSCE=0)  $f_{REF} = f_{IRC1M}$

$f_{VCO} = 2 \times f_{REF} \times (SYNDIV + 1)$

| If PLL is locked (LOCK=1)     | $f_{PLL} = \frac{f_{VCO}}{(POSTDIV + 1)}$ |

|-------------------------------|-------------------------------------------|

| If PLL is not locked (LOCK=0) | $f_{PLL} = \frac{f_{VCO}}{4}$             |

| If PLL is selected (PLLSEL=1) | $f_{bus} = \frac{f_{PLL}}{2}$             |

#### NOTE

Although it is possible to set the dividers to command a very high clock frequency, do not exceed the specified bus frequency limit for the MCU.

Several examples of PLL divider settings are shown in Table 10-25. The following rules help to achieve optimum stability and shortest lock time:

- Use lowest possible  $f_{VCO} / f_{REF}$  ratio (SYNDIV value).

- Use highest possible REFCLK frequency f<sub>REF</sub>.

#### Table 10-25. Examples of PLL Divider Settings

| f <sub>osc</sub> | REFDIV[3:<br>0] | f <sub>REF</sub> | REFFRQ[1:0] | SYNDIV[5:0] | f <sub>vco</sub> | VCOFRQ[1:0] | POSTDIV<br>[4:0] | f <sub>PLL</sub> | f <sub>bus</sub> |

|------------------|-----------------|------------------|-------------|-------------|------------------|-------------|------------------|------------------|------------------|

| off              | \$00            | 1MHz             | 00          | \$18        | 50MHz            | 01          | \$03             | 12.5MHz          | 6.25MHz          |

| ETRIGSEL | ETRIGCH3 | ETRIGCH2 | ETRIGCH1 | ETRIGCH0 | External trigger source is |

|----------|----------|----------|----------|----------|----------------------------|

| 0        | 0        | 0        | 0        | 0        | ANO                        |

| 0        | 0        | 0        | 0        | 1        | AN1                        |

| 0        | 0        | 0        | 1        | 0        | AN2                        |

| 0        | 0        | 0        | 1        | 1        | AN3                        |

| 0        | 0        | 1        | 0        | 0        | AN4                        |

| 0        | 0        | 1        | 0        | 1        | AN5                        |

| 0        | 0        | 1        | 1        | 0        | AN6                        |

| 0        | 0        | 1        | 1        | 1        | AN7                        |

| 0        | 1        | 0        | 0        | 0        | AN8                        |

| 0        | 1        | 0        | 0        | 1        | AN9                        |

| 0        | 1        | 0        | 1        | 0        | AN10                       |

| 0        | 1        | 0        | 1        | 1        | AN11                       |

| 0        | 1        | 1        | 0        | 0        | AN12                       |

| 0        | 1        | 1        | 0        | 1        | AN13                       |

| 0        | 1        | 1        | 1        | 0        | AN14                       |

| 0        | 1        | 1        | 1        | 1        | AN15                       |

| 1        | 0        | 0        | 0        | 0        | ETRIG0 <sup>1</sup>        |

| 1        | 0        | 0        | 0        | 1        | ETRIG1 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 0        | ETRIG2 <sup>1</sup>        |

| 1        | 0        | 0        | 1        | 1        | ETRIG3 <sup>1</sup>        |

| 1        | 0        | 1        | Х        | Х        | Reserved                   |

| 1        | 1        | Х        | Х        | Х        | Reserved                   |

Table 16-5. External Trigger Channel Select Coding

<sup>1</sup> Only if ETRIG3-0 input option is available (see device specification), else ETRISEL is ignored, that means external trigger source is still on one of the AD channels selected by ETRIGCH3-0

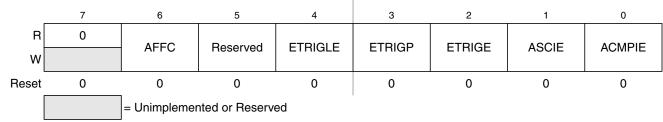

### 16.3.2.3 ATD Control Register 2 (ATDCTL2)

Writes to this register will abort current conversion sequence.

Module Base + 0x0002

Read: Anytime

Write: Anytime

# 19.3 Memory Map and Register Definition

### 19.3.1 Module Memory Map

This section describes the content of the registers in the scalable PWM module. The base address of the scalable PWM module is determined at the MCU level when the MCU is defined. The register decode map is fixed and begins at the first address of the module address offset. The figure below shows the registers associated with the scalable PWM and their relative offset from the base address. The register detail description follows the order they appear in the register map.

Reserved bits within a register will always read as 0 and the write will be unimplemented. Unimplemented functions are indicated by shading the bit.

#### NOTE

Register Address = Base Address + Address Offset, where the Base Address is defined at the MCU level and the Address Offset is defined at the module level.

### 19.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the scalable PWM module.

| Register<br>Name                |        | Bit 7   | 6                           | 5       | 4       | 3       | 2       | 1       | Bit 0   |

|---------------------------------|--------|---------|-----------------------------|---------|---------|---------|---------|---------|---------|

| 0x0000<br>PWME <sup>1</sup>     | R<br>W | PWME7   | PWME6                       | PWME5   | PWME4   | PWME3   | PWME2   | PWME1   | PWME0   |

| 0x0001<br>PWMPOL <sup>1</sup>   | R<br>W | PPOL7   | PPOL6                       | PPOL5   | PPOL4   | PPOL3   | PPOL2   | PPOL1   | PPOL0   |

| 0x0002<br>PWMCLK <sup>1</sup>   | R<br>W | PCLK7   | PCLKL6                      | PCLK5   | PCLK4   | PCLK3   | PCLK2   | PCLK1   | PCLK0   |

| 0x0003<br>PWMPRCLK              | R<br>W | 0       | PCKB2                       | PCKB1   | PCKB0   | 0       | PCKA2   | PCKA1   | PCKA0   |

| 0x0004<br>PWMCAE <sup>1</sup>   | R<br>W | CAE7    | CAE6                        | CAE5    | CAE4    | CAE3    | CAE2    | CAE1    | CAE0    |

| 0x0005<br>PWMCTL <sup>1</sup>   | R<br>W | CON67   | CON45                       | CON23   | CON01   | PSWAI   | PFRZ    | 0       | 0       |

| 0x0006<br>PWMCLKAB <sup>1</sup> | R<br>W | PCLKAB7 | PCLKAB6                     | PCLKAB5 | PCLKAB4 | PCLKAB3 | PCLKAB2 | PCLKAB1 | PCLKAB0 |

|                                 | ſ      |         | = Unimplemented or Reserved |         |         |         |         |         |         |

#### Figure 19-2. The scalable PWM Register Summary (Sheet 1 of 4)

## 23.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

| Register<br>Name                        |        | Bit 7  | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |

|-----------------------------------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x0000<br>TIOS                          | R<br>W | IOS7   | IOS6   | IOS5   | IOS4   | IOS3   | IOS2   | IOS1  | IOS0  |

| 0x0001                                  | R      | 0      | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| CFORC                                   | W      | FOC7   | FOC6   | FOC5   | FOC4   | FOC3   | FOC2   | FOC1  | FOC0  |

| 0x0002<br>OC7M                          | R<br>W | OC7M7  | OC7M6  | OC7M5  | OC7M4  | OC7M3  | OC7M2  | OC7M1 | OC7M0 |

| 0x0003<br>OC7D                          | R<br>W | OC7D7  | OC7D6  | OC7D5  | OC7D4  | OC7D3  | OC7D2  | OC7D1 | OC7D0 |

| 0x0004<br>TCNTH                         | R<br>W | TCNT15 | TCNT14 | TCNT13 | TCNT12 | TCNT11 | TCNT10 | TCNT9 | TCNT8 |

| 0x0005<br>TCNTL                         | R<br>W | TCNT7  | TCNT6  | TCNT5  | TCNT4  | TCNT3  | TCNT2  | TCNT1 | TCNT0 |

| 0x0006<br>TSCR1                         | R<br>W | TEN    | TSWAI  | TSFRZ  | TFFCA  | PRNT   | 0      | 0     | 0     |

| 0x0007<br>TTOV                          | R<br>W | TOV7   | TOV6   | TOV5   | TOV4   | TOV3   | TOV2   | TOV1  | TOV0  |

| 0x0008<br>TCTL1                         | R<br>W | OM7    | OL7    | OM6    | OL6    | OM5    | OL5    | OM4   | OL4   |

| 0x0009<br>TCTL2                         | R<br>W | OM3    | OL3    | OM2    | OL2    | OM1    | OL1    | OM0   | OL0   |

| 0x000A<br>TCTL3                         | R<br>W | EDG7B  | EDG7A  | EDG6B  | EDG6A  | EDG5B  | EDG5A  | EDG4B | EDG4A |

| 0x000B<br>TCTL4                         | R<br>W | EDG3B  | EDG3A  | EDG2B  | EDG2A  | EDG1B  | EDG1A  | EDG0B | EDG0A |

| 0x000C<br>TIE                           | R<br>W | C7I    | C6I    | C5I    | C4I    | C3I    | C2I    | C1I   | C0I   |

| 0x000D<br>TSCR2                         | R<br>W | TOI    | 0      | 0      | 0      | TCRE   | PR2    | PR1   | PR0   |

| 0x000E<br>TFLG1                         | R<br>W | C7F    | C6F    | C5F    | C4F    | C3F    | C2F    | C1F   | C0F   |

| 0x000F<br>TFLG2                         | R<br>W | TOF    | 0      | 0      | 0      | 0      | 0      | 0     | 0     |

| 0x0010–0x001F<br>TCxH–TCxL <sup>1</sup> | R<br>W | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

|                                         | R<br>W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 0x0020<br>PACTL                         | R<br>W | 0      | PAEN   | PAMOD  | PEDGE  | CLK1   | CLK0   | PAOVI | PAI   |

Only bits related to implemented channels are valid.

Figure 23-5. TIM16B8CV3 Register Summary (Sheet 1 of 2)

### 24.4.4.3 Valid Flash Module Commands

Table 24-25 present the valid Flash commands, as enabled by the combination of the functional MCU mode (Normal SingleChip NS, Special Singlechip SS) with the MCU security state (Unsecured, Secured).

Special Singlechip mode is selected by input mmc\_ss\_mode\_ts2 asserted. MCU Secured state is selected by input mmc\_secure input asserted.

| ECMD | Command                      | Unse            | cured           | Secured         |                 |

|------|------------------------------|-----------------|-----------------|-----------------|-----------------|

| FCMD | Command                      | NS <sup>1</sup> | SS <sup>2</sup> | NS <sup>3</sup> | SS <sup>4</sup> |

| 0x01 | Erase Verify All Blocks      | *               | *               | *               | *               |

| 0x02 | Erase Verify Block           | *               | *               | *               | *               |

| 0x03 | Erase Verify P-Flash Section | *               | *               | *               |                 |

| 0x04 | Read Once                    | *               | *               | *               |                 |

| 0x06 | Program P-Flash              | *               | *               | *               |                 |

| 0x07 | Program Once                 | *               | *               | *               |                 |

| 0x08 | Erase All Blocks             |                 | *               |                 | *               |

| 0x09 | Erase Flash Block            | *               | *               | *               |                 |

| 0x0A | Erase P-Flash Sector         | *               | *               | *               |                 |

| 0x0B | Unsecure Flash               |                 | *               |                 | *               |

| 0x0C | Verify Backdoor Access Key   | *               |                 | *               |                 |

| 0x0D | Set User Margin Level        | *               | *               | *               |                 |

| 0x0E | Set Field Margin Level       |                 | *               |                 |                 |

| 0x10 | Erase Verify EEPROM Section  | *               | *               | *               |                 |

| 0x11 | Program EEPROM               | *               | *               | *               |                 |

| 0x12 | Erase EEPROM Sector          | *               | *               | *               |                 |

Table 24-25. Flash Commands by Mode and Security State

<sup>1</sup> Unsecured Normal Single Chip mode

<sup>2</sup> Unsecured Special Single Chip mode.

<sup>3</sup> Secured Normal Single Chip mode.

<sup>4</sup> Secured Special Single Chip mode.

#### 24.4.4.4 P-Flash Commands

Table 24-26 summarizes the valid P-Flash commands along with the effects of the commands on the P-Flash block and other resources within the Flash module.

| FCMD | Command                    | Function on P-Flash Memory                              |

|------|----------------------------|---------------------------------------------------------|

| 0x01 | Erase Verify All<br>Blocks | Verify that all P-Flash (and EEPROM) blocks are erased. |

#### Table 24-26. P-Flash Commands

N

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDIF | <ul> <li>Double Bit Fault Detect Interrupt Flag — The setting of the DFDIF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The DFDIF flag is cleared by writing a 1 to DFDIF. Writing a 0 to DFDIF has no effect on DFDIF.<sup>2</sup></li> <li>No double bit fault detected</li> <li>Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running</li> </ul>                                                                            |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>1</sup> The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or a Flash array read operation returning invalid data was attempted operation returning invalid data was attempted operation.</li> </ul> |

#### Table 26-16. FERSTAT Field Descriptions

<sup>1</sup> The single bit fault and double bit fault flags are mutually exclusive for parity errors (an ECC fault occurrence can be either single fault or double fault but never both). A simultaneous access collision (Flash array read operation returning invalid data attempted while command running) is indicated when both SFDIF and DFDIF flags are high.

<sup>2</sup> There is a one cycle delay in storing the ECC DFDIF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

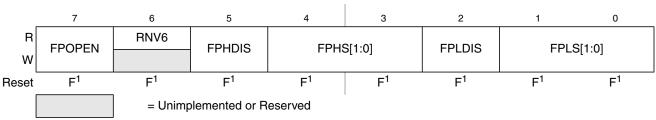

### 26.3.2.9 P-Flash Protection Register (FPROT)

The FPROT register defines which P-Flash sectors are protected against program and erase operations.

Offset Module Base + 0x0008

<sup>1</sup> Loaded from IFR Flash configuration field, during reset sequence.

The (unreserved) bits of the FPROT register are writable with the restriction that the size of the protected region can only be increased (see Section 26.3.2.9.1, "P-Flash Protection Restrictions," and Table 26-21).

During the reset sequence, the FPROT register is loaded with the contents of the P-Flash protection byte in the Flash configuration field at global address 0x3\_FF0C located in P-Flash memory (see Table 26-4) as indicated by reset condition 'F' in Figure 26-13. To change the P-Flash protection that will be loaded during the reset sequence, the upper sector of the P-Flash memory must be unprotected, then the P-Flash protection byte must be reprogrammed. If a double bit fault is detected while reading the P-Flash phrase containing the P-Flash protection byte during the reset sequence, the FPOPEN bit will be cleared and remaining bits in the FPROT register will be set to leave the P-Flash memory fully protected.

8. Reset the MCU

# 26.5.3 Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 26-27.

# 26.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and EEPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module in a fully protected and secured state if errors are encountered during execution of the reset sequence. If a double bit fault is detected during the reset sequence, both MGSTAT bits in the FSTAT register will be set.

CCIF is cleared throughout the initialization sequence. The Flash module holds off all CPU access for a portion of the initialization sequence. Flash reads are allowed once the hold is removed. Completion of the initialization sequence is marked by setting CCIF high which enables user commands.

If a reset occurs while any Flash command is in progress, that command will be immediately aborted. The state of the word being programmed or the sector/block being erased is not guaranteed.

### 30.4.6.15 Program EEPROM Command

The Program EEPROM operation programs one to four previously erased words in the EEPROM block. The Program EEPROM operation will confirm that the targeted location(s) were successfully programmed upon completion.

#### CAUTION

A Flash word must be in the erased state before being programmed. Cumulative programming of bits within a Flash word is not allowed.

| CCOBIX[2:0] | FCCOB Parameters                               |                                                     |  |  |  |  |

|-------------|------------------------------------------------|-----------------------------------------------------|--|--|--|--|

| 000         | 0x11                                           | Global address [17:16] to identify the EEPROM block |  |  |  |  |

| 001         | Global address [15:0] of word to be programmed |                                                     |  |  |  |  |

| 010         | Word 0 program value                           |                                                     |  |  |  |  |

| 011         | Word 1 program value, if desired               |                                                     |  |  |  |  |

| 100         | Word 2 program value, if desired               |                                                     |  |  |  |  |

| 101         | Word 3 program value, if desired               |                                                     |  |  |  |  |

Upon clearing CCIF to launch the Program EEPROM command, the user-supplied words will be transferred to the Memory Controller and be programmed if the area is unprotected. The CCOBIX index value at Program EEPROM command launch determines how many words will be programmed in the EEPROM block. The CCIF flag is set when the operation has completed.

| Table | 30-63. | Program | EEPROM | Command | Error Har | ndlina |

|-------|--------|---------|--------|---------|-----------|--------|

|       |        |         |        | ••••••  |           |        |

| Register | Error Bit | Error Condition                                                                                                                                                                                                                                                                                                           |  |  |  |

|----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                                                                                                                                                                                                                                                                |  |  |  |

|          |           |                                                                                                                                                                                                                                                                                                                           |  |  |  |

|          | ACCERR    | Set if CCOBIX[2:0] > 101 at command launch<br>Set if command not available in current mode (see Table 30-27)<br>Set if an invalid global address [17:0] is supplied<br>Set if a misaligned word address is supplied (global address [0] != 0)<br>Set if the requested group of words breaches the end of the EEPROM block |  |  |  |

|          | ACCENN    | Set if an invalid global address [17:0] is supplied                                                                                                                                                                                                                                                                       |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)                                                                                                                                                                                                                                                    |  |  |  |

|          |           |                                                                                                                                                                                                                                                                                                                           |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                                                                                                                                                                                                                                                                |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                                                                                                                                                                                                                                                       |  |  |  |

|          | MGSTAT0   | ,                                                                                                                                                                                                                                                                                                                         |  |  |  |

### 30.4.6.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

P-Flash memory (see Table 31-4) as indicated by reset condition F in Table 31-23. To change the EEPROM protection that will be loaded during the reset sequence, the P-Flash sector containing the EEPROM protection byte must be unprotected, then the EEPROM protection byte must be programmed. If a double bit fault is detected while reading the P-Flash phrase containing the EEPROM protection byte during the reset sequence, the DPOPEN bit will be cleared and DPS bits will be set to leave the EEPROM memory fully protected.

Trying to alter data in any protected area in the EEPROM memory will result in a protection violation error and the FPVIOL bit will be set in the FSTAT register. Block erase of the EEPROM memory is not possible if any of the EEPROM sectors are protected.

| Field           | Description                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DPOPEN     | <ul> <li>EEPROM Protection Control</li> <li>Enables EEPROM memory protection from program and erase with protected address range defined by DPS bits</li> <li>Disables EEPROM memory protection from program and erase</li> </ul> |

| 6–0<br>DPS[6:0] | <b>EEPROM Protection Size</b> — The DPS[6:0] bits determine the size of the protected area in the EEPROM memory, this size increase in step of 32 bytes, as shown in Table 31-23.                                                 |

| Table 31-22. | EEPROT | Field | Descriptions |

|--------------|--------|-------|--------------|

|--------------|--------|-------|--------------|

#### Table 31-23. EEPROM Protection Address Range

| DPS[6:0]                                                                                         | Global Address Range        | Protected Size |  |  |  |

|--------------------------------------------------------------------------------------------------|-----------------------------|----------------|--|--|--|

| 0000000                                                                                          | 0000000 0x0_0400 – 0x0_041F |                |  |  |  |

| 0000001                                                                                          | 0x0_0400 - 0x0_043F         | 64 bytes       |  |  |  |

| 0000010                                                                                          | 0x0_0400 - 0x0_045F         | 96 bytes       |  |  |  |

| 0000011                                                                                          | 0x0_0400 – 0x0_047F         | 128 bytes      |  |  |  |

| 0000100                                                                                          | 0x0_0400 - 0x0_049F         | 160 bytes      |  |  |  |

| 0000101                                                                                          | 0x0_0400 - 0x0_04BF         | 192 bytes      |  |  |  |

| The Protection Size goes on enlarging in step of 32 bytes, for each DPS value increasing of one. |                             |                |  |  |  |

| 1111111                                                                                          | 1111111 0x0_0400 – 0x0_13FF |                |  |  |  |

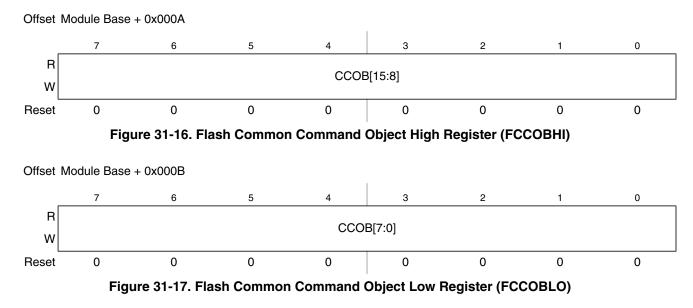

The FCCOB is an array of six words addressed via the CCOBIX index found in the FCCOBIX register. Byte wide reads and writes are allowed to the FCCOB register.

#### 31.3.2.11.1 FCCOB - NVM Command Mode

NVM command mode uses the indexed FCCOB register to provide a command code and its relevant parameters to the Memory Controller. The user first sets up all required FCCOB fields and then initiates the command's execution by writing a 1 to the CCIF bit in the FSTAT register (a 1 written by the user clears the CCIF command completion flag to 0). When the user clears the CCIF bit in the FSTAT register all FCCOB parameter fields are locked and cannot be changed by the user until the command completes (as evidenced by the Memory Controller returning CCIF to 1). Some commands return information to the FCCOB register array.

The generic format for the FCCOB parameter fields in NVM command mode is shown in Table 31-24. The return values are available for reading after the CCIF flag in the FSTAT register has been returned to 1 by the Memory Controller. Writes to the unimplemented parameter fields (CCOBIX = 110 and CCOBIX = 111) are ignored with reads from these fields returning 0x0000.

Table 31-24 shows the generic Flash command format. The high byte of the first word in the CCOB array contains the command code, followed by the parameters for this specific Flash command. For details on the FCCOB settings required by each command, see the Flash command descriptions in Section 31.4.6.

| CCOBIX[2:0] | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|------|-------------------------------------------|

| 000         | н    | FCMD[7:0] defining Flash command          |

| 000         | LO   | 6'h0, Global address [17:16]              |

| 001         | HI   | Global address [15:8]                     |

|             | LO   | Global address [7:0]                      |

Table 31-24. FCCOB - NVM Command Mode (Typical Usage)

| Table 31-64 | . Erase E | EPROM Sector | Command | I FCCOB | Requirements |

|-------------|-----------|--------------|---------|---------|--------------|

|-------------|-----------|--------------|---------|---------|--------------|

| CCOBIX[2:0] | FCCOB                                                                                                          | Parameters                                         |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|

| 000         | 0x12                                                                                                           | Global address [17:16] to identify<br>EEPROM block |  |  |

| 001         | Global address [15:0] anywhere within the sector to be erased.<br>See Section 31.1.2.2 for EEPROM sector size. |                                                    |  |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          | ACCERR    | Set if command not available in current mode (see Table 31-27)                      |

|          | ACCENN    | Set if an invalid global address [17:0] is suppliedsee Table 31-3)                  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 31-65. Erase EEPROM Sector Command Error Handling

### 31.4.7 Interrupts

The Flash module can generate an interrupt when a Flash command operation has completed or when a Flash command operation has detected an ECC fault.

| Table 31-66 | Flash | Interrupt | Sources |

|-------------|-------|-----------|---------|

|-------------|-------|-----------|---------|

| Interrupt Source                   | Interrupt Flag              | Local Enable                | Global (CCR)<br>Mask |

|------------------------------------|-----------------------------|-----------------------------|----------------------|

| Flash Command Complete             | CCIF<br>(FSTAT register)    | CCIE<br>(FCNFG register)    | I Bit                |

| ECC Double Bit Fault on Flash Read | DFDIF<br>(FERSTAT register) | DFDIE<br>(FERCNFG register) | I Bit                |

| ECC Single Bit Fault on Flash Read | SFDIF<br>(FERSTAT register) | SFDIE<br>(FERCNFG register) | I Bit                |

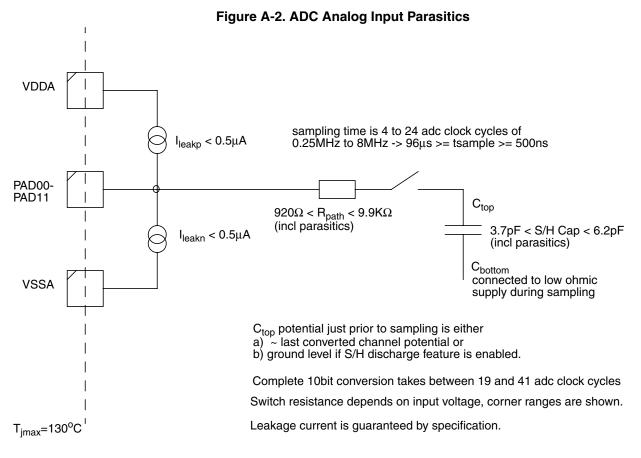

### A.4.3.2 ADC Analog Input Parasitics

### A.4.4 ADC Temperature Sensor

Table A-30. ADC Temperature Sensor

| N | lum | С | Rating                   | Symbol           | Min  | Тур  | Мах  | Unit  |

|---|-----|---|--------------------------|------------------|------|------|------|-------|

|   | 1   | Т | Temperature Sensor Slope | dV <sub>TS</sub> | -4.0 | -3.8 | -3.6 | mV/°C |

# A.5 ACMP Characteristics

This section describes the electrical characteristics of the analog comparator.