Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                            |

|----------------------------|------------------------------------------------------------|

| Product Status             | Active                                                     |

| Core Processor             | 56800EX                                                    |

| Core Size                  | 32-Bit Single-Core                                         |

| Speed                      | 100MHz                                                     |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                 |

| Peripherals                | DMA, POR, PWM, WDT                                         |

| Number of I/O              | 26                                                         |

| Program Memory Size        | 32KB (16K x 16)                                            |

| Program Memory Type        | FLASH                                                      |

| EEPROM Size                | -                                                          |

| RAM Size                   | 3K x 16                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                |

| Data Converters            | A/D 6x12b; D/A 2x12b                                       |

| Oscillator Type            | Internal                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                         |

| Mounting Type              | Surface Mount                                              |

| Package / Case             | 32-LQFP                                                    |

| Supplier Device Package    | 32-LQFP (7x7)                                              |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc56f82723vlc |

|                            |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1 | Over     | view                                                    | 4    |

|---|----------|---------------------------------------------------------|------|

|   | 1.1      | MC56F827xx Product Family                               | 4    |

|   | 1.2      | 56800EX 32-bit Digital Signal Controller (DSC) core     | 5    |

|   | 1.3      | Operation Parameters                                    | .6   |

|   | 1.4      | On-Chip Memory and Memory Protection                    | .6   |

|   | 1.5      | Interrupt Controller                                    | . 7  |

|   | 1.6      | Peripheral highlights                                   | . 7  |

|   | 1.7      | Block diagrams                                          | 13   |

| 2 | MC5      | 6F827xx signal and pin descriptions                     | 16   |

|   | 2.1      | Signal groups                                           | 25   |

| 3 | Order    | ring parts                                              | 25   |

|   | 3.1      | Determining valid orderable parts                       | 25   |

| 4 | Part i   | dentification                                           | 25   |

|   | 4.1      | Description                                             | . 26 |

|   | 4.2      | Format                                                  | . 26 |

|   | 4.3      | Fields                                                  | . 26 |

|   | 4.4      | Example                                                 | 26   |

| 5 | Term     | inology and guidelines                                  | 27   |

|   | 5.1      | Definition: Operating requirement                       | . 27 |

|   | 5.2      | Definition: Operating behavior                          | . 27 |

|   | 5.3      | Definition: Attribute                                   | 27   |

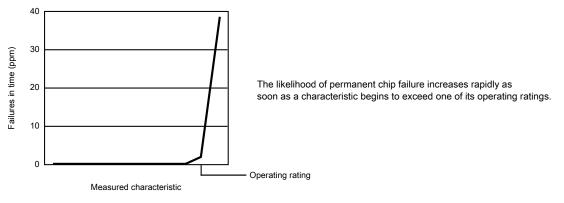

|   | 5.4      | Definition: Rating                                      | 28   |

|   | 5.5      | Result of exceeding a rating                            | . 28 |

|   | 5.6      | Relationship between ratings and operating requirements | 28   |

|   | 5.7      | Guidelines for ratings and operating requirements       | . 29 |

|   | 5.8      | Definition: Typical value                               | . 29 |

|   | 5.9      | Typical value conditions                                | . 30 |

| 6 | <b>D</b> | gs                                                      | 31   |

|    | 6.1    | Thermal handling ratings                   |

|----|--------|--------------------------------------------|

|    | 6.2    | Moisture handling ratings                  |

|    | 6.3    | ESD handling ratings                       |

|    | 6.4    | Voltage and current operating ratings      |

| 7  | Gener  | ral                                        |

|    | 7.1    | General characteristics                    |

|    | 7.2    | AC electrical characteristics              |

|    | 7.3    | Nonswitching electrical specifications35   |

|    | 7.4    | Switching specifications41                 |

|    | 7.5    | Thermal specifications                     |

| 8  | Periph | neral operating requirements and behaviors |

|    | 8.1    | Core modules                               |

|    | 8.2    | System modules45                           |

|    | 8.3    | Clock modules                              |

|    | 8.4    | Memories and memory interfaces             |

|    | 8.5    | Analog                                     |

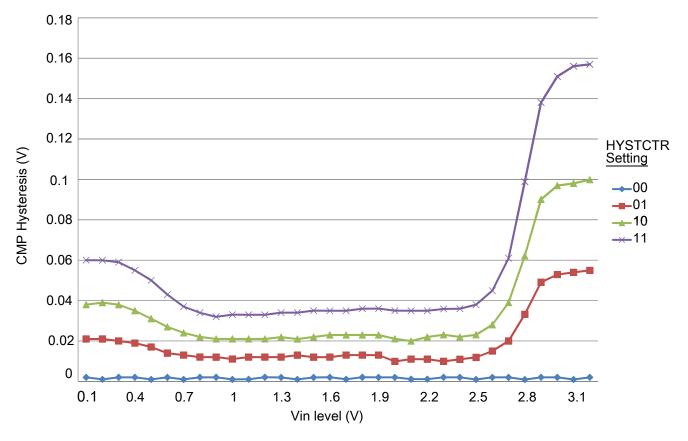

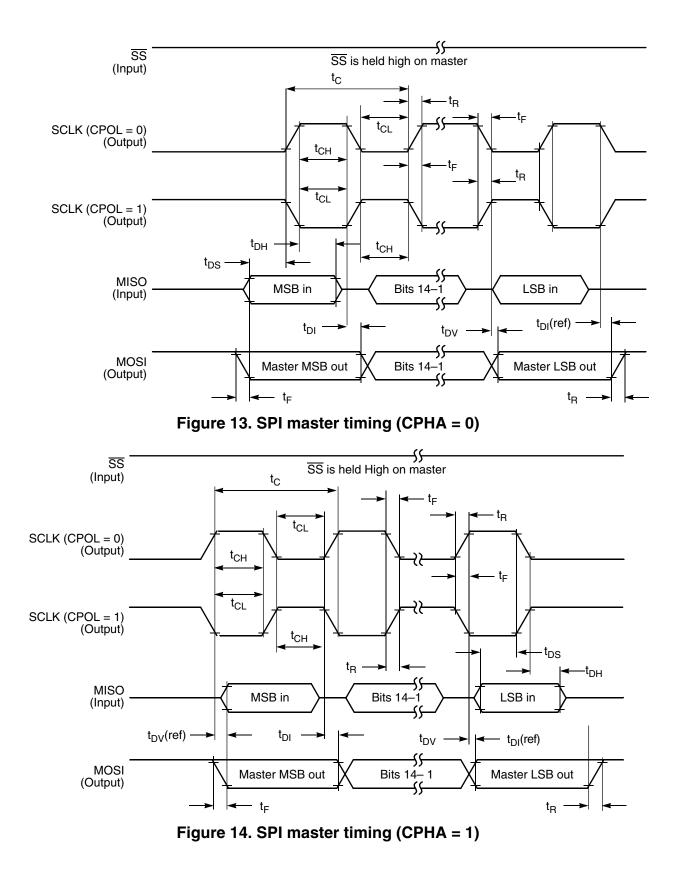

|    | 8.6    | PWMs and timers                            |

|    | 8.7    | Communication interfaces                   |

| 9  | Desig  | n Considerations                           |

|    | 9.1    | Thermal design considerations              |

|    | 9.2    | Electrical design considerations           |

|    | 9.3    | Power-on Reset design considerations       |

| 10 | Obtain | ning package dimensions                    |

| 11 | Pinou  | t                                          |

|    | 11.1   | Signal Multiplexing and Pin Assignments    |

|    | 11.2   | Pinout diagrams71                          |

| 12 | Produ  | ct documentation                           |

| 13 | Revis  | ion History74                              |

## 1 Overview

## 1.1 MC56F827xx Product Family

The following table is the comparsion of features among members of the family.

| Feature                                              |            |            |            |            |            | MC5        | 6F82       |            |            |            |            |            |

|------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Part Number <sup>1</sup>                             | 748V<br>LH | 746V<br>LF | 743V<br>LC | 743V<br>FM | 738V<br>LH | 736V<br>LF | 733V<br>LC | 733V<br>FM | 728V<br>LH | 726V<br>LF | 723V<br>LC | 723V<br>FM |

|                                                      |            | 746M<br>LF |            |            |            |            |            | 733M<br>FM |            |            |            |            |

| Core frequency<br>(MHz)                              | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     |

| Flash memory<br>(KB)                                 | 64         | 64         | 64         | 64         | 48         | 48         | 48         | 48         | 32         | 32         | 32         | 32         |

| RAM (KB)                                             | 8          | 8          | 8          | 8          | 8          | 8          | 8          | 8          | 6          | 6          | 6          | 6          |

| Interrupt<br>Controller                              | Yes        |

| Windowed<br>Computer<br>Operating<br>Properly (WCOP) | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| External<br>Watchdog Monitor<br>(EWM)                | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| Periodic Interrupt<br>Timer (PIT)                    | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          |

| Cyclic<br>Redundancy<br>Check (CRC)                  | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| Quad Timer<br>(TMR)                                  | 1x4        |

| 12-bit Cyclic ADC channels                           | 2x8        | 2x5        | 2x3        | 2x3        | 2x8        | 2x5        | 2x3        | 2x3        | 2x8        | 2x5        | 2x3        | 2x3        |

| PWM Module:                                          |            |            |            |            |            |            |            |            |            |            |            |            |

| Input capture<br>channels <sup>2</sup>               | 12         | 6          | 6          | 6          | 12         | 6          | 6          | 6          | 12         | 6          | 6          | 6          |

| High-resolution channels                             | 8          | 6          | 6          | 6          | 8          | 6          | 6          | 6          | 8          | 6          | 6          | 6          |

| Standard channels                                    | 4          | 0          | 0          | 0          | 4          | 0          | 0          | 0          | 4          | 0          | 0          | 0          |

| 12-bit DAC                                           | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          |

| DMA                                                  | Yes        |

Table 1. MC56F827xx Family

Table continues on the next page...

MC56F827xx, Rev. 3.0, 09/2016

#### Overview

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Bit reverse address mode, which effectively supports DSP and Fast Fourier Transform algorithms

- Full shadowing of the register stack for zero-overhead context saves and restores: nine shadow registers correspond to nine address registers (R0, R1, R2, R3, R4, R5, N, N3, M01)

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions enable compact code

- Enhanced bit manipulation instruction set

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack, with the stack's depth limited only by memory

- Priority level setting for interrupt levels

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, real-time debugging that is independent of processor speed

## **1.3 Operation Parameters**

- Up to 50 MHz operation in normal mode and 100 MHz operation in fast mode

- Operation ambient temperature:

- V Temperature option:-40 °C to 105°C

- M Temperature option:-40 °C to 125°C

- Single 3.3 V power supply

- Supply range:  $V_{DD}$   $V_{SS}$  = 2.7 V to 3.6 V,  $V_{DDA}$   $V_{SSA}$  = 2.7 V to 3.6 V

## 1.4 On-Chip Memory and Memory Protection

- Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Internal flash memory with security and protection to prevent unauthorized access

- Memory resource protection (MRP) unit to protect supervisor programs and resources from user programs

- Programming code can reside in flash memory during flash programming

- The dual-port RAM controller supports concurrent instruction fetches and data accesses, or dual data accesses by the core.

- Concurrent accesses provide increased performance.

- The data and instruction arrive at the core in the same cycle, reducing latency.

- On-chip memory

| Signal Name                | 64 LQFP | 48 LQFP | 32 LQFP | Туре         | State During<br>Reset             | Signal Description                                                                                                                                                                                                                         |

|----------------------------|---------|---------|---------|--------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |         |         |         |              |                                   | high of ADCA; CMPA_IN1 is negative<br>input 1 of analog comparator A. When<br>used as an analog input, the signal goes<br>to both ANA2, VREFHA, and<br>CMPA_IN1.                                                                           |

| GPIOA3                     | 16      | 12      | _       | Input/Output | Input, internal<br>pullup enabled | GPIO Port A3: After reset, the default state is GPIOA3.                                                                                                                                                                                    |

| (ANA3&VREFLA&<br>CMPA_IN2) | -       |         |         | Input        |                                   | ANA3 is analog input to channel 3 of<br>ADCA; VREFLA is analog reference low<br>of ADCA; CMPA_IN2 is negative input 2<br>of analog comparator A.                                                                                           |

| GPIOA4                     | 12      | 8       | —       | Input/Output | Input, internal pullup enabled    | GPIO Port A4: After reset, the default state is GPIOA4.                                                                                                                                                                                    |

| (ANA4&CMPD_IN<br>0)        |         |         |         | Input        |                                   | ANA4 is Analog input to channel 4 of<br>ADCA; CMPD_IN0 is input 0 to<br>comparator D.                                                                                                                                                      |

| GPIOA5                     | 11      |         |         | Input/Output | Input, internal<br>pullup enabled | GPIO Port A5: After reset, the default state is GPIOA5.                                                                                                                                                                                    |

| (ANA5&CMPD_IN<br>1)        | -       |         |         | Input        |                                   | ANA5 is analog input to channel 5 of<br>ADCA; ANC9 is analog input to channel<br>9 of ADCC; CMPD_IN1 is negative input<br>1 of analog comparator D.                                                                                        |

| GPIOA6                     | 10      |         |         | Input/Output | Input, internal pullup enabled    | GPIO Port A6: After reset, the default state is GPIOA6.                                                                                                                                                                                    |

| (ANA6&CMPD_IN<br>2)        |         |         |         | Input        |                                   | ANA6 is analog input to channel 5 of<br>ADCA; CMPD_IN2 is negative input 2 of<br>analog comparator D.                                                                                                                                      |

| GPIOA7                     | 9       |         | —       | Input/Output | Input, internal pullup enabled    | GPIO Port A7: After reset, the default state is GPIOA7.                                                                                                                                                                                    |

| (ANA7&CMPD_IN<br>3)        |         |         |         | Input        |                                   | ANA7 is analog input to channel 7 of<br>ADCA; CMPD_IN3 is negative input 3 of<br>analog comparator D.                                                                                                                                      |

| GPIOB0                     | 24      | 17      | 11      | Input/Output | Input, internal pullup enabled    | GPIO Port B0: After reset, the default state is GPIOB0.                                                                                                                                                                                    |

| (ANB0&CMPB_IN<br>3)        |         |         |         | Input        |                                   | ANB0 is analog input to channel 0 of<br>ADCB; CMPB_IN3 is positive input 3 of<br>analog comparator B. When used as an<br>analog input, the signal goes to ANB0<br>and CMPB_IN3. The ADC control<br>register configures this input as ANB0. |

| GPIOB1                     | 25      | 18      | 12      | Input/Output | Input, internal<br>pullup enabled | GPIO Port B1: After reset, the default state is GPIOB1.                                                                                                                                                                                    |

| (ANB1&CMPB_IN<br>0)        |         |         |         | Input        |                                   | ANB1 is analog input to channel 1 of<br>ADCB; CMPB_IN0 is negative input 0 of<br>analog comparator B. When used as an<br>analog input, the signal goes to ANB1<br>and CMPB_IN0. The ADC control<br>register configures this input as ANB1. |

#### Table 2. Signal descriptions (continued)

Table continues on the next page...

#### MC56F827xx signal and pin descriptions

| Signal Name | 64 LQFP | 48 LQFP | 32 LQFP | Туре                        | State During<br>Reset          | Signal Description                                                                                                                                               |

|-------------|---------|---------|---------|-----------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOE4      | 51      | 39      | 25      | Input/Output                | Input, internal pullup enabled | GPIO Port E4: After reset, the default state is GPIOE4.                                                                                                          |

| (PWMA_2B)   |         |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule<br>2, output B or input capture B                                                                                             |

| (XB_IN2)    |         |         |         | Input                       |                                | Crossbar module input 2                                                                                                                                          |

| GPIOE5      | 52      | 40      | 26      | Input/Output                | Input, internal pullup enabled | GPIO Port E5: After reset, the default state is GPIOE5.                                                                                                          |

| (PWMA_2A)   |         |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule 2, output A or input capture A                                                                                                |

| (XB_IN3)    |         |         |         | Input                       |                                | Crossbar module input 3                                                                                                                                          |

| GPIOE6      | 53      | _       | _       | Input/Output                | Input, internal pullup enabled | GPIO Port E6: After reset, the default state is GPIOE6.                                                                                                          |

| (PWMA_3B)   |         |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule 3, output B or input capture B                                                                                                |

| (XB_IN4)    |         |         |         | Input                       |                                | Crossbar module input 4                                                                                                                                          |

| GPIOE7      | 54      | _       | _       | Input/Output                | Input, internal pullup enabled | GPIO Port E7: After reset, the default state is GPIOE7.                                                                                                          |

| (PWMA_3A)   |         |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule 3, output A or input capture A                                                                                                |

| (XB_IN5)    |         |         |         | Input                       |                                | Crossbar module input 5                                                                                                                                          |

| GPIOF0      | 36      | 28      | _       | Input/Output                | Input, internal pullup enabled | GPIO Port F0: After reset, the default state is GPIOF0.                                                                                                          |

| (XB_IN6)    |         |         |         | Input                       |                                | Crossbar module input 6                                                                                                                                          |

| (SCLK1)     |         |         |         | Input/Output                |                                | SPI1 serial clock — In master mode,<br>SCLK1 pin is an output, clocking slaved<br>listeners. In slave mode, SCLK1 pin is<br>the data clock input 0.              |

| GPIOF1      | 50      | 38      | —       | Input/Output                | Input, internal pullup enabled | GPIO Port F1: After reset, the default state is GPIOF1.                                                                                                          |

| (CLKO1)     |         |         |         | Output                      |                                | Buffered clock output 1: the clock source<br>is selected by clockout select<br>(CLKOSEL) bits in the clock output<br>select register (CLKOUT) of the SIM.        |

| (XB_IN7)    | -       |         |         | Input                       | -                              | Crossbar module input 7                                                                                                                                          |

| (CMPD_O)    | 1       |         |         | Output                      | 1                              | Analog comparator D output                                                                                                                                       |

| GPIOF2      | 39      |         | 19      | Input/Output                | Input, internal pullup enabled | GPIO Port F2: After reset, the default state is GPIOF2.                                                                                                          |

| (SCL0)      |         |         |         | Input/Open-<br>drain Output |                                | I <sup>2</sup> C0 serial clock                                                                                                                                   |

| (XB_OUT6)   | 7       |         |         | Output                      | 1                              | Crossbar module output 6                                                                                                                                         |

| (MISO1)     |         |         |         | Input/Output                |                                | Master in/slave out for SPI1 —In master<br>mode, MISO1 pin is the data input. In<br>slave mode, MISO1 pin is the data<br>output. The MISO line of a slave device |

Table 2. Signal descriptions (continued)

Table continues on the next page...

## 4.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 4.2 Format

Part numbers for this device have the following format: Q 56F8 2 C F P T PP N

## 4.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                                                             | Values                                                                                        |

|-------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| Q     | Qualification status                                                    | <ul> <li>MC = Fully qualified, general market flow</li> <li>PC = Prequalification</li> </ul>  |

| 56F8  | DSC family with flash memory and DSP56800/<br>DSP56800E/DSP56800EX core | • 56F8                                                                                        |

| 2     | DSC subfamily                                                           | • 2                                                                                           |

| С     | Maximum CPU frequency (MHz)                                             | <ul> <li>3 = 50 MHz</li> <li>7 = 100 MHz</li> </ul>                                           |

| F     | Primary program flash memory size                                       | <ul> <li>1 = 16 KB</li> <li>2 = 32 KB</li> <li>3 = 48 KB</li> <li>4 = 64 KB</li> </ul>        |

| P     | Pin count                                                               | <ul> <li>3 = 32</li> <li>6 = 48</li> <li>8 = 64</li> </ul>                                    |

| Т     | Temperature range (°C)                                                  | <ul> <li>V = -40 to 105</li> <li>M = -40 to 125</li> </ul>                                    |

| PP    | Package identifier                                                      | <ul> <li>LC = 32LQFP</li> <li>FM = 32QFN</li> <li>LF = 48LQFP</li> <li>LH = 64LQFP</li> </ul> |

| N     | Packaging type                                                          | <ul> <li>R = Tape and reel</li> <li>(Blank) = Trays</li> </ul>                                |

## 4.4 Example

This is an example part number: MC56F82748VLH

## 5.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

## 5.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

### 5.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

## 5.5 Result of exceeding a rating

## 5.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

## 5.8.2 Example 2

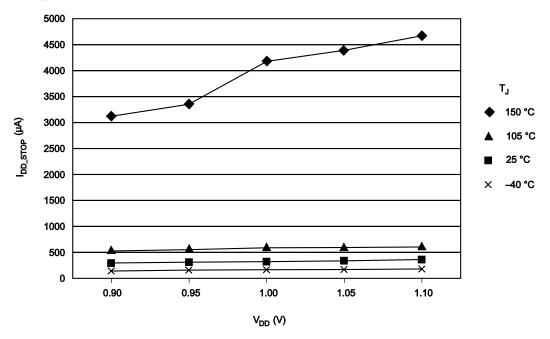

This is an example of a chart that shows typical values for various voltage and temperature conditions:

## 5.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

| Mode | Maximum<br>Frequency | Conditions                                                                                                                 |                              | Typical at<br>3.3 V,<br>25°C |                   | Maximum<br>at 3.6 V,<br>105°C |                   | Maximum<br>at 3.6V,<br>125°C |  |

|------|----------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------|-------------------|-------------------------------|-------------------|------------------------------|--|

|      |                      |                                                                                                                            | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub>             | I <sub>DD</sub> 1 | I <sub>DDA</sub>              | I <sub>DD</sub> 1 | I <sub>DDA</sub>             |  |

|      |                      | <ul> <li>All peripheral modules, except COP, disabled and clocks gated off</li> <li>Processor core in stop mode</li> </ul> |                              |                              |                   |                               |                   |                              |  |

Table 11. Current Consumption (mA)

- 1. No output switching, all ports configured as inputs, all inputs low, no DC loads.

- In all chip LP modes and flash memory VLP modes, the maximum frequency for flash memory operation is 500 kHz due to the fixed frequency ratio of 1:2 between the CPU clock and the flash clock when running with 2 MHz external clock input and CPU running at 1 MHz.

### 7.3.6 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 7.3.7 Capacitance attributes

Table 12.

Capacitance attributes

| Description        | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------|------------------|------|------|------|------|

| Input capacitance  | C <sub>IN</sub>  | —    | 10   | —    | pF   |

| Output capacitance | C <sub>OUT</sub> | _    | 10   | _    | pF   |

## 7.4 Switching specifications

### 7.4.1 Device clock specifications

Table 13. Device clock specifications

| Symbol           | Description                                                                                                                   | Min.  | Max.       | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-------|

|                  | Normal run mode                                                                                                               | e     |            |      |       |

| fsysclk          | Device (system and core) clock frequency <ul> <li>using relaxation oscillator</li> <li>using external clock source</li> </ul> | 0.001 | 100<br>100 | MHz  |       |

| f <sub>BUS</sub> | Bus clock                                                                                                                     | —     | 50         | MHz  |       |

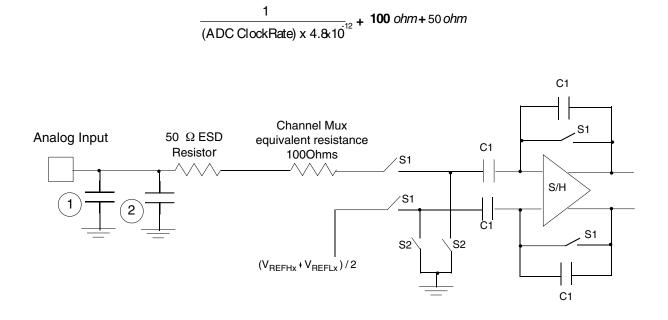

- 1. Parasitic capacitance due to package, pin-to-pin and pin-to-package base coupling = 1.8pF

- 2. Parasitic capacitance due to the chip bond pad, ESD protection devices and signal routing = 2.04pF

- 3. S1 and S2 switch phases are non-overlapping and depend on the ADC clock frequency

Figure 9. Equivalent circuit for A/D loading

### 8.5.2 12-bit Digital-to-Analog Converter (DAC) parameters Table 28. DAC parameters

|                                                                 | Symbol                                                                                                                                                             | Min                                                                                                                                                                                                  | Тур                                                                                                                                                              | Max                                                                                                                                                                           | Unit                                                                                                                                                                             |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DC Specifications                                               |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |

|                                                                 |                                                                                                                                                                    | 12                                                                                                                                                                                                   | 12                                                                                                                                                               | 12                                                                                                                                                                            | bits                                                                                                                                                                             |  |

| At output load                                                  |                                                                                                                                                                    |                                                                                                                                                                                                      | 1                                                                                                                                                                |                                                                                                                                                                               | μs                                                                                                                                                                               |  |

| RLD = 3 kΩ                                                      |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |

| CLD = 400 pF                                                    |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |

| Time from release of PWRDWN signal until DACOUT signal is valid | t <sub>DAPU</sub>                                                                                                                                                  | —                                                                                                                                                                                                    | —                                                                                                                                                                | 11                                                                                                                                                                            | μs                                                                                                                                                                               |  |

| Accuracy                                                        |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |

| Range of input digital words:                                   | INL                                                                                                                                                                | _                                                                                                                                                                                                    | +/- 3                                                                                                                                                            | +/- 4                                                                                                                                                                         | LSB <sup>3</sup>                                                                                                                                                                 |  |

| -                                                               | At output load<br>RLD = 3 kΩ<br>CLD = 400 pF<br>Time from release of PWRDWN<br>signal until DACOUT signal is valid<br><b>Accu</b><br>Range of input digital words: | At output load         RLD = 3 kΩ         CLD = 400 pF         Time from release of PWRDWN signal until DACOUT signal is valid         t_DAPU         Accuracy         Range of input digital words: | At output load     —       RLD = 3 kΩ     —       CLD = 400 pF     —       Time from release of PWRDWN signal until DACOUT signal is valid     t <sub>DAPU</sub> | At output load1212At output load1RLD = 3 kΩ1CLD = 400 pFTime from release of PWRDWN<br>signal until DACOUT signal is validt_DAPUAccuracyRange of input digital words:INL+/- 3 | 121212At output load—1RLD = 3 kΩ—1CLD = 400 pF——Time from release of PWRDWN<br>signal until DACOUT signal is validtDAPU—AccuracyRange of input digital words:INL—+/- 3+/- 3+/- 4 |  |

Table continues on the next page...

#### MC56F827xx, Rev. 3.0, 09/2016

| Parameter                   | Conditions/Comments                                                                     | Symbol              | Min                          | Тур        | Max                          | Unit             |  |

|-----------------------------|-----------------------------------------------------------------------------------------|---------------------|------------------------------|------------|------------------------------|------------------|--|

|                             | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |  |

|                             | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |  |

| Differential non-           | Range of input digital words:                                                           | DNL                 | _                            | +/- 0.8    | +/- 0.9                      | LSB <sup>3</sup> |  |

| linearity <sup>2</sup>      | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |  |

|                             | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |  |

| Monotonicity                | > 6 sigma monotonicity,                                                                 |                     |                              | guaranteed |                              | _                |  |

|                             | < 3.4 ppm non-monotonicity                                                              |                     |                              |            |                              |                  |  |

| Offset error <sup>2</sup>   | Range of input digital words:                                                           | V <sub>OFFSET</sub> | _                            | +/- 25     | + /- 43                      | mV               |  |

|                             | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |  |

|                             | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |  |

| Gain error <sup>2</sup>     | Range of input digital words: 410 to<br>3891 (\$19A - \$F33) 5% to 95% of<br>full range | E <sub>GAIN</sub>   | _                            | +/- 0.5    | +/- 1.5                      | %                |  |

|                             | DAC C                                                                                   | Dutput              |                              |            |                              |                  |  |

| Output voltage range        | Within 40 mV of either $V_{\rm SSA}$ or $V_{\rm DDA}$                                   | V <sub>OUT</sub>    | V <sub>SSA</sub> +<br>0.04 V | _          | V <sub>DDA</sub> - 0.04<br>V | V                |  |

|                             | AC Specifications                                                                       |                     |                              |            |                              |                  |  |

| Signal-to-noise ratio       |                                                                                         | SNR                 |                              | 85         |                              | dB               |  |

| Spurious free dynamic range |                                                                                         | SFDR                | _                            | -72        | —                            | dB               |  |

| Effective number of bits    |                                                                                         | ENOB                | _                            | 11         | _                            | bits             |  |

#### Table 28. DAC parameters (continued)

$1. \quad \mbox{Settling time is swing range from $V_{SSA}$ to $V_{DDA}$ } 2. \ \mbox{No guaranteed specification within 5% of $V_{DDA}$ or $V_{SSA}$ }$

3. LSB = 0.806 mV

#### **CMP and 6-bit DAC electrical specifications** 8.5.3 Table 29. Comparator and 6-bit DAC electrical specifications

| Symbol            | Description                                       | Min.            | Тур. | Max.            | Unit |

|-------------------|---------------------------------------------------|-----------------|------|-----------------|------|

| V <sub>DD</sub>   | Supply voltage                                    | 2.7             | —    | 3.6             | V    |

| I <sub>DDHS</sub> | Supply current, High-speed mode (EN=1, PMODE=1)   | _               | 300  | —               | μA   |

| I <sub>DDLS</sub> | Supply current, low-speed mode (EN=1, PMODE=0)    | _               | 36   | —               | μA   |

| V <sub>AIN</sub>  | Analog input voltage                              | V <sub>SS</sub> | —    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>  | Analog input offset voltage                       | _               | —    | 20              | mV   |

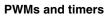

| V <sub>H</sub>    | V <sub>H</sub> Analog comparator hysteresis       |                 |      |                 |      |

|                   | <ul> <li>CR0[HYSTCTR] = 00<sup>1</sup></li> </ul> |                 | 5    | 13              | mV   |

|                   | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>             | —               | 25   | 48              | mV   |

|                   | • CR0[HYSTCTR] = 10 <sup>2</sup>                  | _               | 55   | 105             | mV   |

|                   | • CR0[HYSTCTR] = 11 <sup>2</sup>                  | —               | 80   | 148             | mV   |

Table continues on the next page ...

Figure 11. Typical hysteresis vs. Vin level (V<sub>DD</sub> = 3.3 V, PMODE = 1)

### 8.6 PWMs and timers

### 8.6.1 Enhanced NanoEdge PWM characteristics

| Table 30. | NanoEdge | <b>PWM timing</b> | parameters |

|-----------|----------|-------------------|------------|

|-----------|----------|-------------------|------------|

| Characteristic                                             | Symbol          | Min | Тур | Max | Unit |

|------------------------------------------------------------|-----------------|-----|-----|-----|------|

| PWM clock frequency                                        |                 |     | 100 |     | MHz  |

| NanoEdge Placement (NEP) Step Size <sup>1, 2</sup>         | pwmp            |     | 312 |     | ps   |

| Delay for fault input activating to PWM output deactivated |                 | 1   |     |     | ns   |

| Power-up Time <sup>3</sup>                                 | t <sub>pu</sub> |     | 25  |     | μs   |

1. Reference IPbus clock of 100 MHz in NanoEdge Placement mode.

2. Temperature and voltage variations do not affect NanoEdge Placement step size.

3. Powerdown to NanoEdge mode transition.

## 8.6.2 Quad Timer timing

Parameters listed are guaranteed by design.

MC56F827xx, Rev. 3.0, 09/2016

#### Design Considerations

$R_{\Theta JA}$  = Package junction-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  = Package junction-to-case thermal resistance (°C/W)

$R_{\Theta CA}$  = Package case-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  is device related and cannot be adjusted. You control the thermal environment to change the case to ambient thermal resistance,  $R_{\Theta CA}$ . For instance, you can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the thermal characterization parameter (YJT) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

Where,

$T_T$  = Thermocouple temperature on top of package (°C/W)

$\Psi_{JT}$  = hermal characterization parameter (°C/W)

$P_D$  = Power dissipation in package (W)

The thermal characterization parameter is measured per JESD51–2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

To determine the junction temperature of the device in the application when heat sinks are used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back-calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

Design Considerations

- Configuring the RESET pin to GPIO output in normal operation in a high-noise environment may help to improve the performance of noise transient immunity.

- Add a 2.2 k $\Omega$  external pullup on the TMS pin of the JTAG port to keep EOnCE in a restate during normal operation if JTAG converter is not present.

- During reset and after reset but before I/O initialization, all I/O pins are at tri-state.

- To eliminate PCB trace impedance effect, each ADC input should have a no less than 33 pF  $10\Omega$  RC filter.

## 9.3 Power-on Reset design considerations

### 9.3.1 Improper power-up sequence between VDD/VSS and VDDA/ VSSA:

It is recommended that VDD be kept within 100 mV of VDDA at all times, including power ramp-up and ramp-down. Failure to keep VDDA within 100 mV of VDDA may cause a leakage current through the substrate, between the VDD and VDDA pad cells. This leakage current could prevent operation of the device after it powers up. The voltage difference between VDD and VDDA must be limited to below 0.3 V at all times, to avoid permanent damage to the part (See Table 5). Also see Table 6.

### 9.3.2 Improperly designed protection circuit:

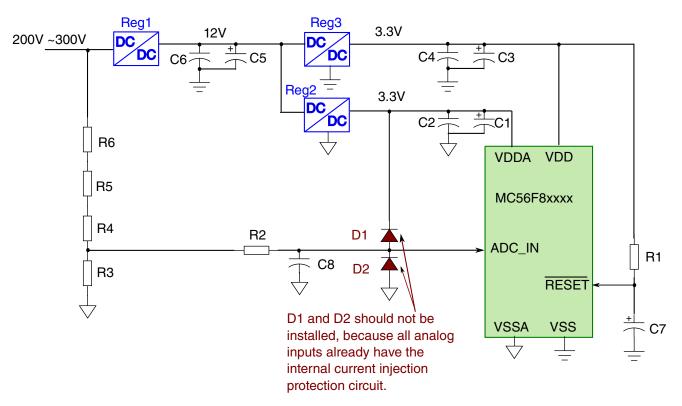

In many circuit designs, it is a general practice to add external clamping diodes on each analog input pin; see diode D1 and D2 in Figure 21, to prevent the surge voltage from damaging the analog input. However, in some cases, these diodes can cause the DSC to fail to start at power-on. For example, in Figure 21, the entire system is directly powered from the power grid; high voltage is fed to 12V DC/DC converter Reg1, then 12V powers DC/DC converter Reg2 and Reg3 to provide 3.3V supply voltage to VDD and VDDA. Due to the startup time delay of DC/DC converters and per-charge the capacitors on 12V and 3.3V rail, VDDA can be charged to a less than 0.5V through a path of R6->R5->R4->R2->D1. If this low voltage duration is more than 1 ms without continuing ramp-up, then it can cause the device to fail to start up.

**Design Considerations**

Figure 21. Protection Circuit Example

MC56F8xxxx DSC uses the 5V tolerance I/O. When the pin is configured to digital input, it can accept 5V input. Table 5. When the pin is configured to analog input, the internal integrated current injection protection circuit is enabled. The current injection protection circuit performs the same functions as external clamp diode D1 and D2 in Figure 21. As long as the source or sink current for each analog pin is less than 3 mA, then there is no damage to the device. See Table 27.

This situation could happen if diodes D1 or D2 are used for clamping; therefore in this case, the D1 and D2 clamping diodes are not recommended to be used.

#### NOTE

In some designs, VDD and VDDA are powered from the same power supply. In this case, above analysis and suggestions are also applicatble.

## 9.3.3 Heavy capacitive load on power supply output:

In some applications, the low cost DC/DC converter may not regulate the output voltage well before it reaches the regulation point, which is roughly around 2.5V to 2.7V. However, the MC56F8xxxx DSC will exit power-on reset at around 2.3V. If the initialization code enables the PLL to run the DSC at full speed right after reset, then the

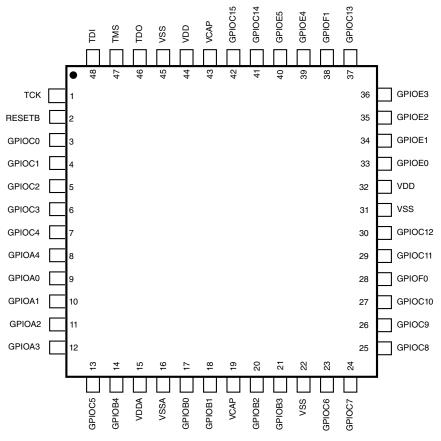

Figure 24. 48-pin LQFP

#### NOTE

The RESETB pin is a 3.3 V pin only.

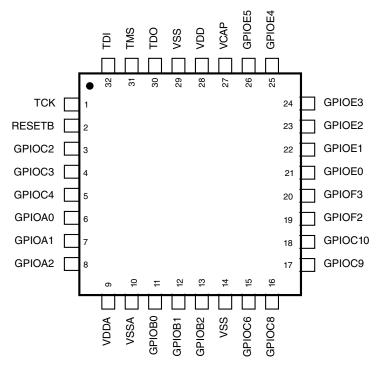

Figure 25. 32-pin LQFP and QFN

## 12 Product documentation

The documents listed in Table 36 are required for a complete description and to successfully design using the device. Documentation is available from local NXP distributors, NXP sales offices, or online at www.nxp.com.

| Table 36. | Device | documentation |

|-----------|--------|---------------|

|-----------|--------|---------------|

| Торіс                                    | Description                                                                                                                       | Document Number   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------|

| DSP56800E/DSP56800EX<br>Reference Manual | Detailed description of the 56800EX family architecture, 32-bit digital signal controller core processor, and the instruction set | DSP56800ERM       |

| MC56F827xx Reference Manual              | Detailed functional description and programming model                                                                             | MC56F827XXRM      |

| MC56F827xx Data Sheet                    | Electrical and timing specifications, pin descriptions, and package information (this document)                                   | MC56F827XXDS      |

| MC56F82xxx Errata                        | Details any chip issues that might be present                                                                                     | MC56F82xxx_Errata |

## **13 Revision History**

The following table summarizes changes to this document since the release of the previous version.

| Rev. No. | Date                 | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | 10/2013              | First public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1      | 11/2013              | <ul> <li>In Table 2, added DACB_O signal description.</li> <li>In Obtaining package dimensions, changed 32-QFN's document number from '98ARE10566D' to '98ASA00473D'.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2      | 03/2016 -<br>05/2016 | <ul> <li>Corrected document part number MC56F827XXDS to MC56F827XX.</li> <li>In "12-bit ADC Electrical Specifications" table, corrected Max Gain Error to 0.990 to 1.010.</li> <li>In Part identification section, in part number fields table, added the 32QFN package identifier.</li> <li>In Electrical design considerations" section, added additional section "Power-on Reset design considerations".</li> <li>Added new section "Power-on Reset design considerations".</li> <li>In "Peripheral highlights" section, added</li> <li>Periodic Interrupt Timer (PIT) Modules</li> <li>External Watchdog Monitor (EWM)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.0      | 09/2016              | <ul> <li>Added products: 56F82746MLF, 56F82733MFM</li> <li>Removed PDB (Programmable Delay Block) mentions, because PDBs are not present<br/>in these devices.</li> <li>Added V and M temperature options to operating characteristics.</li> <li>Moved "Signal groups" section under "MC56F827xx signal and pin descriptions"<br/>section.</li> <li>In "Voltage and current operating ratings" section: updated note; in "Absolute Maximum<br/>Ratings" table, updated Ambient and Junction Temperature rows, also fixed broken<br/>footnotes.</li> <li>In "Power consumption operating behaviors" section, in "Current Consumption" table:<br/>added columns and data for Maximum at 3.6V, 125°C", fixed broken footnotes.</li> <li>In "Thermal operating requirements" section, updated Die junction temperature and<br/>Ambient temperature requirements.</li> <li>In "Relaxation Oscillator Timing" section, in "Relaxation Oscillator Electrical<br/>Specifications" table:</li> <li>Added data for "-40°C to 125°C" temperature range.</li> <li>For "8 MHz Output Frequency, Standby Mode frequency", 2 corrections were<br/>made.</li> <li>Fixed broken footnotes.</li> </ul> |

Table 37.

Revision History

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, and I2C are trademarks of NXP B.V. All other product or service names are the property of their respective owners. All rights reserved.

© 2013–2016 NXP B.V.

Document Number MC56F827XXDS Revision 3.0, 09/2016