Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800EX                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 48KB (24K x 16)                                                       |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                |                                                                       |

| RAM Size                   | 4K x 16                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                           |

| Data Converters            | A/D 6x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount, Wettable Flank                                         |

| Package / Case             | 32-VFQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-HVQFN (5x5)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f82733vfm |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- System

- DMA controller

- Integrated power-on reset (POR) and low-voltage interrupt (LVI) and brown-out reset module

- Inter-module crossbar connection

- JTAG/enhanced on-chip emulation (EOnCE) for unobtrusive, real-time debugging

- Operating characteristics

- Single supply: 3.0 V to 3.6 V

- 5 V-tolerant I/O (except for RESETB pin which is a 3.3 V pin only)

- Operation ambient temperature: V temperature option: -40°C to  $105^\circ C$

- Operation ambient temperature: M temperature option: -40°C to  $125^\circ C$

- 64-pin LQFP, 48-pin LQFP, 32-pin QFN, and 32-pin LQFP packages

# 1 Overview

# 1.1 MC56F827xx Product Family

The following table is the comparsion of features among members of the family.

| Feature                                              | MC56F82    |            |            |            |            |            |            |            |            |            |            |            |

|------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Part Number <sup>1</sup>                             | 748V<br>LH | 746V<br>LF | 743V<br>LC | 743V<br>FM | 738V<br>LH | 736V<br>LF | 733V<br>LC | 733V<br>FM | 728V<br>LH | 726V<br>LF | 723V<br>LC | 723V<br>FM |

|                                                      |            | 746M<br>LF |            |            |            |            |            | 733M<br>FM |            |            |            |            |

| Core frequency<br>(MHz)                              | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     |

| Flash memory<br>(KB)                                 | 64         | 64         | 64         | 64         | 48         | 48         | 48         | 48         | 32         | 32         | 32         | 32         |

| RAM (KB)                                             | 8          | 8          | 8          | 8          | 8          | 8          | 8          | 8          | 6          | 6          | 6          | 6          |

| Interrupt<br>Controller                              | Yes        |

| Windowed<br>Computer<br>Operating<br>Properly (WCOP) | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| External<br>Watchdog Monitor<br>(EWM)                | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| Periodic Interrupt<br>Timer (PIT)                    | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          |

| Cyclic<br>Redundancy<br>Check (CRC)                  | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| Quad Timer<br>(TMR)                                  | 1x4        |

| 12-bit Cyclic ADC channels                           | 2x8        | 2x5        | 2x3        | 2x3        | 2x8        | 2x5        | 2x3        | 2x3        | 2x8        | 2x5        | 2x3        | 2x3        |

| PWM Module:                                          |            |            |            |            |            |            |            |            |            |            |            |            |

| Input capture<br>channels <sup>2</sup>               | 12         | 6          | 6          | 6          | 12         | 6          | 6          | 6          | 12         | 6          | 6          | 6          |

| High-resolution channels                             | 8          | 6          | 6          | 6          | 8          | 6          | 6          | 6          | 8          | 6          | 6          | 6          |

| Standard channels                                    | 4          | 0          | 0          | 0          | 4          | 0          | 0          | 0          | 4          | 0          | 0          | 0          |

| 12-bit DAC                                           | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          |

| DMA                                                  | Yes        |

Table 1. MC56F827xx Family

Table continues on the next page...

- Up to 64 KB program/data flash memory

- Up to 8 KB dual port data/program RAM

# 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user-programmable priority levels for each interrupt source: level 0, level 1, level 2

- Unmaskable level 3 interrupts include illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Interrupt level 3 is highest priority and non-maskable. Its sources include:

- Illegal instructions

- Hardware stack overflow

- SWI instruction

- EOnce interrupts

- Misaligned data accesses

- Lowest-priority software interrupt: level LP

- Support for nested interrupts, so that a higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level is managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

# **1.6 Peripheral highlights**

# 1.6.1 Enhanced Flex Pulse Width Modulator (eFlexPWM)

- 16 bits of resolution for center, edge-aligned, and asymmetrical PWMs

- PWM outputs can be configured as complementary output pairs or independent outputs

- Dedicated time-base counter with period and frequency control per submodule

- Independent top and bottom deadtime insertion for each complementary pair

- Independent control of both edges of each PWM output

- Enhanced input capture and output compare functionality on each input:

- Channels not used for PWM generation can be used for buffered output compare functions.

#### Peripheral highlights

- Channels not used for PWM generation can be used for input capture functions.

- Enhanced dual edge capture functionality

- Synchronization of submodule to external hardware (or other PWM) is supported.

- Double-buffered PWM registers

- Integral reload rates from 1 to 16

- Half-cycle reload capability

- Multiple output trigger events can be generated per PWM cycle via hardware.

- Support for double-switching PWM outputs

- Up to eight fault inputs can be assigned to control multiple PWM outputs

- Programmable filters for fault inputs

- Independently programmable PWM output polarity

- Individual software control of each PWM output

- All outputs can be programmed to change simultaneously via a FORCE\_OUT event.

- PWMX pin can optionally output a third PWM signal from each submodule

- Option to supply the source for each complementary PWM signal pair from any of the following:

- Crossbar module outputs

- External ADC input, taking into account values set in ADC high and low limit registers

## 1.6.2 12-bit Analog-to-Digital Converter (Cyclic type)

- Two independent 12-bit analog-to-digital converters (ADCs):

- 2 x 8-channel external inputs

- Built-in x1, x2, x4 programmable gain pre-amplifier

- Maximum ADC clock frequency up to 10 MHz, having period as low as 100-ns

- Single conversion time of 10 ADC clock cycles

- Additional conversion time of 8 ADC clock cycles

- Support of analog inputs for single-ended and differential, including unipolar differential, conversions

- Sequential, parallel, and independent scan mode

- First 8 samples have offset, limit and zero-crossing calculation supported

- ADC conversions can be synchronized by *any* module connected to the internal crossbar module, such as PWM, timer, GPIO, and comparator modules.

- Support for simultaneous triggering and software-triggering conversions

- Support for a multi-triggering mode with a programmable number of conversions on each trigger

- Each ADC has ability to scan and store up to 8 conversion results.

- Current injection protection

#### Peripheral highlights

- Automatic mode allows the DAC to automatically generate pre-programmed output waveforms, including square, triangle, and sawtooth waveforms (for applications like slope compensation)

- Programmable period, update rate, and range

- Output can be routed to an internal comparator, ADC, or optionally to an off-chip destination

### 1.6.7 Quad Timer

- Four 16-bit up/down counters, with a programmable prescaler for each counter

- Operation modes: edge count, gated count, signed count, capture, compare, PWM, signal shot, single pulse, pulse string, cascaded, quadrature decode

- Programmable input filter

- Counting start can be synchronized across counters

- Up to 100 MHz operation clock

### **1.6.8 Queued Serial Communications Interface (QSCI) modules**

- Operating clock can be up to two times the CPU operating frequency

- Four-word-deep FIFOs available on both transmit and receive buffers

- Standard mark/space non-return-to-zero (NRZ) format

- 16-bit integer and 3-bit fractional baud rate selection

- Full-duplex or single-wire operation

- Programmable 8-bit or 9-bit data format

- Error detection capability

- Two receiver wakeup methods:

- Idle line

- Address mark

- 1/16 bit-time noise detection

- Up to 6.25 Mbit/s baud rate at 100 MHz operation clock

### 1.6.9 Queued Serial Peripheral Interface (QSPI) modules

- Maximum 12.5 Mbit/s baud rate

- Selectable baud rate clock sources for low baud rate communication

- Baud rate as low as Baudrate\_Freq\_in / 8192

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four-word-deep FIFOs available on transmit and receive buffers

| Signal Name                | 64 LQFP | 48 LQFP | 32 LQFP | Туре                          | State During<br>Reset             | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|---------|---------|---------|-------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тск                        | 1       | 1       | 1       | Input                         | Input, internal<br>pullup enabled | Test Clock Input — The pin is connected<br>internally to a pullup resistor. A Schmitt-<br>trigger input is used for noise immunity.<br>After reset, the default state is TCK                                                                                                                                                                                                                                                |

| (GPIOD2)                   |         |         |         | Input/Output                  |                                   | GPIO Port D2                                                                                                                                                                                                                                                                                                                                                                                                                |

| TMS                        | 63      | 47      | 31      | Input                         | Input, internal<br>pullup enabled | Test Mode Select Input — It is sampled<br>on the rising edge of TCK and has an<br>internal pullup resistor. After reset, the<br>default state is TMS.                                                                                                                                                                                                                                                                       |

|                            |         |         |         |                               |                                   | <b>NOTE:</b> Always tie the TMS pin to $V_{DD}$ through a 2.2 k $\Omega$ resistor if need to keep on-board debug capability. Otherwise, directly tie to $V_{DD}$ .                                                                                                                                                                                                                                                          |

| (GPIOD3)                   |         |         |         | Input/Output                  |                                   | GPIO Port D3                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESET or<br>RESETB         | 2       | 2       | 2       | Input                         | Input, internal<br>pullup enabled | Reset — A direct hardware reset on the processor. When RESET is asserted low, the device is initialized and placed in the reset state. A Schmitt-trigger input is used for noise immunity. The internal reset signal is deasserted synchronous with the internal clocks after a fixed number of internal clocks. After reset, the default state is RESET. Recommended a capacitor of up to 0.1 $\mu$ F for filtering noise. |

| (GPIOD4)                   |         |         |         | Input/<br>Opendrain<br>Output |                                   | GPIO Port D4 RESET functionality is<br>disabled in this mode and the device can<br>be reset only through POR, COP reset,<br>or software reset.                                                                                                                                                                                                                                                                              |

| GPIOA0                     | 13      | 9       | 6       | Input/Output                  | Input, internal                   | GPIO Port A0                                                                                                                                                                                                                                                                                                                                                                                                                |

| (ANA0&CMPA_IN<br>3)        | -       |         |         | Input                         | pullup enabled                    | ANA0 is analog input to channel 0 of<br>ADCA; CMPA_IN3 is positive input 3 of<br>analog comparator A. After reset, the<br>default state is GPIOA0.                                                                                                                                                                                                                                                                          |

| (CMPC_O)                   |         |         |         | Output                        |                                   | Analog comparator C output                                                                                                                                                                                                                                                                                                                                                                                                  |

| GPIOA1                     | 14      | 10      | 7       | Input/Output                  | Input, internal pullup enabled    | GPIO Port A1: After reset, the default state is GPIOA1.                                                                                                                                                                                                                                                                                                                                                                     |

| (ANA1&CMPA_IN<br>0)        |         |         |         | Input                         |                                   | ANA1 is analog input to channel 1 of<br>ADCA; CMPA_IN0 is negative input 0 of<br>analog comparator A. When used as an<br>analog input, the signal goes to ANA1<br>and CMPA_IN0. The ADC control<br>register configures this input as ANA1 or<br>CMPA_IN0.                                                                                                                                                                   |

| GPIOA2                     | 15      | 11      | 8       | Input/Output                  | Input, internal<br>pullup enabled | GPIO Port A2: After reset, the default state is GPIOA2.                                                                                                                                                                                                                                                                                                                                                                     |

| (ANA2&VREFHA<br>&CMPA_IN1) |         |         |         | Input                         |                                   | ANA2 is analog input to channel 2 of ADCA; VREFHA is analog reference                                                                                                                                                                                                                                                                                                                                                       |

Table continues on the next page...

#### MC56F827xx signal and pin descriptions

| Table 2. | Signal | descriptions | (continued) |

|----------|--------|--------------|-------------|

|----------|--------|--------------|-------------|

| Signal Name   | 64 LQFP | 48 LQFP | 32 LQFP | Туре                        | State During<br>Reset          | Signal Description                                                                                                            |

|---------------|---------|---------|---------|-----------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|               |         |         |         |                             |                                | is placed in the high-impedance state if the slave device is not selected.                                                    |

| GPIOF3        | 40      | _       | 20      | Input/Output                | Input, internal pullup enabled | GPIO Port F3: After reset, the default state is GPIOF3.                                                                       |

| (SDA0)        |         |         |         | Input/Open-<br>drain Output |                                | I <sup>2</sup> C0 serial data line                                                                                            |

| (XB_OUT7)     |         |         |         | Output                      |                                | Crossbar module output 7                                                                                                      |

| (MOSI1)       |         |         |         | Input/Output                |                                | Master out/slave in for SPI1— In master<br>mode, MOSI1 pin is the data output. In<br>slave mode, MOSI1 pin is the data input. |

| GPIOF4        | 41      |         | _       | Input/Output                | Input, internal pullup enabled | GPIO Port F4: After reset, the default state is GPIOF4.                                                                       |

| (TXD1)        |         |         |         | Output                      |                                | SCI1 transmit data output or transmit/<br>receive in single wire operation                                                    |

| (XB_OUT8)     |         |         |         | Output                      |                                | Crossbar module output 8                                                                                                      |

| (PWMA_0X)     | ]       |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule<br>0, output X or input capture X                                                          |

| (PWMA_FAULT6) |         |         |         | Input                       |                                | Disable PWMA output 6                                                                                                         |

| GPIOF5        | 42      | _       | _       | Input/Output                | Input, internal pullup enabled | GPIO Port F5: After reset, the default state is GPIOF5.                                                                       |

| (RXD1)        |         |         |         | Input                       |                                | SCI1 receive data input                                                                                                       |

| (XB_OUT9)     |         |         |         | Output                      |                                | Crossbar module output 9                                                                                                      |

| (PWMA_1X)     |         |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule<br>1, output X or input capture X                                                          |

| (PWMA_FAULT7) |         |         |         | Input                       |                                | Disable PWMA output 7                                                                                                         |

| GPIOF6        | 58      |         | _       | Input/Output                | Input, internal pullup enabled | GPIO Port F6: After reset, the default state is GPIOF6.                                                                       |

| (PWMA_3X)     |         |         |         | Input/Output                |                                | PWM module A (NanoEdge), submodule<br>3, output X or input capture X                                                          |

| (XB_IN2)      |         |         |         | Input                       |                                | Crossbar module input 2                                                                                                       |

| GPIOF7        | 59      | _       | _       | Input/Output                | Input, internal pullup enabled | GPIO Port F7: After reset, the default state is GPIOF7.                                                                       |

| (CMPC_O)      | -       |         |         | Output                      |                                | Analog comparator C output                                                                                                    |

| (SS1_B)       |         |         |         | Input/Output                |                                | In slave mode, SS1_B indicates to the SPI1 module that the current transfer is to be received.                                |

| (XB_IN3)      | -       |         |         | Input                       | -                              | Crossbar module input 3                                                                                                       |

| GPIOF8        | 6       | —       | —       | Input/Output                | Input, internal pullup enabled | GPIO Port F8: After reset, the default state is GPIOF8.                                                                       |

| (RXD0)        |         |         |         | Input                       |                                | SCI0 receive data input                                                                                                       |

| (XB_OUT10)    |         |         |         | Output                      |                                | Crossbar module output 10                                                                                                     |

| (CMPD_O)      |         |         |         | Output                      |                                | Analog comparator D output                                                                                                    |

| (PWMA_2X)     |         |         |         |                             |                                | PWM module A (NanoEdge), submodule<br>2, output X or input capture X                                                          |

1. If CLKIN is selected as the device's external clock input, then both the GPS\_C0 bit (in GPS1) and the EXT\_SEL bit (in OCCS oscillator control register (OSCTL)) must be set. Also, the crystal oscillator should be powered down.

# 2.1 Signal groups

The input and output signals of the MC56F827xx are organized into functional groups, as detailed in Table 3.

| Functional Group                                                                     |       | Numbe  | r of Pins |        |

|--------------------------------------------------------------------------------------|-------|--------|-----------|--------|

|                                                                                      | 32QFN | 32LQFP | 48LQFP    | 64LQFP |

| Power Inputs (V <sub>DD</sub> , V <sub>DDA</sub> ), Power output( V <sub>CAP</sub> ) | 3     | 3      | 5         | 6      |

| Ground (V <sub>SS</sub> , V <sub>SSA</sub> )                                         | 3     | 3      | 4         | 4      |

| Reset                                                                                | 1     | 1      | 1         | 1      |

| eFlexPWM with NanoEdge ports not including fault pins (for 56F827xx)                 | 6     | 6      | 6         | 8      |

| eFlexPWM without NanoEdge ports not including fault pins                             | 0     | 0      | 0         | 4      |

| Queued Serial Peripheral Interface (QSPI0 and QSPI1) ports                           | 4     | 4      | 5         | 9      |

| Queued Serial Communications Interface (QSCI0 and QSCI1) ports                       | 4     | 4      | 7         | 10     |

| Inter-Integrated Circuit Interface (I <sup>2</sup> C0) ports                         | 2     | 2      | 4         | 6      |

| 12-bit Analog-to-Digital Converter inputs                                            | 6     | 6      | 10        | 16     |

| Analog Comparator inputs/outputs                                                     | 7/3   | 7/3    | 11/4      | 17/5   |

| 12-bit Digital-to-Analog output                                                      | 2     | 2      | 2         | 2      |

| Quad Timer Module (TMRA and TMRB) ports                                              | 3     | 3      | 4         | 4      |

| Controller Area Network (MSCAN)                                                      | 0     | 0      | 2         | 2      |

| Inter-Module Crossbar inputs/outputs                                                 | 8/4   | 8/4    | 12/6      | 17/11  |

| Clock inputs/outputs                                                                 | 1/1   | 1/1    | 2/2       | 2/2    |

| JTAG / Enhanced On-Chip Emulation (EOnCE)                                            | 4     | 4      | 4         | 4      |

Table 3. Functional Group Pin Allocations

# 3 Ordering parts

## 3.1 Determining valid orderable parts

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to **freescale.com** and perform a part number search for the following device numbers: MC56F82

# 4 Part identification

# 6 Ratings

# 6.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | —    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 6.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    |      | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, *Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices*.

# 6.3 ESD handling ratings

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing is in conformity with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if after exposure to ESD pulses, the device no longer meets the device specification. Complete DC parametric and functional testing is performed as per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                      | Min   | Мах   | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Table 4.

ESD/Latch-up Protection

1. Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

## 6.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 5 may affect device reliability or cause permanent damage to the device.

#### NOTE

If the voltage difference between VDD and VDDA or VSS and VSSA is too large, then the device can malfunction or be permanently damaged. The restrictions are:

- At all times, it is recommended that the voltage difference of VDD - VSS be within +/-200 mV of the voltage difference of VDDA - VSSA,, including power ramp up and ramp down; see additional requirements in Table 6. Failure to do this recommendation may result in a harmful leakage current through the substrate, between the VDD/VSS and VDDA/VSSA pad cells. This harmful leakage current could prevent the device from operating after power up.

- At all times, to avoid permanent damage to the part, the voltage difference between VDD and VDDA must absolutely be limited to 0.3 V, See Table 5.

- At all times, to avoid permanent damage to the part, the voltage difference between VSS and VSSA must absolutely be limited to 0.3 V, See Table 5.

| Characteristic              | Symbol           | Notes <sup>1</sup> | Min  | Max | Unit |

|-----------------------------|------------------|--------------------|------|-----|------|

| Supply Voltage Range        | $V_{DD}$         |                    | -0.3 | 4.0 | V    |

| Analog Supply Voltage Range | V <sub>DDA</sub> |                    | -0.3 | 4.0 | V    |

Table 5. Absolute Maximum Ratings ( $V_{SS} = 0 V$ ,  $V_{SSA} = 0 V$ )

Table continues on the next page ...

# 7.1 General characteristics

The device is fabricated in high-density, low-power CMOS with 5 V-tolerant TTLcompatible digital inputs, except for the  $\overrightarrow{\text{RESET}}$  pin which is 3.3V only. The term "5 Vtolerant" refers to the capability of an I/O pin, built on a 3.3 V-compatible process technology, to withstand a voltage up to 5.5 V without damaging the device.

5 V-tolerant I/O is desirable because many systems have a mixture of devices designed for 3.3 V and 5 V power supplies. In such systems, a bus may carry both 3.3 V- and 5 Vcompatible I/O voltage levels (a standard 3.3 V I/O is designed to receive a maximum voltage of 3.3 V  $\pm$  10% during normal operation without causing damage). This 5 Vtolerant capability therefore offers the power savings of 3.3 V I/O levels combined with the ability to receive 5 V levels without damage.

Absolute maximum ratings in Table 5 are stress ratings only, and functional operation at the maximum is not guaranteed. Stress beyond these ratings may affect device reliability or cause permanent damage to the device.

Unless otherwise stated, all specifications within this chapter apply to the temperature range specified in Table 5 over the following supply ranges:  $V_{SS}=V_{SSA}=0V$ ,  $V_{DD}=V_{DDA}=3.0V$  to 3.6V, CL $\leq$ 50 pF, f<sub>OP</sub>=50MHz.

### CAUTION

This device contains protective circuitry to guard against damage due to high static voltage or electrical fields. However, normal precautions are advised to avoid application of any voltages higher than maximum-rated voltages to this highimpedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate voltage level.

# 7.2 AC electrical characteristics

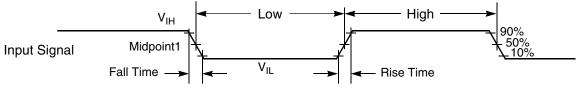

Tests are conducted using the input levels specified in Table 8. Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured between the 10% and 90% points, as shown in Figure 3.

The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

#### Figure 3. Input signal measurement references

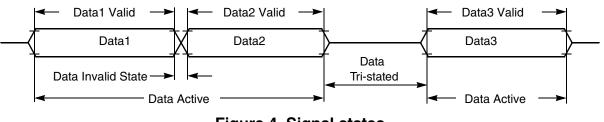

Figure 4 shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached  $V_{OL}$  or  $V_{OH}$

- Data Invalid state, when a signal level is in transition between  $V_{OL}$  and  $V_{OH}$

Figure 4. Signal states

# 7.3 Nonswitching electrical specifications

## 7.3.1 Voltage and current operating requirements

This section includes information about recommended operating conditions.

**NOTE** Recommended  $V_{DD}$  ramp rate is between 1 ms and 200 ms.

| Table 6. | Recommended Operating Conditions (V <sub>REFLx</sub> =0V, V <sub>SSA</sub> =0V, V <sub>SS</sub> =0V) |

|----------|------------------------------------------------------------------------------------------------------|

|----------|------------------------------------------------------------------------------------------------------|

| Characteristic                                         | Symbol                             | Notes <sup>1</sup> | Min                   | Тур | Max              | Unit |

|--------------------------------------------------------|------------------------------------|--------------------|-----------------------|-----|------------------|------|

| Supply voltage                                         | V <sub>DD</sub> , V <sub>DDA</sub> |                    | 2.7                   | 3.3 | 3.6              | V    |

| ADC (Cyclic) Reference Voltage High                    | V <sub>REFHA</sub>                 |                    | V <sub>DDA</sub> -0.6 |     | V <sub>DDA</sub> | V    |

|                                                        | V <sub>REFHB</sub>                 |                    |                       |     |                  |      |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub> | ΔVDD                               |                    | -0.1                  | 0   | 0.1              | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub> | ΔVSS                               |                    | -0.1                  | 0   | 0.1              | V    |

| Input Voltage High (digital inputs)                    | V <sub>IH</sub>                    | Pin Group 1        | 0.7 x V <sub>DD</sub> |     | 5.5              | V    |

| RESET Voltage High                                     | V <sub>IH_RESET</sub>              | Pin Group 2        | 0.7 x V <sub>DD</sub> | _   | V <sub>DD</sub>  | V    |

Table continues on the next page...

#### General

## Table 6. Recommended Operating Conditions (V<sub>REFLx</sub>=0V, V<sub>SSA</sub>=0V, V<sub>SS</sub>=0V) (continued)

| Characteristic                                                                                                     | Symbol          | Notes <sup>1</sup> | Min  | Тур | Max                    | Unit |

|--------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|------|-----|------------------------|------|

| Input Voltage Low (digital inputs)                                                                                 | VIL             | Pin Groups 1, 2    |      |     | 0.35 x V <sub>DD</sub> | V    |

| Oscillator Input Voltage High                                                                                      | VIHOSC          | Pin Group 4        | 2.0  |     | V <sub>DD</sub> + 0.3  | V    |

| XTAL driven by an external clock source                                                                            |                 |                    |      |     |                        |      |

| Oscillator Input Voltage Low                                                                                       | VILOSC          | Pin Group 4        | -0.3 |     | 0.8                    | V    |

| <ul> <li>Output Source Current High (at V<sub>OH</sub> min.)</li> <li>Programmed for low drive strength</li> </ul> | I <sub>ОН</sub> | Pin Group 1        | _    |     | -2                     | mA   |

| Programmed for high drive strength                                                                                 |                 | Pin Group 1        | —    |     | -9                     |      |

| Output Source Current Low (at V <sub>OL</sub> max.) <sup>2, 3</sup><br>• Programmed for low drive strength         | I <sub>OL</sub> | Pin Groups 1, 2    |      |     | 2                      | mA   |

| Programmed for high drive strength                                                                                 |                 | Pin Groups 1, 2    | —    |     | 9                      |      |

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC analog output

- 2. Total IO sink current and total IO source current are limited to 75 mA each

- 3. Contiguous pin DC injection current of regional limit—including sum of negative injection currents or sum of positive injection currents of 16 contiguous pins—is 25 mA.

## 7.3.2 LVD and POR operating requirements

#### Table 7. PMC Low-Voltage Detection (LVD) and Power-On Reset (POR) Parameters

| Characteristic                   | Symbol | Min | Тур  | Max | Unit |

|----------------------------------|--------|-----|------|-----|------|

| POR Assert Voltage <sup>1</sup>  | POR    |     | 2.0  |     | V    |

| POR Release Voltage <sup>2</sup> | POR    |     | 2.7  |     | V    |

| LVI_2p7 Threshold Voltage        |        |     | 2.73 |     | V    |

| LVI_2p2 Threshold Voltage        |        |     | 2.23 |     | V    |

1. During 3.3-volt  $V_{DD}$  power supply ramp down

2. During 3.3-volt  $V_{DD}$  power supply ramp up (gated by LVI\_2p7)

## 7.3.3 Voltage and current operating behaviors

The following table provides information about power supply requirements and I/O pin characteristics.

|                                     |                        | 1                  |                                         |     |                                         | 1    |                                                                |

|-------------------------------------|------------------------|--------------------|-----------------------------------------|-----|-----------------------------------------|------|----------------------------------------------------------------|

| Characteristic                      | Symbol                 | Notes              | Min                                     | Тур | Max                                     | Unit | Test Conditions                                                |

| Output Voltage High                 | V <sub>OH</sub>        | Pin Group 1        | V <sub>DD</sub> - 0.5                   | —   | —                                       | V    | $I_{OH} = I_{OHmax}$                                           |

| Output Voltage Low                  | V <sub>OL</sub>        | Pin Groups<br>1, 2 | _                                       | —   | 0.5                                     | V    | I <sub>OL</sub> = I <sub>OLmax</sub>                           |

| Digital Input Current High          | I <sub>IH</sub>        | Pin Group 1        | —                                       | 0   | +/- 2.5                                 | μA   | V <sub>IN</sub> = 2.4 V to 5.5 V                               |

| pull-up enabled or<br>disabled      |                        | Pin Group 2        |                                         |     |                                         |      | $V_{IN} = 2.4 \text{ V to } V_{DD}$                            |

| Comparator Input Current<br>High    | I <sub>IHC</sub>       | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | $V_{IN} = V_{DDA}$                                             |

| Oscillator Input Current<br>High    | I <sub>IHOSC</sub>     | Pin Group 3        | —                                       | 0   | +/- 2                                   | μA   | $V_{IN} = V_{DDA}$                                             |

| Internal Pull-Up<br>Resistance      | R <sub>Pull-Up</sub>   |                    | 20                                      | —   | 50                                      | kΩ   | —                                                              |

| Internal Pull-Down<br>Resistance    | R <sub>Pull-Down</sub> |                    | 20                                      | —   | 50                                      | kΩ   | —                                                              |

| Comparator Input Current<br>Low     | I <sub>ILC</sub>       | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                           |

| Oscillator Input Current<br>Low     | I <sub>ILOSC</sub>     | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                           |

| DAC Output Voltage<br>Range         | V <sub>DAC</sub>       | Pin Group 5        | Typically<br>V <sub>SSA</sub> +<br>40mV | —   | Typically<br>V <sub>DDA</sub> -<br>40mV | V    | $R_{LD} = 3 \text{ k}\Omega \parallel C_{LD} = 400 \text{ pF}$ |

| Output Current <sup>1</sup>         | I <sub>OZ</sub>        | Pin Groups         | —                                       | 0   | +/- 1                                   | μA   | —                                                              |

| High Impedance State                |                        | 1, 2               |                                         |     |                                         |      |                                                                |

| Schmitt Trigger Input<br>Hysteresis | V <sub>HYS</sub>       | Pin Groups<br>1, 2 | 0.06 x V <sub>DD</sub>                  | —   | —                                       | V    | —                                                              |

| Table 8. | DC Electrical | Characteristics at | Recommended | <b>Operating Cond</b> | litions |

|----------|---------------|--------------------|-------------|-----------------------|---------|

|----------|---------------|--------------------|-------------|-----------------------|---------|

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC

### 7.3.4 Power mode transition operating behaviors

Parameters listed are guaranteed by design.

### NOTE

All address and data buses described here are internal.

#### Table 9. Reset, stop, wait, and interrupt timing

| Characteristic                   | Symbol          | Typical Min     | Typical<br>Max | Unit | See<br>Figure |

|----------------------------------|-----------------|-----------------|----------------|------|---------------|

| Minimum RESET Assertion Duration | t <sub>RA</sub> | 16 <sup>1</sup> | —              | ns   | _             |

Table continues on the next page ...

## 8.2 System modules

## 8.2.1 Voltage regulator specifications

The voltage regulator supplies approximately 1.2 V to the MC56F82xxx's core logic. For proper operations, the voltage regulator requires an external 2.2  $\mu$ F capacitor on each V<sub>CAP</sub> pin. Ceramic and tantalum capacitors tend to provide better performance tolerances. The output voltage can be measured directly on the V<sub>CAP</sub> pin. The specifications for this regulator are shown in Table 17.

| Characteristic                                               | Symbol           | Min | Тур  | Max | Unit    |

|--------------------------------------------------------------|------------------|-----|------|-----|---------|

| Output Voltage <sup>1</sup>                                  | V <sub>CAP</sub> | —   | 1.22 | _   | V       |

| Short Circuit Current <sup>2</sup>                           | I <sub>SS</sub>  | —   | 600  | —   | mA      |

| Short Circuit Tolerance (V <sub>CAP</sub> shorted to ground) | T <sub>RSC</sub> | —   | —    | 30  | Minutes |

Table 17.

Regulator 1.2 V parameters

1. Value is after trim

2. Guaranteed by design

#### Table 18. Bandgap electrical specifications

| Characteristic                 | Symbol           | Min | Тур  | Max | Unit |

|--------------------------------|------------------|-----|------|-----|------|

| Reference Voltage (after trim) | V <sub>REF</sub> | —   | 1.21 | —   | V    |

## 8.3 Clock modules

## 8.3.1 External clock operation timing

Parameters listed are guaranteed by design.

#### Table 19. External clock operation timing requirements

| Characteristic                                              | Symbol            | Min                 | Тур | Max                | Unit |

|-------------------------------------------------------------|-------------------|---------------------|-----|--------------------|------|

| Frequency of operation (external clock driver) <sup>1</sup> | f <sub>osc</sub>  | —                   | —   | 50                 | MHz  |

| Clock pulse width <sup>2</sup>                              | t <sub>PW</sub>   | 8                   |     |                    | ns   |

| External clock input rise time <sup>3</sup>                 | t <sub>rise</sub> | —                   | —   | 1                  | ns   |

| External clock input fall time <sup>4</sup>                 | t <sub>fall</sub> | —                   | —   | 1                  | ns   |

| Input high voltage overdrive by an external clock           | V <sub>ih</sub>   | 0.85V <sub>DD</sub> | —   | —                  | V    |

| Input low voltage overdrive by an external clock            | V <sub>il</sub>   | —                   | —   | 0.3V <sub>DD</sub> | V    |

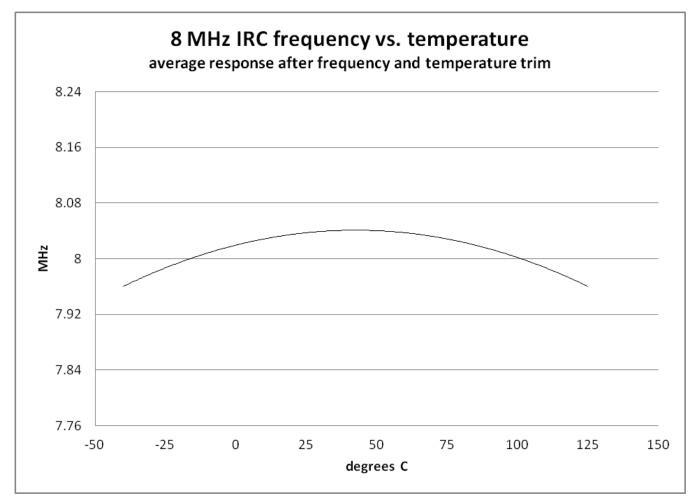

Figure 8. Relaxation Oscillator Temperature Variation (Typical) After Trim (Preliminary)

# 8.4 Memories and memory interfaces

## 8.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

### 8.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Table 23. | NVM program/erase timing specifications |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Symbol              | Description                        | Min. | Тур. | Max. | Unit | Notes |

|---------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub> | Longword Program high-voltage time |      | 7.5  | 18   | μs   | _     |

Table continues on the next page ...

System modules

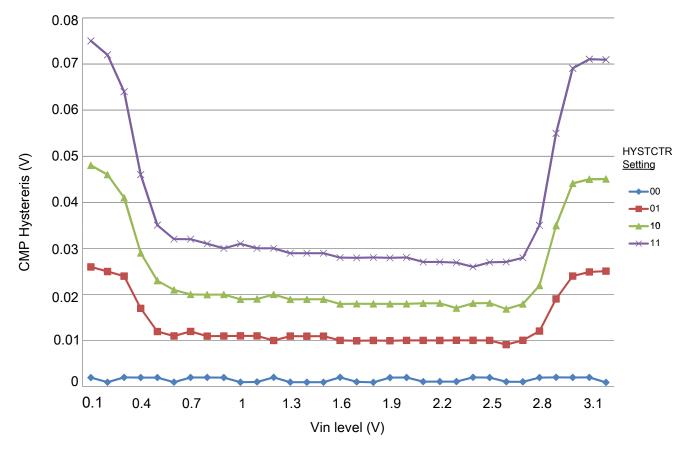

Figure 10. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 0)

## 8.7.2 Queued Serial Communication Interface (SCI) timing

Parameters listed are guaranteed by design.

| Characteristic                                                                              | Symbol                   | Min        | Мах                    | Unit                          | See Figure |

|---------------------------------------------------------------------------------------------|--------------------------|------------|------------------------|-------------------------------|------------|

| Baud rate <sup>1</sup>                                                                      | BR                       | —          | (f <sub>MAX</sub> /16) | Mbit/s                        | —          |

| RXD pulse width                                                                             | RXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 17  |

| TXD pulse width                                                                             | TXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 18  |

|                                                                                             | LIN                      | Slave Mode |                        |                               |            |

| Deviation of slave node clock from nominal<br>clock rate before synchronization             | F <sub>TOL_UNSYNCH</sub> | -14        | 14                     | %                             | _          |

| Deviation of slave node clock relative to<br>the master node clock after<br>synchronization | F <sub>TOL_SYNCH</sub>   | -2         | 2                      | %                             | _          |

| Minimum break character length                                                              | T <sub>BREAK</sub>       | 13         | —                      | Master<br>node bit<br>periods | _          |

|                                                                                             |                          | 11         | —                      | Slave node bit periods        | _          |

#### Table 33. SCI timing

1. f<sub>MAX</sub> is the frequency of operation of the SCI clock in MHz, which can be selected as the bus clock (max.50 MHz depending on part number) or 2x bus clock (max. 100 MHz) for the devices.

#### Figure 18. TXD pulse width

### 8.7.3 Modular/Scalable Controller Area Network (MSCAN) Table 34. MSCAN Timing Parameters

| Characteristic                     | Symbol              | Min | Max | Unit   |

|------------------------------------|---------------------|-----|-----|--------|

| Baud Rate                          | BR <sub>CAN</sub>   | —   | 1   | Mbit/s |

| CAN Wakeup dominant pulse filtered | T <sub>WAKEUP</sub> | —   | 1.5 | μs     |

| CAN Wakeup dominant pulse pass     | T <sub>WAKEUP</sub> | 5   | —   | μs     |

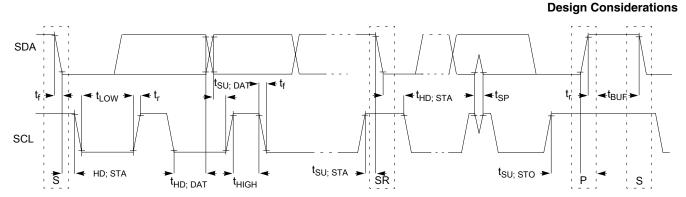

Figure 20. Timing definition for fast and standard mode devices on the I<sup>2</sup>C bus

# 9 Design Considerations

## 9.1 Thermal design considerations

An estimate of the chip junction temperature (TJ) can be obtained from the equation:

$$T_J = T_A + (R_{\Theta JA} \times P_D)$$

Where,

$T_A$  = Ambient temperature for the package (°C)

$R_{\Theta IA}$  = Junction-to-ambient thermal resistance (°C/W)

$P_D$  = Power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single-layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which TJ value is closer to the application depends on the power dissipated by other components on the board.

- The TJ value obtained on a single layer board is appropriate for a tightly packed printed circuit board.

- The TJ value obtained on a board with the internal planes is usually appropriate if the board has low-power dissipation and if the components are well separated.

When a heat sink is used, the thermal resistance is expressed as the sum of a junction-tocase thermal resistance and a case-to-ambient thermal resistance:

$$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CA}$$

Where,

**Design Considerations**

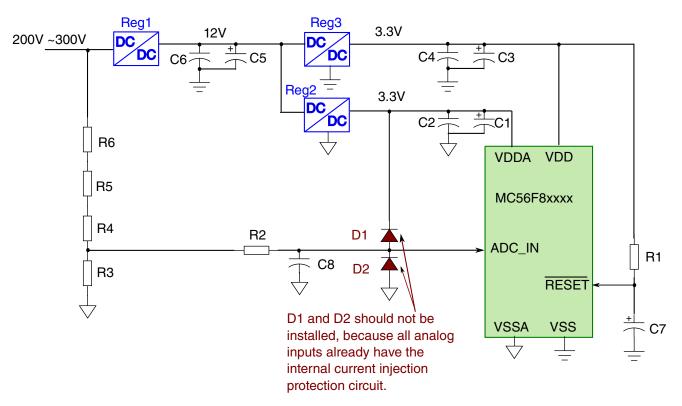

Figure 21. Protection Circuit Example

MC56F8xxxx DSC uses the 5V tolerance I/O. When the pin is configured to digital input, it can accept 5V input. Table 5. When the pin is configured to analog input, the internal integrated current injection protection circuit is enabled. The current injection protection circuit performs the same functions as external clamp diode D1 and D2 in Figure 21. As long as the source or sink current for each analog pin is less than 3 mA, then there is no damage to the device. See Table 27.

This situation could happen if diodes D1 or D2 are used for clamping; therefore in this case, the D1 and D2 clamping diodes are not recommended to be used.

### NOTE

In some designs, VDD and VDDA are powered from the same power supply. In this case, above analysis and suggestions are also applicatble.

## 9.3.3 Heavy capacitive load on power supply output:

In some applications, the low cost DC/DC converter may not regulate the output voltage well before it reaches the regulation point, which is roughly around 2.5V to 2.7V. However, the MC56F8xxxx DSC will exit power-on reset at around 2.3V. If the initialization code enables the PLL to run the DSC at full speed right after reset, then the