#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800EX                                                               |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 100MHz                                                                |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | DMA, POR, PWM, WDT                                                    |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 64KB (32K x 16)                                                       |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 16                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                           |

| Data Converters            | A/D 6x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f82743vlc |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                        |            | MC56F82    |            |            |            |            |            |            |            |            |            |            |

|--------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Part Number <sup>1</sup>       | 748V<br>LH | 746V<br>LF | 743V<br>LC | 743V<br>FM | 738V<br>LH | 736V<br>LF | 733V<br>LC | 733V<br>FM | 728V<br>LH | 726V<br>LF | 723V<br>LC | 723V<br>FM |

|                                |            | 746M<br>LF |            |            |            |            |            | 733M<br>FM |            |            |            |            |

| Analog<br>Comparators<br>(CMP) | 4          | 4          | 3          | 3          | 4          | 4          | 3          | 3          | 4          | 4          | 3          | 3          |

| QSCI                           | 2          | 2          | 1          | 1          | 2          | 2          | 1          | 1          | 2          | 2          | 1          | 1          |

| QSPI                           | 2          | 1          | 1          | 1          | 2          | 1          | 1          | 1          | 2          | 1          | 1          | 1          |

| I2C/SMBus                      | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| MSCAN                          | 1          | 1          | 0          | 0          | 1          | 1          | 0          | 0          | 1          | 1          | 0          | 0          |

| GPIO                           | 54         | 39         | 26         | 26         | 54         | 39         | 26         | 26         | 54         | 39         | 26         | 26         |

| Package pin count              | 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | 32<br>QFN  | 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | 32<br>QFN  | 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | 32<br>QFN  |

| AEC-Q100 <sup>3</sup>          | Yes        | Yes        | No         | No         | Yes        | Yes        | No         | No         | Yes        | Yes        | No         | No         |

Table 1. MC56F827xx Family (continued)

1. Temperature options

V: -40°C to 105°C

M: -40°C to 125°C

2. Input capture shares the pin with cooresponding PWM channels.

3. Qualification aligned to AEC-Q100

# 1.2 56800EX 32-bit Digital Signal Controller (DSC) core

- Efficient 32-bit 56800EX Digital Signal Processor (DSP) engine with modified dual Harvard architecture:

- Three internal address buses

- Four internal data buses: two 32-bit primary buses, one 16-bit secondary data bus, and one 16-bit instruction bus

- 32-bit data accesses

- Supports concurrent instruction fetches in the same cycle, and dual data accesses in the same cycle

- 20 addressing modes

- As many as 100 million instructions per second (MIPS) at 100 MHz core frequency

- 162 basic instructions

- Instruction set supports both fractional arithmetic and integer arithmetic

- 32-bit internal primary data buses support 8-bit, 16-bit, and 32-bit data movement, plus addition, subtraction, and logical operations

- Single-cycle 16 × 16-bit -> 32-bit and 32 x 32-bit -> 64-bit multiplier-accumulator (MAC) with dual parallel moves

- 32-bit arithmetic and logic multi-bit shifter

- Four 36-bit accumulators, including extension bits

- Up to 64 KB program/data flash memory

- Up to 8 KB dual port data/program RAM

# 1.5 Interrupt Controller

- Five interrupt priority levels

- Three user-programmable priority levels for each interrupt source: level 0, level 1, level 2

- Unmaskable level 3 interrupts include illegal instruction, hardware stack overflow, misaligned data access, SWI3 instruction

- Interrupt level 3 is highest priority and non-maskable. Its sources include:

- Illegal instructions

- Hardware stack overflow

- SWI instruction

- EOnce interrupts

- Misaligned data accesses

- Lowest-priority software interrupt: level LP

- Support for nested interrupts, so that a higher priority level interrupt request can interrupt lower priority interrupt subroutine

- Masking of interrupt priority level is managed by the 56800EX core

- Two programmable fast interrupts that can be assigned to any interrupt source

- Notification to System Integration Module (SIM) to restart clock when in wait and stop states

- Ability to relocate interrupt vector table

# **1.6** Peripheral highlights

# 1.6.1 Enhanced Flex Pulse Width Modulator (eFlexPWM)

- 16 bits of resolution for center, edge-aligned, and asymmetrical PWMs

- PWM outputs can be configured as complementary output pairs or independent outputs

- Dedicated time-base counter with period and frequency control per submodule

- Independent top and bottom deadtime insertion for each complementary pair

- Independent control of both edges of each PWM output

- Enhanced input capture and output compare functionality on each input:

- Channels not used for PWM generation can be used for buffered output compare functions.

- Programmable length transmissions (2 bits to 16 bits)

- Programmable transmit and receive shift order (MSB as first bit transmitted)

# 1.6.10 Inter-Integrated Circuit (I2C)/System Management Bus (SMBus) modules

- Compatible with I2C bus standard

- Support for System Management Bus (SMBus) specification, version 2

- Multi-master operation

- General call recognition

- 10-bit address extension

- Start/Repeat and Stop indication flags

- Support for dual slave addresses or configuration of a range of slave addresses

- Programmable glitch input filter with option to clock up to 100 MHz

### 1.6.11 Modular/Scalable Controller Area Network (MSCAN) Module

- Clock source from PLL or oscillator.

- Implementation of the CAN protocol Version 2.0 A/B

- Standard and extended data frames

- 0-to-8 bytes data length

- Programmable bit rate up to 1 Mbit/s

- Support for remote frames

- Individual Rx Mask Registers per Message Buffer

- Internal timer for time-stamping of received and transmitted messages

- Listen-only mode capability

- Programmable loopback mode supporting self-test operation

- Programmable transmission priority scheme: lowest ID, lowest buffer number, or highest priority

- Low power modes, with programmable wakeup on bus activity

# 1.6.12 Windowed Computer Operating Properly (COP) watchdog

- Programmable windowed timeout period

- Support for operation in all power modes: run mode, wait mode, stop mode

- Causes loss of reference reset 128 cycles after loss of reference clock to the PLL is detected

- Selectable reference clock source in support of EN60730 and IEC61508

- Selectable clock sources:

- External crystal oscillator/external clock source

#### Peripheral highlights

- On-chip low-power 200 kHz oscillator

- System bus (IPBus up to 50 MHz)

- 8 MHz / 400 kHz ROSC

- Support for interrupt triggered when the counter reaches the timeout value

### **1.6.13 External Watchdog Monitor (EWM)**

- Monitors external circuit as well as the software flow

- Programmable timeout period

- Interrupt capability prior to timeout

- Independent output (EWM\_OUT\_b) that places external circuit (but not CPU and peripheral) in a safe mode when EWM timeout occurs

- Selectable reference clock source in support of EN60730 and IEC61508

- Wait mode and Stop mode operation is not supported.

- Selectable clock sources:

- External crystal oscillator/external clock source

- On-chip low-power 200 kHz oscillator

- System bus (IPBus up to 50 MHz)

- 8 MHz / 400 kHz ROSC

### 1.6.14 Power supervisor

- Power-on reset (POR) to reset CPU, peripherals, and JTAG/EOnCE controllers (V<sub>DD</sub> > 2.1 V)

- Brownout reset ( $V_{DD} < 1.9 \text{ V}$ )

- Critical warn low-voltage interrupt (LVI2.0)

- Peripheral low-voltage interrupt (LVI2.7)

### 1.6.15 Phase-locked loop

- Wide programmable output frequency: 200 MHz to 400 MHz

- Input reference clock frequency: 8 MHz to 16 MHz

- Detection of loss of lock and loss of reference clock

- Ability to power down

#### MC56F827xx signal and pin descriptions

| Signal Name                | 64 LQFP | 48 LQFP | 32 LQFP | Туре             | State During<br>Reset          | Signal Description                                                                                                                                                                                                               |

|----------------------------|---------|---------|---------|------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DACB_O                     |         |         |         | Analog<br>Output |                                | 12-bit digital-to-analog output                                                                                                                                                                                                  |

| GPIOB2                     | 27      | 20      | 13      | Input/Output     | Input, internal pullup enabled | GPIO Port B2: After reset, the default state is GPIOB2.                                                                                                                                                                          |

| (ANB2&VERFHB<br>&CMPC_IN3) |         |         |         | Input            |                                | ANB2 is analog input to channel 2 of<br>ADCB; VREFHB is analog reference<br>high of ADCB; CMPC_IN3 is positive<br>input 3 of analog comparator C. When<br>used as an analog input, the signal goes<br>to both ANB2 and CMPC_IN3. |

| GPIOB3                     | 28      | 21      | _       | Input/Output     | Input, internal pullup enabled | GPIO Port B3: After reset, the default state is GPIOB3.                                                                                                                                                                          |

| (ANB3&VREFLB&<br>CMPC_IN0) |         |         |         | Input            | -                              | ANB3 is analog input to channel 3 of<br>ADCB; VREFLB is analog reference low<br>of ADCB; CMPC_IN0 is negative input 0<br>of analog comparator C.                                                                                 |

| GPIOB4                     | 21      | 14      | —       | Input/Output     | Input, internal pullup enabled | GPIO Port B4: After reset, the default state is GPIOB4.                                                                                                                                                                          |

| (ANB4&CMPC_IN<br>1)        |         |         |         | Input            |                                | ANB4 is analog input to channel 4 of<br>ADCB; CMPC_IN1 is negative input 1 of<br>analog comparator C.                                                                                                                            |

| GPIOB5                     | 20      |         | _       | Input/Output     | Input, internal pullup enabled | GPIO Port B5: After reset, the default state is GPIOB5.                                                                                                                                                                          |

| (ANB5&CMPC_IN<br>2)        |         |         |         | Input            | -                              | ANB5 is analog input to channel 5 of<br>ADCB; CMPC_IN2 is negative input 2 of<br>analog comparator C.                                                                                                                            |

| GPIOB6                     | 19      |         | —       | Input/Output     | Input, internal pullup enabled | GPIO Port B6: After reset, the default state is GPIOB6.                                                                                                                                                                          |

| (ANB6&CMPB_IN<br>1)        |         |         |         | Input            |                                | ANB6 is analog input to channel 6 of<br>ADCB; CMPB_IN1 is negative input 1 of<br>analog comparator B.                                                                                                                            |

| GPIOB7                     | 17      |         | —       | Input/Output     | Input, internal pullup enabled | GPIO Port B7: After reset, the default state is GPIOB7.                                                                                                                                                                          |

| (ANB7&CMPB_IN<br>2)        |         |         |         | Input            |                                | ANB7 is analog input to channel 7 of<br>ADCB; CMPB_IN2 is negative input 2 of<br>analog comparator B.                                                                                                                            |

| GPIOC0                     | 3       | 3       | —       | Input/Output     | Input, internal pullup enabled | GPIO Port C0: After reset, the default state is GPIOC0.                                                                                                                                                                          |

| (EXTAL)                    |         |         |         | Analog Input     |                                | The external crystal oscillator input<br>(EXTAL) connects the internal crystal<br>oscillator input to an external crystal or<br>ceramic resonator.                                                                               |

| (CLKIN0)                   |         |         |         | Input            |                                | External clock input 0 <sup>1</sup>                                                                                                                                                                                              |

| GPIOC1                     | 4       | 4       | _       | Input/Output     | Input, internal pullup enabled | GPIO Port C1: After reset, the default state is GPIOC1.                                                                                                                                                                          |

| (XTAL)                     |         |         |         | Input            | ]                              | The external crystal oscillator output (XTAL) connects the internal crystal                                                                                                                                                      |

Table 2. Signal descriptions (continued)

Table continues on the next page...

#### MC56F827xx signal and pin descriptions

| Signal Name      | 64 LQFP | 48 LQFP | 32 LQFP | Туре                        | State During<br>Reset          | Signal Description                                                                                                                                                                                                                                 |

|------------------|---------|---------|---------|-----------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ( <u>SS0_B</u> ) |         |         |         | Input/Output                |                                | In slave mode, SS0_B indicates to the SPI module 0 that the current transfer is to be received.                                                                                                                                                    |

| (TXD0)           |         |         |         | Output                      |                                | SCI0 transmit data output or transmit/<br>receive in single wire operation                                                                                                                                                                         |

| (XB_IN8)         |         |         |         | Input                       |                                | Crossbar module input 8                                                                                                                                                                                                                            |

| GPIOC8           | 33      | 25      | 16      | Input/Output                | Input, internal pullup enabled | GPIO Port C8: After reset, the default state is GPIOC8.                                                                                                                                                                                            |

| (MISO0)          |         |         |         | Input/Output                |                                | Master in/slave out for SPI0 — In master<br>mode, MISO0 pin is the data input. In<br>slave mode, MISO0 pin is the data<br>output. The MISO line of a slave device<br>is placed in the high-impedance state if<br>the slave device is not selected. |

| (RXD0)           | -       |         |         | Input                       | -                              | SCI0 receive data input                                                                                                                                                                                                                            |

| (XB_IN9)         | _       |         |         | Input                       | -                              | Crossbar module input 9                                                                                                                                                                                                                            |

| (XB_OUT6)        | -       |         |         | Output                      | -                              | Crossbar module output 6                                                                                                                                                                                                                           |

| GPIOC9           | 34      | 26      | 17      | Input/Output                | Input, internal pullup enabled | GPIO Port C9: After reset, the default state is GPIOC9.                                                                                                                                                                                            |

| (SCLK0)          |         |         |         | Input/Output                | -                              | SPI0 serial clock. In master mode,<br>SCLK0 pin is an output, clocking slaved<br>listeners. In slave mode, SCLK0 pin is<br>the data clock input.                                                                                                   |

| (XB_IN4)         | _       |         |         | Input                       |                                | Crossbar module input 4                                                                                                                                                                                                                            |

| (TXD0)           |         |         |         | Output                      | -                              | SCI0 transmit data output or transmit/<br>receive in single wire operation                                                                                                                                                                         |

| (XB_OUT8)        |         |         |         | Output                      |                                | Crossbar module output 8                                                                                                                                                                                                                           |

| GPIOC10          | 35      | 27      | 18      | Input/Output                | Input, internal pullup enabled | GPIO Port C10: After reset, the default state is GPIOC10.                                                                                                                                                                                          |

| (MOSI0)          |         |         |         | Input/Output                |                                | Master out/slave in for SPI0 — In master mode, MOSI0 pin is the data output. In slave mode, MOSI0 pin is the data input.                                                                                                                           |

| (XB_IN5)         |         |         |         | Input                       |                                | Crossbar module input 4                                                                                                                                                                                                                            |

| (MISO0)          |         |         |         | Input/Output                |                                | Master in/slave out for SPI0 — In master<br>mode, MISO0 pin is the data input. In<br>slave mode, MISO0 pin is the data<br>output. The MISO line of a slave device<br>is placed in the high-impedance state if<br>the slave device is not selected. |

| (XB_OUT9)        | 1       |         |         | Output                      | 1                              | Crossbar module output 9                                                                                                                                                                                                                           |

| GPIOC11          | 37      | 29      | -       | Input/Output                | Input, internal pullup enabled | GPIO Port C11: After reset, the default state is GPIOC11.                                                                                                                                                                                          |

| (CANTX)          | 1       |         |         | Open-drain<br>Output        |                                | CAN transmit data output                                                                                                                                                                                                                           |

| (SCL0)           |         |         |         | Input/Open-<br>drain Output | ]                              | I <sup>2</sup> C0 serial clock                                                                                                                                                                                                                     |

Table 2. Signal descriptions (continued)

Table continues on the next page...

# 5.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

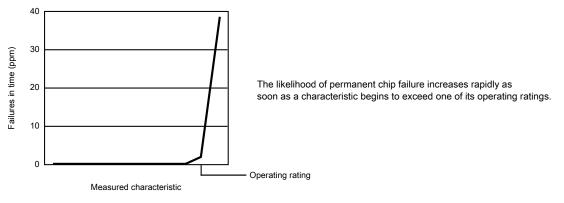

# 5.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

### 5.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

# 5.5 Result of exceeding a rating

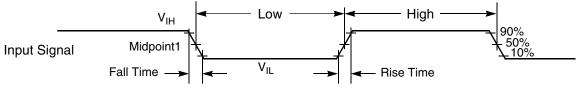

The midpoint is  $V_{IL} + (V_{IH} - V_{IL})/2$ .

### Figure 3. Input signal measurement references

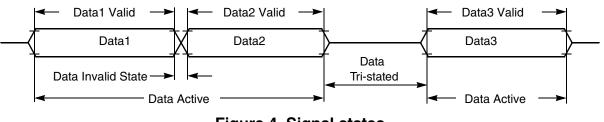

Figure 4 shows the definitions of the following signal states:

- Active state, when a bus or signal is driven, and enters a low impedance state

- Tri-stated, when a bus or signal is placed in a high impedance state

- Data Valid state, when a signal level has reached  $V_{OL}$  or  $V_{OH}$

- Data Invalid state, when a signal level is in transition between  $V_{OL}$  and  $V_{OH}$

Figure 4. Signal states

# 7.3 Nonswitching electrical specifications

### 7.3.1 Voltage and current operating requirements

This section includes information about recommended operating conditions.

**NOTE** Recommended  $V_{DD}$  ramp rate is between 1 ms and 200 ms.

| Table 6. | Recommended Operating Conditions (V <sub>REFLx</sub> =0V, V <sub>SSA</sub> =0V, V <sub>SS</sub> =0V) |

|----------|------------------------------------------------------------------------------------------------------|

|----------|------------------------------------------------------------------------------------------------------|

| Characteristic                                         | Symbol                             | Notes <sup>1</sup> | Min                   | Тур | Max              | Unit |

|--------------------------------------------------------|------------------------------------|--------------------|-----------------------|-----|------------------|------|

| Supply voltage                                         | V <sub>DD</sub> , V <sub>DDA</sub> |                    | 2.7                   | 3.3 | 3.6              | V    |

| ADC (Cyclic) Reference Voltage High                    | V <sub>REFHA</sub>                 |                    | V <sub>DDA</sub> -0.6 |     | V <sub>DDA</sub> | V    |

|                                                        | V <sub>REFHB</sub>                 |                    |                       |     |                  |      |

| Voltage difference V <sub>DD</sub> to V <sub>DDA</sub> | ΔVDD                               |                    | -0.1                  | 0   | 0.1              | V    |

| Voltage difference V <sub>SS</sub> to V <sub>SSA</sub> | ΔVSS                               |                    | -0.1                  | 0   | 0.1              | V    |

| Input Voltage High (digital inputs)                    | V <sub>IH</sub>                    | Pin Group 1        | 0.7 x V <sub>DD</sub> |     | 5.5              | V    |

| RESET Voltage High                                     | V <sub>IH_RESET</sub>              | Pin Group 2        | 0.7 x V <sub>DD</sub> | —   | V <sub>DD</sub>  | V    |

Table continues on the next page...

|                                     |                        | 1                  |                                         |     |                                         | 1    |                                                                |

|-------------------------------------|------------------------|--------------------|-----------------------------------------|-----|-----------------------------------------|------|----------------------------------------------------------------|

| Characteristic                      | Symbol                 | Notes              | Min                                     | Тур | Max                                     | Unit | Test Conditions                                                |

| Output Voltage High                 | V <sub>OH</sub>        | Pin Group 1        | V <sub>DD</sub> - 0.5                   | —   | —                                       | V    | $I_{OH} = I_{OHmax}$                                           |

| Output Voltage Low                  | V <sub>OL</sub>        | Pin Groups<br>1, 2 | _                                       | —   | 0.5                                     | V    | I <sub>OL</sub> = I <sub>OLmax</sub>                           |

| Digital Input Current High          | I <sub>IH</sub>        | Pin Group 1        | —                                       | 0   | +/- 2.5                                 | μA   | V <sub>IN</sub> = 2.4 V to 5.5 V                               |

| pull-up enabled or<br>disabled      |                        | Pin Group 2        |                                         |     |                                         |      | $V_{IN} = 2.4 \text{ V to } V_{DD}$                            |

| Comparator Input Current<br>High    | I <sub>IHC</sub>       | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | $V_{IN} = V_{DDA}$                                             |

| Oscillator Input Current<br>High    | I <sub>IHOSC</sub>     | Pin Group 3        | —                                       | 0   | +/- 2                                   | μA   | $V_{IN} = V_{DDA}$                                             |

| Internal Pull-Up<br>Resistance      | R <sub>Pull-Up</sub>   |                    | 20                                      | —   | 50                                      | kΩ   | —                                                              |

| Internal Pull-Down<br>Resistance    | R <sub>Pull-Down</sub> |                    | 20                                      | —   | 50                                      | kΩ   | —                                                              |

| Comparator Input Current<br>Low     | I <sub>ILC</sub>       | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                           |

| Oscillator Input Current<br>Low     | I <sub>ILOSC</sub>     | Pin Group 3        | _                                       | 0   | +/- 2                                   | μA   | V <sub>IN</sub> = 0V                                           |

| DAC Output Voltage<br>Range         | V <sub>DAC</sub>       | Pin Group 5        | Typically<br>V <sub>SSA</sub> +<br>40mV | —   | Typically<br>V <sub>DDA</sub> -<br>40mV | V    | $R_{LD} = 3 \text{ k}\Omega \parallel C_{LD} = 400 \text{ pF}$ |

| Output Current <sup>1</sup>         | I <sub>OZ</sub>        | Pin Groups         | —                                       | 0   | +/- 1                                   | μA   | —                                                              |

| High Impedance State                |                        | 1, 2               |                                         |     |                                         |      |                                                                |

| Schmitt Trigger Input<br>Hysteresis | V <sub>HYS</sub>       | Pin Groups<br>1, 2 | 0.06 x V <sub>DD</sub>                  | —   | —                                       | V    | —                                                              |

| Table 8. | DC Electrical | Characteristics at | Recommended | <b>Operating Conditions</b> |

|----------|---------------|--------------------|-------------|-----------------------------|

|----------|---------------|--------------------|-------------|-----------------------------|

#### 1. Default Mode

- Pin Group 1: GPIO, TDI, TDO, TMS, TCK

- Pin Group 2: RESET

- Pin Group 3: ADC and Comparator Analog Inputs

- Pin Group 4: XTAL, EXTAL

- Pin Group 5: DAC

### 7.3.4 Power mode transition operating behaviors

Parameters listed are guaranteed by design.

### NOTE

All address and data buses described here are internal.

### Table 9. Reset, stop, wait, and interrupt timing

| Characteristic                   | Symbol          | Typical Min     | Typical<br>Max | Unit | See<br>Figure |

|----------------------------------|-----------------|-----------------|----------------|------|---------------|

| Minimum RESET Assertion Duration | t <sub>RA</sub> | 16 <sup>1</sup> | —              | ns   | _             |

Table continues on the next page ...

#### General

Table 9. Reset, stop, wait, and interrupt timing (continued)

| Characteristic                                                              | Symbol           | Typical Min                    | Typical<br>Max | Unit | See<br>Figure |

|-----------------------------------------------------------------------------|------------------|--------------------------------|----------------|------|---------------|

| RESET deassertion to First Address Fetch                                    | t <sub>RDA</sub> | 865 x T <sub>OSC</sub> + 8 x T |                | ns   | —             |

| Delay from Interrupt Assertion to Fetch of first instruction (exiting Stop) | t <sub>IF</sub>  | 361.3                          | 570.9          | ns   | —             |

1. If the RESET pin filter is enabled by setting the RST\_FLT bit in the SIM\_CTRL register to 1, the minimum pulse assertion must be greater than 21 ns. Recommended a capacitor of up to 0.1 μF on RESET.

### NOTE

In Table 9, T = system clock cycle and  $T_{OSC}$  = oscillator clock cycle. For an operating frequency of 50MHz, T=20 ns. At 4 MHz (used coming out of reset and stop modes), T=250 ns.

### Table 10. Power mode transition behavior

| Symbol           | Description                                                                                                                                                   | Min   | Max     | Unit | Notes <sup>1</sup> |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|------|--------------------|

| T <sub>POR</sub> | After a POR event, the amount of delay from when V <sub>DD</sub> reaches 2.7 V to when the first instruction executes (over the operating temperature range). | 199   | 225     | μs   |                    |

|                  | STOP mode to RUN mode                                                                                                                                         | 6.79  | 7.27.31 | μs   | 2                  |

|                  | LPS mode to LPRUN mode                                                                                                                                        | 240.9 | 551     | μs   | 3                  |

|                  | VLPS mode to VLPRUN mode                                                                                                                                      | 1424  | 1459    | μs   | 4                  |

|                  | WAIT mode to RUN mode                                                                                                                                         | 0.570 | 0.620   | μs   | 5                  |

|                  | LPWAIT mode to LPRUN mode                                                                                                                                     | 237.2 | 554     | μs   | 3                  |

|                  | VLPWAIT mode to VLPRUN mode                                                                                                                                   | 1413  | 1500    | μs   | 4                  |

1. Wakeup times are measured from GPIO toggle for wakeup till GPIO toggle at the wakeup interrupt subroutine from respective stop/wait mode.

- 2. Clock configuration: CPU clock=4 MHz. System clock source is 8 MHz IRC in normal mode.

- 3. CPU clock = 200 KHz and 8 MHz IRC on standby. Exit by an interrupt on PORTC GPIO.

- 4. Using 64 KHz external clock; CPU Clock = 32KHz. Exit by an interrupt on PortC GPIO.

- 5. Clock configuration: CPU and system clocks= 100 MHz. Bus Clock = 50 MHz. .Exit by interrupt on PORTC GPIO

### 7.3.5 Power consumption operating behaviors Table 11. Current Consumption (mA)

| Mode | Maximum<br>Frequency | Conditions                                                                                                                                     | 3.3                          | cal at<br>3 V,<br>5°C | at 3              | mum<br>.6 V,<br>5°C | at 3              | imum<br>8.6V,<br>5°C |

|------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-------------------|---------------------|-------------------|----------------------|

|      |                      |                                                                                                                                                | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub>      | I <sub>DD</sub> 1 | I <sub>DDA</sub>    | I <sub>DD</sub> 1 | I <sub>DDA</sub>     |

| RUN1 | 100 MHz              | <ul> <li>100 MHz Core</li> <li>50 MHz Peripheral clock</li> <li>Regulators are in full regulation</li> <li>Relaxation Oscillator on</li> </ul> | 38.1                         | 9.9                   | 53.5              | 13.2                | 53.5              | 13.2                 |

Table continues on the next page ...

| Mode | Maximum<br>Frequency | Conditions                                                                                                                 | 3.3                          | cal at<br>3 V,<br>5°C | at 3              | mum<br>.6 V,<br>5°C | at 3              | mum<br>8.6V,<br>5°C |

|------|----------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------|-------------------|---------------------|-------------------|---------------------|

|      |                      |                                                                                                                            | I <sub>DD</sub> <sup>1</sup> | I <sub>DDA</sub>      | I <sub>DD</sub> 1 | I <sub>DDA</sub>    | I <sub>DD</sub> 1 | I <sub>DDA</sub>    |

|      |                      | <ul> <li>All peripheral modules, except COP, disabled and clocks gated off</li> <li>Processor core in stop mode</li> </ul> |                              |                       |                   |                     |                   |                     |

Table 11. Current Consumption (mA)

- 1. No output switching, all ports configured as inputs, all inputs low, no DC loads.

- In all chip LP modes and flash memory VLP modes, the maximum frequency for flash memory operation is 500 kHz due to the fixed frequency ratio of 1:2 between the CPU clock and the flash clock when running with 2 MHz external clock input and CPU running at 1 MHz.

### 7.3.6 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

### 7.3.7 Capacitance attributes

Table 12.

Capacitance attributes

| Description        | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------|------------------|------|------|------|------|

| Input capacitance  | C <sub>IN</sub>  | —    | 10   | —    | pF   |

| Output capacitance | C <sub>OUT</sub> | _    | 10   | _    | pF   |

# 7.4 Switching specifications

### 7.4.1 Device clock specifications

Table 13. Device clock specifications

| Symbol           | Description                                                                                                                   | Min.  | Max.       | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-------|

|                  | Normal run mod                                                                                                                | e     |            |      |       |

| fsysclk          | Device (system and core) clock frequency <ul> <li>using relaxation oscillator</li> <li>using external clock source</li> </ul> | 0.001 | 100<br>100 | MHz  |       |

| f <sub>BUS</sub> | Bus clock                                                                                                                     | _     | 50         | MHz  |       |

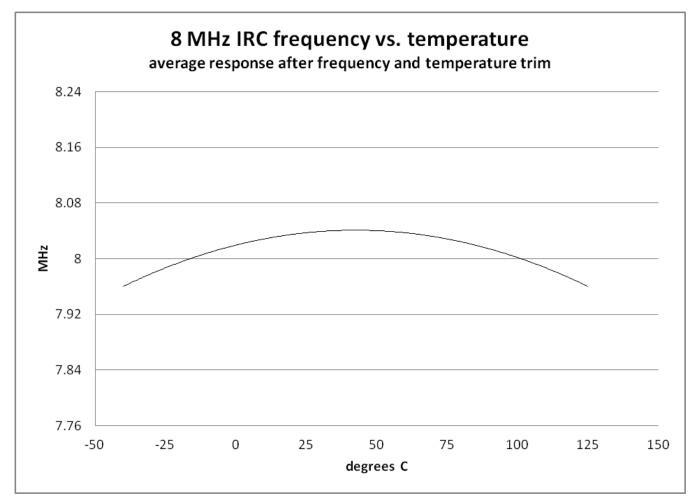

Figure 8. Relaxation Oscillator Temperature Variation (Typical) After Trim (Preliminary)

# 8.4 Memories and memory interfaces

### 8.4.1 Flash electrical specifications

This section describes the electrical characteristics of the flash memory module.

### 8.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Table 23. | NVM program/erase timing specifications |

|-----------|-----------------------------------------|

|-----------|-----------------------------------------|

| Symbol              | Description                        | Min. | Тур. | Max. | Unit | Notes |

|---------------------|------------------------------------|------|------|------|------|-------|

| t <sub>hvpgm4</sub> | Longword Program high-voltage time |      | 7.5  | 18   | μs   | _     |

Table continues on the next page ...

| Symbol                | Description                    | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|--------------------------------|------|------|------|------|-------|

| t <sub>hversscr</sub> | Sector Erase high-voltage time | —    | 13   | 113  | ms   | 1     |

| t <sub>hversall</sub> | Erase All high-voltage time    | _    | 52   | 452  | ms   | 1     |

### Table 23. NVM program/erase timing specifications (continued)

1. Maximum time based on expectations at cycling end-of-life.

### 8.4.1.2 Flash timing specifications — commands Table 24. Flash command timing specifications

| Symbol                | Description                                   | Min.     | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|----------|------|------|------|-------|

| t <sub>rd1sec1k</sub> | Read 1s Section execution time (flash sector) |          | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | _        | —    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | —        | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | _        | 65   | 145  | μs   |       |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | —        | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | _        | —    | 0.9  | ms   | 1     |

| t <sub>rdonce</sub>   | Read Once execution time                      | _        | _    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | _        | 65   | _    | μs   |       |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | —        | 70   | 575  | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | <u> </u> | _    | 30   | μs   | 1     |

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

### 8.4.1.3 Flash high voltage current behaviors Table 25. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation |      | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

### 8.4.1.4 Reliability specifications Table 26. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Program                                | m Flash |                   |      |        |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | _    | years  | _     |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | _    | years  | _     |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              |      | cycles | 2     |

#### System modules

- Typical data retention values are based on measured response accelerated at high temperature and derated to a constant 25 °C use profile. Engineering Bulletin EB618 does not apply to this technology. Typical endurance defined in Engineering Bulletin EB619.

- 2. Cycling endurance represents number of program/erase cycles at –40 °C  $\leq$  T<sub>j</sub>  $\leq$  125 °C.

# 8.5 Analog

### 8.5.1 12-bit Cyclic Analog-to-Digital Converter (ADC) Parameters Table 27. 12-bit ADC Electrical Specifications

| Characteristic                               | Symbol                | Min                      | Тур           | Max                                   | Unit                |

|----------------------------------------------|-----------------------|--------------------------|---------------|---------------------------------------|---------------------|

| Recommended Operating Condition              | าร                    |                          | •             |                                       |                     |

| Supply Voltage <sup>1</sup>                  | VDDA                  | 3                        | 3.3           | 3.6                                   | V                   |

| VREFH (in external reference mode)           | Vrefhx                | VDDA-0.6                 |               | VDDA                                  | V                   |

| ADC Conversion Clock <sup>2</sup>            | f <sub>ADCCLK</sub>   | 0.1                      |               | 10                                    | MHz                 |

| Conversion Range <sup>3</sup>                | R <sub>AD</sub>       |                          |               | V <sub>REFH</sub> – V <sub>REFL</sub> | V                   |

| Fully Differential                           |                       | $-(V_{REFH} - V_{REFL})$ |               | V <sub>REFH</sub>                     |                     |

| Single Ended/Unipolar                        |                       | V <sub>REFL</sub>        |               | V KEFH                                |                     |

| Input Voltage Range (per input) <sup>4</sup> | V <sub>ADIN</sub>     | V <sub>REFL</sub>        |               | V <sub>REFH</sub>                     | V                   |

| External Reference                           |                       | 0                        |               | V <sub>DDA</sub>                      |                     |

| Internal Reference                           |                       | 0                        |               | ♥ DDA                                 |                     |

| Timing and Power                             |                       |                          |               |                                       |                     |

| Conversion Time <sup>5</sup>                 | t <sub>ADC</sub>      |                          | 8             |                                       | ADC Clock<br>Cycles |

| ADC Power-Up Time (from adc_pdn)             | t <sub>ADPU</sub>     |                          | 13            |                                       | ADC Clock<br>Cycles |

| ADC RUN Current (per ADC block)              | I <sub>ADRUN</sub>    |                          | 1.8           |                                       | mA                  |

| ADC Powerdown Current (adc_pdn enabled)      | I <sub>ADPWRDWN</sub> |                          | 0.1           |                                       | μA                  |

| V <sub>REFH</sub> Current (in external mode) | I <sub>VREFH</sub>    |                          | 190           | 225                                   | μΑ                  |

| Accuracy (DC or Absolute)                    |                       |                          |               |                                       |                     |

| Integral non-Linearity <sup>6</sup>          | INL                   |                          | +/- 1.5       | +/- 2.2                               | LSB <sup>7</sup>    |

| Differential non-Linearity <sup>6</sup>      | DNL                   |                          | +/- 0.5       | +/- 0.8                               | LSB <sup>7</sup>    |

| Monotonicity                                 |                       |                          | GUARANTE      | ED                                    |                     |

| Offset <sup>8</sup>                          | V <sub>OFFSET</sub>   |                          | +/- 8         |                                       | mV                  |

| Fully Differential                           |                       |                          | +/- 12        |                                       |                     |

| Single Ended/Unipolar                        |                       |                          | T/- 12        |                                       |                     |

| Gain Error                                   | E <sub>GAIN</sub>     |                          | 0.996 to1.004 | 0.990 to 1.010                        |                     |

| AC Specifications <sup>9</sup>               |                       |                          |               |                                       |                     |

| Signal to Noise Ratio                        | SNR                   |                          | 66            |                                       | dB                  |

| Total Harmonic Distortion                    | THD                   |                          | 75            |                                       | dB                  |

Table continues on the next page...

**PWMs and timers**

| Characteristic                                              | Symbol          | Min | Max | Unit | See Figure |

|-------------------------------------------------------------|-----------------|-----|-----|------|------------|

| Clock (SCK) high time                                       | t <sub>CH</sub> |     |     | ns   | Figure 13  |

| Master                                                      |                 |     |     | ns   | Figure 14  |

| Slave                                                       |                 |     |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

| Clock (SCK) low time                                        | t <sub>CL</sub> | 28  |     | ns   | Figure 16  |

| Master                                                      |                 | 28  |     | ns   |            |

| Slave                                                       |                 |     |     |      |            |

| Data set-up time required for inputs                        | t <sub>DS</sub> | 20  |     | ns   | Figure 13  |

| Master                                                      |                 | 1   | _   | ns   | Figure 14  |

| Slave                                                       |                 |     |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

| Data hold time required for inputs                          | t <sub>DH</sub> | 1   |     | ns   | Figure 13  |

| Master                                                      |                 | 3   | _   | ns   | Figure 14  |

| Slave                                                       |                 | 0   |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

| Access time (time to data active from high-impedance state) | t <sub>A</sub>  | 5   | _   | ns   | Figure 16  |

| Slave                                                       |                 |     |     |      |            |

| Disable time (hold time to high-<br>impedance state)        | t <sub>D</sub>  | 5   | _   | ns   | Figure 16  |

| Slave                                                       |                 |     |     |      |            |

| Data valid for outputs                                      | t <sub>DV</sub> | _   |     | ns   | Figure 13  |

| Master                                                      |                 | _   |     | ns   | Figure 14  |

| Slave (after enable edge)                                   |                 |     |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

| Data invalid                                                | t <sub>DI</sub> | 0   |     | ns   | Figure 13  |

| Master                                                      |                 | 0   |     | ns   | Figure 14  |

| Slave                                                       |                 | Ū   |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

| Rise time                                                   | t <sub>R</sub>  | _   | 1   | ns   | Figure 13  |

| Master                                                      |                 | _   | 1   | ns   | Figure 14  |

| Slave                                                       |                 |     |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

| Fall time                                                   | t <sub>F</sub>  | _   | 1   | ns   | Figure 13  |

| Master                                                      |                 | _   | 1   | ns   | Figure 14  |

| Slave                                                       |                 |     |     |      | Figure 15  |

|                                                             |                 |     |     |      | Figure 16  |

### Table 32. SPI timing (continued)

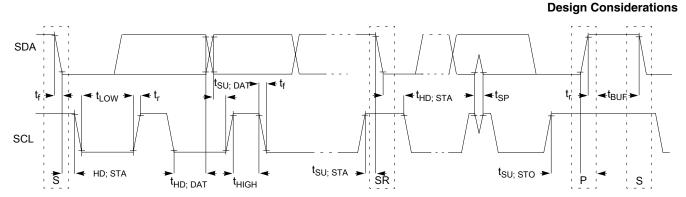

Figure 20. Timing definition for fast and standard mode devices on the I<sup>2</sup>C bus

# 9 Design Considerations

### 9.1 Thermal design considerations

An estimate of the chip junction temperature (TJ) can be obtained from the equation:

$$T_J = T_A + (R_{\Theta JA} \times P_D)$$

Where,

$T_A$  = Ambient temperature for the package (°C)

$R_{\Theta IA}$  = Junction-to-ambient thermal resistance (°C/W)

$P_D$  = Power dissipation in the package (W)

The junction-to-ambient thermal resistance is an industry-standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single-layer board and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which TJ value is closer to the application depends on the power dissipated by other components on the board.

- The TJ value obtained on a single layer board is appropriate for a tightly packed printed circuit board.

- The TJ value obtained on a board with the internal planes is usually appropriate if the board has low-power dissipation and if the components are well separated.

When a heat sink is used, the thermal resistance is expressed as the sum of a junction-tocase thermal resistance and a case-to-ambient thermal resistance:

$$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CA}$$

Where,

#### Design Considerations

$R_{\Theta JA}$  = Package junction-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  = Package junction-to-case thermal resistance (°C/W)

$R_{\Theta CA}$  = Package case-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  is device related and cannot be adjusted. You control the thermal environment to change the case to ambient thermal resistance,  $R_{\Theta CA}$ . For instance, you can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the thermal characterization parameter (YJT) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

Where,

$T_T$  = Thermocouple temperature on top of package (°C/W)

$\Psi_{JT}$  = hermal characterization parameter (°C/W)

$P_D$  = Power dissipation in package (W)

The thermal characterization parameter is measured per JESD51–2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

To determine the junction temperature of the device in the application when heat sinks are used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back-calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

**Design Considerations**

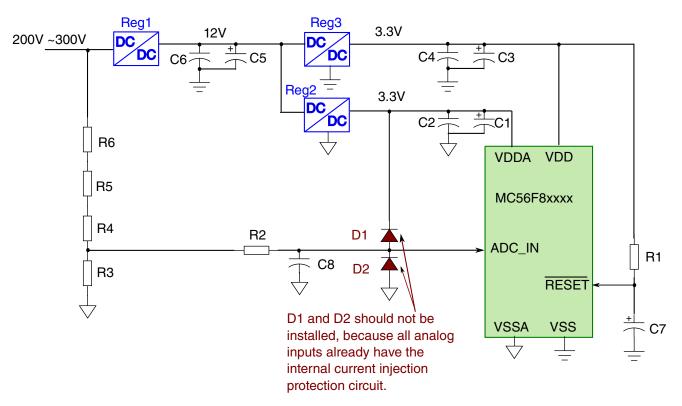

Figure 21. Protection Circuit Example

MC56F8xxxx DSC uses the 5V tolerance I/O. When the pin is configured to digital input, it can accept 5V input. Table 5. When the pin is configured to analog input, the internal integrated current injection protection circuit is enabled. The current injection protection circuit performs the same functions as external clamp diode D1 and D2 in Figure 21. As long as the source or sink current for each analog pin is less than 3 mA, then there is no damage to the device. See Table 27.

This situation could happen if diodes D1 or D2 are used for clamping; therefore in this case, the D1 and D2 clamping diodes are not recommended to be used.

### NOTE

In some designs, VDD and VDDA are powered from the same power supply. In this case, above analysis and suggestions are also applicatble.

# 9.3.3 Heavy capacitive load on power supply output:

In some applications, the low cost DC/DC converter may not regulate the output voltage well before it reaches the regulation point, which is roughly around 2.5V to 2.7V. However, the MC56F8xxxx DSC will exit power-on reset at around 2.3V. If the initialization code enables the PLL to run the DSC at full speed right after reset, then the

# 11 Pinout

# **11.1 Signal Multiplexing and Pin Assignments**

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The SIM's GPS registers are responsible for selecting which ALT functionality is available on most pins.

### NOTE

- The RESETB pin is a 3.3 V pin only.

- If the GPIOC1 pin is used as GPIO, the XOSC should be powered down.

- Not all CMPD pins are not available on 48 LQFP, 32 LQFP, and 32 QFN packages.

- QSPI signals—including MISO1, MOSI1, SCLK1, and SS0\_B—are not available on the 48 LQFP, 32 LQFP, and 32 QFN packages.

| 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | Pin Name | Default | ALT0                     | ALT1     | ALT2   | ALT3      |

|------------|------------|------------|----------|---------|--------------------------|----------|--------|-----------|

|            | LULL       | LULL       |          |         |                          |          |        |           |

| 1          | 1          | 1          | TCK      | TCK     | GPIOD2                   |          |        |           |

| 2          | 2          | 2          | RESETB   | RESETB  | GPIOD4                   |          |        |           |

| 3          | 3          | _          | GPIOC0   | GPIOC0  | EXTAL                    | CLKIN0   |        |           |

| 4          | 4          | _          | GPIOC1   | GPIOC1  | XTAL                     |          |        |           |

| 5          | 5          | 3          | GPIOC2   | GPIOC2  | TXD0                     | XB_OUT11 | XB_IN2 | CLKO0     |

| 6          | _          | _          | GPIOF8   | GPIOF8  | RXD0                     | XB_OUT10 | CMPD_O | PWM_2X    |

| 7          | 6          | 4          | GPIOC3   | GPIOC3  | TA0                      | CMPA_O   | RXD0   | CLKIN1    |

| 8          | 7          | 5          | GPIOC4   | GPIOC4  | TA1                      | CMPB_O   | XB_IN6 | EWM_OUT_B |

| 9          | _          | _          | GPIOA7   | GPIOA7  | ANA7&CMPD_IN3            |          |        |           |

| 10         | _          | _          | GPIOA6   | GPIOA6  | ANA6&CMPD_IN2            |          |        |           |

| 11         | _          | -          | GPIOA5   | GPIOA5  | ANA5&CMPD_IN1            |          |        |           |

| 12         | 8          | _          | GPIOA4   | GPIOA4  | ANA4&CMPD_IN0            |          |        |           |

| 13         | 9          | 6          | GPIOA0   | GPIOA0  | ANA0&CMPA_IN3            | CMPC_O   |        |           |

| 14         | 10         | 7          | GPIOA1   | GPIOA1  | ANA1&CMPA_IN0            |          |        |           |

| 15         | 11         | 8          | GPIOA2   | GPIOA2  | ANA2&VREFHA&CMPA_<br>IN1 |          |        |           |

| 16         | 12         | _          | GPIOA3   | GPIOA3  | ANA3&VREFLA&CMPA_<br>IN2 |          |        |           |

| 17         | _          | _          | GPIOB7   | GPIOB7  | ANB7&CMPB_IN2            |          |        |           |

| 18         | 13         | -          | GPIOC5   | GPIOC5  | DACA_O                   | XB_IN7   |        |           |

| 19         | -          | _          | GPIOB6   | GPIOB6  | ANB6&CMPB_IN1            |          |        |           |

# **13 Revision History**

The following table summarizes changes to this document since the release of the previous version.

| Rev. No. | Date                 | Substantial Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2        | 10/2013              | First public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 2.1      | 11/2013              | <ul> <li>In Table 2, added DACB_O signal description.</li> <li>In Obtaining package dimensions, changed 32-QFN's document number from '98ARE10566D' to '98ASA00473D'.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 2.2      | 03/2016 -<br>05/2016 | <ul> <li>Corrected document part number MC56F827XXDS to MC56F827XX.</li> <li>In "12-bit ADC Electrical Specifications" table, corrected Max Gain Error to 0.990 to 1.010.</li> <li>In Part identification section, in part number fields table, added the 32QFN package identifier.</li> <li>In Electrical design considerations" section, added additional section "Power-on Reset design considerations".</li> <li>Added new section "Power-on Reset design considerations".</li> <li>In "Peripheral highlights" section, added</li> <li>Periodic Interrupt Timer (PIT) Modules</li> <li>External Watchdog Monitor (EWM)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 3.0      | 09/2016              | <ul> <li>Added products: 56F82746MLF, 56F82733MFM</li> <li>Removed PDB (Programmable Delay Block) mentions, because PDBs are not present<br/>in these devices.</li> <li>Added V and M temperature options to operating characteristics.</li> <li>Moved "Signal groups" section under "MC56F827xx signal and pin descriptions"<br/>section.</li> <li>In "Voltage and current operating ratings" section: updated note; in "Absolute Maximum<br/>Ratings" table, updated Ambient and Junction Temperature rows, also fixed broken<br/>footnotes.</li> <li>In "Power consumption operating behaviors" section, in "Current Consumption" table:<br/>added columns and data for Maximum at 3.6V, 125°C", fixed broken footnotes.</li> <li>In "Thermal operating requirements" section, updated Die junction temperature and<br/>Ambient temperature requirements.</li> <li>In "Relaxation Oscillator Timing" section, in "Relaxation Oscillator Electrical<br/>Specifications" table:</li> <li>Added data for "-40°C to 125°C" temperature range.</li> <li>For "8 MHz Output Frequency, Standby Mode frequency", 2 corrections were<br/>made.</li> <li>Fixed broken footnotes.</li> </ul> |  |  |

Table 37.

Revision History