# E·XFL

#### NXP USA Inc. - MC56F82748VLHR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | 56800EX                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 100MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                     |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 54                                                                     |

| Program Memory Size        | 64KB (32K x 16)                                                        |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 4K x 16                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f82748vlhr |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

# 1.1 MC56F827xx Product Family

The following table is the comparsion of features among members of the family.

| Feature                                              | MC56F82    |            |            |            |            |            |            |            |            |            |            |            |

|------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Part Number <sup>1</sup>                             | 748V<br>LH | 746V<br>LF | 743V<br>LC | 743V<br>FM | 738V<br>LH | 736V<br>LF | 733V<br>LC | 733V<br>FM | 728V<br>LH | 726V<br>LF | 723V<br>LC | 723V<br>FM |

|                                                      |            | 746M<br>LF |            |            |            |            |            | 733M<br>FM |            |            |            |            |

| Core frequency<br>(MHz)                              | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     | 100/50     |

| Flash memory<br>(KB)                                 | 64         | 64         | 64         | 64         | 48         | 48         | 48         | 48         | 32         | 32         | 32         | 32         |

| RAM (KB)                                             | 8          | 8          | 8          | 8          | 8          | 8          | 8          | 8          | 6          | 6          | 6          | 6          |

| Interrupt<br>Controller                              | Yes        |

| Windowed<br>Computer<br>Operating<br>Properly (WCOP) | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| External<br>Watchdog Monitor<br>(EWM)                | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| Periodic Interrupt<br>Timer (PIT)                    | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          |

| Cyclic<br>Redundancy<br>Check (CRC)                  | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| Quad Timer<br>(TMR)                                  | 1x4        |

| 12-bit Cyclic ADC channels                           | 2x8        | 2x5        | 2x3        | 2x3        | 2x8        | 2x5        | 2x3        | 2x3        | 2x8        | 2x5        | 2x3        | 2x3        |

| PWM Module:                                          |            |            |            |            |            |            |            |            |            |            |            |            |

| Input capture<br>channels <sup>2</sup>               | 12         | 6          | 6          | 6          | 12         | 6          | 6          | 6          | 12         | 6          | 6          | 6          |

| High-resolution channels                             | 8          | 6          | 6          | 6          | 8          | 6          | 6          | 6          | 8          | 6          | 6          | 6          |

| Standard channels                                    | 4          | 0          | 0          | 0          | 4          | 0          | 0          | 0          | 4          | 0          | 0          | 0          |

| 12-bit DAC                                           | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          | 2          |

| DMA                                                  | Yes        |

Table 1. MC56F827xx Family

Table continues on the next page...

| Feature                        |            |            |            |            |            | MC5        | 6F82       |            |            |            |            |            |

|--------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Part Number <sup>1</sup>       | 748V<br>LH | 746V<br>LF | 743V<br>LC | 743V<br>FM | 738V<br>LH | 736V<br>LF | 733V<br>LC | 733V<br>FM | 728V<br>LH | 726V<br>LF | 723V<br>LC | 723V<br>FM |

|                                |            | 746M<br>LF |            |            |            |            |            | 733M<br>FM |            |            |            |            |

| Analog<br>Comparators<br>(CMP) | 4          | 4          | 3          | 3          | 4          | 4          | 3          | 3          | 4          | 4          | 3          | 3          |

| QSCI                           | 2          | 2          | 1          | 1          | 2          | 2          | 1          | 1          | 2          | 2          | 1          | 1          |

| QSPI                           | 2          | 1          | 1          | 1          | 2          | 1          | 1          | 1          | 2          | 1          | 1          | 1          |

| I2C/SMBus                      | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          | 1          |

| MSCAN                          | 1          | 1          | 0          | 0          | 1          | 1          | 0          | 0          | 1          | 1          | 0          | 0          |

| GPIO                           | 54         | 39         | 26         | 26         | 54         | 39         | 26         | 26         | 54         | 39         | 26         | 26         |

| Package pin count              | 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | 32<br>QFN  | 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | 32<br>QFN  | 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | 32<br>QFN  |

| AEC-Q100 <sup>3</sup>          | Yes        | Yes        | No         | No         | Yes        | Yes        | No         | No         | Yes        | Yes        | No         | No         |

Table 1. MC56F827xx Family (continued)

1. Temperature options

V: -40°C to 105°C

M: -40°C to 125°C

2. Input capture shares the pin with cooresponding PWM channels.

3. Qualification aligned to AEC-Q100

# 1.2 56800EX 32-bit Digital Signal Controller (DSC) core

- Efficient 32-bit 56800EX Digital Signal Processor (DSP) engine with modified dual Harvard architecture:

- Three internal address buses

- Four internal data buses: two 32-bit primary buses, one 16-bit secondary data bus, and one 16-bit instruction bus

- 32-bit data accesses

- Supports concurrent instruction fetches in the same cycle, and dual data accesses in the same cycle

- 20 addressing modes

- As many as 100 million instructions per second (MIPS) at 100 MHz core frequency

- 162 basic instructions

- Instruction set supports both fractional arithmetic and integer arithmetic

- 32-bit internal primary data buses support 8-bit, 16-bit, and 32-bit data movement, plus addition, subtraction, and logical operations

- Single-cycle 16 × 16-bit -> 32-bit and 32 x 32-bit -> 64-bit multiplier-accumulator (MAC) with dual parallel moves

- 32-bit arithmetic and logic multi-bit shifter

- Four 36-bit accumulators, including extension bits

### 1.6.16 Clock sources

### 1.6.16.1 On-chip oscillators

- Tunable 8 MHz relaxation oscillator with 400 kHz at standby mode (divide-by-two output)

- 200 kHz low frequency clock as secondary clock source for COP, EWM, PIT

### 1.6.16.2 Crystal oscillator

- Support for both high ESR crystal oscillator (ESR greater than 100  $\Omega$ ) and ceramic resonator

- Operating frequency: 4–16 MHz

### 1.6.17 Cyclic Redundancy Check (CRC) Generator

- Hardware CRC generator circuit with 16-bit shift register

- High-speed hardware CRC calculation

- Programmable initial seed value

- CRC16-CCITT compliancy with  $x^{16} + x^{12} + x^5 + 1$  polynomial

- Error detection for all single, double, odd, and most multibit errors

- Option to transpose input data or output data (CRC result) bitwise, which is required for certain CRC standards

### 1.6.18 General Purpose I/O (GPIO)

- 5 V tolerance (except RESETB pin)

- Individual control of peripheral mode or GPIO mode for each pin

- Programmable push-pull or open drain output

- Configurable pullup or pulldown on all input pins

- All pins (except JTAG and RESETB) default to be GPIO inputs

- 2 mA / 9 mA source/sink capability

- Controllable output slew rate

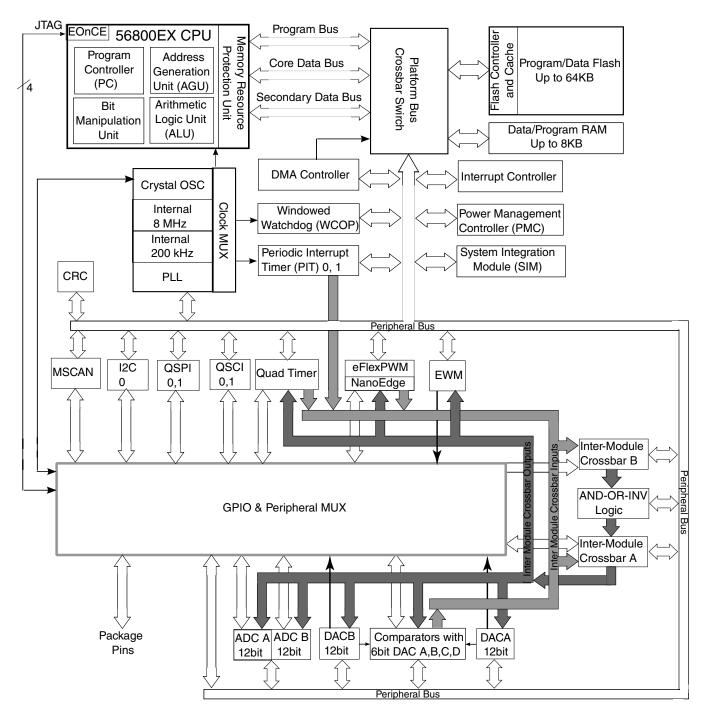

# 1.7 Block diagrams

The 56800EX core is based on a modified dual Harvard-style architecture, consisting of three execution units operating in parallel, and allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set

Figure 2. System diagram

| Signal Name                | 64 LQFP | 48 LQFP | 32 LQFP | Туре                          | State During<br>Reset             | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|---------|---------|---------|-------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| тск                        | 1       | 1       | 1       | Input                         | Input, internal<br>pullup enabled | Test Clock Input — The pin is connected<br>internally to a pullup resistor. A Schmitt-<br>trigger input is used for noise immunity.<br>After reset, the default state is TCK                                                                                                                                                                                                                                                |

| (GPIOD2)                   |         |         |         | Input/Output                  |                                   | GPIO Port D2                                                                                                                                                                                                                                                                                                                                                                                                                |

| TMS                        | 63      | 47      | 31      | Input                         | Input, internal<br>pullup enabled | Test Mode Select Input — It is sampled<br>on the rising edge of TCK and has an<br>internal pullup resistor. After reset, the<br>default state is TMS.                                                                                                                                                                                                                                                                       |

|                            |         |         |         |                               |                                   | <b>NOTE:</b> Always tie the TMS pin to $V_{DD}$ through a 2.2 k $\Omega$ resistor if need to keep on-board debug capability. Otherwise, directly tie to $V_{DD}$ .                                                                                                                                                                                                                                                          |

| (GPIOD3)                   |         |         |         | Input/Output                  |                                   | GPIO Port D3                                                                                                                                                                                                                                                                                                                                                                                                                |

| RESET or<br>RESETB         | 2       | 2       | 2       | Input                         | Input, internal<br>pullup enabled | Reset — A direct hardware reset on the processor. When RESET is asserted low, the device is initialized and placed in the reset state. A Schmitt-trigger input is used for noise immunity. The internal reset signal is deasserted synchronous with the internal clocks after a fixed number of internal clocks. After reset, the default state is RESET. Recommended a capacitor of up to 0.1 $\mu$ F for filtering noise. |

| (GPIOD4)                   |         |         |         | Input/<br>Opendrain<br>Output |                                   | GPIO Port D4 RESET functionality is<br>disabled in this mode and the device can<br>be reset only through POR, COP reset,<br>or software reset.                                                                                                                                                                                                                                                                              |

| GPIOA0                     | 13      | 9       | 6       | Input/Output                  | Input, internal                   | GPIO Port A0                                                                                                                                                                                                                                                                                                                                                                                                                |

| (ANA0&CMPA_IN<br>3)        | -       |         |         | Input                         | pullup enabled                    | ANA0 is analog input to channel 0 of<br>ADCA; CMPA_IN3 is positive input 3 of<br>analog comparator A. After reset, the<br>default state is GPIOA0.                                                                                                                                                                                                                                                                          |

| (CMPC_O)                   |         |         |         | Output                        |                                   | Analog comparator C output                                                                                                                                                                                                                                                                                                                                                                                                  |

| GPIOA1                     | 14      | 10      | 7       | Input/Output                  | Input, internal pullup enabled    | GPIO Port A1: After reset, the default state is GPIOA1.                                                                                                                                                                                                                                                                                                                                                                     |

| (ANA1&CMPA_IN<br>0)        |         |         |         | Input                         |                                   | ANA1 is analog input to channel 1 of<br>ADCA; CMPA_IN0 is negative input 0 of<br>analog comparator A. When used as an<br>analog input, the signal goes to ANA1<br>and CMPA_IN0. The ADC control<br>register configures this input as ANA1 or<br>CMPA_IN0.                                                                                                                                                                   |

| GPIOA2                     | 15      | 11      | 8       | Input/Output                  | Input, internal<br>pullup enabled | GPIO Port A2: After reset, the default state is GPIOA2.                                                                                                                                                                                                                                                                                                                                                                     |

| (ANA2&VREFHA<br>&CMPA_IN1) |         |         |         | Input                         |                                   | ANA2 is analog input to channel 2 of ADCA; VREFHA is analog reference                                                                                                                                                                                                                                                                                                                                                       |

Table continues on the next page...

| Signal Name                | 64 LQFP | 48 LQFP | 32 LQFP | Туре         | State During<br>Reset             | Signal Description                                                                                                                                                                                                                         |

|----------------------------|---------|---------|---------|--------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                            |         |         |         |              |                                   | high of ADCA; CMPA_IN1 is negative<br>input 1 of analog comparator A. When<br>used as an analog input, the signal goes<br>to both ANA2, VREFHA, and<br>CMPA_IN1.                                                                           |

| GPIOA3                     | 16      | 12      | _       | Input/Output | Input, internal<br>pullup enabled | GPIO Port A3: After reset, the default state is GPIOA3.                                                                                                                                                                                    |

| (ANA3&VREFLA&<br>CMPA_IN2) | -       |         |         | Input        |                                   | ANA3 is analog input to channel 3 of<br>ADCA; VREFLA is analog reference low<br>of ADCA; CMPA_IN2 is negative input 2<br>of analog comparator A.                                                                                           |

| GPIOA4                     | 12      | 8       | —       | Input/Output | Input, internal pullup enabled    | GPIO Port A4: After reset, the default state is GPIOA4.                                                                                                                                                                                    |

| (ANA4&CMPD_IN<br>0)        |         |         |         | Input        |                                   | ANA4 is Analog input to channel 4 of<br>ADCA; CMPD_IN0 is input 0 to<br>comparator D.                                                                                                                                                      |

| GPIOA5                     | 11      |         |         | Input/Output | Input, internal<br>pullup enabled | GPIO Port A5: After reset, the default state is GPIOA5.                                                                                                                                                                                    |

| (ANA5&CMPD_IN<br>1)        | -       |         |         | Input        |                                   | ANA5 is analog input to channel 5 of<br>ADCA; ANC9 is analog input to channel<br>9 of ADCC; CMPD_IN1 is negative input<br>1 of analog comparator D.                                                                                        |

| GPIOA6                     | 10      |         |         | Input/Output | Input, internal pullup enabled    | GPIO Port A6: After reset, the default state is GPIOA6.                                                                                                                                                                                    |

| (ANA6&CMPD_IN<br>2)        |         |         |         | Input        |                                   | ANA6 is analog input to channel 5 of<br>ADCA; CMPD_IN2 is negative input 2 of<br>analog comparator D.                                                                                                                                      |

| GPIOA7                     | 9       |         | —       | Input/Output | Input, internal pullup enabled    | GPIO Port A7: After reset, the default state is GPIOA7.                                                                                                                                                                                    |

| (ANA7&CMPD_IN<br>3)        |         |         |         | Input        |                                   | ANA7 is analog input to channel 7 of<br>ADCA; CMPD_IN3 is negative input 3 of<br>analog comparator D.                                                                                                                                      |

| GPIOB0                     | 24      | 17      | 11      | Input/Output | Input, internal pullup enabled    | GPIO Port B0: After reset, the default state is GPIOB0.                                                                                                                                                                                    |

| (ANB0&CMPB_IN<br>3)        |         |         |         | Input        |                                   | ANB0 is analog input to channel 0 of<br>ADCB; CMPB_IN3 is positive input 3 of<br>analog comparator B. When used as an<br>analog input, the signal goes to ANB0<br>and CMPB_IN3. The ADC control<br>register configures this input as ANB0. |

| GPIOB1                     | 25      | 18      | 12      | Input/Output | Input, internal<br>pullup enabled | GPIO Port B1: After reset, the default state is GPIOB1.                                                                                                                                                                                    |

| (ANB1&CMPB_IN<br>0)        |         |         |         | Input        |                                   | ANB1 is analog input to channel 1 of<br>ADCB; CMPB_IN0 is negative input 0 of<br>analog comparator B. When used as an<br>analog input, the signal goes to ANB1<br>and CMPB_IN0. The ADC control<br>register configures this input as ANB1. |

### Table 2. Signal descriptions (continued)

Table continues on the next page...

#### MC56F827xx signal and pin descriptions

| Signal Name      | 64 LQFP | 48 LQFP | 32 LQFP | Туре             | State During<br>Reset          | Signal Description                                                                                                                                        |

|------------------|---------|---------|---------|------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |         |         |         |                  |                                | oscillator output to an external crystal or ceramic resonator.                                                                                            |

| GPIOC2           | 5       | 5       | 3       | Input/Output     | Input, internal pullup enabled | GPIO Port C2: After reset, the default state is GPIOC2.                                                                                                   |

| (TXD0)           |         |         |         | Output           |                                | SCI0 transmit data output or transmit/<br>receive in single wire operation                                                                                |

| (XB_OUT11)       |         |         |         | Output           |                                | Crossbar module output 11                                                                                                                                 |

| (XB_IN2)         |         |         |         | Input            |                                | Crossbar module input 2                                                                                                                                   |

| (CLKO0)          |         |         |         | Output           |                                | Buffered clock output 0: the clock source<br>is selected by clockout select<br>(CLKOSEL) bits in the clock output<br>select register (CLKOUT) of the SIM. |

| GPIOC3           | 7       | 6       | 4       | Input/Output     | Input, internal pullup enabled | GPIO Port C3: After reset, the default state is GPIOC3.                                                                                                   |

| (TA0)            |         |         |         | Input/Output     |                                | Quad timer module A channel 0 input/<br>output                                                                                                            |

| (CMPA_O)         |         |         |         | Output           |                                | Analog comparator A output                                                                                                                                |

| (RXD0)           |         |         |         | Input            |                                | SCI0 receive data input                                                                                                                                   |

| (CLKIN1)         |         |         |         | Input            |                                | External clock input 1                                                                                                                                    |

| GPIOC4           | 8       | 7       | 5       | Input/Output     | Input, internal pullup enabled | GPIO Port C4: After reset, the default state is GPIOC4.                                                                                                   |

| (TA1)            |         |         |         | Input/Output     |                                | Quad timer module A channel 1 input/<br>output                                                                                                            |

| (CMPB_O)         |         |         |         | Output           |                                | Analog comparator B output                                                                                                                                |

| (XB_IN6)         |         |         |         | Input            |                                | Crossbar module input 6                                                                                                                                   |

| (EWM_OUT_B)      |         |         |         | Output           |                                | External Watchdog Module output                                                                                                                           |

| GPIOC5           | 18      | 13      | -       | Input/Output     | Input, internal pullup enabled | GPIO Port C5: After reset, the default state is GPIOC5.                                                                                                   |

| (DACA_O)         |         |         |         | Analog<br>Output |                                | 12-bit digital-to-analog output                                                                                                                           |

| (XB_IN7)         |         |         |         | Input            |                                | Crossbar module input 7                                                                                                                                   |

| GPIOC6           | 31      | 23      | 15      | Input/Output     | Input, internal pullup enabled | GPIO Port C6: After reset, the default state is GPIOC6.                                                                                                   |

| (TA2)            |         |         |         | Input/Output     |                                | Quad timer module A channel 2 input/<br>output                                                                                                            |

| (XB_IN3)         |         |         |         | Input            |                                | Crossbar module input 3                                                                                                                                   |

| (CMP_REF)        |         |         |         | Analog Input     |                                | Positive input 3 of analog comparator A and B and C.                                                                                                      |

| ( <u>SS0_B</u> ) |         |         |         | Input/Output     |                                | In slave mode, <u>SS0_B</u> indicates to the SPI module 0 that the current transfer is to be received.                                                    |

| GPIOC7           | 32      | 24      | -       | Input/Output     | Input, internal pullup enable  | GPIO Port C7: After reset, the default state is GPIOC7.                                                                                                   |

### Table 2. Signal descriptions (continued)

Table continues on the next page...

# 5.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

# 5.8.2 Example 2

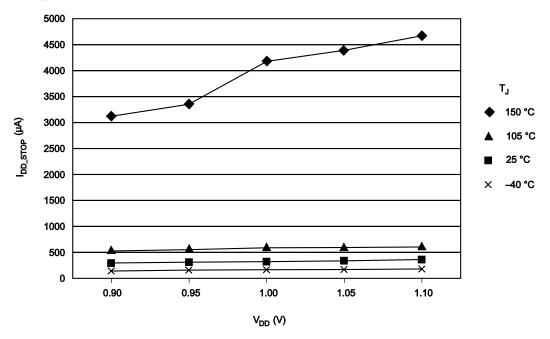

This is an example of a chart that shows typical values for various voltage and temperature conditions:

# 5.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | C°   |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

# 6 Ratings

# 6.1 Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | —    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 6.2 Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level |      | 3    |      | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, *Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices*.

# 6.3 ESD handling ratings

Although damage from electrostatic discharge (ESD) is much less common on these devices than on early CMOS circuits, use normal handling precautions to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage.

All ESD testing is in conformity with AEC-Q100 Stress Test Qualification. During the device qualification ESD stresses were performed for the human body model (HBM), the machine model (MM), and the charge device model (CDM).

All latch-up testing is in conformity with AEC-Q100 Stress Test Qualification.

A device is defined as a failure if after exposure to ESD pulses, the device no longer meets the device specification. Complete DC parametric and functional testing is performed as per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Characteristic <sup>1</sup>                      | Min   | Мах   | Unit |

|--------------------------------------------------|-------|-------|------|

| ESD for Human Body Model (HBM)                   | -2000 | +2000 | V    |

| ESD for Machine Model (MM)                       | -200  | +200  | V    |

| ESD for Charge Device Model (CDM)                | -500  | +500  | V    |

| Latch-up current at TA= 85°C (I <sub>LAT</sub> ) | -100  | +100  | mA   |

Table 4.

ESD/Latch-up Protection

1. Parameter is achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted.

# 6.4 Voltage and current operating ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 5 may affect device reliability or cause permanent damage to the device.

#### NOTE

If the voltage difference between VDD and VDDA or VSS and VSSA is too large, then the device can malfunction or be permanently damaged. The restrictions are:

- At all times, it is recommended that the voltage difference of VDD - VSS be within +/-200 mV of the voltage difference of VDDA - VSSA,, including power ramp up and ramp down; see additional requirements in Table 6. Failure to do this recommendation may result in a harmful leakage current through the substrate, between the VDD/VSS and VDDA/VSSA pad cells. This harmful leakage current could prevent the device from operating after power up.

- At all times, to avoid permanent damage to the part, the voltage difference between VDD and VDDA must absolutely be limited to 0.3 V, See Table 5.

- At all times, to avoid permanent damage to the part, the voltage difference between VSS and VSSA must absolutely be limited to 0.3 V, See Table 5.

| Characteristic              | Symbol           | Notes <sup>1</sup> | Min  | Max | Unit |

|-----------------------------|------------------|--------------------|------|-----|------|

| Supply Voltage Range        | $V_{DD}$         |                    | -0.3 | 4.0 | V    |

| Analog Supply Voltage Range | V <sub>DDA</sub> |                    | -0.3 | 4.0 | V    |

Table 5. Absolute Maximum Ratings ( $V_{SS} = 0 V$ ,  $V_{SSA} = 0 V$ )

Table continues on the next page ...

calculations, determine the difference between actual pin voltage and  $V_{SS}$  or  $V_{DD}$  and multiply by the pin current for each I/O pin. Except in cases of unusually high pin current (heavy loads), the difference between pin voltage and  $V_{SS}$  or  $V_{DD}$  is very small.

| Board<br>type        | Symbol            | Descriptio<br>n                                                                                                             | 32 QFN | 32 LQFP | 48 LQFP | 64 LQFP | Unit | Notes |

|----------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|--------|---------|---------|---------|------|-------|

| Single-layer<br>(1s) | R <sub>ejA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)                                                 | 96     | 83      | 70      | 64      | °C/W | ,     |

| Four-layer<br>(2s2p) | R <sub>θJA</sub>  | Thermal<br>resistance,<br>junction to<br>ambient<br>(natural<br>convection)                                                 | 33     | 55      | 46      | 46      | °C/W | 1,    |

| Single-layer<br>(1s) | R <sub>ejma</sub> | Thermal<br>resistance,<br>junction to<br>ambient<br>(200 ft./min.<br>air speed)                                             | 80     | 70      | 57      | 52      | °C/W | 1,2   |

| Four-layer<br>(2s2p) | R <sub>θJMA</sub> | Thermal<br>resistance,<br>junction to<br>ambient<br>(200 ft./min.<br>air speed)                                             | 27     | 49      | 39      | 39      | °C/W | 1,2   |

| _                    | R <sub>θJB</sub>  | Thermal<br>resistance,<br>junction to<br>board                                                                              | 12     | 31      | 23      | 28      | °C/W |       |

| _                    | R <sub>θJC</sub>  | Thermal<br>resistance,<br>junction to<br>case                                                                               | 1.8    | 22      | 17      | 15      | °C/W |       |

| _                    | Ψ <sub>JT</sub>   | Thermal<br>characteriza<br>tion<br>parameter,<br>junction to<br>package top<br>outside<br>center<br>(natural<br>convection) | 6      | 5       | 3       | 3       | °C/W |       |

See Thermal design considerations for more detail on thermal design considerations.

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

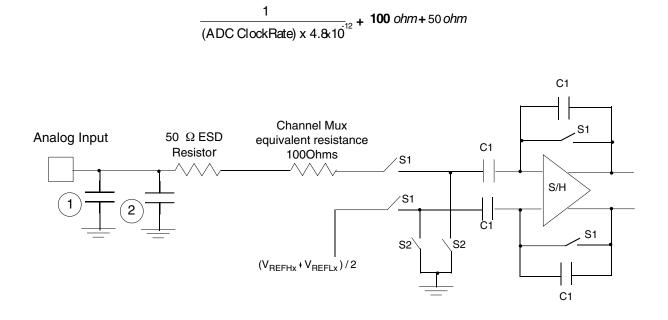

- 1. Parasitic capacitance due to package, pin-to-pin and pin-to-package base coupling = 1.8pF

- 2. Parasitic capacitance due to the chip bond pad, ESD protection devices and signal routing = 2.04pF

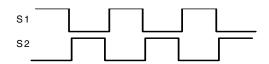

- 3. S1 and S2 switch phases are non-overlapping and depend on the ADC clock frequency

Figure 9. Equivalent circuit for A/D loading

### 8.5.2 12-bit Digital-to-Analog Converter (DAC) parameters Table 28. DAC parameters

|                                                                 | Symbol                                                                                                                                                             | Min                                                                                                                                                                                                  | Тур                                                                                                                                                              | Max                                                                                                                                                                           | Unit                                                                                                                                                                             |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DC Speci                                                        | fications                                                                                                                                                          |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |  |

|                                                                 |                                                                                                                                                                    | 12                                                                                                                                                                                                   | 12                                                                                                                                                               | 12                                                                                                                                                                            | bits                                                                                                                                                                             |  |  |

| At output load                                                  |                                                                                                                                                                    |                                                                                                                                                                                                      | 1                                                                                                                                                                |                                                                                                                                                                               | μs                                                                                                                                                                               |  |  |

| RLD = 3 kΩ                                                      |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |  |

| CLD = 400 pF                                                    |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |  |

| Time from release of PWRDWN signal until DACOUT signal is valid | t <sub>DAPU</sub>                                                                                                                                                  | —                                                                                                                                                                                                    | —                                                                                                                                                                | 11                                                                                                                                                                            | μs                                                                                                                                                                               |  |  |

| Accuracy                                                        |                                                                                                                                                                    |                                                                                                                                                                                                      |                                                                                                                                                                  |                                                                                                                                                                               |                                                                                                                                                                                  |  |  |

| Range of input digital words:                                   | INL                                                                                                                                                                | _                                                                                                                                                                                                    | +/- 3                                                                                                                                                            | +/- 4                                                                                                                                                                         | LSB <sup>3</sup>                                                                                                                                                                 |  |  |

| -                                                               | At output load<br>RLD = 3 kΩ<br>CLD = 400 pF<br>Time from release of PWRDWN<br>signal until DACOUT signal is valid<br><b>Accu</b><br>Range of input digital words: | At output load         RLD = 3 kΩ         CLD = 400 pF         Time from release of PWRDWN signal until DACOUT signal is valid         t_DAPU         Accuracy         Range of input digital words: | At output load     —       RLD = 3 kΩ     —       CLD = 400 pF     —       Time from release of PWRDWN signal until DACOUT signal is valid     t <sub>DAPU</sub> | At output load1212At output load1RLD = 3 kΩ1CLD = 400 pFTime from release of PWRDWN<br>signal until DACOUT signal is validt_DAPUAccuracyRange of input digital words:INL+/- 3 | 121212At output load—1RLD = 3 kΩ—1CLD = 400 pF——Time from release of PWRDWN<br>signal until DACOUT signal is validtDAPU—AccuracyRange of input digital words:INL—+/- 3+/- 3+/- 4 |  |  |

Table continues on the next page...

| Parameter                   | Conditions/Comments                                                                     | Symbol              | Min                          | Тур        | Max                          | Unit             |

|-----------------------------|-----------------------------------------------------------------------------------------|---------------------|------------------------------|------------|------------------------------|------------------|

|                             | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |

|                             | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |

| Differential non-           | Range of input digital words:                                                           | DNL                 | _                            | +/- 0.8    | +/- 0.9                      | LSB <sup>3</sup> |

| linearity <sup>2</sup>      | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |

|                             | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |

| Monotonicity                | > 6 sigma monotonicity,                                                                 |                     |                              | guaranteed |                              | _                |

|                             | < 3.4 ppm non-monotonicity                                                              |                     |                              |            |                              |                  |

| Offset error <sup>2</sup>   | Range of input digital words:                                                           | V <sub>OFFSET</sub> | _                            | +/- 25     | + /- 43                      | mV               |

|                             | 410 to 3891 (\$19A - \$F33)                                                             |                     |                              |            |                              |                  |

|                             | 5% to 95% of full range                                                                 |                     |                              |            |                              |                  |

| Gain error <sup>2</sup>     | Range of input digital words: 410 to<br>3891 (\$19A - \$F33) 5% to 95% of<br>full range | E <sub>GAIN</sub>   | _                            | +/- 0.5    | +/- 1.5                      | %                |

|                             | DAC C                                                                                   | Dutput              |                              |            |                              |                  |

| Output voltage range        | Within 40 mV of either $V_{\rm SSA}$ or $V_{\rm DDA}$                                   | V <sub>OUT</sub>    | V <sub>SSA</sub> +<br>0.04 V | _          | V <sub>DDA</sub> - 0.04<br>V | V                |

|                             | AC Specifications                                                                       |                     |                              |            |                              |                  |

| Signal-to-noise ratio       |                                                                                         | SNR                 |                              | 85         |                              | dB               |

| Spurious free dynamic range |                                                                                         | SFDR                | _                            | -72        | —                            | dB               |

| Effective number of bits    |                                                                                         | ENOB                | _                            | 11         | _                            | bits             |

### Table 28. DAC parameters (continued)

$1. \quad \mbox{Settling time is swing range from $V_{SSA}$ to $V_{DDA}$ } 2. \ \mbox{No guaranteed specification within 5% of $V_{DDA}$ or $V_{SSA}$ }$

3. LSB = 0.806 mV

#### **CMP and 6-bit DAC electrical specifications** 8.5.3 Table 29. Comparator and 6-bit DAC electrical specifications

| Symbol            | Description                                     | Min.            | Тур. | Max.            | Unit |

|-------------------|-------------------------------------------------|-----------------|------|-----------------|------|

| V <sub>DD</sub>   | Supply voltage                                  | 2.7             | —    | 3.6             | V    |

| I <sub>DDHS</sub> | Supply current, High-speed mode (EN=1, PMODE=1) | —               | 300  | —               | μA   |

| I <sub>DDLS</sub> | Supply current, low-speed mode (EN=1, PMODE=0)  | _               | 36   | —               | μA   |

| V <sub>AIN</sub>  | Analog input voltage                            | V <sub>SS</sub> | —    | V <sub>DD</sub> | V    |

| V <sub>AIO</sub>  | Analog input offset voltage                     | _               | —    | 20              | mV   |

| V <sub>H</sub>    | Analog comparator hysteresis                    |                 |      |                 |      |

|                   | • CR0[HYSTCTR] = $00^1$                         | —               | 5    | 13              | mV   |

|                   | <ul> <li>CR0[HYSTCTR] = 01</li> </ul>           | —               | 25   | 48              | mV   |

|                   | • CR0[HYSTCTR] = 10 <sup>2</sup>                | _               | 55   | 105             | mV   |

|                   | • CR0[HYSTCTR] = 11 <sup>2</sup>                | —               | 80   | 148             | mV   |

Table continues on the next page ...

System modules

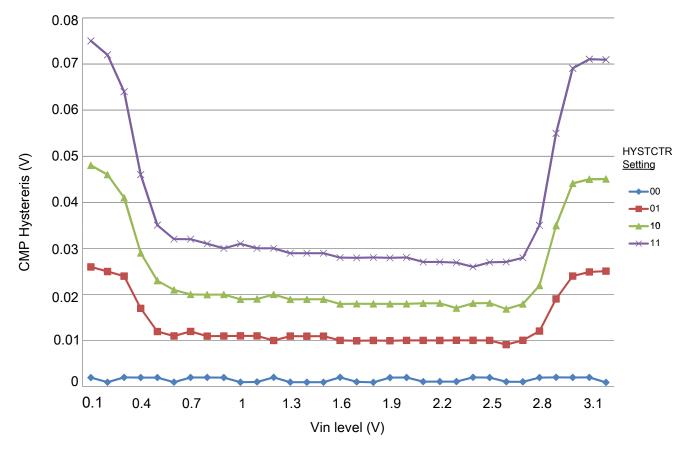

Figure 10. Typical hysteresis vs. Vin level ( $V_{DD}$  = 3.3 V, PMODE = 0)

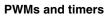

Figure 11. Typical hysteresis vs. Vin level (V<sub>DD</sub> = 3.3 V, PMODE = 1)

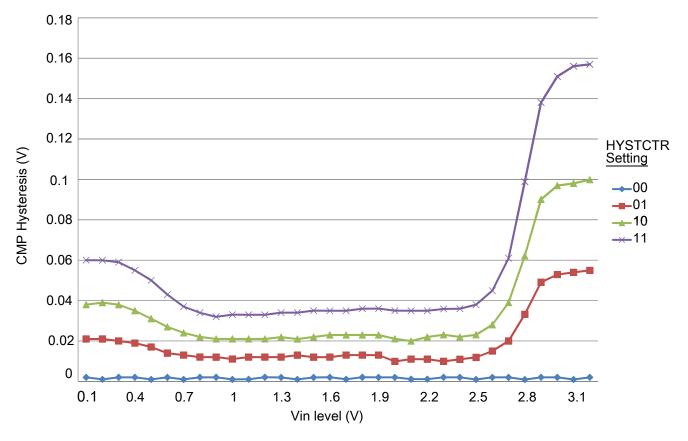

### 8.6 PWMs and timers

### 8.6.1 Enhanced NanoEdge PWM characteristics

| Table 30. | NanoEdge | <b>PWM timing</b> | parameters |

|-----------|----------|-------------------|------------|

|-----------|----------|-------------------|------------|

| Characteristic                                             | Symbol          | Min | Тур | Max | Unit |

|------------------------------------------------------------|-----------------|-----|-----|-----|------|

| PWM clock frequency                                        |                 |     | 100 |     | MHz  |

| NanoEdge Placement (NEP) Step Size <sup>1, 2</sup>         | pwmp            |     | 312 |     | ps   |

| Delay for fault input activating to PWM output deactivated |                 | 1   |     |     | ns   |

| Power-up Time <sup>3</sup>                                 | t <sub>pu</sub> |     | 25  |     | μs   |

1. Reference IPbus clock of 100 MHz in NanoEdge Placement mode.

2. Temperature and voltage variations do not affect NanoEdge Placement step size.

3. Powerdown to NanoEdge mode transition.

# 8.6.2 Quad Timer timing

Parameters listed are guaranteed by design.

# 8.7.2 Queued Serial Communication Interface (SCI) timing

Parameters listed are guaranteed by design.

| Characteristic                                                                              | Symbol                   | Min        | Мах                    | Unit                          | See Figure |

|---------------------------------------------------------------------------------------------|--------------------------|------------|------------------------|-------------------------------|------------|

| Baud rate <sup>1</sup>                                                                      | BR                       | —          | (f <sub>MAX</sub> /16) | Mbit/s                        | —          |

| RXD pulse width                                                                             | RXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 17  |

| TXD pulse width                                                                             | TXD <sub>PW</sub>        | 0.965/BR   | 1.04/BR                | ns                            | Figure 18  |

|                                                                                             | LIN                      | Slave Mode |                        |                               |            |

| Deviation of slave node clock from nominal<br>clock rate before synchronization             | F <sub>TOL_UNSYNCH</sub> | -14        | 14                     | %                             | _          |

| Deviation of slave node clock relative to<br>the master node clock after<br>synchronization | F <sub>TOL_SYNCH</sub>   | -2         | 2                      | %                             | _          |

| Minimum break character length                                                              | T <sub>BREAK</sub>       | 13         | —                      | Master<br>node bit<br>periods | _          |

|                                                                                             |                          | 11         | —                      | Slave node bit periods        | _          |

#### Table 33. SCI timing

1. f<sub>MAX</sub> is the frequency of operation of the SCI clock in MHz, which can be selected as the bus clock (max.50 MHz depending on part number) or 2x bus clock (max. 100 MHz) for the devices.

#### Figure 18. TXD pulse width

#### 8.7.3 Modular/Scalable Controller Area Network (MSCAN) Table 34. MSCAN Timing Parameters

| Characteristic                     | Symbol              | Min | Max | Unit   |

|------------------------------------|---------------------|-----|-----|--------|

| Baud Rate                          | BR <sub>CAN</sub>   | —   | 1   | Mbit/s |

| CAN Wakeup dominant pulse filtered | T <sub>WAKEUP</sub> | —   | 1.5 | μs     |

| CAN Wakeup dominant pulse pass     | T <sub>WAKEUP</sub> | 5   | _   | μs     |

#### Design Considerations

$R_{\Theta JA}$  = Package junction-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  = Package junction-to-case thermal resistance (°C/W)

$R_{\Theta CA}$  = Package case-to-ambient thermal resistance (°C/W)

$R_{\Theta JC}$  is device related and cannot be adjusted. You control the thermal environment to change the case to ambient thermal resistance,  $R_{\Theta CA}$ . For instance, you can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the thermal characterization parameter (YJT) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\Psi_{JT} \times P_D)$$

Where,

$T_T$  = Thermocouple temperature on top of package (°C/W)

$\Psi_{JT}$  = hermal characterization parameter (°C/W)

$P_D$  = Power dissipation in package (W)

The thermal characterization parameter is measured per JESD51–2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

To determine the junction temperature of the device in the application when heat sinks are used, the junction temperature is determined from a thermocouple inserted at the interface between the case of the package and the interface material. A clearance slot or hole is normally required in the heat sink. Minimizing the size of the clearance is important to minimize the change in thermal performance caused by removing part of the thermal interface to the heat sink. Because of the experimental difficulties with this technique, many engineers measure the heat sink temperature and then back-calculate the case temperature using a separate measurement of the thermal resistance of the interface. From this case temperature, the junction temperature is determined from the junction-to-case thermal resistance.

# 11 Pinout

# **11.1 Signal Multiplexing and Pin Assignments**

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The SIM's GPS registers are responsible for selecting which ALT functionality is available on most pins.

### NOTE

- The RESETB pin is a 3.3 V pin only.

- If the GPIOC1 pin is used as GPIO, the XOSC should be powered down.

- Not all CMPD pins are not available on 48 LQFP, 32 LQFP, and 32 QFN packages.

- QSPI signals—including MISO1, MOSI1, SCLK1, and SS0\_B—are not available on the 48 LQFP, 32 LQFP, and 32 QFN packages.

| 64<br>LQFP | 48<br>LQFP | 32<br>LQFP | Pin Name | Default | ALT0                     | ALT1     | ALT2   | ALT3      |

|------------|------------|------------|----------|---------|--------------------------|----------|--------|-----------|

|            | LULL       | LULL       |          |         |                          |          |        |           |

| 1          | 1          | 1          | TCK      | TCK     | GPIOD2                   |          |        |           |

| 2          | 2          | 2          | RESETB   | RESETB  | GPIOD4                   |          |        |           |

| 3          | 3          | Ι          | GPIOC0   | GPIOC0  | EXTAL                    | CLKINO   |        |           |

| 4          | 4          | _          | GPIOC1   | GPIOC1  | XTAL                     |          |        |           |

| 5          | 5          | 3          | GPIOC2   | GPIOC2  | TXD0                     | XB_OUT11 | XB_IN2 | CLKO0     |

| 6          | _          | _          | GPIOF8   | GPIOF8  | RXD0                     | XB_OUT10 | CMPD_O | PWM_2X    |

| 7          | 6          | 4          | GPIOC3   | GPIOC3  | TA0                      | CMPA_O   | RXD0   | CLKIN1    |

| 8          | 7          | 5          | GPIOC4   | GPIOC4  | TA1                      | CMPB_O   | XB_IN6 | EWM_OUT_B |

| 9          | _          | _          | GPIOA7   | GPIOA7  | ANA7&CMPD_IN3            |          |        |           |

| 10         | _          | _          | GPIOA6   | GPIOA6  | ANA6&CMPD_IN2            |          |        |           |

| 11         | _          | _          | GPIOA5   | GPIOA5  | ANA5&CMPD_IN1            |          |        |           |

| 12         | 8          | _          | GPIOA4   | GPIOA4  | ANA4&CMPD_IN0            |          |        |           |

| 13         | 9          | 6          | GPIOA0   | GPIOA0  | ANA0&CMPA_IN3            | CMPC_O   |        |           |

| 14         | 10         | 7          | GPIOA1   | GPIOA1  | ANA1&CMPA_IN0            |          |        |           |

| 15         | 11         | 8          | GPIOA2   | GPIOA2  | ANA2&VREFHA&CMPA_<br>IN1 |          |        |           |

| 16         | 12         | _          | GPIOA3   | GPIOA3  | ANA3&VREFLA&CMPA_<br>IN2 |          |        |           |

| 17         | _          | _          | GPIOB7   | GPIOB7  | ANB7&CMPB_IN2            |          |        |           |

| 18         | 13         | _          | GPIOC5   | GPIOC5  | DACA_O                   | XB_IN7   |        |           |

| 19         | -          | _          | GPIOB6   | GPIOB6  | ANB6&CMPB_IN1            |          |        |           |

Figure 24. 48-pin LQFP

### NOTE

The RESETB pin is a 3.3 V pin only.

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, and I2C are trademarks of NXP B.V. All other product or service names are the property of their respective owners. All rights reserved.

© 2013–2016 NXP B.V.

Document Number MC56F827XXDS Revision 3.0, 09/2016