#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                          |

| Core Size                  | 16/32-Bit                                                                      |

| Speed                      | 55MHz                                                                          |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 62                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                                  |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-LQFP                                                                       |

| Supplier Device Package    | 100-LQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x128b-au-999 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• The GPNVM Bit 1 is used as a brownout reset enable signal for the reset controller. Setting the GPNVM Bit 1 enables the brownout reset when a brownout is detected, Clearing the GPNVM Bit 1 disables the brownout reset. Asserting ERASE disables the brownout reset by default.

# 8.5.6 Calibration Bits

Eight NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

# 8.6 Fast Flash Programming Interface

The Fast Flash Programming Interface allows programming the device through either a serial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang-programming with market-standard industrial programmers.

The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.

The Fast Flash Programming Interface is enabled and the Fast Programming Mode is entered when the TST pin and the PA0 and PA1 pins are all tied high.

# 8.7 SAM-BA Boot Assistant

The SAM-BA Boot Assistant is a default Boot Program that provides an easy way to program in-situ the on-chip Flash memory.

The SAM-BA Boot Assistant supports serial communication via the DBGU or the USB Device Port.

- Communication via the DBGU supports a wide range of crystals from 3 to 20 MHz via software auto-detection.

- Communication via the USB Device Port is limited to an 18.432 MHz crystal.

The SAM-BA Boot provides an interface with SAM-BA Graphic User Interface (GUI).

The SAM-BA Boot is in ROM and is mapped at address 0x0 when the GPNVM Bit 2 is set to 0.

When GPNVM bit 2 is set to 1, the device boots from the Flash.

When GPNVM bit 2 is set to 0, the device boots from ROM (SAM-BA).

# • PAGEN: Page Number

| Command                                   | PAGEN Description                                                           |

|-------------------------------------------|-----------------------------------------------------------------------------|

| Write Page Command                        | PAGEN defines the page number to be written.                                |

| Write Page and Lock Command               | PAGEN defines the page number to be written and its associated lock region. |

| Erase All Command                         | This field is meaningless                                                   |

| Set/Clear Lock Bit Command                | PAGEN defines one page number of the lock region to be locked or unlocked.  |

| Set/Clear General Purpose NVM Bit Command | PAGEN defines the general-purpose bit number.                               |

| Set Security Bit Command                  | This field is meaningless                                                   |

Note: Depending on the command, all the possible unused bits of PAGEN are meaningless.

# • KEY: Write Protection Key

This field should be written with the value 0x5A to enable the command defined by the bits of the register. If the field is written with a different value, the write is not performed and no action is started.

# 26.5 Debug Unit (DBGU) User Interface

| Offset          | Register                     | Name      | Access     | Reset |

|-----------------|------------------------------|-----------|------------|-------|

| 0x0000          | Control Register             | DBGU_CR   | Write-only | _     |

| 0x0004          | Mode Register                | DBGU_MR   | Read-write | 0x0   |

| 0x0008          | Interrupt Enable Register    | DBGU_IER  | Write-only | _     |

| 0x000C          | Interrupt Disable Register   | DBGU_IDR  | Write-only | _     |

| 0x0010          | Interrupt Mask Register      | DBGU_IMR  | Read-only  | 0x0   |

| 0x0014          | Status Register              | DBGU_SR   | Read-only  | _     |

| 0x0018          | Receive Holding Register     | DBGU_RHR  | Read-only  | 0x0   |

| 0x001C          | Transmit Holding Register    | DBGU_THR  | Write-only | _     |

| 0x0020          | Baud Rate Generator Register | DBGU_BRGR | Read-write | 0x0   |

| 0x0024 - 0x003C | Reserved                     | _         | _          | _     |

| 0x0040          | Chip ID Register             | DBGU_CIDR | Read-only  | _     |

| 0x0044          | Chip ID Extension Register   | DBGU_EXID | Read-only  | _     |

| 0x0048          | Force NTRST Register         | DBGU_FNR  | Read-write | 0x0   |

| 0x004C - 0x00FC | Reserved                     | _         | _          | _     |

| 0x0100 - 0x0124 | PDC Area                     | _         | _          | _     |

# Table 26-2. Register Mapping

# 27.6.5 PIO Controller Output Disable Register

| Name:        | PIO_ODR    |     |     |     |     |     |     |

|--------------|------------|-----|-----|-----|-----|-----|-----|

| Access Type: | Write-only | 1   |     |     |     |     |     |

| 31           | 30         | 29  | 28  | 27  | 26  | 25  | 24  |

| P31          | P30        | P29 | P28 | P27 | P26 | P25 | P24 |

| 23           | 22         | 21  | 20  | 19  | 18  | 17  | 16  |

| P23          | P22        | P21 | P20 | P19 | P18 | P17 | P16 |

| 15           | 14         | 13  | 12  | 11  | 10  | 9   | 8   |

| P15          | P14        | P13 | P12 | P11 | P10 | P9  | P8  |

| 7            | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

| P7           | P6         | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0-P31: Output Disable

0 = No effect.

1 = Disables the output on the I/O line.

## 27.6.6 PIO Controller Output Status Register

| Name: | PIO_OSR |

|-------|---------|

|       |         |

Access Type: Read-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Output Status

0 = The I/O line is a pure input.

1 = The I/O line is enabled in output.

#### 28.6.3.3 Clock Generation

The SPI Baud rate clock is generated by dividing the Master Clock (MCK), by a value between 1 and 255.

This allows a maximum operating baud rate at up to Master Clock and a minimum operating baud rate of MCK divided by 255.

Programming the SCBR field at 0 is forbidden. Triggering a transfer while SCBR is at 0 can lead to unpredictable results.

At reset, SCBR is 0 and the user has to program it at a valid value before performing the first transfer.

The divisor can be defined independently for each chip select, as it has to be programmed in the SCBR field of the Chip Select Registers. This allows the SPI to automatically adapt the baud rate for each interfaced peripheral without reprogramming.

#### 28.6.3.4 Transfer Delays

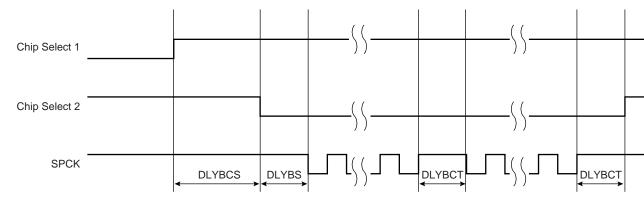

Figure 28-7 shows a chip select transfer change and consecutive transfers on the same chip select. Three delays can be programmed to modify the transfer waveforms:

- The delay between chip selects, programmable only once for all the chip selects by writing the DLYBCS field in the Mode Register. Allows insertion of a delay between release of one chip select and before assertion of a new one.

- The delay before SPCK, independently programmable for each chip select by writing the field DLYBS. Allows the start of SPCK to be delayed after the chip select has been asserted.

- The delay between consecutive transfers, independently programmable for each chip select by writing the DLYBCT field. Allows insertion of a delay between two transfers occurring on the same chip select

These delays allow the SPI to be adapted to the interfaced peripherals and their speed and bus release time.

#### Figure 28-7. Programmable Delays

#### 28.6.3.5 Peripheral Selection

The serial peripherals are selected through the assertion of the NPCS0 to NPCS3 signals. By default, all the NPCS signals are high before and after each transfer.

The peripheral selection can be performed in two different ways:

- Fixed Peripheral Select: SPI exchanges data with only one peripheral

- Variable Peripheral Select: Data can be exchanged with more than one peripheral

Fixed Peripheral Select is activated by writing the PS bit to zero in SPI\_MR (Mode Register). In this case, the current peripheral is defined by the PCS field in SPI\_MR and the PCS field in the SPI\_TDR has no effect.

Variable Peripheral Select is activated by setting PS bit to one. The PCS field in SPI\_TDR is used to select the current peripheral. This means that the peripheral selection can be defined for each new data.

The Fixed Peripheral Selection allows buffer transfers with a single peripheral. Using the PDC is an optimal means, as the size of the data transfer between the memory and the SPI is either 8 bits or 16 bits. However, changing the peripheral selection requires the Mode Register to be reprogrammed.

# Atmel

# 29.6.2 TWI Master Mode Register

| Register Name: | TWI_MN  | /IR  |       |      |    |        |    |

|----------------|---------|------|-------|------|----|--------|----|

| Address Type:  | Read-wr | rite |       |      |    |        |    |

| 31             | 30      | 29   | 28    | 27   | 26 | 25     | 24 |

| -              | -       | -    | -     | -    | -  | -      | -  |

| 23             | 22      | 21   | 20    | 19   | 18 | 17     | 16 |

| _              |         |      |       | DADR |    |        |    |

| 15             | 14      | 13   | 12    | 11   | 10 | 9      | 8  |

| —              | _       | —    | MREAD | -    | _  | IADRSZ |    |

| 7              | 6       | 5    | 4     | 3    | 2  | 1      | 0  |

| -              | _       | _    | -     | -    | _  | —      | _  |

# • IADRSZ: Internal Device Address Size

#### Table 29-4.

| IADRSZ[9:8] |                                                      |                                    |  |  |

|-------------|------------------------------------------------------|------------------------------------|--|--|

| 0           | 0 No internal device address (Byte command protocol) |                                    |  |  |

| 0           | 1                                                    | One-byte internal device address   |  |  |

| 1           | 0                                                    | Two-byte internal device address   |  |  |

| 1           | 1                                                    | Three-byte internal device address |  |  |

## • MREAD: Master Read Direction

0 = Master write direction.

1 = Master read direction.

# • DADR: Device Address

The device address is used to access slave devices in read or write mode.

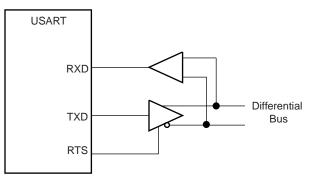

#### 30.6.6 RS485 Mode

The USART features the RS485 mode to enable line driver control. While operating in RS485 mode, the USART behaves as though in asynchronous or synchronous mode and configuration of all the parameters is possible. The difference is that the RTS pin is driven high when the transmitter is operating. The behavior of the RTS pin is controlled by the TXEMPTY bit. A typical connection of the USART to a RS485 bus is shown in Figure 30-26.

The USART is set in RS485 mode by programming the USART\_MODE field in the Mode Register (US\_MR) to the value 0x1.

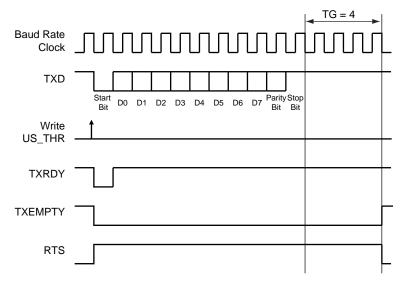

The RTS pin is at a level inverse to the TXEMPTY bit. Significantly, the RTS pin remains high when a timeguard is programmed so that the line can remain driven after the last character completion. Figure 30-27 gives an example of the RTS waveform during a character transmission when the timeguard is enabled.

#### Figure 30-27. Example of RTS Drive with Timeguard

# 30.7.8 USART Transmit Holding Register

| Name:        | US_THR   | ł  |    |     |    |    |       |

|--------------|----------|----|----|-----|----|----|-------|

| Access Type: | Write-on | ly |    |     |    |    |       |

| 31           | 30       | 29 | 28 | 27  | 26 | 25 | 24    |

| -            | _        | _  | -  | -   | -  | -  | -     |

| 23           | 22       | 21 | 20 | 19  | 18 | 17 | 16    |

| -            | _        | _  | -  | -   | -  | _  | -     |

| 15           | 14       | 13 | 12 | 11  | 10 | 9  | 8     |

| TXSYNH       | -        | -  | -  | -   | -  | —  | TXCHR |

| 7            | 6        | 5  | 4  | 3   | 2  | 1  | 0     |

|              |          |    | TX | CHR |    |    |       |

# • TXCHR: Character to be Transmitted

Next character to be transmitted after the current character if TXRDY is not set.

# • TXSYNH: Sync Field to be transmitted

0: The next character sent is encoded as a data. Start Frame Delimiter is DATA SYNC.

1: The next character sent is encoded as a command. Start Frame Delimiter is COMMAND SYNC.

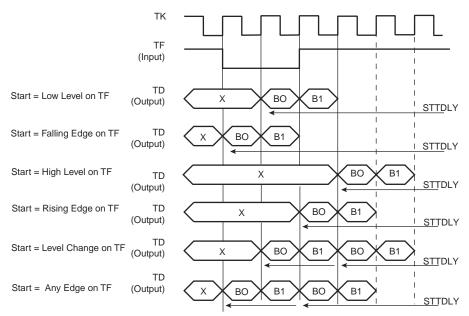

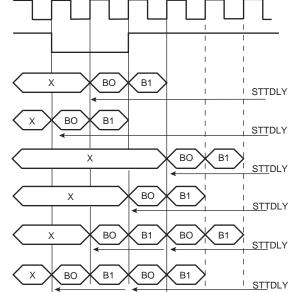

#### Figure 31-11. Receive Pulse/Edge Start Modes

|                            | RK            |         |

|----------------------------|---------------|---------|

|                            | RF<br>(Input) |         |

| Start = Low Level on RF    | RD<br>(Input) | ХВО     |

| Start = Falling Edge on RF | RD<br>(Input) | X BO B1 |

| Start = High Level on RF   | RD<br>(Input) |         |

| Start = Rising Edge on RF  | RD<br>(Input) |         |

| Start = Level Change on RF | RD<br>(Input) | X BO    |

| Start = Any Edge on RF     | RD<br>(Input) | X BO B1 |

# 31.8.4 SSC Receive Frame Mode Register

| Name:        | SSC_RF  | SSC_RFMR |    |       |        |    |        |  |  |  |

|--------------|---------|----------|----|-------|--------|----|--------|--|--|--|

| Access Type: | Read-wi | rite     |    |       |        |    |        |  |  |  |

| 31           | 30      | 29       | 28 | 27    | 26     | 25 | 24     |  |  |  |

| -            | _       | -        | -  | -     | -      | -  | FSEDGE |  |  |  |

| 23           | 22      | 21       | 20 | 19    | 18     | 17 | 16     |  |  |  |

| -            |         | FSOS     |    | FSLEN |        |    |        |  |  |  |

| 15           | 14      | 13       | 12 | 11    | 10     | 9  | 8      |  |  |  |

| -            | _       |          |    |       | DATNB  |    |        |  |  |  |

| 7            | 6       | 5        | 4  | 3     | 2      | 1  | 0      |  |  |  |

| MSBF         | —       | LOOP     |    |       | DATLEN |    |        |  |  |  |

# • DATLEN: Data Length

0: Forbidden value (1-bit data length not supported).

Any other value: The bit stream contains DATLEN + 1 data bits. Moreover, it defines the transfer size performed by the PDC2 assigned to the Receiver. If DATLEN is lower or equal to 7, data transfers are in bytes. If DATLEN is between 8 and 15 (included), half-words are transferred, and for any other value, 32-bit words are transferred.

## • LOOP: Loop Mode

0: Normal operating mode.

1: RD is driven by TD, RF is driven by TF and TK drives RK.

# • MSBF: Most Significant Bit First

0: The lowest significant bit of the data register is sampled first in the bit stream.

1: The most significant bit of the data register is sampled first in the bit stream.

# • DATNB: Data Number per Frame

This field defines the number of data words to be received after each transfer start, which is equal to (DATNB + 1).

# • FSLEN: Receive Frame Sync Length

This field defines the length of the Receive Frame Sync Signal and the number of bits sampled and stored in the Receive Sync Data Register. When this mode is selected by the START field in the Receive Clock Mode Register, it also determines the length of the sampled data to be compared to the Compare 0 or Compare 1 register.

Pulse length is equal to (FSLEN + 1) Receive Clock periods. Thus, if FSLEN is 0, the Receive Frame Sync signal is generated during one Receive Clock period.

# 32.6.5 TC Channel Mode Register: Waveform Mode

Register Name:TC\_CMRx [x=0..2] (WAVE = 1)Access Type:Read-write

| 31     | 30            | 29    | 28   | 27   | 26      | 25   | 24 |

|--------|---------------|-------|------|------|---------|------|----|

| BSV    | BSWTRG BEEVT  |       | BC   | BCPC |         | СРВ  |    |

| 23     | 22            | 21    | 20   | 19   | 18      | 17   | 16 |

| ASV    | /TRG          | A     | EEVT | ACPC |         | ACPA |    |

| 15     | 14            | 13    | 12   | 11   | 10      | 9    | 8  |

| WAVE   | WAVSEL ENETRG |       | EEVT |      | EEVTEDG |      |    |

| 7      | 6             | 5     | 4    | 3    | 2       | 1    | 0  |

| CPCDIS | CPCSTOP       | BURST |      | CLKI | TCCLKS  |      |    |

# • TCCLKS: Clock Selection

|   | TCCLKS |   | Clock Selected |

|---|--------|---|----------------|

| 0 | 0      | 0 | TIMER_CLOCK1   |

| 0 | 0      | 1 | TIMER_CLOCK2   |

| 0 | 1      | 0 | TIMER_CLOCK3   |

| 0 | 1      | 1 | TIMER_CLOCK4   |

| 1 | 0      | 0 | TIMER_CLOCK5   |

| 1 | 0      | 1 | XC0            |

| 1 | 1      | 0 | XC1            |

| 1 | 1      | 1 | XC2            |

# • CLKI: Clock Invert

0 = Counter is incremented on rising edge of the clock.

1 = Counter is incremented on falling edge of the clock.

# • BURST: Burst Signal Selection

| BUI | RST |                                               |

|-----|-----|-----------------------------------------------|

| 0   | 0   | The clock is not gated by an external signal. |

| 0   | 1   | XC0 is ANDed with the selected clock.         |

| 1   | 0   | XC1 is ANDed with the selected clock.         |

| 1   | 1   | XC2 is ANDed with the selected clock.         |

# • CPCSTOP: Counter Clock Stopped with RC Compare

0 = Counter clock is not stopped when counter reaches RC.

1 = Counter clock is stopped when counter reaches RC.

# CPCDIS: Counter Clock Disable with RC Compare

0 = Counter clock is not disabled when counter reaches RC.

1 = Counter clock is disabled when counter reaches RC.

Atmel

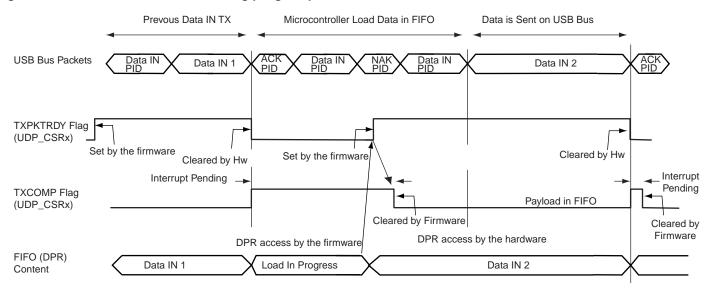

Figure 34-6. Data IN Transfer for Non Ping-pong Endpoint

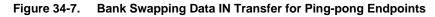

## Using Endpoints With Ping-pong Attribute

The use of an endpoint with ping-pong attributes is necessary during isochronous transfer. This also allows handling the maximum bandwidth defined in the USB specification during bulk transfer. To be able to guarantee a constant or the maximum bandwidth, the microcontroller must prepare the next data payload to be sent while the current one is being sent by the USB device. Thus two banks of memory are used. While one is available for the microcontroller, the other one is locked by the USB device.

When using a ping-pong endpoint, the following procedures are required to perform Data IN transactions:

# Atmel

# 36.6 CAN Controller Features

## 36.6.1 CAN Protocol Overview

The Controller Area Network (CAN) is a multi-master serial communication protocol that efficiently supports real-time control with a very high level of security with bit rates up to 1 Mbit/s.

The CAN protocol supports four different frame types:

- Data frames: They carry data from a transmitter node to the receiver nodes. The overall maximum data frame length is 108 bits for a standard frame and 128 bits for an extended frame.

- Remote frames: A destination node can request data from the source by sending a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node then sends a data frame as a response to this node request.

- Error frames: An error frame is generated by any node that detects a bus error.

- Overload frames: They provide an extra delay between the preceding and the successive data frames or remote frames.

The Atmel CAN controller provides the CPU with full functionality of the CAN protocol V2.0 Part A and V2.0 Part B. It minimizes the CPU load in communication overhead. The Data Link Layer and part of the physical layer are automatically handled by the CAN controller itself.

The CPU reads or writes data or messages via the CAN controller mailboxes. An identifier is assigned to each mailbox. The CAN controller encapsulates or decodes data messages to build or to decode bus data frames. Remote frames, error frames and overload frames are automatically handled by the CAN controller under supervision of the software application.

## 36.6.2 Mailbox Organization

The CAN module has 8 buffers, also called channels or mailboxes. An identifier that corresponds to the CAN identifier is defined for each active mailbox. Message identifiers can match the standard frame identifier or the extended frame identifier. This identifier is defined for the first time during the CAN initialization, but can be dynamically reconfigured later so that the mailbox can handle a new message family. Several mailboxes can be configured with the same ID.

Each mailbox can be configured in receive or in transmit mode independently. The mailbox object type is defined in the MOT field of the CAN\_MMRx register.

#### 36.6.2.1 Message Acceptance Procedure

If the MIDE field in the CAN\_MIDx register is set, the mailbox can handle the extended format identifier; otherwise, the mailbox handles the standard format identifier. Once a new message is received, its ID is masked with the CAN\_MAMx value and compared with the CAN\_MIDx value. If accepted, the message ID is copied to the CAN\_MIDx register.

It is also possible to configure a mailbox in Consumer Mode. In this mode, after each transfer request, a remote frame is automatically sent. The first answer received is stored in the corresponding mailbox data registers.

Several mailboxes can be chained to receive a buffer. They must be configured with the same ID in Receive Mode, except for the last one, which can be configured in Receive with Overwrite Mode. The last mailbox can be used to detect a buffer overflow.

| Mailbox Object Type    | Description                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive                | The first message received is stored in mailbox data registers. Data remain available until the next transfer request.                                                                                                                      |

| Receive with overwrite | The last message received is stored in mailbox data register. The next message always overwrites the previous one. The application has to check whether a new message has not overwritten the current one while reading the data registers. |

| Consumer               | A remote frame is sent by the mailbox. The answer received is stored in mailbox data register.<br>This extends Receive mailbox features. Data remain available until the next transfer request.                                             |

#### 36.6.2.3 Transmit Mailbox

When transmitting a message, the message length and data are written to the transmit mailbox with the correct identifier. For each transmit mailbox, a priority is assigned. The controller automatically sends the message with the highest priority first (set with the field PRIOR in CAN\_MMRx register).

It is also possible to configure a mailbox in Producer Mode. In this mode, when a remote frame is received, the mailbox data are sent automatically. By enabling this mode, a producer can be done using only one mailbox instead of two: one to detect the remote frame and one to send the answer.

| Mailbox Object Type                                                                                                                                                                                                                                                 | Description |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| TransmitThe message stored in the mailbox data registers will try to win the bus arbitration imme<br>or later according to or not the Time Management Unit configuration (see Section 36.6.3)The application is notified that the message has been sent or aborted. |             |

| Producer The message prepared in the mailbox data registers will be sent after receiving the new frame. This extends transmit mailbox features.                                                                                                                     |             |

#### 36.6.4 CAN 2.0 Standard Features

#### 36.6.4.1 CAN Bit Timing Configuration

All controllers on a CAN bus must have the same bit rate and bit length. At different clock frequencies of the individual controllers, the bit rate has to be adjusted by the time segments.

The CAN protocol specification partitions the nominal bit time into four different segments:

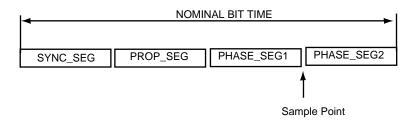

#### Figure 36-4. Partition of the CAN Bit Time

#### • TIME QUANTUM

The TIME QUANTUM (TQ) is a fixed unit of time derived from the MCK period. The total number of TIME QUANTA in a bit time is programmable from 8 to 25.

SYNC SEG: SYNChronization Segment.

This part of the bit time is used to synchronize the various nodes on the bus. An edge is expected to lie within this segment. It is 1 TQ long.

• PROP SEG: PROPagation Segment.

This part of the bit time is used to compensate for the physical delay times within the network. It is twice the sum of the signal's propagation time on the bus line, the input comparator delay, and the output driver delay. It is programmable to be 1,2,..., 8 TQ long.

This parameter is defined in the PROPAG field of the "CAN Baudrate Register".

• PHASE SEG1, PHASE SEG2: PHASE Segment 1 and 2.

The Phase-Buffer-Segments are used to compensate for edge phase errors. These segments can be lengthened (PHASE SEG1) or shortened (PHASE SEG2) by resynchronization.

Phase Segment 1 is programmable to be 1,2,..., 8 TQ long.

Phase Segment 2 length has to be at least as long as the Information Processing Time (IPT) and may not be more than the length of Phase Segment 1.

These parameters are defined in the PHASE1 and PHASE2 fields of the "CAN Baudrate Register".

• INFORMATION PROCESSING TIME:

The Information Processing Time (IPT) is the time required for the logic to determine the bit level of a sampled bit. The IPT begins at the sample point, is measured in TQ and **is fixed at 2 TQ for the Atmel CAN**. Since Phase Segment 2 also begins at the sample point and is the last segment in the bit time, PHASE SEG2 shall not be less than the IPT.

• SAMPLE POINT:

The SAMPLE POINT is the point in time at which the bus level is read and interpreted as the value of that respective bit. Its location is at the end of PHASE\_SEG1.

• SJW: ReSynchronization Jump Width.

The ReSynchronization Jump Width defines the limit to the amount of lengthening or shortening of the Phase Segments.

SJW is programmable to be the minimum of PHASE SEG1 and 4 TQ.

If the SMP field in the CAN\_BR register is set, then the incoming bit stream is sampled three times with a period of half a CAN clock period, centered on sample point.

```

Tphs1 + Tphs2 = 12 Tcsc

Because this number is even, we choose Tphs2 = Tphs1 (else we would choose Tphs2

= Tphs1 + Tcsc)

Tphs1 = Tphs2 = (12/2) Tcsc = 6 Tcsc

=> PHASE1 = PHASE2 = Tphs1/Tcsc - 1 = 5

The resynchronization jump width must be comprised between 1 Tcsc and the

minimum of 4 Tcsc and Tphs1. We choose its maximum value:

Tsjw = Min(4 Tcsc,Tphs1) = 4 Tcsc

=> SJW = Tsjw/Tcsc - 1 = 3

Finally: CAN_BR = 0x00053255

```

#### 36.6.4.2 CAN Bus Synchronization

Two types of synchronization are distinguished: "hard synchronization" at the start of a frame and "resynchronization" inside a frame. After a hard synchronization, the bit time is restarted with the end of the SYNC\_SEG segment, regardless of the phase error. Resynchronization causes a reduction or increase in the bit time so that the position of the sample point is shifted with respect to the detected edge.

The effect of resynchronization is the same as that of hard synchronization when the magnitude of the phase error of the edge causing the resynchronization is less than or equal to the programmed value of the resynchronization jump width  $(t_{SJW})$ .

When the magnitude of the phase error is larger than the resynchronization jump width and

- the phase error is positive, then PHASE\_SEG1 is lengthened by an amount equal to the resynchronization jump width.

- the phase error is negative, then PHASE\_SEG2 is shortened by an amount equal to the resynchronization jump width.

# 37.5.26.9 Late Collisions Register

| Register Name: | EMAC_  | LCOL |    |    |    |    |    |

|----------------|--------|------|----|----|----|----|----|

| Access Type:   | Read-w | rite |    |    |    |    |    |

| 31             | 30     | 29   | 28 | 27 | 26 | 25 | 24 |

| -              | _      | -    | -  | -  | -  | -  | -  |

| 23             | 22     | 21   | 20 | 19 | 18 | 17 | 16 |

| -              | _      | -    | _  | _  | _  | _  | -  |

| 15             | 14     | 13   | 12 | 11 | 10 | 9  | 8  |

| -              | _      | -    | -  | -  | _  | _  | -  |

| 7              | 6      | 5    | 4  | 3  | 2  | 1  | 0  |

|                |        |      | LC | OL |    |    |    |

# • LCOL: Late Collisions

An 8-bit register counting the number of frames that experience a collision after the slot time (512 bits) has expired. A late collision is counted twice; i.e., both as a collision and a late collision.

#### **Register Name:** EMAC\_EXCOL Access Type: Read-write 31 30 29 28 27 26 25 24 \_ \_ \_ \_ \_ \_ \_ \_ 23 22 21 20 19 18 17 16 \_ \_ \_ \_ \_ \_ \_ \_ 15 13 12 10 9 14 11 8 \_ -\_ \_ \_ \_ \_ \_ 7 6 5 4 2 0 3 1 EXCOL

# 37.5.26.10Excessive Collisions Register

#### • EXCOL: Excessive Collisions

An 8-bit register counting the number of frames that failed to be transmitted because they experienced 16 collisions.

# Table 38-3. 1.8V Voltage Regulator Characteristics

| I <sub>VDDIN</sub> | Current consumption       | After startup, no load                              | 90 |     | μA |

|--------------------|---------------------------|-----------------------------------------------------|----|-----|----|

|                    |                           | After startup, Idle mode, no load                   | 10 | 25  | μA |

| T <sub>START</sub> | Startup Time              | $C_{load}$ = 2.2 µF, after V <sub>DDIN</sub> > 2.7V |    | 150 | μS |

| Ι <sub>Ο</sub>     | Maximum DC Output Current | $V_{DDIN} = 3.3V$                                   |    | 100 | mA |

| Ι <sub>Ο</sub>     | Maximum DC Output Current | V <sub>DDIN</sub> = 3.3V, in Idle Mode              |    | 1   | mA |

# Table 38-4. Brownout Detector Characteristics

| Symbol              | Parameter                | Conditions                                                      | Min  | Тур  | Max  | Units |

|---------------------|--------------------------|-----------------------------------------------------------------|------|------|------|-------|

| V <sub>BOT18-</sub> | VDDCORE Threshold Level  |                                                                 | 1.65 | 1.68 | 1.71 | V     |

| V <sub>HYST18</sub> | VDDCORE Hysteresis       | $V_{HYST18} = V_{BOT18+} - V_{BOT18-}$                          |      | 50   | 65   | mV    |

| V <sub>BOT33-</sub> | VDDFLASH Threshold Level |                                                                 | 2.70 | 2.80 | 2.90 | V     |

| V <sub>HYST33</sub> | VDDFLASH Hysteresis      | V <sub>HYST33</sub> = V <sub>BOT33+</sub> - V <sub>BOT33-</sub> |      | 70   | 120  | mV    |

|                     | Current Consumption      | BOD on (GPNVM0 bit active)                                      |      | 24   | 30   | μA    |

| DD                  | Current Consumption      | BOD off (GPNVM0 bit inactive)                                   |      |      | 1    | μA    |

| T <sub>START</sub>  | Startup Time             |                                                                 |      | 100  | 200  | μs    |

# Table 38-5. DC Flash Characteristics SAM7X512/256/128

| Symbol          | Parameter               | Conditions                   | Min | Мах                                              | Units |

|-----------------|-------------------------|------------------------------|-----|--------------------------------------------------|-------|

| T <sub>PU</sub> | Power-up delay          |                              |     | 45                                               | μS    |

| -               |                         | @25°C                        |     |                                                  |       |

|                 |                         | onto VDDCORE = 1.8V          |     | 10                                               |       |

|                 | Ctop allow as more than | onto VDDFLASH = 3.3V         | 45  | μA                                               |       |

| I <sub>SB</sub> | Standby current         | @85°C                        |     |                                                  |       |

|                 |                         | onto VDDCORE = 1.8V          |     | 45<br>10<br>30<br>10<br>120<br>3.0<br>0.8<br>400 |       |

|                 |                         | onto VDDFLASH = 3.3V         |     |                                                  | μA    |

|                 |                         | Random Read @ 30MHz          |     |                                                  |       |

|                 |                         | onto VDDCORE = 1.8V          |     | 3.0                                              |       |

|                 |                         | onto VDDFLASH = 3.3V         |     | 45<br>10<br>30<br>10<br>120<br>3.0<br>0.8<br>400 | mA    |

| I <sub>CC</sub> | Active current          | Write (one bank for SAMX512) |     |                                                  |       |

|                 |                         | onto VDDCORE = 1.8V          |     | 400                                              | μA    |

|                 |                         | onto VDDFLASH = 3.3V         |     | 45<br>10<br>30<br>10<br>120<br>3.0<br>0.8<br>400 | mA    |

# 38.4 Crystal Oscillators Characteristics

# 38.4.1 RC Oscillator Characteristics

#### Table 38-8. RC Oscillator Characteristics

| Symbol                 | Parameter               | Conditions                  | Min | Тур | Max | Unit |

|------------------------|-------------------------|-----------------------------|-----|-----|-----|------|

| 1/(t <sub>CPRC</sub> ) | RC Oscillator Frequency | $V_{DDPLL} = 1.65V$         | 22  | 32  | 42  | kHz  |

|                        | Duty Cycle              |                             | 45  | 50  | 55  | %    |

| t <sub>ST</sub>        | Startup Time            | $V_{\text{DDPLL}} = 1.65 V$ |     |     | 75  | μs   |

| I <sub>OSC</sub>       | Current Consumption     | After Startup Time          |     |     | 1.9 | μA   |

Do not disable a channel before completion of one period of the selected clock.

# 41.3.6 Real Time Timer (RTT)

### 41.3.6.1 RTT: Possible Event Loss when Reading RTT\_SR

If an event (RTTINC or ALMS) occurs within the same slow clock cycle during which the RTT\_SR is read, the corresponding bit might be cleared. This can lead to the loss of this event. Problem Fix/Workaround:

The software must handle the RTT event as an interrupt and should not poll RTT\_SR.

#### 41.3.7 Serial Peripheral Interface (SPI)

#### 41.3.7.1 SPI: Bad tx\_ready Behavior when CSAAT = 1 and SCBR = 1

If the SPI2 is programmed with CSAAT = 1, SCBR(baudrate) = 1 and two transfers are performed consecutively on the same slave with an IDLE state between them, the tx\_ready signal does not rise after the second data has been transferred in the shifter. This can imply for example, that the second data is sent twice. Problem Fix/Workaround

Do not use the combination CSAAT = 1 and SCBR = 1.

#### 41.3.7.2 SPI: LASTXFER (Last Transfer) Behavior

In FIXED Mode, with CSAAT bit set, and in "PDC mode" the Chip Select can rise depending on the data written in the SPI\_TDR when the TX\_EMPTY flag is set. If for example, the PDC writes a "1" in the bit 24 (LASTXFER bit) of the SPI\_TDR, the chip select will rise as soon as the TXEMPTY flag is set.

Problem Fix/Workaround

Use the CS in PIO mode when PDC mode is required and CS has to be maintained between transfers.

#### 41.3.7.3 SPI: SPCK Behavior in Master Mode

SPCK pin can toggle out before the first transfer in Master Mode. Problem Fix/Workaround

In Master Mode, MSTR bit must be set (in SPI\_MR register) before configuring SPI\_CSRx registers.

#### 41.3.7.4 SPI: Chip Select and Fixed Mode

In fixed Mode, if a transfer is performed through a PDC on a Chip select different from the Chip select 0, the output spi\_size sampled by the PDC will depend on the field, BITS (Bits per Transfer) of SPI\_CSR0 register, whatever the selected Chip select is. For example, if SPI\_CSR0 is configured for a 10-bit transfer whereas SPI\_CSR1 is configured for an 8-bit transfer, when a transfer is performed in Fixed mode through the PDC, on Chip select 1, the transfer will be considered as a HalfWord transfer.

Problem Fix/Workaround

If a PDC transfer has to be performed in 8 bits, on a Chip select y (y as different from 0), the BITS field of the SPI\_CSR0 must be configured in 8 bits, in the same way as the BITS field of the CSRy Register.

#### 41.3.7.5 SPI: Baudrate Set to 1

When Baudrate is set at 1 (i.e. when serial clock frequency equals the system clock frequency) and when the BITS field of the SPI\_CSR register (number of bits to be transmitted) equals an ODD value (in this case 9,11,13 or 15), an additional pulse will be generated on output SPCK.

Everything is OK if the BITS field equals 8,10,12,14 or 16 and Baudrate = 1. Problem Fix/Workaround

# Atmel