# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                      |

| Core Size                  | 16/32-Bit                                                                  |

| Speed                      | 55MHz                                                                      |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                              |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-LQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x128b-au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 9.1 Reset Controller

- Based on one power-on reset cell and one brownout detector

- Status of the last reset, either Power-up Reset, Software Reset, User Reset, Watchdog Reset, Brownout Reset

- Controls the internal resets and the NRST pin output

- Allows to shape a signal on the NRST line, guaranteeing that the length of the pulse meets any requirement.

#### 9.1.1 Brownout Detector and Power-on Reset

The SAM7X512/256/128 embeds one brownout detection circuit and a power-on reset cell. The power-on reset is supplied with and monitors VDDCORE.

Both signals are provided to the Flash to prevent any code corruption during power-up or power-down sequences or if brownouts occur on the power supplies.

The power-on reset cell has a limited-accuracy threshold at around 1.5V. Its output remains low during power-up until VDDCORE goes over this voltage level. This signal goes to the reset controller and allows a full re-initialization of the device.

The brownout detector monitors the VDDCORE and VDDFLASH levels during operation by comparing them to a fixed trigger level. It secures system operations in the most difficult environments and prevents code corruption in case of brownout on the VDDCORE or VDDFLASH.

When the brownout detector is enabled and VDDCORE decreases to a value below the trigger level (Vbot18-, defined as Vbot18 - hyst/2), the brownout output is immediately activated.

When VDDCORE increases above the trigger level (Vbot18+, defined as Vbot18 + hyst/2), the reset is released. The brownout detector only detects a drop if the voltage on VDDCORE stays below the threshold voltage for longer than about 1µs.

The VDDCORE threshold voltage has a hysteresis of about 50 mV, to ensure spike free brownout detection. The typical value of the brownout detector threshold is 1.68V with an accuracy of  $\pm 2\%$  and is factory calibrated.

When the brownout detector is enabled and VDDFLASH decreases to a value below the trigger level (Vbot33-, defined as Vbot33 - hyst/2), the brownout output is immediately activated.

When VDDFLASH increases above the trigger level (Vbot33+, defined as Vbot33 + hyst/2), the reset is released. The brownout detector only detects a drop if the voltage on VDDCORE stays below the threshold voltage for longer than about 1µs.

The VDDFLASH threshold voltage has a hysteresis of about 50 mV, to ensure spike free brownout detection. The typical value of the brownout detector threshold is 2.80V with an accuracy of  $\pm$  3.5% and is factory calibrated.

The brownout detector is low-power, as it consumes less than 28  $\mu$ A static current. However, it can be deactivated to save its static current. In this case, it consumes less than 1 $\mu$ A. The deactivation is configured through the GPNVM bit 0 of the Flash.

## 18.4.2 MC Abort Status Register

| Register Name | : MC_AS | R   |    |        |           |           |            |

|---------------|---------|-----|----|--------|-----------|-----------|------------|

| Access Type:  | Read-or | nly |    |        |           |           |            |

| Reset Value:  | 0x0     |     |    |        |           |           |            |

| Offset:       | 0x04    |     |    |        |           |           |            |

| 31            | 30      | 29  | 28 | 27     | 26        | 25        | 24         |

| -             | _       | -   | -  | -      | SVMST_ARM | SVMST_PDC | SVMST_EMAC |

| 23            | 22      | 21  | 20 | 19     | 18        | 17        | 16         |

| -             | _       | -   | -  | -      | MST_ARM   | MST_PDC   | MST_EMAC   |

| 15            | 14      | 13  | 12 | 11     | 10        | 9         | 8          |

| -             | _       | -   | -  | ABTTYP |           | ABTSZ     |            |

| 7             | 6       | 5   | 4  | 3      | 2         | 1         | 0          |

| _             | _       | -   | -  | _      | -         | MISADD    | UNDADD     |

#### • UNDADD: Undefined Address Abort Status

0: The last abort was not due to the access of an undefined address in the address space.

1: The last abort was due to the access of an undefined address in the address space.

#### • MISADD: Misaligned Address Abort Status

0: The last aborted access was not due to an address misalignment.

1: The last aborted access was due to an address misalignment.

#### • ABTSZ: Abort Size Status

| AB | Abort Size |           |

|----|------------|-----------|

| 0  | 0          | Byte      |

| 0  | 1          | Half-word |

| 1  | 0          | Word      |

| 1  | 1          | Reserved  |

#### • ABTTYP: Abort Type Status

| ABT | Abort Type |            |

|-----|------------|------------|

| 0   | 0          | Data Read  |

| 0   | 1          | Data Write |

| 1   | 0          | Code Fetch |

| 1   | 1          | Reserved   |

#### • MST\_EMAC: EMAC Abort Source

0: The last aborted access was not due to the EMAC.

1: The last aborted access was due to the EMAC.

#### Table 20-1. Signal Description List (Continued)

| Signal Name | Function                                                                                          | Туре         | Active<br>Level | Comments                   |  |

|-------------|---------------------------------------------------------------------------------------------------|--------------|-----------------|----------------------------|--|

| VDDPLL      | PLL Power Supply                                                                                  | Power        |                 |                            |  |

| GND         | Ground                                                                                            | Ground       |                 |                            |  |

|             | Clock                                                                                             | ks           |                 |                            |  |

|             | Main Clock Input.                                                                                 |              |                 |                            |  |

| XIN         | This input can be tied to GND. In this case, the device is clocked by the internal RC oscillator. | Input        |                 | 32KHz to 50MHz             |  |

|             | Tes                                                                                               | t            |                 |                            |  |

| TST         | Test Mode Select                                                                                  | Input        | High            | Must be connected to VDDIO |  |

| PGMEN0      | Test Mode Select                                                                                  | Input        | High            | Must be connected to VDDIO |  |

| PGMEN1      | Test Mode Select                                                                                  | Input        | High            | Must be connected to VDDIO |  |

|             | PIO                                                                                               | )            |                 |                            |  |

| PGMNCMD     | Valid command available                                                                           | Input        | Low             | Pulled-up input at reset   |  |

| PGMRDY      | 0: Device is busy                                                                                 | <b>0</b>     |                 |                            |  |

| PGMRDY      | 1: Device is ready for a new command                                                              | Output       | High            | Pulled-up input at reset   |  |

| PGMNOE      | Output Enable (active high)                                                                       | Input        | Low             | Pulled-up input at reset   |  |

| PGMNVALID   | 0: DATA[15:0] is in input mode                                                                    | Output       | Low             | Dulled up input at reast   |  |

| PGIVINVALID | 1: DATA[15:0] is in output mode                                                                   | Output       | Low             | Pulled-up input at reset   |  |

| PGMM[3:0]   | Specifies DATA type (See Table 20-2)                                                              | Input        |                 | Pulled-up input at reset   |  |

| PGMD[15:0]  | Bi-directional data bus                                                                           | Input/Output |                 | Pulled-up input at reset   |  |

#### 20.2.2 Signal Names

Depending on the MODE settings, DATA is latched in different internal registers.

| Table 20-2. Mod | e Coding |                       |

|-----------------|----------|-----------------------|

| MODE[3:0]       | Symbol   | Data                  |

| 0000            | CMDE     | Command Register      |

| 0001            | ADDR0    | Address Register LSBs |

| 0010            | ADDR1    |                       |

| 0101            | DATA     | Data Register         |

| Default         | IDLE     | No register           |

When MODE is equal to CMDE, then a new command (strobed on DATA[15:0] signals) is stored in the command register.

| Table 20-3. | Command Bit Coding |

|-------------|--------------------|

|-------------|--------------------|

| DATA[15:0] | Symbol | Command Executed          |

|------------|--------|---------------------------|

| 0x0011     | READ   | Read Flash                |

| 0x0012     | WP     | Write Page Flash          |

| 0x0022     | WPL    | Write Page and Lock Flash |

| 0x0032     | EWP    | Erase Page and Write Page |

#### 23.8.12 AIC Interrupt Disable Command Register

| Register Name:<br>Access Type: | AIC_IDC<br>Write-on |       |       |       |       |       |       |

|--------------------------------|---------------------|-------|-------|-------|-------|-------|-------|

| 31                             | 30                  | 29    | 28    | 27    | 26    | 25    | 24    |

| PID31                          | PID30               | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23                             | 22                  | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23                          | PID22               | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15                             | 14                  | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15                          | PID14               | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7                              | 6                   | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7                           | PID6                | PID5  | PID4  | PID3  | PID2  | SYS   | FIQ   |

#### • FIQ, SYS, PID2-PID31: Interrupt Disable

0 = No effect.

1 = Disables corresponding interrupt.

#### 23.8.13 AIC Interrupt Clear Command Register

| Register Name:<br>Access Type: | AIC_ICC<br>Write-on |       |       |       |       |       |       |

|--------------------------------|---------------------|-------|-------|-------|-------|-------|-------|

| 31                             | 30                  | 29    | 28    | 27    | 26    | 25    | 24    |

| PID31                          | PID30               | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23                             | 22                  | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23                          | PID22               | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15                             | 14                  | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15                          | PID14               | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7                              | 6                   | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7                           | PID6                | PID5  | PID4  | PID3  | PID2  | SYS   | FIQ   |

#### • FIQ, SYS, PID2-PID31: Interrupt Clear

0 = No effect.

1 = Clears corresponding interrupt.

#### 26.4.2 Receiver

#### 26.4.2.1 Receiver Reset, Enable and Disable

After device reset, the Debug Unit receiver is disabled and must be enabled before being used. The receiver can be enabled by writing the control register DBGU\_CR with the bit RXEN at 1. At this command, the receiver starts looking for a start bit.

The programmer can disable the receiver by writing DBGU\_CR with the bit RXDIS at 1. If the receiver is waiting for a start bit, it is immediately stopped. However, if the receiver has already detected a start bit and is receiving the data, it waits for the stop bit before actually stopping its operation.

The programmer can also put the receiver in its reset state by writing DBGU\_CR with the bit RSTRX at 1. In doing so, the receiver immediately stops its current operations and is disabled, whatever its current state. If RSTRX is applied when data is being processed, this data is lost.

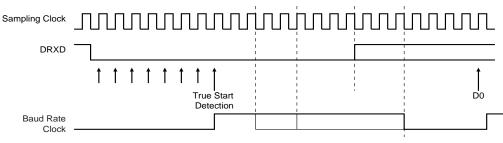

#### 26.4.2.2 Start Detection and Data Sampling

The Debug Unit only supports asynchronous operations, and this affects only its receiver. The Debug Unit receiver detects the start of a received character by sampling the DRXD signal until it detects a valid start bit. A low level (space) on DRXD is interpreted as a valid start bit if it is detected for more than 7 cycles of the sampling clock, which is 16 times the baud rate. Hence, a space that is longer than 7/16 of the bit period is detected as a valid start bit. A space which is 7/16 of a bit period or shorter is ignored and the receiver continues to wait for a valid start bit.

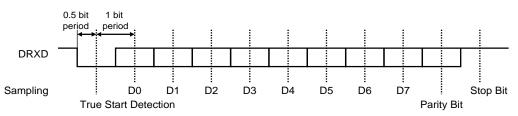

When a valid start bit has been detected, the receiver samples the DRXD at the theoretical midpoint of each bit. It is assumed that each bit lasts 16 cycles of the sampling clock (1-bit period) so the bit sampling point is eight cycles (0.5-bit period) after the start of the bit. The first sampling point is therefore 24 cycles (1.5-bit periods) after the falling edge of the start bit was detected.

Each subsequent bit is sampled 16 cycles (1-bit period) after the previous one.

#### Figure 26-4. Start Bit Detection

#### Figure 26-5. Character Reception

Example: 8-bit, parity enabled 1 stop

#### 26.4.2.3 Receiver Ready

When a complete character is received, it is transferred to the DBGU\_RHR and the RXRDY status bit in DBGU\_SR (Status Register) is set. The bit RXRDY is automatically cleared when the receive holding register DBGU\_RHR is read.

## 28.6 Functional Description

#### 28.6.1 Modes of Operation

The SPI operates in Master Mode or in Slave Mode.

Operation in Master Mode is programmed by writing at 1 the MSTR bit in the Mode Register. The pins NPCS0 to NPCS3 are all configured as outputs, the SPCK pin is driven, the MISO line is wired on the receiver input and the MOSI line driven as an output by the transmitter.

If the MSTR bit is written at 0, the SPI operates in Slave Mode. The MISO line is driven by the transmitter output, the MOSI line is wired on the receiver input, the SPCK pin is driven by the transmitter to synchronize the receiver. The NPCS0 pin becomes an input, and is used as a Slave Select signal (NSS). The pins NPCS1 to NPCS3 are not driven and can be used for other purposes.

The data transfers are identically programmable for both modes of operations. The baud rate generator is activated only in Master Mode.

#### 28.6.2 Data Transfer

Four combinations of polarity and phase are available for data transfers. The clock polarity is programmed with the CPOL bit in the Chip Select Register. The clock phase is programmed with the NCPHA bit. These two parameters determine the edges of the clock signal on which data is driven and sampled. Each of the two parameters has two possible states, resulting in four possible combinations that are incompatible with one another. Thus, a master/slave pair must use the same parameter pair values to communicate. If multiple slaves are used and fixed in different configurations, the master must reconfigure itself each time it needs to communicate with a different slave.

Table 28-2 shows the four modes and corresponding parameter settings.

| SPI Mode | CPOL | NCPHA |

|----------|------|-------|

| 0        | 0    | 1     |

| 1        | 0    | 0     |

| 2        | 1    | 1     |

| 3        | 1    | 0     |

#### Table 28-2. SPI Bus Protocol Mode

Figure 28-3 and Figure 28-4 show examples of data transfers.

## 29.6.3 TWI Internal Address Register

| Register Name: | TWI_IAE | DR  |    |    |    |    |    |

|----------------|---------|-----|----|----|----|----|----|

| Access Type:   | Read-wr | ite |    |    |    |    |    |

| 31             | 30      | 29  | 28 | 27 | 26 | 25 | 24 |

| -              | -       | -   | -  | -  | -  | _  | -  |

| 23             | 22      | 21  | 20 | 19 | 18 | 17 | 16 |

|                |         |     | IA | DR |    |    |    |

| 15             | 14      | 13  | 12 | 11 | 10 | 9  | 8  |

|                | IADR    |     |    |    |    |    |    |

| 7              | 6       | 5   | 4  | 3  | 2  | 1  | 0  |

|                |         |     | IA | DR |    |    |    |

#### • IADR: Internal Address

0, 1, 2 or 3 bytes depending on IADRSZ.

- Low significant byte address in 10-bit mode addresses.

| Table 30-2. | Baud Rate Example (OVER = 0) (Continued) |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

| Source Clock | Expected Baud<br>Rate | Calculation Result | CD | Actual Baud Rate | Error |

|--------------|-----------------------|--------------------|----|------------------|-------|

| 18 432 000   | 38 400                | 30.00              | 30 | 38 400.00        | 0.00% |

| 24 000 000   | 38 400                | 39.06              | 39 | 38 461.54        | 0.16% |

| 24 576 000   | 38 400                | 40.00              | 40 | 38 400.00        | 0.00% |

| 25 000 000   | 38 400                | 40.69              | 40 | 38 109.76        | 0.76% |

| 32 000 000   | 38 400                | 52.08              | 52 | 38 461.54        | 0.16% |

| 32 768 000   | 38 400                | 53.33              | 53 | 38 641.51        | 0.63% |

| 33 000 000   | 38 400                | 53.71              | 54 | 38 194.44        | 0.54% |

| 40 000 000   | 38 400                | 65.10              | 65 | 38 461.54        | 0.16% |

| 50 000 000   | 38 400                | 81.38              | 81 | 38 580.25        | 0.47% |

The baud rate is calculated with the following formula:

$BaudRate = MCK/CD \times 16$

The baud rate error is calculated with the following formula. It is not recommended to work with an error higher than 5%.

$Error = 1 - \left(\frac{ExpectedBaudRate}{ActualBaudRate}\right)$

#### 30.6.1.3 Fractional Baud Rate in Asynchronous Mode

The Baud Rate generator previously defined is subject to the following limitation: the output frequency changes by only integer multiples of the reference frequency. An approach to this problem is to integrate a fractional N clock generator that has a high resolution. The generator architecture is modified to obtain Baud Rate changes by a fraction of the reference source clock. This fractional part is programmed with the FP field in the Baud Rate Generator Register (US\_BRGR). If FP is not 0, the fractional part is activated. The resolution is one eighth of the clock divider. This feature is only available when using USART normal mode. The fractional Baud Rate is calculated using the following formula:

$Baudrate = \frac{SelectedClock}{\left(8(2 - Over)\left(CD + \frac{FP}{8}\right)\right)}$

The modified architecture is presented below:

## 30.7.8 USART Transmit Holding Register

| Name:        | US_THR   | ł  |    |     |    |    |       |

|--------------|----------|----|----|-----|----|----|-------|

| Access Type: | Write-on | ly |    |     |    |    |       |

| 31           | 30       | 29 | 28 | 27  | 26 | 25 | 24    |

| -            | _        | _  | -  | -   | -  | -  | -     |

| 23           | 22       | 21 | 20 | 19  | 18 | 17 | 16    |

| -            | _        | _  | -  | -   | -  | _  | -     |

| 15           | 14       | 13 | 12 | 11  | 10 | 9  | 8     |

| TXSYNH       | -        | -  | -  | -   | -  | —  | TXCHR |

| 7            | 6        | 5  | 4  | 3   | 2  | 1  | 0     |

|              |          |    | TX | CHR |    |    |       |

#### • TXCHR: Character to be Transmitted

Next character to be transmitted after the current character if TXRDY is not set.

#### • TXSYNH: Sync Field to be transmitted

0: The next character sent is encoded as a data. Start Frame Delimiter is DATA SYNC.

1: The next character sent is encoded as a command. Start Frame Delimiter is COMMAND SYNC.

## 30.7.11 USART Transmitter Timeguard Register

| Name:        | US_TTO  | US_TTGR |    |    |    |    |    |  |  |

|--------------|---------|---------|----|----|----|----|----|--|--|

| Access Type: | Read-wi | rite    |    |    |    |    |    |  |  |

| 31           | 30      | 29      | 28 | 27 | 26 | 25 | 24 |  |  |

| -            | _       | -       | -  | -  | -  | _  | -  |  |  |

| 23           | 22      | 21      | 20 | 19 | 18 | 17 | 16 |  |  |

| -            | _       | -       | -  | -  | _  | -  | -  |  |  |

| 15           | 14      | 13      | 12 | 11 | 10 | 9  | 8  |  |  |

| -            | -       | -       | -  | -  | _  | _  | -  |  |  |

| 7            | 6       | 5       | 4  | 3  | 2  | 1  | 0  |  |  |

|              |         |         | Т  | G  |    |    |    |  |  |

#### • TG: Timeguard Value

0: The Transmitter Timeguard is disabled.

1 - 255: The Transmitter timeguard is enabled and the timeguard delay is TG x Bit Period.

#### 32.6.5 TC Channel Mode Register: Waveform Mode

Register Name:TC\_CMRx [x=0..2] (WAVE = 1)Access Type:Read-write

| 31     | 30      | 29                | 28           | 27     | 26    | 25      | 24  |

|--------|---------|-------------------|--------------|--------|-------|---------|-----|

| BSV    | /TRG    | B                 | EVT          | BC     | PC    | BCPB    |     |

| 23     | 22      | 21                | 20           | 19     | 18    | 17      | 16  |

| ASV    | WTRG A  |                   | AEEVT ACPC A |        | AEEVT |         | CPA |

| 15     | 14      | 13                | 12           | 11     | 10    | 9       | 8   |

| WAVE   | WAW     | WAVSEL ENETRG     |              | B EEVT |       | EEVTEDG |     |

| 7      | 6       | 5                 | 4            | 3      | 2     | 1       | 0   |

| CPCDIS | CPCSTOP | BURST CLKI TCCLKS |              |        |       |         |     |

#### • TCCLKS: Clock Selection

|   | TCCLKS |   |              |  |

|---|--------|---|--------------|--|

| 0 | 0      | 0 | TIMER_CLOCK1 |  |

| 0 | 0      | 1 | TIMER_CLOCK2 |  |

| 0 | 1      | 0 | TIMER_CLOCK3 |  |

| 0 | 1      | 1 | TIMER_CLOCK4 |  |

| 1 | 0      | 0 | TIMER_CLOCK5 |  |

| 1 | 0      | 1 | XC0          |  |

| 1 | 1      | 0 | XC1          |  |

| 1 | 1      | 1 | XC2          |  |

#### • CLKI: Clock Invert

0 = Counter is incremented on rising edge of the clock.

1 = Counter is incremented on falling edge of the clock.

#### • BURST: Burst Signal Selection

| BURST |   |                                               |

|-------|---|-----------------------------------------------|

| 0     | 0 | The clock is not gated by an external signal. |

| 0     | 1 | XC0 is ANDed with the selected clock.         |

| 1     | 0 | XC1 is ANDed with the selected clock.         |

| 1     | 1 | XC2 is ANDed with the selected clock.         |

#### • CPCSTOP: Counter Clock Stopped with RC Compare

0 = Counter clock is not stopped when counter reaches RC.

1 = Counter clock is stopped when counter reaches RC.

#### CPCDIS: Counter Clock Disable with RC Compare

0 = Counter clock is not disabled when counter reaches RC.

1 = Counter clock is disabled when counter reaches RC.

Atmel

#### 32.6.11 TC Interrupt Enable Register

| Register Name<br>Access Type: |       | TC_IERx [x=02]<br>Write-only |      |      |      |  |  |  |

|-------------------------------|-------|------------------------------|------|------|------|--|--|--|

| 31                            | 30    | 29                           | 28   | 27   | 26   |  |  |  |

| -                             | -     | -                            | -    | -    | -    |  |  |  |

| 23                            | 22    | 21                           | 20   | 19   | 18   |  |  |  |

| -                             | _     | _                            | _    | _    | _    |  |  |  |

| 15                            | 14    | 13                           | 12   | 11   | 10   |  |  |  |

| -                             | -     | -                            | -    | -    | -    |  |  |  |

| 7                             | 6     | 5                            | 4    | 3    | 2    |  |  |  |

| ETRGS                         | LDRBS | LDRAS                        | CPCS | CPBS | CPAS |  |  |  |

#### COVFS: Counter Overflow

0 = No effect.

1 = Enables the Counter Overflow Interrupt.

#### LOVRS: Load Overrun

0 = No effect.

1 = Enables the Load Overrun Interrupt.

#### • CPAS: RA Compare

0 = No effect.

1 = Enables the RA Compare Interrupt.

#### CPBS: RB Compare

0 = No effect.

1 = Enables the RB Compare Interrupt.

#### CPCS: RC Compare

0 = No effect.

1 = Enables the RC Compare Interrupt.

#### • LDRAS: RA Loading

0 = No effect.

1 = Enables the RA Load Interrupt.

#### LDRBS: RB Loading

0 = No effect.

1 = Enables the RB Load Interrupt.

#### • ETRGS: External Trigger

0 = No effect.

1 = Enables the External Trigger Interrupt.

# Atmel

25

\_

17

—

9

\_

1 LOVRS 24

\_

16

-

8

\_ 0

COVFS

#### 35.6.7 ADC Last Converted Data Register

| Register Name: | ADC_LC  | ADC_LCDR |    |     |    |    |     |  |  |

|----------------|---------|----------|----|-----|----|----|-----|--|--|

| Access Type:   | Read-on | ly       |    |     |    |    |     |  |  |

| 31             | 30      | 29       | 28 | 27  | 26 | 25 | 24  |  |  |

| -              | _       | _        | -  | -   | -  | -  | -   |  |  |

| 23             | 22      | 21       | 20 | 19  | 18 | 17 | 16  |  |  |

| -              | _       | _        | -  | -   | -  | -  | -   |  |  |

| 15             | 14      | 13       | 12 | 11  | 10 | 9  | 8   |  |  |

| -              | -       |          |    |     |    | LD | ATA |  |  |

| 7              | 6       | 5        | 4  | 3   | 2  | 1  | 0   |  |  |

|                |         |          | LD | ATA |    |    |     |  |  |

#### • LDATA: Last Data Converted

The analog-to-digital conversion data is placed into this register at the end of a conversion and remains until a new conversion is completed.

#### 35.6.8 ADC Interrupt Enable Register

| Register Name:<br>Access Type: | ADC_IEI<br>Write-on |       |       |        |       |       |       |

|--------------------------------|---------------------|-------|-------|--------|-------|-------|-------|

| 31                             | 30                  | 29    | 28    | 27     | 26    | 25    | 24    |

| -                              | _                   | —     | -     | -      | _     | —     | -     |

| 23                             | 22                  | 21    | 20    | 19     | 18    | 17    | 16    |

| -                              | _                   | -     | -     | RXBUFF | ENDRX | GOVRE | DRDY  |

| 15                             | 14                  | 13    | 12    | 11     | 10    | 9     | 8     |

| OVRE7                          | OVRE6               | OVRE5 | OVRE4 | OVRE3  | OVRE2 | OVRE1 | OVRE0 |

| 7                              | 6                   | 5     | 4     | 3      | 2     | 1     | 0     |

| EOC7                           | EOC6                | EOC5  | EOC4  | EOC3   | EOC2  | EOC1  | EOC0  |

- EOCx: End of Conversion Interrupt Enable x

- OVREx: Overrun Error Interrupt Enable x

- DRDY: Data Ready Interrupt Enable

- GOVRE: General Overrun Error Interrupt Enable

- ENDRX: End of Receive Buffer Interrupt Enable

- RXBUFF: Receive Buffer Full Interrupt Enable

0 = No effect.

1 = Enables the corresponding interrupt.

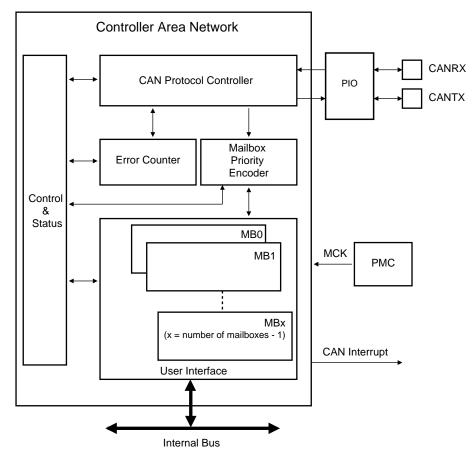

## 36.2 Block Diagram

#### Figure 36-1. CAN Block Diagram

Atmel

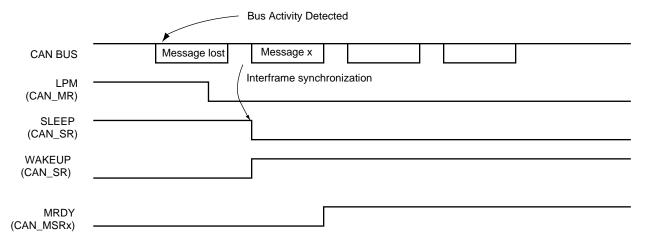

#### Figure 36-9. Disabling Low-power Mode

## 36.7 Functional Description

#### 36.7.1 CAN Controller Initialization

After power-up reset, the CAN controller is disabled. The CAN controller clock must be activated by the Power Management Controller (PMC) and the CAN controller interrupt line must be enabled by the interrupt controller (AIC).

The CAN controller must be initialized with the CAN network parameters. The CAN\_BR register defines the sampling point in the bit time period. CAN\_BR must be set before the CAN controller is enabled by setting the CANEN field in the CAN\_MR register.

The CAN controller is enabled by setting the CANEN flag in the CAN\_MR register. At this stage, the internal CAN controller state machine is reset, error counters are reset to 0, error flags are reset to 0.

Once the CAN controller is enabled, bus synchronization is done automatically by scanning eleven recessive bits. The WAKEUP bit in the CAN\_SR register is automatically set to 1 when the CAN controller is synchronized (WAKEUP and SLEEP are stuck at 0 after a reset).

The CAN controller can start listening to the network in Autobaud Mode. In this case, the error counters are locked and a mailbox may be configured in Receive Mode. By scanning error flags, the CAN\_BR register values synchronized with the network. Once no error has been detected, the application disables the Autobaud Mode, clearing the ABM field in the CAN\_MR register.

#### 36.8.18 CAN Message Data High Register

| Name:<br>Access Type: | CAN_MI<br>Read-wi |    |    |    |    |    |    |

|-----------------------|-------------------|----|----|----|----|----|----|

| 31                    | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

|                       |                   |    | M  | DH |    |    |    |

| 23                    | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

|                       |                   |    | M  | DH |    |    |    |

| 15                    | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

|                       |                   |    | M  | DH |    |    |    |

| 7                     | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                       |                   |    | M  | DH |    |    |    |

#### • MDH: Message Data High Value

When MRDY field is set in the CAN\_MSRx register, the upper 32 bits of a received message are read or written by the software application. Otherwise, the MDH value is locked by the CAN controller to send/receive a new message.

In Receive with overwrite, the CAN controller may modify MDH value while the software application reads MDH and MDL registers. To check that MDH and MDL do not belong to different messages, the application has to check the MMI field in the CAN\_MSRx register. In this mode, the software application must re-read CAN\_MDH and CAN\_MDL, while the MMI bit in the CAN\_MSRx register is set.

Bytes are received/sent on the bus in the following order:

- 1. CAN\_MDL[7:0]

- 2. CAN\_MDL[15:8]

- 3. CAN\_MDL[23:16]

- 4. CAN\_MDL[31:24]

- 5. CAN\_MDH[7:0]

- 6. CAN\_MDH[15:8]

- 7. CAN\_MDH[23:16]

- 8. CAN\_MDH[31:24]

Table 37-2. Transmit Buffe

Transmit Buffer Descriptor Entry (Continued)

| Bit   | Function                                                                                                                                                                        |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       | Used. Needs to be zero for the EMAC to read data from the transmit buffer. The EMAC sets this to one for the first buffer of a frame once it has been successfully transmitted. |  |  |  |  |

| 31    | Software has to clear this bit before the buffer can be used again.                                                                                                             |  |  |  |  |

|       | Note: This bit is only set for the first buffer in a frame unlike receive where all buffers have the Used bit set once used.                                                    |  |  |  |  |

| 30    | Wrap. Marks last descriptor in transmit buffer descriptor list.                                                                                                                 |  |  |  |  |

| 29    | Retry limit exceeded, transmit error detected                                                                                                                                   |  |  |  |  |

| 28    | Transmit underrun, occurs either when hresp is not OK (bus error) or the transmit data could not be fetched in time or when buffers are exhausted in mid frame.                 |  |  |  |  |

| 27    | Buffers exhausted in mid frame                                                                                                                                                  |  |  |  |  |

| 26:17 | Reserved                                                                                                                                                                        |  |  |  |  |

| 16    | No CRC. When set, no CRC is appended to the current frame. This bit only needs to be set for the last buffer of a frame.                                                        |  |  |  |  |

| 15    | Last buffer. When set, this bit indicates the last buffer in the current frame has been reached.                                                                                |  |  |  |  |

| 14:11 | Reserved                                                                                                                                                                        |  |  |  |  |

| 10:0  | Length of buffer                                                                                                                                                                |  |  |  |  |

#### 37.3.2 Transmit Block

This block transmits frames in accordance with the Ethernet IEEE 802.3 CSMA/CD protocol. Frame assembly starts by adding preamble and the start frame delimiter. Data is taken from the transmit FIFO a word at a time. Data is transmitted least significant nibble first. If necessary, padding is added to increase the frame length to 60 bytes. CRC is calculated as a 32-bit polynomial. This is inverted and appended to the end of the frame, taking the frame length to a minimum of 64 bytes. If the No CRC bit is set in the second word of the last buffer descriptor of a transmit frame, neither pad nor CRC are appended.

In full-duplex mode, frames are transmitted immediately. Back-to-back frames are transmitted at least 96 bit times apart to guarantee the interframe gap.

In half-duplex mode, the transmitter checks carrier sense. If asserted, it waits for it to de-assert and then starts transmission after the interframe gap of 96 bit times. If the collision signal is asserted during transmission, the transmitter transmits a jam sequence of 32 bits taken from the data register and then retry transmission after the back off time has elapsed.

The back-off time is based on an XOR of the 10 least significant bits of the data coming from the transmit FIFO and a 10bit pseudo random number generator. The number of bits used depends on the number of collisions seen. After the first collision, 1 bit is used, after the second 2, and so on up to 10. Above 10, all 10 bits are used. An error is indicated and no further attempts are made if 16 attempts cause collisions.

If transmit DMA underruns, bad CRC is automatically appended using the same mechanism as jam insertion and the tx\_er signal is asserted. For a properly configured system, this should never happen.

If the back pressure bit is set in the network control register in half duplex mode, the transmit block transmits 64 bits of data, which can consist of 16 nibbles of 1011 or in bit-rate mode 64 1s, whenever it sees an incoming frame to force a collision. This provides a way of implementing flow control in half-duplex mode.

#### 37.5.8 Interrupt Status Register

| Register Name:<br>Access Type: |       | EMAC_ISR<br>Read-write |      |       |       |       |     |  |  |  |  |

|--------------------------------|-------|------------------------|------|-------|-------|-------|-----|--|--|--|--|

| 31                             | 30    | 29                     | 28   | 27    | 26    | 25    | 24  |  |  |  |  |

| _                              | -     | _                      | _    | _     | _     | _     | —   |  |  |  |  |

| 23                             | 22    | 21                     | 20   | 19    | 18    | 17    | 16  |  |  |  |  |

| -                              | —     | -                      | -    | -     | -     | -     | -   |  |  |  |  |

| 15                             | 14    | 13                     | 12   | 11    | 10    | 9     | 8   |  |  |  |  |

| —                              | —     | PTZ                    | PFR  | HRESP | ROVR  |       | -   |  |  |  |  |

| 7                              | 6     | 5                      | 4    | 3     | 2     | 1     | 0   |  |  |  |  |

| TCOMP                          | TXERR | RLE                    | TUND | TXUBR | RXUBR | RCOMP | MFD |  |  |  |  |

#### • MFD: Management Frame Done

The PHY maintenance register has completed its operation. Cleared on read.

#### • RCOMP: Receive Complete

A frame has been stored in memory. Cleared on read.

#### • RXUBR: Receive Used Bit Read

Set when a receive buffer descriptor is read with its used bit set. Cleared on read.

#### • TXUBR: Transmit Used Bit Read

Set when a transmit buffer descriptor is read with its used bit set. Cleared on read.

#### • TUND: Ethernet Transmit Buffer Underrun

The transmit DMA did not fetch frame data in time for it to be transmitted or hresp returned not OK. Also set if a used bit is read mid-frame or when a new transmit queue pointer is written. Cleared on read.

#### • RLE: Retry Limit Exceeded

Cleared on read.

#### • TXERR: Transmit Error

Transmit buffers exhausted in mid-frame - transmit error. Cleared on read.

#### • TCOMP: Transmit Complete

Set when a frame has been transmitted. Cleared on read.

#### ROVR: Receive Overrun

Set when the receive overrun status bit gets set. Cleared on read.

#### • HRESP: Hresp not OK

Set when the DMA block sees  ${\tt a}\ {\tt bus}\ {\tt error}.$  Cleared on read.

#### PFR: Pause Frame Received

Indicates a valid pause has been received. Cleared on a read.

#### • PTZ: Pause Time Zero

Set when the pause time register, 0x38 decrements to zero. Cleared on a read.

Atmel

## 37.5.24 Type ID Checking Register

| Register Name:<br>Access Type: |    | EMAC_TID<br>Read-write |    |    |    |    |    |  |  |  |  |

|--------------------------------|----|------------------------|----|----|----|----|----|--|--|--|--|

| 31                             | 30 | 29                     | 28 | 27 | 26 | 25 | 24 |  |  |  |  |

| -                              | -  | _                      | _  | _  | _  | _  | —  |  |  |  |  |

| 23                             | 22 | 21                     | 20 | 19 | 18 | 17 | 16 |  |  |  |  |

| -                              | _  | _                      | _  | _  | _  | _  | -  |  |  |  |  |

| 15                             | 14 | 13                     | 12 | 11 | 10 | 9  | 8  |  |  |  |  |

| TID                            |    |                        |    |    |    |    |    |  |  |  |  |

| 7                              | 6  | 5                      | 4  | 3  | 2  | 1  | 0  |  |  |  |  |

| TID                            |    |                        |    |    |    |    |    |  |  |  |  |

## • TID: Type ID Checking

For use in comparisons with received frames TypeID/Length field.

#### 41.4.10.5 TWI: Software Reset

when a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

Problem Fix/Workaround

None.

#### 41.4.11 Universal Synchronous Asynchronous Receiver Transmitter (USART)

#### 41.4.11.1 USART: CTS in Hardware Handshaking

When Hardware Handshaking is used and if CTS goes low near the end of the start bit, a character can be lost.

CTS must not go high during a time slot occurring between 2 Master Clock periods before and 16 Master Clock periods after the rising edge of the start bit.

Problem Fix/Workaround

None.

#### 41.4.11.2 USART: Hardware Handshaking – Two Characters Sent

If CTS switches from 0 to 1 during the TX of a character and if the holding register (US\_THR) is not empty, the content of US\_THR will also be transmitted.

Problem Fix/Workaround

Don't use the PDC in transmit mode and do not fill US\_THR before TXEMPTY is set at 1.

#### 41.4.11.3 USART: RXBRK Flag Error in Asynchronous Mode

In receiver mode, when there are two consecutive characters (without time guard in between), RXBRK is not taken into account. As a result, the RXBRK flag is not enabled correctly and the frame error flag is set Problem Fix/Workaround

Constraints on the transmitter device connected to the SAM7X USART receiver side:

The transmitter may use the timeguard feature or send two STOP conditions. Only one STOP condition is taken into account by the receiver state machine. After this STOP condition, as there is no valid data, the receiver state machine will go in idle mode and enable the RXBRK flag.

#### 41.4.11.4 USART: DCD is Active High instead of Low.

The DCD signal is active at High level in the USART Modem Mode .

DCD should be active at Low level.

Problem Fix/Workaround

Add an inverter.

Atmel