Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                               |

|----------------------------|---------------------------------------------------------------|

| Product Status             | Obsolete                                                      |

| Core Processor             | ARM7®                                                         |

| Core Size                  | 16/32-Bit                                                     |

| Speed                      | 55MHz                                                         |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 62                                                            |

| Program Memory Size        | 128KB (128K x 8)                                              |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 32K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                 |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 100-TFBGA                                                     |

| Supplier Device Package    | 100-TFBGA (9x9)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at91sam7x128b-cu   |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16.4.2 Watchdog Timer Mode Register

| Register Name: | WDT_M   | 1R        |          |    |    |    |    |

|----------------|---------|-----------|----------|----|----|----|----|

| Access Type:   | Read-w  | rite Once |          |    |    |    |    |

| 31             | 30      | 29        | 28       | 27 | 26 | 25 | 24 |

| -              | —       | WDIDLEHLT | WDDBGHLT |    | W  | DD |    |

| 23             | 22      | 21        | 20       | 19 | 18 | 17 | 16 |

|                | WDD     |           |          |    |    |    |    |

| 15             | 14      | 13        | 12       | 11 | 10 | 9  | 8  |

| WDDIS          | WDRPROC | WDRSTEN   | WDFIEN   |    | WI | VC |    |

| 7              | 6       | 5         | 4        | 3  | 2  | 1  | 0  |

|                | WDV     |           |          |    |    |    |    |

#### • WDV: Watchdog Counter Value

Defines the value loaded in the 12-bit Watchdog Counter.

#### • WDFIEN: Watchdog Fault Interrupt Enable

- 0: A Watchdog fault (underflow or error) has no effect on interrupt.

- 1: A Watchdog fault (underflow or error) asserts interrupt.

#### • WDRSTEN: Watchdog Reset Enable

- 0: A Watchdog fault (underflow or error) has no effect on the resets.

- 1: A Watchdog fault (underflow or error) triggers a Watchdog reset.

#### WDRPROC: Watchdog Reset Processor

- 0: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates all resets.

- 1: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates the processor reset.

#### • WDD: Watchdog Delta Value

Defines the permitted range for reloading the Watchdog Timer.

If the Watchdog Timer value is less than or equal to WDD, writing WDT\_CR with WDRSTT = 1 restarts the timer. If the Watchdog Timer value is greater than WDD, writing WDT\_CR with WDRSTT = 1 causes a Watchdog error.

#### • WDDBGHLT: Watchdog Debug Halt

0: The Watchdog runs when the processor is in debug state.

1: The Watchdog stops when the processor is in debug state.

#### • WDIDLEHLT: Watchdog Idle Halt

- 0: The Watchdog runs when the system is in idle mode.

- 1: The Watchdog stops when the system is in idle state.

#### • WDDIS: Watchdog Disable

0: Enables the Watchdog Timer.

- 1: Disables the Watchdog Timer.

- Note: The WDD and WDV values must not be modified within three slow clock periods after a restart of the watchdog performed by a write access in WDT\_CR; otherwise, the watchdog may trigger an end of period earlier than expected.

In the same way, the **Clear Lock** command **(CLB)** is used to clear lock bits. All the lock bits can also be cleared by the EA command.

| Read/Write | DR Data    |  |  |  |

|------------|------------|--|--|--|

| Write      | SLB or CLB |  |  |  |

| Write      | Bit Mask   |  |  |  |

#### Table 20-23. Set and Clear Lock Bit Command

Lock bits can be read using **Get Lock Bit** command **(GLB)**. When a bit set in the Bit Mask is returned, then the corresponding lock bit is active.

| Table 20-24. | Get Lock Bit Command |

|--------------|----------------------|

|--------------|----------------------|

| Read/Write | DR Data  |

|------------|----------|

| Write      | GLB      |

| Read       | Bit Mask |

#### 20.3.4.5 Flash General-purpose NVM Commands

General-purpose NVM bits (GP NVM) can be set with the **Set GPNVM** command **(SGPB)**. Using this command, several GP NVM bits can be activated at the same time. Bit 0 of Bit Mask corresponds to the first GPNVM bit and so on.

In the same way, the **Clear GPNVM** command **(CGPB)** is used to clear GP NVM bits. All the general-purpose NVM bits are also cleared by the EA command.

#### Table 20-25. Set and Clear General-purpose NVM Bit Command

| Read/Write | DR Data      |

|------------|--------------|

| Write      | SGPB or CGPB |

| Write      | Bit Mask     |

GP NVM bits can be read using **Get GPNVM Bit** command **(GGPB)**. When a bit set in the Bit Mask is returned, then the corresponding GPNVM bit is set.

#### Table 20-26. Get General-purpose NVM Bit Command

| Read/Write | DR Data  |

|------------|----------|

| Write      | GGPB     |

| Read       | Bit Mask |

#### 20.3.4.6 Flash Security Bit Command

Security bits can be set using **Set Security Bit** command (SSE). Once the security bit is active, the Fast Flash programming is disabled. No other command can be run. Only an event on the Erase pin can erase the security bit once the contents of the Flash have been erased.

The AT91SAM7X512 security bit is controlled by the EFC0. To use the **Set Security Bit** command, the EFC0 must be selected using the **Select EFC** command.

#### Table 20-27. Set Security Bit Command

| Read/Write | DR Data |

|------------|---------|

| Write      | SSE     |

Once the security bit is set, it is not possible to access FFPI. The only way to erase the security bit is to erase the Flash.

In order to erase the Flash, the user must perform the following:

- Power-off the chip

- Power-on the chip with TST = 0

- NVPTYP and NVPSIZ identifies the type of embedded non-volatile memory and its size

- ARCH identifies the set of embedded peripheral

- SRAMSIZ indicates the size of the embedded SRAM

- EPROC indicates the embedded ARM processor

- VERSION gives the revision of the silicon

The second register is device-dependent and reads 0 if the bit EXT is 0.

# 26.4.8 ICE Access Prevention

The Debug Unit allows blockage of access to the system through the ARM processor's ICE interface. This feature is implemented via the register Force NTRST (DBGU\_FNR), that allows assertion of the NTRST signal of the ICE Interface. Writing the bit FNTRST (Force NTRST) to 1 in this register prevents any activity on the TAP controller.

On standard devices, the FNTRST bit resets to 0 and thus does not prevent ICE access.

This feature is especially useful on custom ROM devices for customers who do not want their on-chip code to be visible.

# 27.6.11 PIO Controller Clear Output Data Register

| Name:        | PIO_CODR  |     |     |     |     |     |     |

|--------------|-----------|-----|-----|-----|-----|-----|-----|

| Access Type: | Write-onl | У   |     |     |     |     |     |

| 31           | 30        | 29  | 28  | 27  | 26  | 25  | 24  |

| P31          | P30       | P29 | P28 | P27 | P26 | P25 | P24 |

| 23           | 22        | 21  | 20  | 19  | 18  | 17  | 16  |

| P23          | P22       | P21 | P20 | P19 | P18 | P17 | P16 |

| 15           | 14        | 13  | 12  | 11  | 10  | 9   | 8   |

| P15          | P14       | P13 | P12 | P11 | P10 | P9  | P8  |

| 7            | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

| P7           | P6        | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0-P31: Set Output Data

0 = No effect.

1 = Clears the data to be driven on the I/O line.

# 27.6.12 PIO Controller Output Data Status Register

| Name: | PIO ODSR |

|-------|----------|

| Nume. | 110_0001 |

Access Type: Read-only or Read-write

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0-P31: Output Data Status

0 = The data to be driven on the I/O line is 0.

1 = The data to be driven on the I/O line is 1.

# 27.6.19 PIO Multi-driver Disable Register

| Name:        | PIO_MDDR   |

|--------------|------------|

| Access Type: | Write-only |

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

# • P0-P31: Multi Drive Disable.

0 = No effect.

1 = Disables Multi Drive on the I/O line.

#### 27.6.20 PIO Multi-driver Status Register

| Name: | PIO   | MDSR |

|-------|-------|------|

|       | · · · |      |

| Access Type: | Read-only |

|--------------|-----------|

|--------------|-----------|

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

#### • P0-P31: Multi Drive Status.

0 = The Multi Drive is disabled on the I/O line. The pin is driven at high and low level.

1 = The Multi Drive is enabled on the I/O line. The pin is driven at low level only.

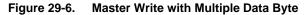

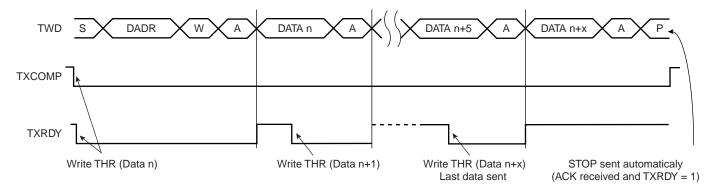

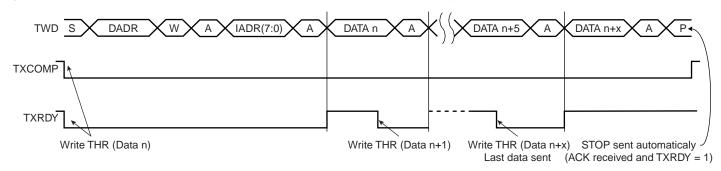

#### Figure 29-7. Master Write with One Byte Internal Address and Multiple Data Bytes

# 29.6.2 TWI Master Mode Register

| Register Name: | TWI_MN  | /IR        |       |      |    |     |     |  |  |

|----------------|---------|------------|-------|------|----|-----|-----|--|--|

| Address Type:  | Read-wr | Read-write |       |      |    |     |     |  |  |

| 31             | 30      | 29         | 28    | 27   | 26 | 25  | 24  |  |  |

| -              | -       | -          | -     | -    | -  | -   | -   |  |  |

| 23             | 22      | 21         | 20    | 19   | 18 | 17  | 16  |  |  |

| _              |         |            |       | DADR |    |     |     |  |  |

| 15             | 14      | 13         | 12    | 11   | 10 | 9   | 8   |  |  |

| —              | _       | —          | MREAD | -    | _  | IAD | RSZ |  |  |

| 7              | 6       | 5          | 4     | 3    | 2  | 1   | 0   |  |  |

| -              | _       | _          | -     | -    | _  | —   | _   |  |  |

# • IADRSZ: Internal Device Address Size

#### Table 29-4.

| IADRSZ[9:8] |   |                                                    |  |

|-------------|---|----------------------------------------------------|--|

| 0           | 0 | No internal device address (Byte command protocol) |  |

| 0           | 1 | One-byte internal device address                   |  |

| 1           | 0 | Two-byte internal device address                   |  |

| 1           | 1 | Three-byte internal device address                 |  |

#### • MREAD: Master Read Direction

0 = Master write direction.

1 = Master read direction.

# • DADR: Device Address

The device address is used to access slave devices in read or write mode.

# 30.6 Functional Description

The USART is capable of managing several types of serial synchronous or asynchronous communications.

It supports the following communication modes:

- 5- to 9-bit full-duplex asynchronous serial communication

- MSB- or LSB-first

- 1, 1.5 or 2 stop bits

- Parity even, odd, marked, space or none

- By 8 or by 16 over-sampling receiver frequency

- Optional hardware handshaking

- Optional modem signals management

- Optional break management

- Optional multidrop serial communication

- High-speed 5- to 9-bit full-duplex synchronous serial communication

- MSB- or LSB-first

- 1 or 2 stop bits

- Parity even, odd, marked, space or none

- By 8 or by 16 over-sampling frequency

- Optional hardware handshaking

- Optional modem signals management

- Optional break management

- Optional multidrop serial communication

- RS485 with driver control signal

- ISO7816, T0 or T1 protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- InfraRed IrDA Modulation and Demodulation

- Test modes

- Remote loopback, local loopback, automatic echo

# 30.6.1 Baud Rate Generator

The Baud Rate Generator provides the bit period clock named the Baud Rate Clock to both the receiver and the transmitter.

The Baud Rate Generator clock source can be selected by setting the USCLKS field in the Mode Register (US\_MR) between:

- the Master Clock MCK

- a division of the Master Clock, the divider being product dependent, but generally set to 8

- the external clock, available on the SCK pin

The Baud Rate Generator is based upon a 16-bit divider, which is programmed with the CD field of the Baud Rate Generator Register (US\_BRGR). If CD is programmed at 0, the Baud Rate Generator does not generate any clock. If CD is programmed at 1, the divider is bypassed and becomes inactive.

If the external SCK clock is selected, the duration of the low and high levels of the signal provided on the SCK pin must be longer than a Master Clock (MCK) period. The frequency of the signal provided on SCK must be at least 4.5 times lower than MCK.

#### 30.6.5.2 IrDA Baud Rate

Table 30-10 gives some examples of CD values, baud rate error and pulse duration. Note that the requirement on the maximum acceptable error of ±1.87% must be met.

| Peripheral Clock | Baud Rate | CD  | Baud Rate Error | Pulse Time |

|------------------|-----------|-----|-----------------|------------|

| 3 686 400        | 115 200   | 2   | 0.00%           | 1.63       |

| 20 000 000       | 115 200   | 11  | 1.38%           | 1.63       |

| 32 768 000       | 115 200   | 18  | 1.25%           | 1.63       |

| 40 000 000       | 115 200   | 22  | 1.38%           | 1.63       |

| 3 686 400        | 57 600    | 4   | 0.00%           | 3.26       |

| 20 000 000       | 57 600    | 22  | 1.38%           | 3.26       |

| 32 768 000       | 57 600    | 36  | 1.25%           | 3.26       |

| 40 000 000       | 57 600    | 43  | 0.93%           | 3.26       |

| 3 686 400        | 38 400    | 6   | 0.00%           | 4.88       |

| 20 000 000       | 38 400    | 33  | 1.38%           | 4.88       |

| 32 768 000       | 38 400    | 53  | 0.63%           | 4.88       |

| 40 000 000       | 38 400    | 65  | 0.16%           | 4.88       |

| 3 686 400        | 19 200    | 12  | 0.00%           | 9.77       |

| 20 000 000       | 19 200    | 65  | 0.16%           | 9.77       |

| 32 768 000       | 19 200    | 107 | 0.31%           | 9.77       |

| 40 000 000       | 19 200    | 130 | 0.16%           | 9.77       |

| 3 686 400        | 9 600     | 24  | 0.00%           | 19.53      |

| 20 000 000       | 9 600     | 130 | 0.16%           | 19.53      |

| 32 768 000       | 9 600     | 213 | 0.16%           | 19.53      |

| 40 000 000       | 9 600     | 260 | 0.16%           | 19.53      |

| 3 686 400        | 2 400     | 96  | 0.00%           | 78.13      |

| 20 000 000       | 2 400     | 521 | 0.03%           | 78.13      |

| 32 768 000       | 2 400     | 853 | 0.04%           | 78.13      |

Table 30-10. IrDA Baud Rate Error

# 30.7.11 USART Transmitter Timeguard Register

| Name:        | US_TTO  | US_TTGR |    |    |    |    |    |  |

|--------------|---------|---------|----|----|----|----|----|--|

| Access Type: | Read-wi | rite    |    |    |    |    |    |  |

| 31           | 30      | 29      | 28 | 27 | 26 | 25 | 24 |  |

| -            | _       | -       | -  | -  | -  | _  | -  |  |

| 23           | 22      | 21      | 20 | 19 | 18 | 17 | 16 |  |

| -            | _       | -       | -  | -  | _  | -  | -  |  |

| 15           | 14      | 13      | 12 | 11 | 10 | 9  | 8  |  |

| -            | -       | -       | -  | -  | _  | _  | -  |  |

| 7            | 6       | 5       | 4  | 3  | 2  | 1  | 0  |  |

|              |         |         | Т  | G  |    |    |    |  |

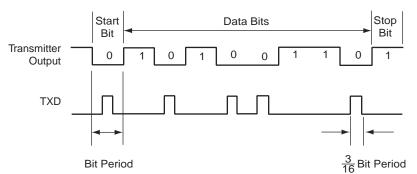

#### • TG: Timeguard Value

0: The Transmitter Timeguard is disabled.

1 - 255: The Transmitter timeguard is enabled and the timeguard delay is TG x Bit Period.

# 31.3 Application Block Diagram

Figure 31-2. Application Block Diagram

| OS or RTOS Driver |       | Power<br>Management |                         | Interrupt<br>Ianagement | Test<br>Management |                |

|-------------------|-------|---------------------|-------------------------|-------------------------|--------------------|----------------|

| SSC               |       |                     |                         |                         |                    |                |

| Serial AUDIO      | Codec |                     | Time Slot<br>Management | Frame<br>Management     |                    | Line Interface |

# 31.4 Pin Name List

Table 31-1.I/O Lines Description

| Pin Name | Pin Description           | Туре         |

|----------|---------------------------|--------------|

| RF       | Receiver Frame Synchro    | Input/Output |

| RK       | Receiver Clock            | Input/Output |

| RD       | Receiver Data             | Input        |

| TF       | Transmitter Frame Synchro | Input/Output |

| ТК       | Transmitter Clock         | Input/Output |

| TD       | Transmitter Data          | Output       |

# 31.5 **Product Dependencies**

#### 31.5.1 I/O Lines

The pins used for interfacing the compliant external devices may be multiplexed with PIO lines.

Before using the SSC receiver, the PIO controller must be configured to dedicate the SSC receiver I/O lines to the SSC peripheral mode.

Before using the SSC transmitter, the PIO controller must be configured to dedicate the SSC transmitter I/O lines to the SSC peripheral mode.

#### 31.5.2 Power Management

The SSC is not continuously clocked. The SSC interface may be clocked through the Power Management Controller (PMC), therefore the programmer must first configure the PMC to enable the SSC clock.

#### 31.5.3 Interrupt

The SSC interface has an interrupt line connected to the Advanced Interrupt Controller (AIC). Handling interrupts requires programming the AIC before configuring the SSC.

All SSC interrupts can be enabled/disabled configuring the SSC Interrupt mask register. Each pending and unmasked SSC interrupt will assert the SSC interrupt line. The SSC interrupt service routine can get the interrupt origin by reading the SSC interrupt status register.

# **31.6 Functional Description**

This chapter contains the functional description of the following: SSC Functional Block, Clock Management, Data format, Start, Transmitter, Receiver and Frame Sync.

#### 31.6.7 Data Format

The data framing format of both the transmitter and the receiver are programmable through the Transmitter Frame Mode Register (SSC\_TFMR) and the Receiver Frame Mode Register (SSC\_RFMR). In either case, the user can independently select:

- the event that starts the data transfer (START)

- the delay in number of bit periods between the start event and the first data bit (STTDLY)

- the length of the data (DATLEN)

- the number of data to be transferred for each start event (DATNB).

- the length of synchronization transferred for each start event (FSLEN)

- the bit sense: most or lowest significant bit first (MSBF).

Additionally, the transmitter can be used to transfer synchronization and select the level driven on the TD pin while not in data transfer operation. This is done respectively by the Frame Sync Data Enable (FSDEN) and by the Data Default Value (DATDEF) bits in SSC\_TFMR.

# 33.6.10 PWM Channel Duty Cycle Register

| Register Name:<br>Access Type: | PWM_C<br>Read-wi | DTY[0X-1] |    |     |    |    |    |

|--------------------------------|------------------|-----------|----|-----|----|----|----|

| 31                             | 30               | 29        | 28 | 27  | 26 | 25 | 24 |

|                                |                  |           | CE | ΟΤΥ |    |    |    |

| 23                             | 22               | 21        | 20 | 19  | 18 | 17 | 16 |

|                                |                  |           | CE | ΤY  |    |    |    |

| 15                             | 14               | 13        | 12 | 11  | 10 | 9  | 8  |

|                                |                  |           | CE | ΤY  |    |    |    |

| 7                              | 6                | 5         | 4  | 3   | 2  | 1  | 0  |

|                                |                  |           | CE | ΤY  |    |    |    |

Only the first 16 bits (internal channel counter size) are significant.

# • CDTY: Channel Duty Cycle

Defines the waveform duty cycle. This value must be defined between 0 and CPRD (PWM\_CPRx).

#### 34.5.1.2 USB Bus Transactions

Each transfer results in one or more transactions over the USB bus. There are three kinds of transactions flowing across the bus in packets:

- 1. Setup Transaction

- 2. Data IN Transaction

- 3. Data OUT Transaction

#### 34.5.1.3 USB Transfer Event Definitions

As indicated below, transfers are sequential events carried out on the USB bus.

Table 34-3. USB Transfer Events

|                                         | • Setup transaction > Data IN transactions > Status                          |

|-----------------------------------------|------------------------------------------------------------------------------|

|                                         | OUT transaction                                                              |

| Control Transfers <sup>(1) (3)</sup>    | <ul> <li>Setup transaction &gt; Data OUT transactions &gt; Status</li> </ul> |

|                                         | IN transaction                                                               |

|                                         | <ul> <li>Setup transaction &gt; Status IN transaction</li> </ul>             |

| Interrupt IN Transfer                   | <ul> <li>Data IN transaction &gt; Data IN transaction</li> </ul>             |

| (device toward host)                    |                                                                              |

| Interrupt OUT Transfer                  | <ul> <li>Data OUT transaction &gt; Data OUT transaction</li> </ul>           |

| (host toward device)                    |                                                                              |

| Isochronous IN Transfer <sup>(2)</sup>  | <ul> <li>Data IN transaction &gt; Data IN transaction</li> </ul>             |

| (device toward host)                    |                                                                              |

| Isochronous OUT Transfer <sup>(2)</sup> | Data OUT transaction > Data OUT transaction                                  |

| (host toward device)                    |                                                                              |

| Bulk IN Transfer                        | Data IN transaction > Data IN transaction                                    |

| (device toward host)                    |                                                                              |

| Bulk OUT Transfer                       | Data OUT transaction > Data OUT transaction                                  |

| (host toward device)                    |                                                                              |

Notes: 1. Control transfer must use endpoints with no ping-pong attributes.

- 2. Isochronous transfers must use endpoints with ping-pong attributes.

- 3. Control transfers can be aborted using a stall handshake.

A status transaction is a special type of host-to-device transaction used only in a control transfer. The control transfer must be performed using endpoints with no ping-pong attributes. According to the control sequence (read or write), the USB device sends or receives a status transaction.

# 34.6.3 UDP Function Address Register

| Register Name | : UDP_F | UDP_FADDR |    |      |    |    |     |  |  |  |  |

|---------------|---------|-----------|----|------|----|----|-----|--|--|--|--|

| Access Type:  | Read-wr | ite       |    |      |    |    |     |  |  |  |  |

| 31            | 30      | 29        | 28 | 27   | 26 | 25 | 24  |  |  |  |  |

| -             | -       | -         | -  | -    | -  | -  | -   |  |  |  |  |

| 23            | 22      | 21        | 20 | 19   | 18 | 17 | 16  |  |  |  |  |

| _             | _       | -         | -  | -    | -  | _  | -   |  |  |  |  |

| 15            | 14      | 13        | 12 | 11   | 10 | 9  | 8   |  |  |  |  |

| -             | -       | -         | -  | —    | -  | _  | FEN |  |  |  |  |

| 7             | 6       | 5         | 4  | 3    | 2  | 1  | 0   |  |  |  |  |

| -             |         |           |    | FADD |    |    |     |  |  |  |  |

# • FADD[6:0]: Function Address Value

The Function Address Value must be programmed by firmware once the device receives a set address request from the host, and has achieved the status stage of the no-data control sequence. Refer to the *Universal Serial Bus Specification, Rev. 2.0* for more information. After power up or reset, the function address value is set to 0.

#### • FEN: Function Enable

Read:

0 = Function endpoint disabled.

1 = Function endpoint enabled.

Write:

0 = Disables function endpoint.

1 = Default value.

The Function Enable bit (FEN) allows the microcontroller to enable or disable the function endpoints. The microcontroller sets this bit after receipt of a reset from the host. Once this bit is set, the USB device is able to accept and transfer data packets from and to the host.

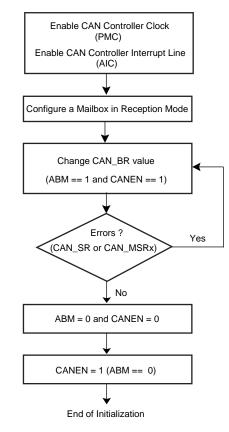

#### Figure 36-10. Possible Initialization Procedure

#### 36.7.2 CAN Controller Interrupt Handling

There are two different types of interrupts. One type of interrupt is a message-object related interrupt, the other is a system interrupt that handles errors or system-related interrupt sources.

All interrupt sources can be masked by writing the corresponding field in the CAN\_IDR register. They can be unmasked by writing to the CAN\_IER register. After a power-up reset, all interrupt sources are disabled (masked). The current mask status can be checked by reading the CAN\_IMR register.

The CAN\_SR register gives all interrupt source states.

The following events may initiate one of the two interrupts:

- Message object interrupt

- Data registers in the mailbox object are available to the application. In Receive Mode, a new message was received. In Transmit Mode, a message was transmitted successfully.

- A sent transmission was aborted.

- System interrupts

- Bus off interrupt: The CAN module enters the bus off state.

- Error passive interrupt: The CAN module enters Error Passive Mode.

- Error Active Mode: The CAN module is neither in Error Passive Mode nor in Bus Off mode.

- Warn Limit interrupt: The CAN module is in Error-active Mode, but at least one of its error counter value exceeds 96.

- Wake-up interrupt: This interrupt is generated after a wake-up and a bus synchronization.

- Sleep interrupt: This interrupt is generated after a Low-power Mode enable once all pending messages in transmission have been sent.

- Internal timer counter overflow interrupt: This interrupt is generated when the internal timer rolls over.

A form error results from violations on one or more of the fixed form of the following bit fields:

- CRC delimiter

- ACK delimiter

- End of frame

- Error delimiter

- Overload delimiter

This flag is automatically cleared by reading CAN\_SR register.

#### • BERR: Bit Error

0 = No bit error occurred during a previous transfer.

1 = A bit error occurred during a previous transfer.

A bit error is set when the bit value monitored on the line is different from the bit value sent.

This flag is automatically cleared by reading CAN\_SR register.

#### • RBSY: Receiver busy

0 = CAN receiver is not receiving a frame.

1 = CAN receiver is receiving a frame.

Receiver busy. This status bit is set by hardware while CAN receiver is acquiring or monitoring a frame (remote, data, overload or error frame). It is automatically reset when CAN is not receiving.

#### • TBSY: Transmitter busy

0 = CAN transmitter is not transmitting a frame.

1 = CAN transmitter is transmitting a frame.

Transmitter busy. This status bit is set by hardware while CAN transmitter is generating a frame (remote, data, overload or error frame). It is automatically reset when CAN is not transmitting.

# • OVLSY: Overload busy

0 = CAN transmitter is not transmitting an overload frame.

1 = CAN transmitter is transmitting a overload frame.

It is automatically reset when the bus is not transmitting an overload frame.

# 37.4 Programming Interface

# 37.4.1 Initialization

#### 37.4.1.1 Configuration

Initialization of the EMAC configuration (e.g., loop-back mode, frequency ratios) must be done while the transmit and receive circuits are disabled. See the description of the network control register and network configuration register earlier in this document.

To change loop-back mode, the following sequence of operations must be followed:

- 1. Write to network control register to disable transmit and receive circuits.

- 2. Write to network control register to change loop-back mode.

- 3. Write to network control register to re-enable transmit or receive circuits.

Note: These writes to network control register cannot be combined in any way.

#### 37.4.1.2 Receive Buffer List

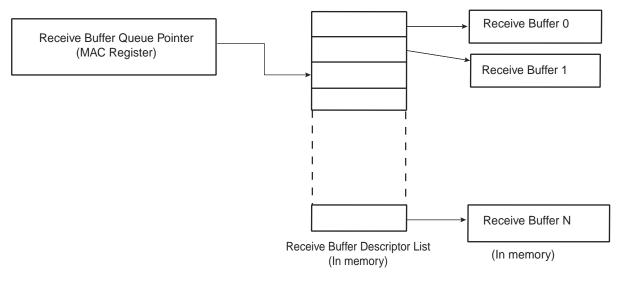

Receive data is written to areas of data (i.e., buffers) in system memory. These buffers are listed in another data structure that also resides in main memory. This data structure (receive buffer queue) is a sequence of descriptor entries as defined in "Receive Buffer Descriptor Entry" on page 537. It points to this data structure.

#### Figure 37-2. Receive Buffer List

To create the list of buffers:

- 1. Allocate a number (n) of buffers of 128 bytes in system memory.

- 2. Allocate an area 2*n* words for the receive buffer descriptor entry in system memory and create *n* entries in this list. Mark all entries in this list as owned by EMAC, i.e., bit 0 of word 0 set to 0.

- 3. If less than 1024 buffers are defined, the last descriptor must be marked with the wrap bit (bit 1 in word 0 set to 1).

- 4. Write address of receive buffer descriptor entry to EMAC register receive\_buffer queue pointer.

- 5. The receive circuits can then be enabled by writing to the address recognition registers and then to the network control register.

#### 37.4.1.3 Transmit Buffer List

Transmit data is read from areas of data (the buffers) in system memory These buffers are listed in another data structure that also resides in main memory. This data structure (Transmit Buffer Queue) is a sequence of descriptor entries (as defined in Table 37-2 on page 539) that points to this data structure.

To create this list of buffers:

# Atmel

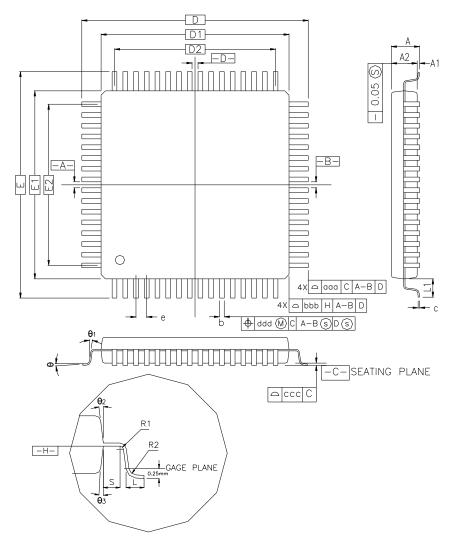

# 39. SAM7X512/256/128 Mechanical Characteristics

# 39.1 Package Drawings

Figure 39-1. LQFP Package Drawing

Atmel

| Part  | SAM7Xx Product<br>Revision or Manufacturing Number<br>Errata | SAM7X512 rev A | SAM7X512 rev B | SAM7X256/128 rev A | SAM7X256/128 rev B | SAM7X256/128 rev C |

|-------|--------------------------------------------------------------|----------------|----------------|--------------------|--------------------|--------------------|

| SPI   | LASTXFER (Last Transfer) behavior                            | Х              | Х              | Х                  | Х                  | _                  |

| SPI   | SPCK Behavior in Master Mode                                 |                | Х              | Х                  | Х                  | -                  |

| SPI   | Chip Select and Fixed Mode                                   |                | Х              | Х                  | Х                  | -                  |

| SPI   | Baudrate Set to 1                                            | Х              | Х              | Х                  | Х                  | _                  |

| SPI   | Bad Serial Clock Generation on 2nd Chip Select               | Х              | Х              | Х                  | Х                  | Х                  |

| SSC   | Periodic Transmission Limitations in Master Mode             | Х              | Х              | Х                  | Х                  | -                  |

| SSC   | Transmitter Limitations in Slave Mode                        | Х              | Х              | Х                  | Х                  | -                  |

| SSC   | Transmitter Limitations in Slave Mode                        | Х              | Х              | Х                  | Х                  | -                  |

| TWI   | Clock Divider                                                | Х              | Х              | Х                  | Х                  | _                  |

| TWI   | Software Reset                                               | Х              | Х              | Х                  | Х                  | _                  |

| TWI   | Disabling Does not Operate Correctly                         | Х              | Х              | Х                  | Х                  | -                  |

| TWI   | NACK Status Bit Lost                                         | Х              | Х              | Х                  | Х                  | _                  |

| TWI   | Possible Receive Holding Register Corruption                 | Х              | Х              | Х                  | Х                  | -                  |

| USART | CTS in Hardware Handshaking                                  | Х              | Х              | Х                  | Х                  | _                  |

| USART | Hardware Handshaking – Two Characters Sent                   | Х              | Х              | Х                  | Х                  | -                  |

| USART | RXBRK Flag Error in Asynchronous Mode                        | Х              | Х              | Х                  | Х                  | -                  |

| USART | DCD is active High instead of Low                            | Х              | Х              | Х                  | Х                  | Х                  |

# Table 41-1. Errata Summary Table (Continued)