#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                       |

| Core Size                  | 16/32-Bit                                                                   |

| Speed                      | 55MHz                                                                       |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                               |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-LQFP                                                                    |

| Supplier Device Package    | 100-LQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x128c-aur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Configuration Summary of the SAM7X512/256/128

The SAM7X512, SAM7X256 and SAM7X128 differ only in memory sizes. Table 1-1 summarizes the configurations of the three devices.

| Table 1-1. | Configuration Summary |

|------------|-----------------------|

|------------|-----------------------|

| Device   | Flash      | Flash Organization | SRAM       |

|----------|------------|--------------------|------------|

| SAM7X512 | 512 Kbytes | Dual-plane         | 128 Kbytes |

| SAM7X256 | 256 Kbytes | Single-plane       | 64 Kbytes  |

| SAM7X128 | 128 Kbytes | Single-plane       | 32 Kbytes  |

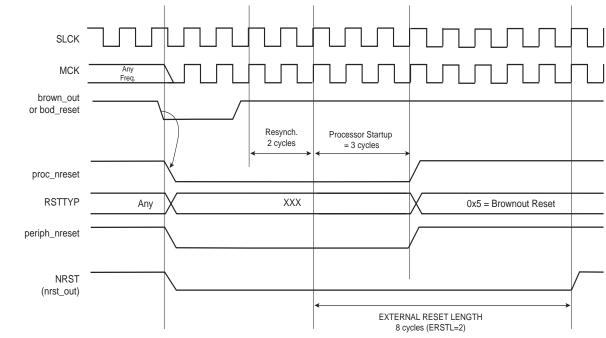

#### 13.2.4.3 Brownout Reset

When the brown\_out/bod\_reset signal is asserted, the Reset State Manager immediately enters the Brownout Reset. In this state, the processor, the peripheral and the external reset lines are asserted.

The Brownout Reset is left 3 Slow Clock cycles after the rising edge of brown\_out/bod\_reset after a two-cycle resynchronization. An external reset is also triggered.

When the processor reset is released, the field RSTTYP in RSTC\_SR is loaded with the value 0x5, thus indicating that the last reset is a Brownout Reset.

#### Figure 13-6. Brownout Reset State

## 13.3 Reset Controller (RSTC) User Interface

Table 13-1. Register Mapping

| Offset | Register         | Name    | Access     | Reset       |

|--------|------------------|---------|------------|-------------|

| 0x00   | Control Register | RSTC_CR | Write-only | -           |

| 0x04   | Status Register  | RSTC_SR | Read-only  | 0x0000_0000 |

| 0x08   | Mode Register    | RSTC_MR | Read-write | 0x0000_0000 |

It is made up of:

- A bus arbiter

- An address decoder

- An abort status

- A misalignment detector

- An Embedded Flash Controller

The MC handles only little-endian mode accesses. The masters work in little-endian mode only.

#### 18.3.1 Bus Arbiter

The Memory Controller has a simple, hard-wired priority bus arbiter that gives the control of the bus to one of the three masters. The EMAC has the highest priority; the Peripheral DMA Controller has the medium priority; the ARM processor has the lowest one.

#### 18.3.2 Address Decoder

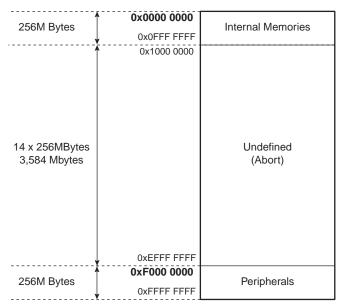

The Memory Controller features an Address Decoder that first decodes the four highest bits of the 32-bit address bus and defines three separate areas:

- One 256-Mbyte address space for the internal memories

- One 256-Mbyte address space reserved for the embedded peripherals

- An undefined address space of 3584M bytes representing fourteen 256-Mbyte areas that return an Abort if accessed

Figure 18-2 shows the assignment of the 256-Mbyte memory areas.

#### Figure 18-2. Memory Areas

#### 18.3.2.1 Internal Memory Mapping

Within the Internal Memory address space, the Address Decoder of the Memory Controller decodes eight more address bits to allocate 1-Mbyte address spaces for the embedded memories.

The allocated memories are accessed all along the 1-Mbyte address space and so are repeated n times within this address space, n equaling 1M bytes divided by the size of the memory.

When the address of the access is undefined within the internal memory area, the Address Decoder returns an Abort to the master.

# Atmel

| Figure 25-4. | Switch Master Clock from Main Clock to Slow Clock |

|--------------|---------------------------------------------------|

|              | Slow Clock                                        |

|              | Main Clock                                        |

|              | MCKRDY                                            |

|              | Master Clock                                      |

|              | Write PMC_MCKR                                    |

| Figure 25-5. | Change PLL Programming                            |

| -            |                                                   |

|              |                                                   |

|              | LOCK                                              |

|              | MCKRDY                                            |

|              |                                                   |

|              | Write CKGR_PLLR                                   |

## 27.4 Functional Description

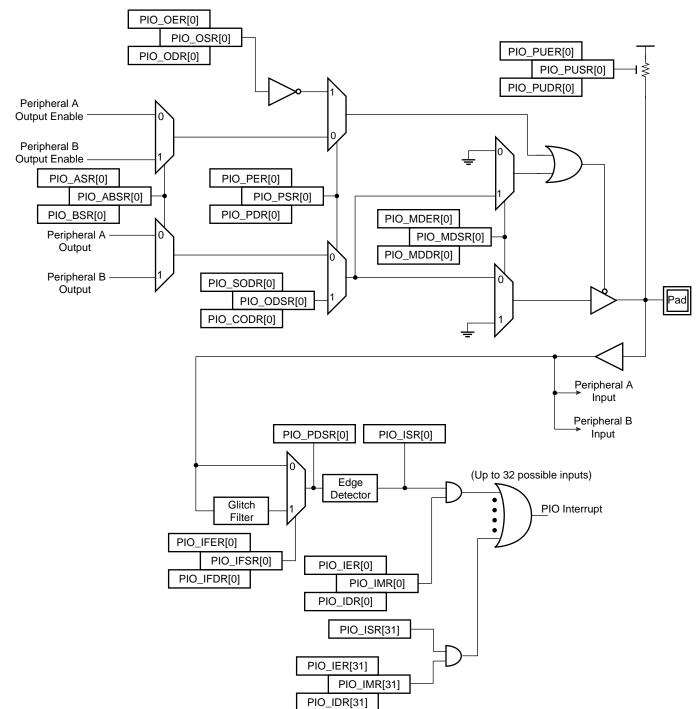

The PIO Controller features up to 32 fully-programmable I/O lines. Most of the control logic associated to each I/O is represented in Figure 27-3. In this description each signal shown represents but one of up to 32 possible indexes.

#### Figure 27-3. I/O Line Control Logic

## 27.4.1 Pull-up Resistor Control

Each I/O line is designed with an embedded pull-up resistor. The pull-up resistor can be enabled or disabled by writing respectively PIO\_PUER (Pull-up Enable Register) and PIO\_PUDR (Pull-up Disable Resistor). Writing in these registers

# Atmel

## 27.6.11 PIO Controller Clear Output Data Register

| Name:        | PIO_CO    | DR  |     |     |     |     |     |

|--------------|-----------|-----|-----|-----|-----|-----|-----|

| Access Type: | Write-onl | У   |     |     |     |     |     |

| 31           | 30        | 29  | 28  | 27  | 26  | 25  | 24  |

| P31          | P30       | P29 | P28 | P27 | P26 | P25 | P24 |

| 23           | 22        | 21  | 20  | 19  | 18  | 17  | 16  |

| P23          | P22       | P21 | P20 | P19 | P18 | P17 | P16 |

| 15           | 14        | 13  | 12  | 11  | 10  | 9   | 8   |

| P15          | P14       | P13 | P12 | P11 | P10 | P9  | P8  |

| 7            | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

| P7           | P6        | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Set Output Data

0 = No effect.

1 = Clears the data to be driven on the I/O line.

#### 27.6.12 PIO Controller Output Data Status Register

| Name: | PIO ODSR |

|-------|----------|

| Nume. | 110_0001 |

Access Type: Read-only or Read-write

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

#### • P0-P31: Output Data Status

0 = The data to be driven on the I/O line is 0.

1 = The data to be driven on the I/O line is 1.

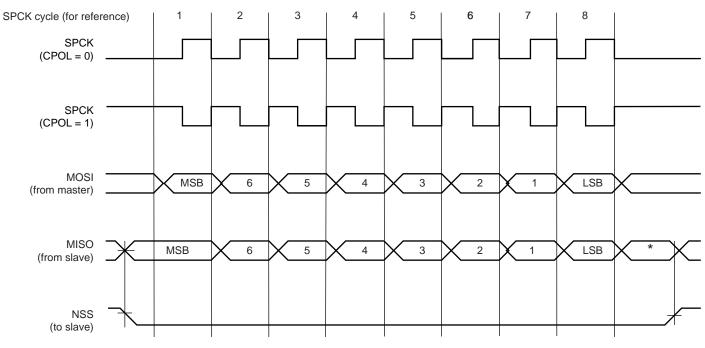

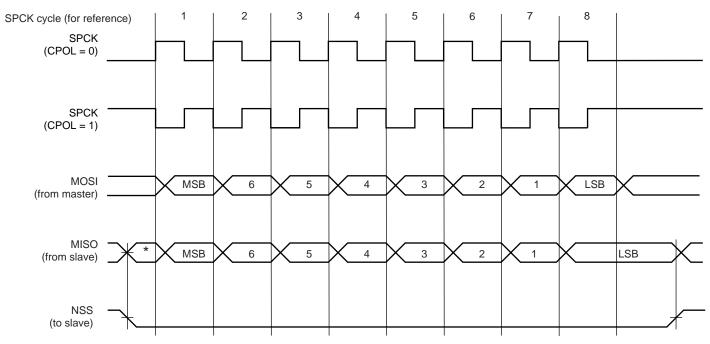

\* Not defined, but normally MSB of previous character received.

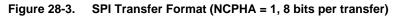

#### Figure 28-4. SPI Transfer Format (NCPHA = 0, 8 bits per transfer)

\* Not defined but normally LSB of previous character transmitted.

## 28.7.6 SPI Interrupt Enable Register

| Name:<br>Access Type: | SPI_IER<br>Write-on |       |       |       |      |         |      |

|-----------------------|---------------------|-------|-------|-------|------|---------|------|

| 31                    | 30                  | 29    | 28    | 27    | 26   | 25      | 24   |

| _                     | _                   | -     | -     | -     | —    | -       | -    |

| 23                    | 22                  | 21    | 20    | 19    | 18   | 17      | 16   |

| —                     | _                   | -     | —     | —     | —    | —       | —    |

| 15                    | 14                  | 13    | 12    | 11    | 10   | 9       | 8    |

| -                     | —                   | -     | _     | -     | -    | TXEMPTY | NSSR |

| 7                     | 6                   | 5     | 4     | 3     | 2    | 1       | 0    |

| TXBUFE                | RXBUFF              | ENDTX | ENDRX | OVRES | MODF | TDRE    | RDRF |

- RDRF: Receive Data Register Full Interrupt Enable

- TDRE: SPI Transmit Data Register Empty Interrupt Enable

- MODF: Mode Fault Error Interrupt Enable

- OVRES: Overrun Error Interrupt Enable

- ENDRX: End of Receive Buffer Interrupt Enable

- ENDTX: End of Transmit Buffer Interrupt Enable

- RXBUFF: Receive Buffer Full Interrupt Enable

- TXBUFE: Transmit Buffer Empty Interrupt Enable

- TXEMPTY: Transmission Registers Empty Enable

- NSSR: NSS Rising Interrupt Enable

0 = No effect.

1 = Enables the corresponding interrupt.

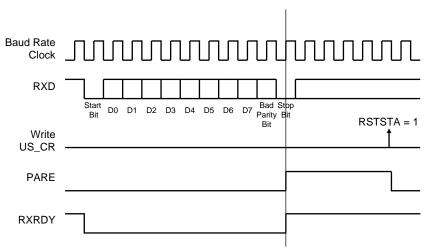

#### 30.6.3.5 Parity

The USART supports five parity modes selected by programming the PAR field in the Mode Register (US\_MR). The PAR field also enables the Multidrop mode, see "Multidrop Mode" on page 305. Even and odd parity bit generation and error detection are supported.

If even parity is selected, the parity generator of the transmitter drives the parity bit at 0 if a number of 1s in the character data bit is even, and at 1 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If odd parity is selected, the parity generator of the transmitter drives the parity bit at 1 if a number of 1s in the character data bit is even, and at 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit at 1 if a number of 1s in the character data bit is even, and at 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If the mark parity is used, the parity generator of the transmitter drives the parity bit at 1 for all characters. The receiver parity checker reports an error if the parity bit is sampled at 0. If the space parity is used, the parity generator of the transmitter drives the parity bit at 0 for all characters. The receiver parity checker reports an error if the parity does not generate any parity bit and the receiver does not report any parity error.

Table 30-6 shows an example of the parity bit for the character 0x41 (character ASCII "A") depending on the configuration of the USART. Because there are two bits at 1, 1 bit is added when a parity is odd, or 0 is added when a parity is even.

| Character | Hexa | Binary    | Parity Bit | Parity Mode |

|-----------|------|-----------|------------|-------------|

| A         | 0x41 | 0100 0001 | 1          | Odd         |

| A         | 0x41 | 0100 0001 | 0          | Even        |

| A         | 0x41 | 0100 0001 | 1          | Mark        |

| A         | 0x41 | 0100 0001 | 0          | Space       |

| A         | 0x41 | 0100 0001 | None       | None        |

#### Table 30-6.Parity Bit Examples

When the receiver detects a parity error, it sets the PARE (Parity Error) bit in the Channel Status Register (US\_CSR). The PARE bit can be cleared by writing the Control Register (US\_CR) with the RSTSTA bit at 1. Figure 30-12 illustrates the parity bit status setting and clearing.

#### Figure 30-12. Parity Error

## 33.6.12 PWM Channel Counter Register

| Register Name:<br>Access Type: | PWM_C<br>Read-or | CNT[0X-1] |    |    |    |    |    |  |

|--------------------------------|------------------|-----------|----|----|----|----|----|--|

|                                |                  |           |    |    |    |    |    |  |

| 31                             | 30               | 29        | 28 | 27 | 26 | 25 | 24 |  |

|                                |                  |           | C  | NT |    |    |    |  |

| 23                             | 22               | 21        | 20 | 19 | 18 | 17 | 16 |  |

|                                |                  |           | C  | NT |    |    |    |  |

| 15                             | 14               | 13        | 12 | 11 | 10 | 9  | 8  |  |

| CNT                            |                  |           |    |    |    |    |    |  |

| 7                              | 6                | 5         | 4  | 3  | 2  | 1  | 0  |  |

|                                | CNT              |           |    |    |    |    |    |  |

#### • CNT: Channel Counter Register

Internal counter value. This register is reset when:

- the channel is enabled (writing CHIDx in the PWM\_ENA register).

- the counter reaches CPRD value defined in the PWM\_CPRDx register if the waveform is left aligned.

the consumer mailbox must have a lower number than the Receive with Overwrite mailbox. The transfer command can be triggered for all mailboxes at the same time by setting several MBx fields in the CAN\_TCR register.

#### Figure 36-18. Consumer Handling

| CAN BUS                |          | Remote Frame | Message x | Remote Frame | Message y |           |

|------------------------|----------|--------------|-----------|--------------|-----------|-----------|

| MRDY<br>(CAN_MSRx)     |          |              |           | ٦            |           |           |

| MMI<br>(CAN_MSRx)      |          |              |           |              |           |           |

| MTCR<br>(CAN_MCRx)     | <b>↑</b> |              |           | <b>≜</b>     |           |           |

|                        |          |              |           |              |           |           |

| (CAN_MDLx<br>CAN_MDHx) |          |              |           | Message x    |           | Message y |

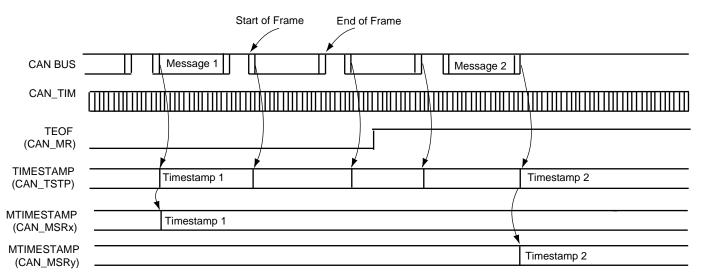

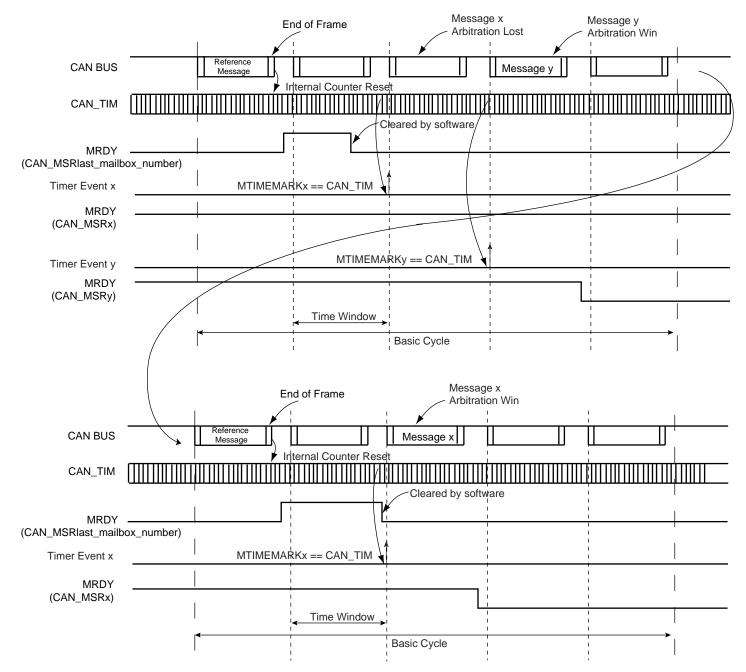

#### 36.7.4 CAN Controller Timing Modes

Using the free running 16-bit internal timer, the CAN controller can be set in one of the two following timing modes:

- Timestamping Mode: The value of the internal timer is captured at each Start Of Frame or each End Of Frame.

- Time Triggered Mode: The mailbox transfer operation is triggered when the internal timer reaches the mailbox trigger.

Timestamping Mode is enabled by clearing the TTM bit in the CAN\_MR register. Time Triggered Mode is enabled by setting the TTM bit in the CAN\_MR register.

#### 36.7.4.1 Timestamping Mode

Each mailbox has its own timestamp value. Each time a message is sent or received by a mailbox, the 16-bit value MTIMESTAMP of the CAN\_TIMESTP register is transferred to the LSB bits of the CAN\_MSRx register. The value read in the CAN\_MSRx register corresponds to the internal timer value at the Start Of Frame or the End Of Frame of the message handled by the mailbox.

#### Figure 36-19. Mailbox Timestamp

#### Figure 36-21. Time Triggered Operations

## 37.5.2 Network Configuration Register

| Register Name | EMAC_I | EMAC_NCFGR |     |        |       |       |      |  |  |

|---------------|--------|------------|-----|--------|-------|-------|------|--|--|

| Access Type:  | Read-w | ite        |     |        |       |       |      |  |  |

| 31            | 30     | 29         | 28  | 27     | 26    | 25    | 24   |  |  |

| -             | -      | -          | -   | -      | -     | -     | -    |  |  |

| 23            | 22     | 21         | 20  | 19     | 18    | 17    | 16   |  |  |

| -             | -      | -          | -   | IRXFCS | EFRHD | DRFCS | RLCE |  |  |

| 15            | 14     | 13         | 12  | 11 10  |       | 9     | 8    |  |  |

| RB            | OF     | PAE        | RTY | CI     | _K    |       | BIG  |  |  |

| 7             | 6      | 5          | 4   | 3      | 2     | 1     | 0    |  |  |

| UNI           | MTI    | NBC        | CAF | JFRAME | —     | FD    | SPD  |  |  |

#### • SPD: Speed

Set to 1 to indicate 100 Mbit/s operation, 0 for 10 Mbit/s.

#### • FD: Full Duplex

If set to 1, the transmit block ignores the state of collision and carrier sense and allows receive while transmitting.

#### • CAF: Copy All Frames

When set to 1, all valid frames are received.

#### • JFRAME: Jumbo Frames

Set to one to enable jumbo frames of up to 10240 bytes to be accepted.

#### NBC: No Broadcast

When set to 1, frames addressed to the broadcast address of all ones are not received.

#### • MTI: Multicast Hash Enable

When set, multicast frames are received when the 6-bit hash function of the destination address points to a bit that is set in the hash register.

#### • UNI: Unicast Hash Enable

When set, unicast frames are received when the 6-bit hash function of the destination address points to a bit that is set in the hash register.

#### • BIG: Receive 1536 bytes frames

Setting this bit means the EMAC receives frames up to 1536 bytes in length. Normally, the EMAC would reject any frame above 1518 bytes.

## 37.5.26.11 Transmit Underrun Errors Register

| Register Name: | EMAC_  | EMAC_TUND  |    |    |    |    |    |  |  |

|----------------|--------|------------|----|----|----|----|----|--|--|

| Access Type:   | Read-w | Read-write |    |    |    |    |    |  |  |

| 31             | 30     | 29         | 28 | 27 | 26 | 25 | 24 |  |  |

| -              | _      | -          | -  | -  | -  | -  | -  |  |  |

| 23             | 22     | 21         | 20 | 19 | 18 | 17 | 16 |  |  |

| _              | _      | _          | -  | -  | _  | _  | -  |  |  |

| 15             | 14     | 13         | 12 | 11 | 10 | 9  | 8  |  |  |

| -              | -      | -          | -  | -  | -  | -  | -  |  |  |

| 7              | 6      | 5          | 4  | 3  | 2  | 1  | 0  |  |  |

|                |        |            | TU | ND |    |    |    |  |  |

#### • TUND: Transmit Underruns

An 8-bit register counting the number of frames not transmitted due to a transmit DMA underrun. If this register is incremented, then no other statistics register is incremented.

| 37.5.26.12Carrier S | ense Errors | Register |

|---------------------|-------------|----------|

|---------------------|-------------|----------|

| Register Name:<br>Access Type: | : EMAC_0<br>Read-wr |    |    |         |    |    |    |

|--------------------------------|---------------------|----|----|---------|----|----|----|

| 31                             | 30                  | 29 | 28 | 27      | 26 | 25 | 24 |

| -                              | _                   | —  | -  | —       | —  | —  | —  |

| 23                             | 22                  | 21 | 20 | 19      | 18 | 17 | 16 |

| -                              | _                   | -  | -  | -       | -  | -  | -  |

| 15                             | 14                  | 13 | 12 | 11      | 10 | 9  | 8  |

| -                              | —                   | -  | -  | -       | -  | -  | -  |

| 7                              | 6                   | 5  | 4  | 3<br>SE | 2  | 1  | 0  |

|                                |                     |    | 0. | JL      |    |    |    |

#### • CSE: Carrier Sense Errors

An 8-bit register counting the number of frames transmitted where carrier sense was not seen during transmission or where carrier sense was deasserted after being asserted in a transmit frame without collision (no underrun). Only incremented in halfduplex mode. The only effect of a carrier sense error is to increment this register. The behavior of the other statistics registers is unaffected by the detection of a carrier sense error.

## 41. SAM7X512/256/128 Errata

## 41.1 Marking

All devices are marked with the Atmel logo and the ordering code.

Additional marking has the following format:

where

- "YY": manufactory year

- "WW": manufactory week

- "V": revision

- "XXXXXXXXX": lot number

| Part  | SAM7Xx Product<br>Revision or Manufacturing Number<br>Errata | SAM7X512 rev A | SAM7X512 rev B | SAM7X256/128 rev A | SAM7X256/128 rev B | SAM7X256/128 rev C |

|-------|--------------------------------------------------------------|----------------|----------------|--------------------|--------------------|--------------------|

| SPI   | LASTXFER (Last Transfer) behavior                            | Х              | Х              | Х                  | Х                  | _                  |

| SPI   | SPCK Behavior in Master Mode                                 | Х              | Х              | Х                  | Х                  | -                  |

| SPI   | Chip Select and Fixed Mode                                   | Х              | Х              | Х                  | Х                  | -                  |

| SPI   | Baudrate Set to 1                                            | Х              | Х              | Х                  | Х                  | _                  |

| SPI   | Bad Serial Clock Generation on 2nd Chip Select               | Х              | Х              | Х                  | Х                  | Х                  |

| SSC   | Periodic Transmission Limitations in Master Mode             | Х              | Х              | Х                  | Х                  | -                  |

| SSC   | Transmitter Limitations in Slave Mode                        | Х              | Х              | Х                  | Х                  | -                  |

| SSC   | Transmitter Limitations in Slave Mode                        | Х              | Х              | Х                  | Х                  | -                  |

| TWI   | Clock Divider                                                | Х              | Х              | Х                  | Х                  | _                  |

| TWI   | Software Reset                                               | Х              | Х              | Х                  | Х                  | _                  |

| TWI   | Disabling Does not Operate Correctly                         | Х              | Х              | Х                  | Х                  | -                  |

| TWI   | NACK Status Bit Lost                                         | Х              | Х              | Х                  | Х                  | _                  |

| TWI   | Possible Receive Holding Register Corruption                 | Х              | Х              | Х                  | Х                  | -                  |

| USART | CTS in Hardware Handshaking                                  | Х              | Х              | Х                  | Х                  | _                  |

| USART | Hardware Handshaking – Two Characters Sent                   | Х              | Х              | Х                  | Х                  | -                  |

| USART | RXBRK Flag Error in Asynchronous Mode                        | Х              | Х              | Х                  | Х                  | -                  |

| USART | DCD is active High instead of Low                            | Х              | Х              | Х                  | Х                  | Х                  |

## Table 41-1. Errata Summary Table (Continued)

## 41.5 AT91SAM7X256/128 Errata - Rev. B Parts

Refer to Section 41.1 "Marking" on page 607.

Note: AT91SAM7X256 Revision B chip ID is 0x275B 0940. AT91SAM7X128 Revision B chip ID is 0x275A 0740.

#### 41.5.1 Analog-to-Digital Converter (ADC)

#### 41.5.1.1 ADC: DRDY Bit Cleared

The DRDY Flag should be clear only after a read of ADC\_LCDR (Last Converted Data Register). A read of any ADC\_CDRx register (Channel Data Register) automatically clears the DRDY flag. Problem Fix/Workaround:

#### None

#### 41.5.1.2 ADC: DRDY not Cleared on Disable

When reading LCDR at the same instant as an end of conversion, with DRDY already active, DRDY is kept active regardless of the enable status of the current channel. This sets DRDY, whereas new data is not stored. Problem Fix/Workaround

None

#### 41.5.1.3 ADC: DRDY Possibly Skipped due to CDR Read

Reading CDR for channel "y" at the same instant as an end of conversion on channel "x" with EOC[x] already active, leads to skipping to set the DRDY flag if channel "x" is enabled. Problem Fix/Workaround

Use of DRDY functionality with access to CDR registers should be avoided.

#### 41.5.1.4 ADC: Possible Skip on DRDY when Disabling a Channel

DRDY does not rise when disabling channel "y" at the same time as an end of "x" channel conversion, although data is stored into CDRx and LCDR.

Problem Fix/Workaround

None.

#### 41.5.1.5 ADC: GOVRE Bit is not Updated

Read of the Status Register at the same instant as an end of conversion leads to skipping the update of the GOVRE (general overrun) flag. GOVRE is neither reset nor set.

For example, if reading the status while an end of conversion is occurring and:

- 1. GOVRE is active but DRDY is inactive, does not correspond to a new general overrun condition but the GOVRE flag is not reset.

- 2. GOVRE is inactive but DRDY is active, does correspond to a new general overrun condition but the GOVRE flag is not set.

Problem Fix/Workaround

None

#### 41.5.1.6 ADC: GOVRE Bit is not Set when Reading CDR

When reading CDRy (Channel Data Register y) at the same instant as an end of conversion on channel "x" with the following conditions:

| Version<br>6120H<br>(Continued) | ) Comments                                                                                                |      |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------|------|--|--|--|--|--|

|                                 | UDP:                                                                                                      |      |  |  |  |  |  |

|                                 | Section 34.6 "USB Device Port (UDP) User Interface", reset value for UDP_RST_EP is 0x000_0000.            |      |  |  |  |  |  |

|                                 | Table 34-1, "USB Endpoint Description", footnote added to Dual-Bank heading.                              | 5150 |  |  |  |  |  |

|                                 | Section 34.5.2.5 "Transmit Data Cancellation", added to datasheet                                         |      |  |  |  |  |  |

|                                 | Section 34.6.9 "UDP Reset Endpoint Register", added steps to clear endpoints.                             |      |  |  |  |  |  |

|                                 | Electrical Characteristics:                                                                               |      |  |  |  |  |  |

|                                 | Table 38-2, "DC Characteristics", CMOS conditions added to IO for VOL and VOH.                            | rfo  |  |  |  |  |  |

|                                 | Table 38-16, "External Voltage Reference Input", added ADVREF input w/conditions "8-bit resolution mode". |      |  |  |  |  |  |

|                                 | Mechanical Characteristics:                                                                               |      |  |  |  |  |  |

|                                 | Table 39-1, "100-lead LQFP Package Dimensions", Symbol line A, Inch Max value is 0.063                    | 5608 |  |  |  |  |  |

|                                 | Ordering Information:                                                                                     |      |  |  |  |  |  |

|                                 | Section 40. "AT91SAM7X Ordering Information", MLR B parts added to ordering information.                  |      |  |  |  |  |  |

|                                 | Errata:                                                                                                   |      |  |  |  |  |  |

|                                 | Section 41.5 "AT91SAM7X256/128 Errata - Rev. B Parts", added to errata.                                   | 6064 |  |  |  |  |  |

|                                 | Section 41.4.3.1 "EFC: Embedded Flash Access Time", added to SAM7X512 erraa.                              |      |  |  |  |  |  |

|                                 | Section 41.4.8.7 "SPI: Software Reset must be Written Twice" added to errata.                             |      |  |  |  |  |  |

|                                 | USART: XOFF Character Bad Behavior, removed from errata.                                                  | 5338 |  |  |  |  |  |

| De | scription                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Fe | atures                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 1. | Configuration Summary of the SAM7X512/256/128 4                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| 2. | SAM7X512/256/128 Block Diagram                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 3. | Signal Description                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 4. | Package         9           4.1         100-lead LQFP Package Outline         9           4.2         100-lead LQFP Pinout         9           4.3         100-ball TFBGA Package Outline         10           4.4         100-ball TFBGA Pinout         10                                                                                                                |  |  |  |  |  |  |

| 5. | Power Considerations115.1Power Supplies115.2Power Consumption115.3Voltage Regulator115.4Typical Powering Schematics11                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 6. | I/O Lines Considerations       13         6.1       JTAG Port Pins       13         6.2       Test Pin       13         6.3       Reset Pin       13         6.4       ERASE Pin       13         6.5       PIO Controller Lines       13         6.6       I/O Lines Current Drawing       14                                                                             |  |  |  |  |  |  |

| 7. | Processor and Architecture157.1ARM7TDMI Processor157.2Debug and Test Features157.3Memory Controller157.4Peripheral DMA Controller16                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 8. | Memories         17           8.1         SAM7X512         17           8.2         SAM7X256         17           8.3         SAM7X128         17           8.4         Memory Mapping         17           8.5         Embedded Flash         20           8.6         Fast Flash Programming Interface         22           8.7         SAM-BA Boot Assistant         22 |  |  |  |  |  |  |

| 9. | System Controller239.1Reset Controller259.2Clock Generator269.3Power Management Controller279.4Advanced Interrupt Controller279.5Debug Unit28                                                                                                                                                                                                                              |  |  |  |  |  |  |