#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                       |

| Core Size                  | 16/32-Bit                                                                   |

| Speed                      | 55MHz                                                                       |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 62                                                                          |

| Program Memory Size        | 128KB (128K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 32K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                               |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TFBGA                                                                   |

| Supplier Device Package    | 100-TFBGA (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x128c-cur |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 10.9 USART

- Programmable Baud Rate Generator

- 5- to 9-bit full-duplex synchronous or asynchronous serial communications

- 1, 1.5 or 2 stop bits in Asynchronous Mode

- 1 or 2 stop bits in Synchronous Mode

- Parity generation and error detection

- Framing error detection, overrun error detection

- MSB or LSB first

- Optional break generation and detection

- By 8 or by 16 over-sampling receiver frequency

- Hardware handshaking RTS CTS

- Modem Signals Management DTR-DSR-DCD-RI on USART1

- Receiver time-out and transmitter timeguard

- Multi-drop Mode with address generation and detection

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- IrDA modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

## **10.10 Serial Synchronous Controller**

- Provides serial synchronous communication links used in audio and telecom applications

- Contains an independent receiver and transmitter and a common clock divider

- Offers a configurable frame sync and data length

- Receiver and transmitter can be programmed to start automatically or on detection of different event on the frame sync signal

- Receiver and transmitter include a data signal, a clock signal and a frame synchronization signal

# 10.11 Timer Counter

- Three 16-bit Timer Counter Channels

- Two output compare or one input capture per channel

- Wide range of functions including:

- Frequency measurement

- Event counting

- Interval measurement

- Pulse generation

- Delay timing

- Pulse Width Modulation

- Up/down capabilities

- Each channel is user-configurable and contains:

- Three external clock inputs

# 14.4.2 Real-time Timer Alarm Register

| Register Name:<br>Access Type: | RTT_AF<br>Read-wi |    |    |    |    |    |    |

|--------------------------------|-------------------|----|----|----|----|----|----|

| 31                             | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

|                                |                   |    | AL | M∨ |    |    |    |

| 23                             | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

|                                |                   |    | AL | MV |    |    |    |

| 15                             | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

|                                |                   |    | AL | MV |    |    |    |

| 7                              | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                                |                   |    | AL | MV |    |    |    |

#### • ALMV: Alarm Value

Defines the alarm value (ALMV+1) compared with the Real-time Timer.

## 14.4.3 Real-time Timer Value Register

| Register Name:<br>Access Type: | RTT_VI<br>Read-o |    |    |      |    |    |    |

|--------------------------------|------------------|----|----|------|----|----|----|

| 31                             | 30               | 29 | 28 | 27   | 26 | 25 | 24 |

|                                |                  |    | CF | TV   |    |    |    |

| 23                             | 22               | 21 | 20 | 19   | 18 | 17 | 16 |

|                                |                  |    | CR | TV   |    |    |    |

| 15                             | 14               | 13 | 12 | 11   | 10 | 9  | 8  |

|                                |                  |    | CR | RTV  |    |    |    |

| 7                              | 6                | 5  | 4  | 3    | 2  | 1  | 0  |

|                                |                  |    | CF | RTV. |    |    |    |

#### • CRTV: Current Real-time Value

Returns the current value of the Real-time Timer.

## 15.4.4 Periodic Interval Timer Image Register

| Register Name: | PIT_PII |     |     |      |    |    |    |

|----------------|---------|-----|-----|------|----|----|----|

| Access Type:   | Read-or | nly |     |      |    |    |    |

| 31             | 30      | 29  | 28  | 27   | 26 | 25 | 24 |

|                |         |     | PIC | CNT  |    |    |    |

|                |         |     |     |      |    |    |    |

| 23             | 22      | 21  | 20  | 19   | 18 | 17 | 16 |

|                | PIC     | CNT |     | CPIV |    |    |    |

| 45             |         | 10  | 10  | 44   | 10 | 0  | 0  |

| 15             | 14      | 13  | 12  | 11   | 10 | 9  | 8  |

|                |         |     | CI  | PIV  |    |    |    |

| _              |         | _   |     |      | 0  |    |    |

| 1              | 6       | 5   | 4   | 3    | 2  | 1  | 0  |

|                |         |     | CI  | PIV  |    |    |    |

## • CPIV: Current Periodic Interval Value

Returns the current value of the periodic interval timer.

## • PICNT: Periodic Interval Counter

Returns the number of occurrences of periodic intervals since the last read of PIT\_PIVR.

## 16.4.3 Watchdog Timer Status Register

| Register Name: | WDT_S   | R   |    |    |    |       |       |

|----------------|---------|-----|----|----|----|-------|-------|

| Access Type:   | Read-or | nly |    |    |    |       |       |

| 31             | 30      | 29  | 28 | 27 | 26 | 25    | 24    |

| -              | _       | -   | -  | -  | -  | -     | -     |

| 23             | 22      | 21  | 20 | 19 | 18 | 17    | 16    |

| _              | _       | -   | -  | -  | -  | _     | _     |

| 15             | 14      | 13  | 12 | 11 | 10 | 9     | 8     |

| _              | _       | -   | -  | -  | -  | -     | -     |

| 7              | 6       | 5   | 4  | 3  | 2  | 1     | 0     |

| _              | _       | _   | _  | _  | -  | WDERR | WDUNF |

## • WDUNF: Watchdog Underflow

0: No Watchdog underflow occurred since the last read of WDT\_SR.

1: At least one Watchdog underflow occurred since the last read of WDT\_SR.

## • WDERR: Watchdog Error

0: No Watchdog error occurred since the last read of WDT\_SR.

1: At least one Watchdog error occurred since the last read of WDT\_SR.

|               | initialità Bit Goding (G | , on an a company of the second se |

|---------------|--------------------------|-----------------------------------------------------------------------------------------------------------------|

| DATA[15:0]    | Symbol                   | Command Executed                                                                                                |

| 0x0042        | EWPL                     | Erase Page and Write Page then Lock                                                                             |

| 0x0013        | EA                       | Erase All                                                                                                       |

| 0x0014        | SLB                      | Set Lock Bit                                                                                                    |

| 0x0024        | CLB                      | Clear Lock Bit                                                                                                  |

| 0x0015        | GLB                      | Get Lock Bit                                                                                                    |

| 0x0034        | SGPB                     | Set General Purpose NVM bit                                                                                     |

| 0x0044        | CGPB                     | Clear General Purpose NVM bit                                                                                   |

| 0x0025        | GGPB                     | Get General Purpose NVM bit                                                                                     |

| 0x0054        | SSE                      | Set Security Bit                                                                                                |

| 0x0035        | GSE                      | Get Security Bit                                                                                                |

| 0x001F        | WRAM                     | Write Memory                                                                                                    |

| 0x0016        | SEFC                     | Select EFC Controller <sup>(1)</sup>                                                                            |

| 0x001E        | GVE                      | Get Version                                                                                                     |

| Natas d Ammil | LOA TO A CAMEVEAD        |                                                                                                                 |

#### Table 20-3. Command Bit Coding (Continued)

Note: 1. Applies to AT91SAM7X512.

#### 20.2.3 Entering Programming Mode

The following algorithm puts the device in Parallel Programming Mode:

- Apply GND, VDDIO, VDDCORE, VDDFLASH and VDDPLL.

- Apply XIN clock within T<sub>POR RESET</sub> if an external clock is available.

- Wait for T<sub>POR\_RESET</sub>

- Start a read or write handshaking.

- Note: After reset, the device is clocked by the internal RC oscillator. Before clearing RDY signal, if an external clock ( > 32 kHz) is connected to XIN, then the device switches on the external clock. Else, XIN input is not considered. A higher frequency on XIN speeds up the programmer handshake.

#### 20.2.4 Programmer Handshaking

An handshake is defined for read and write operations. When the device is ready to start a new operation (RDY signal set), the programmer starts the handshake by clearing the NCMD signal. The handshaking is achieved once NCMD signal is high and RDY is high.

#### 20.2.4.1 Write Handshaking

For details on the write handshaking sequence, refer to Figure 20-2and Table 20-4.

## 23.8.20 AIC Fast Forcing Status Register

| Register Name: | AIC_FFSR  |

|----------------|-----------|

| Access Type:   | Read-only |

| 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PID31 | PID30 | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23 | PID22 | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15 | PID14 | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7  | PID6  | PID5  | PID4  | PID3  | PID2  | SYS   | _     |

## • SYS, PID2-PID31: Fast Forcing Status

0 = The Fast Forcing feature is disabled on the corresponding interrupt.

1 = The Fast Forcing feature is enabled on the corresponding interrupt.

# 24. Clock Generator

## 24.1 Overview

The Clock Generator is made up of 1 PLL, a Main Oscillator, as well as an RC Oscillator .

It provides the following clocks:

- SLCK, the Slow Clock, which is the only permanent clock within the system

- MAINCK is the output of the Main Oscillator

- PLLCK is the output of the Divider and PLL block

The Clock Generator User Interface is embedded within the Power Management Controller one and is described in Section 25.9. However, the Clock Generator registers are named CKGR\_.

## 24.2 Slow Clock RC Oscillator

The user has to take into account the possible drifts of the RC Oscillator. More details are given in the section "DC Characteristics" of the product datasheet.

## 24.3 Main Oscillator

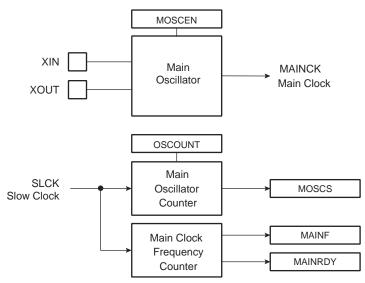

Figure 24-1 shows the Main Oscillator block diagram.

#### Figure 24-1. Main Oscillator Block Diagram

## 24.3.1 Main Oscillator Connections

The Clock Generator integrates a Main Oscillator that is designed for a 3 to 20 MHz fundamental crystal. The typical crystal connection is illustrated in Figure 24-2. For further details on the electrical characteristics of the Main Oscillator, see the section "DC Characteristics" of the product datasheet.

# 26.3 Product Dependencies

#### 26.3.1 I/O Lines

Depending on product integration, the Debug Unit pins may be multiplexed with PIO lines. In this case, the programmer must first configure the corresponding PIO Controller to enable I/O lines operations of the Debug Unit.

#### 26.3.2 Power Management

Depending on product integration, the Debug Unit clock may be controllable through the Power Management Controller. In this case, the programmer must first configure the PMC to enable the Debug Unit clock. Usually, the peripheral identifier used for this purpose is 1.

## 26.3.3 Interrupt Source

Depending on product integration, the Debug Unit interrupt line is connected to one of the interrupt sources of the Advanced Interrupt Controller. Interrupt handling requires programming of the AIC before configuring the Debug Unit. Usually, the Debug Unit interrupt line connects to the interrupt source 1 of the AIC, which may be shared with the real-time clock, the system timer interrupt lines and other system peripheral interrupts, as shown in Figure 26-1. This sharing requires the programmer to determine the source of the interrupt when the source 1 is triggered.

## 26.4 UART Operations

The Debug Unit operates as a UART, (asynchronous mode only) and supports only 8-bit character handling (with parity). It has no clock pin.

The Debug Unit's UART is made up of a receiver and a transmitter that operate independently, and a common baud rate generator. Receiver timeout and transmitter time guard are not implemented. However, all the implemented features are compatible with those of a standard USART.

#### 26.4.1 Baud Rate Generator

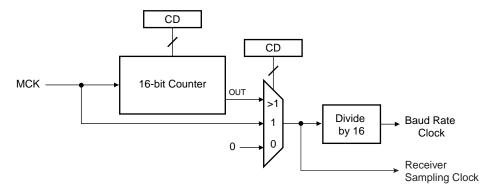

The baud rate generator provides the bit period clock named baud rate clock to both the receiver and the transmitter.

The baud rate clock is the master clock divided by 16 times the value (CD) written in DBGU\_BRGR (Baud Rate Generator Register). If DBGU\_BRGR is set to 0, the baud rate clock is disabled and the Debug Unit's UART remains inactive. The maximum allowable baud rate is Master Clock divided by 16. The minimum allowable baud rate is Master Clock divided by 16. The minimum allowable baud rate is Master Clock divided by 16 x 65536).

Baud Rate =

$$\frac{MCK}{16 \times CD}$$

#### Figure 26-3. Baud Rate Generator

## 26.5.6 Debug Unit Status Register

| Name:        | DBGU_S  | SR   |        |        |    |         |       |

|--------------|---------|------|--------|--------|----|---------|-------|

| Access Type: | Read-on | lly  |        |        |    |         |       |

| 31           | 30      | 29   | 28     | 27     | 26 | 25      | 24    |

| COMMRX       | COMMTX  | _    | -      | -      | -  | -       | -     |

| 23           | 22      | 21   | 20     | 19     | 18 | 17      | 16    |

| -            | Ι       | _    | -      | —      | -  | -       | —     |

| 15           | 14      | 13   | 12     | 11     | 10 | 9       | 8     |

| -            | Ι       | _    | RXBUFF | TXBUFE | -  | TXEMPTY | —     |

| 7            | 6       | 5    | 4      | 3      | 2  | 1       | 0     |

| PARE         | FRAME   | OVRE | ENDTX  | ENDRX  | _  | TXRDY   | RXRDY |

## • RXRDY: Receiver Ready

0 = No character has been received since the last read of the DBGU\_RHR or the receiver is disabled.

1 = At least one complete character has been received, transferred to DBGU\_RHR and not yet read.

## • TXRDY: Transmitter Ready

0 = A character has been written to DBGU\_THR and not yet transferred to the Shift Register, or the transmitter is disabled.

1 = There is no character written to DBGU\_THR not yet transferred to the Shift Register.

#### • ENDRX: End of Receiver Transfer

0 = The End of Transfer signal from the receiver Peripheral Data Controller channel is inactive.

1 = The End of Transfer signal from the receiver Peripheral Data Controller channel is active.

#### • ENDTX: End of Transmitter Transfer

0 = The End of Transfer signal from the transmitter Peripheral Data Controller channel is inactive.

1 = The End of Transfer signal from the transmitter Peripheral Data Controller channel is active.

#### OVRE: Overrun Error

0 = No overrun error has occurred since the last RSTSTA.

1 = At least one overrun error has occurred since the last RSTSTA.

#### • FRAME: Framing Error

- 0 = No framing error has occurred since the last RSTSTA.

- 1 = At least one framing error has occurred since the last RSTSTA.

#### • PARE: Parity Error

- 0 = No parity error has occurred since the last RSTSTA.

- 1 = At least one parity error has occurred since the last RSTSTA.

#### • TXEMPTY: Transmitter Empty

0 = There are characters in DBGU\_THR, or characters being processed by the transmitter, or the transmitter is disabled.

1 = There are no characters in DBGU\_THR and there are no characters being processed by the transmitter.

#### TXBUFE: Transmission Buffer Empty

#### 29.5.4 Master Receiver Mode

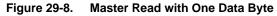

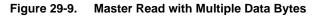

The read sequence begins by setting the START bit. After the start condition has been sent, the master sends a 7-bit slave address to notify the slave device. The bit following the slave address indicates the transfer direction, 1 in this case (MREAD = 1 in TWI\_MMR). During the acknowledge clock pulse (9th pulse), the master releases the data line (HIGH), enabling the slave to pull it down in order to generate the acknowledge. The master polls the data line during this clock pulse and sets the **NACK** bit in the status register if the slave does not acknowledge the byte.

If an acknowledge is received, the master is then ready to receive data from the slave. After data has been received, the master sends an acknowledge condition to notify the slave that the data has been received except for the last data, after the stop condition. See Figure 29-9. When the RXRDY bit is set in the status register, a character has been received in the receive-holding register (TWI\_RHR). The RXRDY bit is reset when reading the TWI\_RHR.

When a single data byte read is performed, with or without internal address (IADR), the START and STOP bits must be set at the same time. See Figure 29-8. When a multiple data byte read is performed, with or without internal address (IADR), the STOP bit must be set after the next-to-last data received. See Figure 29-9. For Internal Address usage see Section 29.5.5.

#### • PARE: Parity Error

0: No parity error has been detected since the last RSTSTA.

1: At least one parity error has been detected since the last RSTSTA.

#### • TIMEOUT: Receiver Time-out

0: There has not been a time-out since the last Start Time-out command (STTTO in US\_CR) or the Time-out Register is 0.

1: There has been a time-out since the last Start Time-out command (STTTO in US\_CR).

#### • TXEMPTY: Transmitter Empty

0: There are characters in either US\_THR or the Transmit Shift Register, or the transmitter is disabled.

1: There are no characters in US\_THR, nor in the Transmit Shift Register.

#### • ITERATION: Max number of Repetitions Reached

0: Maximum number of repetitions has not been reached since the last RSIT.

1: Maximum number of repetitions has been reached since the last RSIT.

#### • TXBUFE: Transmission Buffer Empty

0: The signal Buffer Empty from the Transmit PDC channel is inactive.

1: The signal Buffer Empty from the Transmit PDC channel is active.

#### • RXBUFF: Reception Buffer Full

0: The signal Buffer Full from the Receive PDC channel is inactive.

1: The signal Buffer Full from the Receive PDC channel is active.

#### NACK: Non Acknowledge

0: No Non Acknowledge has not been detected since the last RSTNACK.

1: At least one Non Acknowledge has been detected since the last RSTNACK.

## • RIIC: Ring Indicator Input Change Flag

0: No input change has been detected on the RI pin since the last read of US\_CSR.

1: At least one input change has been detected on the RI pin since the last read of US\_CSR.

## DSRIC: Data Set Ready Input Change Flag

0: No input change has been detected on the DSR pin since the last read of US\_CSR.

1: At least one input change has been detected on the DSR pin since the last read of US\_CSR.

## • DCDIC: Data Carrier Detect Input Change Flag

0: No input change has been detected on the DCD pin since the last read of US\_CSR.

1: At least one input change has been detected on the DCD pin since the last read of US\_CSR.

## • CTSIC: Clear to Send Input Change Flag

0: No input change has been detected on the CTS pin since the last read of US\_CSR.

1: At least one input change has been detected on the CTS pin since the last read of US\_CSR.

## 31.8.2 SSC Clock Mode Register

| Name:<br>Access Type: | SSC_CM<br>Read-wr |    |    |    |    |    |    |

|-----------------------|-------------------|----|----|----|----|----|----|

| 31                    | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

| -                     | _                 | _  | _  | _  | _  | _  | —  |

| 23                    | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

| -                     | _                 | _  | -  | -  | _  | _  | _  |

| 15                    | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

| -                     | _                 | —  | -  |    | D  | IV |    |

| 7                     | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                       |                   |    | D  | IV |    |    |    |

#### • DIV: Clock Divider

0: The Clock Divider is not active.

Any Other Value: The Divided Clock equals the Master Clock divided by 2 times DIV. The maximum bit rate is MCK/2. The minimum bit rate is  $MCK/2 \times 4095 = MCK/8190$ .

## • CP0: Compare 0 Interrupt Disable

0: No effect.

1: Disables the Compare 0 Interrupt.

#### • CP1: Compare 1 Interrupt Disable

0: No effect.

1: Disables the Compare 1 Interrupt.

## • TXSYN: Tx Sync Interrupt Enable

0: No effect.

1: Disables the Tx Sync Interrupt.

## • RXSYN: Rx Sync Interrupt Enable

0: No effect.

1: Disables the Rx Sync Interrupt.

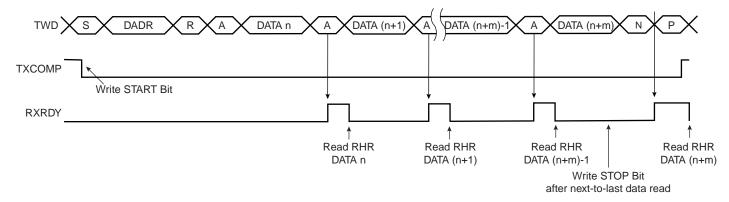

#### 32.5.4 Clock Control

The clock of each counter can be controlled in two different ways: it can be enabled/disabled and started/stopped. See Figure 32-4.

- The clock can be enabled or disabled by the user with the CLKEN and the CLKDIS commands in the Control Register. In Capture Mode it can be disabled by an RB load event if LDBDIS is set to 1 in TC\_CMR. In Waveform Mode, it can be disabled by an RC Compare event if CPCDIS is set to 1 in TC\_CMR. When disabled, the start or the stop actions have no effect: only a CLKEN command in the Control Register can re-enable the clock. When the clock is enabled, the CLKSTA bit is set in the Status Register.

- The clock can also be started or stopped: a trigger (software, synchro, external or compare) always starts the clock. The clock can be stopped by an RB load event in Capture Mode (LDBSTOP = 1 in TC\_CMR) or a RC compare event in Waveform Mode (CPCSTOP = 1 in TC\_CMR). The start and the stop commands have effect only if the clock is enabled.

#### Figure 32-4. Clock Control

## 32.5.5 TC Operating Modes

Each channel can independently operate in two different modes:

- Capture Mode provides measurement on signals.

- Waveform Mode provides wave generation.

The TC Operating Mode is programmed with the WAVE bit in the TC Channel Mode Register.

In Capture Mode, TIOA and TIOB are configured as inputs.

In Waveform Mode, TIOA is always configured to be an output and TIOB is an output if it is not selected to be the external trigger.

#### 32.5.6 Trigger

A trigger resets the counter and starts the counter clock. Three types of triggers are common to both modes, and a fourth external trigger is available to each mode.

The following triggers are common to both modes:

When the device firmware has polled this bit or has been interrupted by this signal, it must transfer data from the FIFO to microcontroller memory. The number of bytes received is available in RXBYTECNT field. Bank 1 FIFO values are read through UDP\_ FDRx register. Once a transfer is done, the device firmware must release Bank 1 to the USB device by clearing RX\_DATA\_BK1.

## • DIR: Transfer Direction (only available for control endpoints)

Read/Write

0 = Allows Data OUT transactions in the control data stage.

1 = Enables Data IN transactions in the control data stage.

Refer to Chapter 8.5.3 of the Universal Serial Bus Specification, Rev. 2.0 for more information on the control data stage.

This bit must be set before UDP\_CSRx/RXSETUP is cleared at the end of the setup stage. According to the request sent in the setup data packet, the data stage is either a device to host (DIR = 1) or host to device (DIR = 0) data transfer. It is not necessary to check this bit to reverse direction for the status stage.

## • EPTYPE[2:0]: Endpoint Type

Read/Write

| 000 | Control         |

|-----|-----------------|

| 001 | Isochronous OUT |

| 101 | Isochronous IN  |

| 010 | Bulk OUT        |

| 110 | Bulk IN         |

| 011 | Interrupt OUT   |

| 111 | Interrupt IN    |

## • DTGLE: Data Toggle

Read-only

0 = Identifies DATA0 packet.

1 = Identifies DATA1 packet.

Refer to Chapter 8 of the Universal Serial Bus Specification, Rev. 2.0 for more information on DATA0, DATA1 packet definitions.

## • EPEDS: Endpoint Enable Disable

Read:

0 = Endpoint disabled.

1 = Endpoint enabled.

Write:

0 = Disables endpoint.

```

1 = Enables endpoint.

```

Control endpoints are always enabled. Reading or writing this field has no effect on control endpoints.

Note: After reset, all endpoints are configured as control endpoints (zero).

## • RXBYTECNT[10:0]: Number of Bytes Available in the FIFO

Read-only

When the host sends a data packet to the device, the USB device stores the data in the FIFO and notifies the microcontroller. The microcontroller can load the data from the FIFO by reading RXBYTECENT bytes in the UDP\_FDRx register.

## 37.5.1 Network Control Register

| Register Name | EMAC_1  | EMAC_NCR   |     |    |       |        |    |  |  |  |  |  |

|---------------|---------|------------|-----|----|-------|--------|----|--|--|--|--|--|

| Access Type:  | Read-wr | Read-write |     |    |       |        |    |  |  |  |  |  |

| 31            | 30      | 29         | 28  | 27 | 26    | 25     | 24 |  |  |  |  |  |

| -             | -       | -          | -   | -  | —     | —      | -  |  |  |  |  |  |

| 23            | 22      | 21         | 20  | 19 | 18    | 17     | 16 |  |  |  |  |  |

| _             | _       | _          | _   | _  | _     | _      | _  |  |  |  |  |  |

| 15            | 14      | 13         | 12  | 11 | 10    | 9      | 8  |  |  |  |  |  |

| -             | —       | —          | —   | —  | THALT | TSTART | BP |  |  |  |  |  |

| 7             | 6       | 5          | 4   | 3  | 2     | 1      | 0  |  |  |  |  |  |

| WESTAT        | INCSTAT | CLRSTAT    | MPE | TE | RE    | LLB    | LB |  |  |  |  |  |

#### • LB: LoopBack

Asserts the loopback signal to the PHY.

#### • LLB: Loopback Local

Connects txd to rxd, tx\_en to rx\_dv, forces full duplex and drives  $rx_clk$  and  $tx_clk$  with pclk divided by 4. rx\_clk and  $tx_clk$  may glitch as the EMAC is switched into and out of internal loop back. It is important that receive and transmit circuits have already been disabled when making the switch into and out of internal loop back.

#### • RE: Receive Enable

When set, enables the EMAC to receive data. When reset, frame reception stops immediately and the receive FIFO is cleared. The receive queue pointer register is unaffected.

#### • TE: Transmit Enable

When set, enables the Ethernet transmitter to send data. When reset transmission, stops immediately, the transmit FIFO and control registers are cleared and the transmit queue pointer register resets to point to the start of the transmit descriptor list.

#### • MPE: Management Port Enable

Set to one to enable the management port. When zero, forces MDIO to high impedance state and MDC low.

#### • CLRSTAT: Clear Statistics Registers

This bit is write only. Writing a one clears the statistics registers.

#### • INCSTAT: Increment Statistics Registers

This bit is write only. Writing a one increments all the statistics registers by one for test purposes.

#### • WESTAT: Write Enable for Statistics Registers

Setting this bit to one makes the statistics registers writable for functional test purposes.

#### • BP: Back Pressure

If set in half duplex mode, forces collisions on all received frames.

#### • TSTART: Start Transmission

Writing one to this bit starts transmission.

#### • THALT: Transmit Halt

Writing one to this bit halts transmission as soon as any ongoing frame transmission ends.

## 37.5.5 Receive Buffer Queue Pointer Register

| Register Name: | EMAC_I  | RBQP |    |    |    |    |    |

|----------------|---------|------|----|----|----|----|----|

| Access Type:   | Read-wi | rite |    |    |    |    |    |

| 31             | 30      | 29   | 28 | 27 | 26 | 25 | 24 |

|                |         |      | AD | DR |    |    |    |

| 23             | 22      | 21   | 20 | 19 | 18 | 17 | 16 |

|                |         |      | AD | DR |    |    |    |

| 15             | 14      | 13   | 12 | 11 | 10 | 9  | 8  |

|                |         |      | AD | DR |    |    |    |

| 7              | 6       | 5    | 4  | 3  | 2  | 1  | 0  |

| ADDR           |         |      |    |    |    | _  | -  |

This register points to the entry in the receive buffer queue (descriptor list) currently being used. It is written with the start location of the receive buffer descriptor list. The lower order bits increment as buffers are used up and wrap to their original values after either 1024 buffers or when the wrap bit of the entry is set.

Reading this register returns the location of the descriptor currently being accessed. This value increments as buffers are used. Software should not use this register for determining where to remove received frames from the queue as it constantly changes as new frames are received. Software should instead work its way through the buffer descriptor queue checking the used bits.

Receive buffer writes also comprise bursts of two words and, as with transmit buffer reads, it is recommended that bit 2 is always written with zero to prevent a burst crossing a 1K boundary, in violation of section 3.6 of the AMBA specification.

#### • ADDR: Receive buffer queue pointer address

Written with the address of the start of the receive queue, reads as a pointer to the current buffer being used.

#### 41.3.9 Two-wire Interface (TWI)

#### 41.3.9.1 TWI: Clock Divider

The value of CLDIV x 2<sup>CKDIV</sup> must be less than or equal to 8191, the value of CHDIV x 2<sup>CKDIV</sup> must be less than or equal to 8191.

Problem Fix/Workaround

None.

#### 41.3.9.2 TWI: Disabling Does not Operate Correctly

Any transfer in progress is immediately frozen if the Control Register (TWI\_CR) is written with the bit MSDIS at 1. Furthermore, the status bits TXCOMP and TXRDY in the Status Register (TWI\_SR) are not reset. Problem Fix/Workaround

The user must wait for the end of transfer before disabling the TWI. In addition, the interrupts must be disabled before disabling the TWI.

#### 41.3.9.3 TWI: NACK Status Bit Lost

During a master frame, if TWI\_SR is read between the Non Acknowledge condition detection and the TXCOMP bit rising in the TWI\_SR, the NACK bit is not set.

Problem Fix/Workaround

The user must wait for the TXCOMP status bit by interrupt and must not read the TWI\_SR as long as transmission is not completed.

TXCOMP and NACK fields are set simultaneously and the NACK field is reset after the read of the TWI\_SR.

#### 41.3.9.4 TWI: Possible Receive Holding Register Corruption

When loading the TWI\_RHR, the transfer direction is ignored. The last data byte received in the TWI\_RHR is corrupted at the end of the first subsequent transmit data byte. Neither RXRDY nor OVERRUN status bits are set if this occurs. Problem Fix/Workaround

The user must be sure that received data is read before transmitting any new data.

#### 41.3.9.5 TWI: Software Reset

when a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

Problem Fix/Workaround

None.

#### 41.3.10 Universal Synchronous Asynchronous Receiver Transmitter (USART)

#### 41.3.10.1 USART: CTS in Hardware Handshaking

When Hardware Handshaking is used and if CTS goes low near the end of the start bit, a character can be lost.

CTS must not go high during a time slot occurring between 2 Master Clock periods before and 16 Master Clock periods after the rising edge of the start bit.

Problem Fix/Workaround

None.

#### 41.3.10.2 USART: Hardware Handshaking – Two Characters Sent

If CTS switches from 0 to 1 during the TX of a character and if the holding register (US\_THR) is not empty, the content of US\_THR will also be transmitted.

Problem Fix/Workaround

Don't use the PDC in transmit mode and do not fill US\_THR before TXEMPTY is set at 1.

#### 41.3.10.3 USART: RXBRK Flag Error in Asynchronous Mode

In receiver mode, when there are two consecutive characters (without time guard in between), RXBRK is not taken into account. As a result, the RXBRK flag is not enabled correctly and the frame error flag is set Problem Fix/Workaround

Constraints on the transmitter device connected to the SAM7X USART receiver side:

The transmitter may use the timeguard feature or send two STOP conditions. Only one STOP condition is taken into account by the receiver state machine. After this STOP condition, as there is no valid data, the receiver state machine will go in idle mode and enable the RXBRK flag.

#### 41.3.10.4 USART: DCD is Active High instead of Low.

The DCD signal is active at High level in the USART Modem Mode .

DCD should be active at Low level.

Problem Fix/Workaround

Add an inverter.

|                   | 9.6                                                                                                                                                                                  | Periodic Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                   | 9.7                                                                                                                                                                                  | Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

|                   | 9.8                                                                                                                                                                                  | Real-time Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

|                   | 9.9                                                                                                                                                                                  | PIO Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

|                   | 9.10                                                                                                                                                                                 | Voltage Regulator Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                 |

| 10.               | Perio                                                                                                                                                                                | herals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30                                                                 |

|                   | 10.1                                                                                                                                                                                 | User Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

|                   | 10.2                                                                                                                                                                                 | Peripheral Identifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

|                   | 10.3                                                                                                                                                                                 | Peripheral Multiplexing on PIO Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

|                   | 10.4                                                                                                                                                                                 | PIO Controller A Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

|                   | 10.5                                                                                                                                                                                 | PIO Controller B Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

|                   | 10.6                                                                                                                                                                                 | Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

|                   | 10.7                                                                                                                                                                                 | Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

|                   | 10.8                                                                                                                                                                                 | Two-wire Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

|                   | 10.9                                                                                                                                                                                 | USART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                    |

|                   | 10.10                                                                                                                                                                                | Serial Synchronous Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |

|                   |                                                                                                                                                                                      | Timer Counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

|                   |                                                                                                                                                                                      | Pulse Width Modulation Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

|                   |                                                                                                                                                                                      | USB Device Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

|                   |                                                                                                                                                                                      | CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

|                   |                                                                                                                                                                                      | Analog-to-Digital Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

|                   |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 11.               | ARM                                                                                                                                                                                  | 7TDMI Processor Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

|                   | 11.1                                                                                                                                                                                 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

|                   | 11.2                                                                                                                                                                                 | ARM7TDMI Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                                                                 |

|                   |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 12.               |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |