#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detans                     |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | ARM7®                                                                         |

| Core Size                  | 16/32-Bit                                                                     |

| Speed                      | 55MHz                                                                         |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 62                                                                            |

| Program Memory Size        | 256KB (256K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 64K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                                 |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-LQFP                                                                      |

| Supplier Device Package    | 100-LQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x256-au-999 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

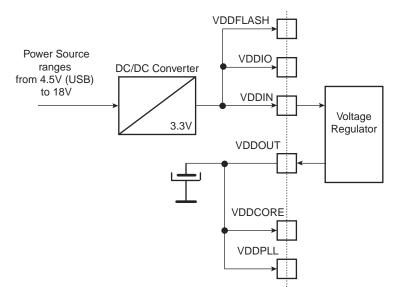

Figure 5-1. 3.3V System Single Power Supply Schematic

| User and<br>System Mode | Supervisor<br>Mode | Abort Mode | Undefined<br>Mode | Interrupt<br>Mode | Fast Interrupt<br>Mode |

|-------------------------|--------------------|------------|-------------------|-------------------|------------------------|

| R0                      | R0                 | R0         | R0                | R0                | R0                     |

| R1                      | R1                 | R1         | R1                | R1                | R1                     |

| R2                      | R2                 | R2         | R2                | R2                | R2                     |

| R3                      | R3                 | R3         | R3                | R3                | R3                     |

| R4                      | R4                 | R4         | R4                | R4                | R4                     |

| R5                      | R5                 | R5         | R5                | R5                | R5                     |

| R6                      | R6                 | R6         | R6                | R6                | R6                     |

| R7                      | R7                 | R7         | R7                | R7                | R7                     |

| R8                      | R8                 | R8         | R8                | R8                | R8_FIQ                 |

| R9                      | R9                 | R9         | R9                | R9                | R9_FIQ                 |

| R10                     | R10                | R10        | R10               | R10               | R10_FIQ                |

| R11                     | R11                | R11        | R11               | R11               | R11_FIQ                |

| R12                     | R12                | R12        | R12               | R12               | R12_FIQ                |

| R13                     | R13_SVC            | R13_ABORT  | R13_UNDEF         | R13_IRQ           | R13_FIQ                |

| R14                     | R14_SVC            | R14_ABORT  | R14_UNDEF         | R14_IRQ           | R14_FIQ                |

| PC                      | PC                 | PC         | PC                | PC                | PC                     |

Table 11-1. ARM7TDMI ARM Modes and Registers Layout

| CPSR | CPSR     | CPSR       | CPSR       | CPSR     | CPSR     |

|------|----------|------------|------------|----------|----------|

|      | SPSR_SVC | SPSR_ABORT | SPSR_UNDEF | SPSR_IRQ | SPSR_FIQ |

Mode-specific banked registers

#### 11.2.4.1 Modes and Exception Handling

All exceptions have banked registers for R14 and R13.

After an exception, R14 holds the return address for exception processing. This address is used to return after the exception is processed, as well as to address the instruction that caused the exception.

R13 is banked across exception modes to provide each exception handler with a private stack pointer.

The fast interrupt mode also banks registers 8 to 12 so that interrupt processing can begin without having to save these registers.

A seventh processing mode, System Mode, does not have any banked registers. It uses the User Mode registers. System Mode runs tasks that require a privileged processor mode and allows them to invoke all classes of exceptions.

#### 11.2.4.2 Status Registers

All other processor states are held in status registers. The current operating processor status is in the Current Program Status Register (CPSR). The CPSR holds:

- four ALU flags (Negative, Zero, Carry, and Overflow)

- two interrupt disable bits (one for each type of interrupt)

- one bit to indicate ARM or Thumb execution

- five bits to encode the current processor mode

All five exception modes also have a Saved Program Status Register (SPSR) that holds the CPSR of the task immediately preceding the exception.

### 19.3.3 MC Flash Status Register

| Register Name<br>Access Type: | : MC_FSF<br>Read-on |              |              |              |              |              |              |

|-------------------------------|---------------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Offset: (EFC0)                | 0x68                |              |              |              |              |              |              |

| Offset: (EFC1)                | 0x78                |              |              |              |              |              |              |

| 31                            | 30                  | 29           | 28           | 27           | 26           | 25           | 24           |

| LOCKS15                       | LOCKS14             | LOCKS13      | LOCKS12      | LOCKS11      | LOCKS10      | LOCKS9       | LOCKS8       |

| 23<br>LOCKS7                  | 22<br>LOCKS6        | 21<br>LOCKS5 | 20<br>LOCKS4 | 19<br>LOCKS3 | 18<br>LOCKS2 | 17<br>LOCKS1 | 16<br>LOCKS0 |

| LUCKS7                        | LUCKSU              | LUCKSS       | LOCK34       | LOCK33       | LUCK32       | LUCKST       | LUCKSU       |

| 15                            | 14                  | 13           | 12           | 11           | 10           | 9            | 8            |

| _                             | _                   | —            | —            | _            | GPNVM2       | GPNVM1       | GPNVM0       |

| 7                             | 6                   | 5            | 4            | 3            | 2            | 1            | 0            |

| _                             | _                   | —            | SECURITY     | PROGE        | LOCKE        | -            | FRDY         |

### • FRDY: Flash Ready Status

0: The EFC is busy and the application must wait before running a new command.

1: The EFC is ready to run a new command.

### • LOCKE: Lock Error Status

0: No programming of at least one locked lock region has happened since the last read of MC\_FSR.

1: Programming of at least one locked lock region has happened since the last read of MC\_FSR.

### • PROGE: Programming Error Status

0: No invalid commands and no bad keywords were written in the Flash Command Register MC\_FCR.

1: An invalid command and/or a bad keyword was/were written in the Flash Command Register MC\_FCR.

### • SECURITY: Security Bit Status (Does not apply to EFC1 on the AT91SAM7X512.)

0: The security bit is inactive.

1: The security bit is active.

### • GPNVMx: General-purpose NVM Bit Status (Does not apply to EFC1 on the AT91SAM7X512.)

0: The corresponding general-purpose NVM bit is inactive.

1: The corresponding general-purpose NVM bit is active.

### • EFC LOCKSx: Lock Region x Lock Status

0: The corresponding lock region is not locked.

1: The corresponding lock region is locked.

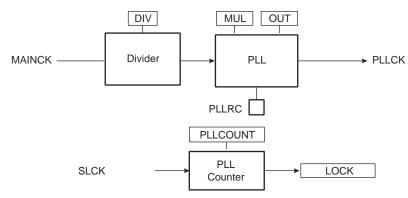

### 24.4 Divider and PLL Block

The PLL embeds an input divider to increase the accuracy of the resulting clock signals. However, the user must respect the PLL minimum input frequency when programming the divider.

Figure 24-3 shows the block diagram of the divider and PLL block.

### Figure 24-3. Divider and PLL Block Diagram

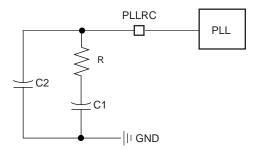

### 24.4.1 PLL Filter

The PLL requires connection to an external second-order filter through the PLLRC pin. Figure 24-4 shows a schematic of these filters.

### Figure 24-4. PLL Capacitors and Resistors

Values of R, C1 and C2 to be connected to the PLLRC pin must be calculated as a function of the PLL input frequency, the PLL output frequency and the phase margin. A trade-off has to be found between output signal overshoot and startup time.

### 24.4.2 Divider and Phase Lock Loop Programming

The divider can be set between 1 and 255 in steps of 1. When a divider field (DIV) is set to 0, the output of the corresponding divider and the PLL output is a continuous signal at level 0. On reset, each DIV field is set to 0, thus the corresponding PLL input clock is set to 0.

The PLL allows multiplication of the divider's outputs. The PLL clock signal has a frequency that depends on the respective source signal frequency and on the parameters DIV and MUL. The factor applied to the source signal frequency is (MUL + 1)/DIV. When MUL is written to 0, the corresponding PLL is disabled and its power consumption is saved. Re-enabling the PLL can be performed by writing a value higher than 0 in the MUL field.

Whenever the PLL is re-enabled or one of its parameters is changed, the LOCK bit in PMC\_SR is automatically cleared. The values written in the PLLCOUNT field in CKGR\_PLLR are loaded in the PLL counter. The PLL counter then decrements at the speed of the Slow Clock until it reaches 0. At this time, the LOCK bit is set in PMC\_SR and can trigger an interrupt to the processor. The user has to load the number of Slow Clock cycles required to cover the PLL transient

### 27.6.17 PIO Controller Interrupt Status Register

| Name:        | PIO_ISR |     |     |     |     |     |     |

|--------------|---------|-----|-----|-----|-----|-----|-----|

| Access Type: | Read-on | ly  |     |     |     |     |     |

| 31           | 30      | 29  | 28  | 27  | 26  | 25  | 24  |

| P31          | P30     | P29 | P28 | P27 | P26 | P25 | P24 |

| 23           | 22      | 21  | 20  | 19  | 18  | 17  | 16  |

| P23          | P22     | P21 | P20 | P19 | P18 | P17 | P16 |

| 15           | 14      | 13  | 12  | 11  | 10  | 9   | 8   |

| P15          | P14     | P13 | P12 | P11 | P10 | P9  | P8  |

| 7            | 6       | 5   | 4   | 3   | 2   | 1   | 0   |

| P7           | P6      | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: Input Change Interrupt Status

0 = No Input Change has been detected on the I/O line since PIO\_ISR was last read or since reset.

1 = At least one Input Change has been detected on the I/O line since PIO\_ISR was last read or since reset.

### 27.6.18 PIO Multi-driver Enable Register

| ame:        | PIO_MDE    | R   |     |     |     |     |     |

|-------------|------------|-----|-----|-----|-----|-----|-----|

| ccess Type: | Write-only |     |     |     |     |     |     |

| 31          | 30         | 29  | 28  | 27  | 26  | 25  | 24  |

| P31         | P30        | P29 | P28 | P27 | P26 | P25 | P24 |

| 23          | 22         | 21  | 20  | 19  | 18  | 17  | 16  |

| P23         | P22        | P21 | P20 | P19 | P18 | P17 | P16 |

| 15          | 14         | 13  | 12  | 11  | 10  | 9   | 8   |

| P15         | P14        | P13 | P12 | P11 | P10 | P9  | P8  |

| 7           | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

| P7          | P6         | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: Multi Drive Enable.

0 = No effect.

1 = Enables Multi Drive on the I/O line.

### 27.6.29 PIO Output Write Status Register

| Name:<br>Access Type: | PIO_OW<br>Read-on |     |     |     |     |     |     |

|-----------------------|-------------------|-----|-----|-----|-----|-----|-----|

| 31                    | 30                | 29  | 28  | 27  | 26  | 25  | 24  |

| P31                   | P30               | P29 | P28 | P27 | P26 | P25 | P24 |

| 23                    | 22                | 21  | 20  | 19  | 18  | 17  | 16  |

| P23                   | P22               | P21 | P20 | P19 | P18 | P17 | P16 |

| 15                    | 14                | 13  | 12  | 11  | 10  | 9   | 8   |

| P15                   | P14               | P13 | P12 | P11 | P10 | P9  | P8  |

| 7                     | 6                 | 5   | 4   | 3   | 2   | 1   | 0   |

| P7                    | P6                | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: Output Write Status.

0 = Writing PIO\_ODSR does not affect the I/O line.

1 = Writing PIO\_ODSR affects the I/O line.

The Variable Peripheral Selection allows buffer transfers with multiple peripherals without reprogramming the Mode Register. Data written in SPI\_TDR is 32 bits wide and defines the real data to be transmitted and the peripheral it is destined to. Using the PDC in this mode requires 32-bit wide buffers, with the data in the LSBs and the PCS and LASTXFER fields in the MSBs, however the SPI still controls the number of bits (8 to16) to be transferred through MISO and MOSI lines with the chip select configuration registers. This is not the optimal means in term of memory size for the buffers, but it provides a very effective means to exchange data with several peripherals without any intervention of the processor.

### 28.6.3.6 Peripheral Chip Select Decoding

The user can program the SPI to operate with up to 15 peripherals by decoding the four Chip Select lines, NPCS0 to NPCS3 with an external logic. This can be enabled by writing the PCSDEC bit at 1 in the Mode Register (SPI\_MR).

When operating without decoding, the SPI makes sure that in any case only one chip select line is activated, i.e. driven low at a time. If two bits are defined low in a PCS field, only the lowest numbered chip select is driven low.

When operating with decoding, the SPI directly outputs the value defined by the PCS field of either the Mode Register or the Transmit Data Register (depending on PS).

As the SPI sets a default value of 0xF on the chip select lines (i.e. all chip select lines at 1) when not processing any transfer, only 15 peripherals can be decoded.

The SPI has only four Chip Select Registers, not 15. As a result, when decoding is activated, each chip select defines the characteristics of up to four peripherals. As an example, SPI\_CRS0 defines the characteristics of the externally decoded peripherals 0 to 3, corresponding to the PCS values 0x0 to 0x3. Thus, the user has to make sure to connect compatible peripherals on the decoded chip select lines 0 to 3, 4 to 7, 8 to 11 and 12 to 14.

### 28.6.3.7 Peripheral Deselection

When operating normally, as soon as the transfer of the last data written in SPI\_TDR is completed, the NPCS lines all rise. This might lead to runtime error if the processor is too long in responding to an interrupt, and thus might lead to difficulties for interfacing with some serial peripherals requiring the chip select line to remain active during a full set of transfers.

To facilitate interfacing with such devices, the Chip Select Register can be programmed with the CSAAT bit (Chip Select Active After Transfer) at 1. This allows the chip select lines to remain in their current state (low = active) until transfer to another peripheral is required.

Figure 28-8 shows different peripheral deselection cases and the effect of the CSAAT bit.

## 28.7 Serial Peripheral Interface (SPI) User Interface

| Offset          | Register                   | Name     | Access     | Reset      |

|-----------------|----------------------------|----------|------------|------------|

| 0x00            | Control Register           | SPI_CR   | Write-only |            |

| 0x04            | Mode Register              | SPI_MR   | Read-write | 0x0        |

| 0x08            | Receive Data Register      | SPI_RDR  | Read-only  | 0x0        |

| 0x0C            | Transmit Data Register     | SPI_TDR  | Write-only |            |

| 0x10            | Status Register            | SPI_SR   | Read-only  | 0x000000F0 |

| 0x14            | Interrupt Enable Register  | SPI_IER  | Write-only |            |

| 0x18            | Interrupt Disable Register | SPI_IDR  | Write-only |            |

| 0x1C            | Interrupt Mask Register    | SPI_IMR  | Read-only  | 0x0        |

| 0x20 - 0x2C     | Reserved                   |          |            |            |

| 0x30            | Chip Select Register 0     | SPI_CSR0 | Read-write | 0x0        |

| 0x34            | Chip Select Register 1     | SPI_CSR1 | Read-write | 0x0        |

| 0x38            | Chip Select Register 2     | SPI_CSR2 | Read-write | 0x0        |

| 0x3C            | Chip Select Register 3     | SPI_CSR3 | Read-write | 0x0        |

| 0x004C - 0x00F8 | Reserved                   | _        | -          | _          |

| 0x004C - 0x00FC | Reserved                   | _        | -          | _          |

| 0x100 - 0x124   | Reserved for the PDC       |          |            |            |

### Table 28-3. Register Mapping

### 28.7.3 SPI Receive Data Register

| Name:        | SPI_RDI |    |    |    |    |    |    |

|--------------|---------|----|----|----|----|----|----|

| Access Type: | Read-on | ly |    |    |    |    |    |

| 31           | 30      | 29 | 28 | 27 | 26 | 25 | 24 |

| -            | -       | _  | -  | _  | -  | _  | -  |

| 23           | 22      | 21 | 20 | 19 | 18 | 17 | 16 |

| _            | _       | _  | -  |    | PC | CS |    |

| 15           | 14      | 13 | 12 | 11 | 10 | 9  | 8  |

|              |         |    | F  | RD |    |    |    |

| 7            | 6       | 5  | 4  | 3  | 2  | 1  | 0  |

|              |         |    | F  | RD |    |    |    |

### • RD: Receive Data

Data received by the SPI Interface is stored in this register right-justified. Unused bits read zero.

### • PCS: Peripheral Chip Select

In Master Mode only, these bits indicate the value on the NPCS pins at the end of a transfer. Otherwise, these bits read zero.

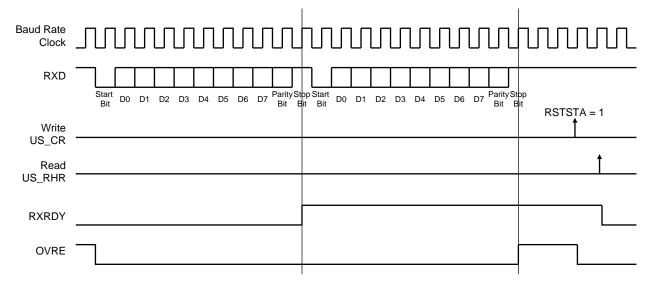

### Figure 30-11. Receiver Status

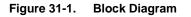

# 31. Synchronous Serial Controller (SSC)

### 31.1 Overview

The Atmel Synchronous Serial Controller (SSC) provides a synchronous communication link with external devices. It supports many serial synchronous communication protocols generally used in audio and telecom applications such as I2S, Short Frame Sync, Long Frame Sync, etc.

The SSC contains an independent receiver and transmitter and a common clock divider. The receiver and the transmitter each interface with three signals: the TD/RD signal for data, the TK/RK signal for the clock and the TF/RF signal for the Frame Sync. The transfers can be programmed to start automatically or on different events detected on the Frame Sync signal.

The SSC's high-level of programmability and its two dedicated PDC channels of up to 32 bits permit a continuous high bit rate data transfer without processor intervention.

Featuring connection to two PDC channels, the SSC permits interfacing with low processor overhead to the following:

- CODEC's in master or slave mode

- DAC through dedicated serial interface, particularly I2S

- Magnetic card reader

### 31.2 Block Diagram

### • ETRGEDG: External Trigger Edge Selection

| ETRGEDG |   | Edge         |

|---------|---|--------------|

| 0       | 0 | none         |

| 0       | 1 | rising edge  |

| 1       | 0 | falling edge |

| 1       | 1 | each edge    |

### ABETRG: TIOA or TIOB External Trigger Selection

0 = TIOB is used as an external trigger.

1 = TIOA is used as an external trigger.

### • CPCTRG: RC Compare Trigger Enable

0 = RC Compare has no effect on the counter and its clock.

1 = RC Compare resets the counter and starts the counter clock.

### • WAVE

0 = Capture Mode is enabled.

1 = Capture Mode is disabled (Waveform Mode is enabled).

### • LDRA: RA Loading Selection

| LD | RA | Edge                 |

|----|----|----------------------|

| 0  | 0  | none                 |

| 0  | 1  | rising edge of TIOA  |

| 1  | 0  | falling edge of TIOA |

| 1  | 1  | each edge of TIOA    |

### • LDRB: RB Loading Selection

| LDRB |   | Edge                 |

|------|---|----------------------|

| 0    | 0 | none                 |

| 0    | 1 | rising edge of TIOA  |

| 1    | 0 | falling edge of TIOA |

| 1    | 1 | each edge of TIOA    |

### 33.6.3 PWM Disable Register

| Register Name: | PWM_D    | IS |    |       |       |       |       |

|----------------|----------|----|----|-------|-------|-------|-------|

| Access Type:   | Write-on | ly |    |       |       |       |       |

| 31             | 30       | 29 | 28 | 27    | 26    | 25    | 24    |

| -              | _        | _  | -  | -     | -     | -     | -     |

| 23             | 22       | 21 | 20 | 19    | 18    | 17    | 16    |

| _              | _        | _  | -  | _     | _     | _     | -     |

| 15             | 14       | 13 | 12 | 11    | 10    | 9     | 8     |

| -              | _        | _  | -  | —     | -     | -     | -     |

| 7              | 6        | 5  | 4  | 3     | 2     | 1     | 0     |

| -              | _        | _  | -  | CHID3 | CHID2 | CHID1 | CHID0 |

### • CHIDx: Channel ID

0 = No effect.

1 = Disable PWM output for channel x.

### 33.6.6 PWM Interrupt Disable Register

| Register Name: | PWM_IC   | DR |    |       |       |       |       |

|----------------|----------|----|----|-------|-------|-------|-------|

| Access Type:   | Write-on | ly |    |       |       |       |       |

| 31             | 30       | 29 | 28 | 27    | 26    | 25    | 24    |

| -              | _        | -  | -  | -     | -     | -     | -     |

| 23             | 22       | 21 | 20 | 19    | 18    | 17    | 16    |

| -              | _        | _  | _  | _     | -     | _     | _     |

| 15             | 14       | 13 | 12 | 11    | 10    | 9     | 8     |

| -              | —        | —  | _  | -     | -     | -     | -     |

| 7              | 6        | 5  | 4  | 3     | 2     | 1     | 0     |

| _              | _        | _  | -  | CHID3 | CHID2 | CHID1 | CHID0 |

### • CHIDx: Channel ID.

0 = No effect.

1 = Disable interrupt for PWM channel x.

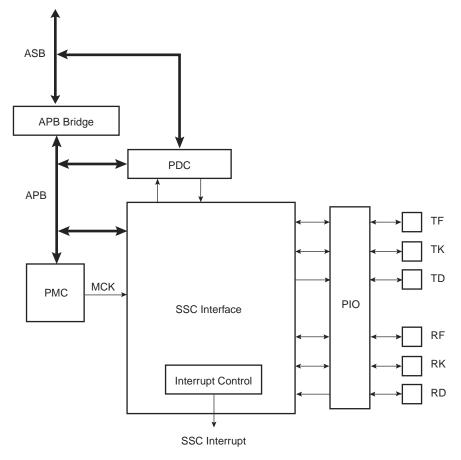

### 35.5.4 Conversion Results

When a conversion is completed, the resulting 10-bit digital value is stored in the Channel Data Register (ADC\_CDR) of the current channel and in the ADC Last Converted Data Register (ADC\_LCDR).

The channel EOC bit in the Status Register (ADC\_SR) is set and the DRDY is set. In the case of a connected PDC channel, DRDY rising triggers a data transfer request. In any case, either EOC and DRDY can trigger an interrupt.

Reading one of the ADC\_CDR registers clears the corresponding EOC bit. Reading ADC\_LCDR clears the DRDY bit and the EOC bit corresponding to the last converted channel.

#### Figure 35-2. EOCx and DRDY Flag Behavior

### 36.8.18 CAN Message Data High Register

| Name:<br>Access Type: | CAN_M<br>Read-w |    |    |    |    |    |    |

|-----------------------|-----------------|----|----|----|----|----|----|

| 31                    | 30              | 29 | 28 | 27 | 26 | 25 | 24 |

|                       |                 |    | M  | DH |    |    |    |

| 23                    | 22              | 21 | 20 | 19 | 18 | 17 | 16 |

|                       |                 |    | M  | DH |    |    |    |

| 15                    | 14              | 13 | 12 | 11 | 10 | 9  | 8  |

|                       |                 |    | M  | DH |    |    |    |

| 7                     | 6               | 5  | 4  | 3  | 2  | 1  | 0  |

|                       |                 |    | M  | DH |    |    |    |

### • MDH: Message Data High Value

When MRDY field is set in the CAN\_MSRx register, the upper 32 bits of a received message are read or written by the software application. Otherwise, the MDH value is locked by the CAN controller to send/receive a new message.

In Receive with overwrite, the CAN controller may modify MDH value while the software application reads MDH and MDL registers. To check that MDH and MDL do not belong to different messages, the application has to check the MMI field in the CAN\_MSRx register. In this mode, the software application must re-read CAN\_MDH and CAN\_MDL, while the MMI bit in the CAN\_MSRx register is set.

Bytes are received/sent on the bus in the following order:

- 1. CAN\_MDL[7:0]

- 2. CAN\_MDL[15:8]

- 3. CAN\_MDL[23:16]

- 4. CAN\_MDL[31:24]

- 5. CAN\_MDH[7:0]

- 6. CAN\_MDH[15:8]

- 7. CAN\_MDH[23:16]

- 8. CAN\_MDH[31:24]

### 37.5.4 Transmit Status Register

| Register Name | EMAC_   | ſSR  |     |     |     |     |     |

|---------------|---------|------|-----|-----|-----|-----|-----|

| Access Type:  | Read-wr | ite  |     |     |     |     |     |

| 31            | 30      | 29   | 28  | 27  | 26  | 25  | 24  |

| -             | -       | -    | -   | -   | -   | -   | -   |

| 23            | 22      | 21   | 20  | 19  | 18  | 17  | 16  |

| _             | _       | _    | -   | _   | -   | -   | -   |

| 15            | 14      | 13   | 12  | 11  | 10  | 9   | 8   |

| _             | _       | _    | _   | _   | _   | _   | -   |

| 7             | 6       | 5    | 4   | 3   | 2   | 1   | 0   |

| -             | UND     | COMP | BEX | TGO | RLE | COL | UBR |

This register, when read, provides details of the status of a transmit. Once read, individual bits may be cleared by writing 1 to them. It is not possible to set a bit to 1 by writing to the register.

### • UBR: Used Bit Read

Set when a transmit buffer descriptor is read with its used bit set. Cleared by writing a one to this bit.

### COL: Collision Occurred

Set by the assertion of collision. Cleared by writing a one to this bit.

### • RLE: Retry Limit exceeded

Cleared by writing a one to this bit.

### • TGO: Transmit Go

If high transmit is active.

### • BEX: Buffers exhausted mid frame

If the buffers run out during transmission of a frame, then transmission stops, FCS shall be bad and tx\_er asserted. Cleared by writing a one to this bit.

### COMP: Transmit Complete

Set when a frame has been transmitted. Cleared by writing a one to this bit.

### • UND: Transmit Underrun

Set when transmit DMA was not able to read data from memory, either because the bus was not granted in time, because a not OK hresp(bus error) was returned or because a used bit was read midway through frame transmission. If this occurs, the transmitter forces bad CRC. Cleared by writing a one to this bit.

### 37.5.11 Interrupt Mask Register

| Register Name:<br>Access Type: | EMAC_I<br>Read-on |     |      |       |       |       |     |

|--------------------------------|-------------------|-----|------|-------|-------|-------|-----|

| 31                             | 30                | 29  | 28   | 27    | 26    | 25    | 24  |

| -                              | -                 | —   | —    | —     | —     | —     | —   |

| 23                             | 22                | 21  | 20   | 19    | 18    | 17    | 16  |

| -                              | _                 | _   | _    | —     | —     | _     | —   |

| 15                             | 14                | 13  | 12   | 11    | 10    | 9     | 8   |

| -                              | —                 | PTZ | PFR  | HRESP | ROVR  |       | -   |

| 7                              | 6                 | 5   | 4    | 3     | 2     | 1     | 0   |

| TCOMP                          | TXERR             | RLE | TUND | TXUBR | RXUBR | RCOMP | MFD |

### • MFD: Management Frame sent

Management done interrupt masked.

### • RCOMP: Receive Complete

Receive complete interrupt masked.

### • RXUBR: Receive Used Bit Read

Receive used bit read interrupt masked.

#### • TXUBR: Transmit Used Bit Read

Transmit used bit read interrupt masked.

### • TUND: Ethernet Transmit Buffer Underrun

Transmit underrun interrupt masked.

#### • RLE: Retry Limit Exceeded

Retry limit exceeded interrupt masked.

#### • TXERR

Transmit buffers exhausted in mid-frame interrupt masked.

### • TCOMP: Transmit Complete

Transmit complete interrupt masked.

### • ROVR: Receive Overrun

Receive overrun interrupt masked.

### • HRESP: Hresp not OK

Hresp not OK interrupt masked.

### • PFR: Pause Frame Received

Pause frame received interrupt masked.

### • PTZ: Pause Time Zero

Pause time zero interrupt masked.

### 41.7 AT91SAM7X256/128 Errata - Rev. C Parts

Refer to Section 41.1 "Marking" on page 607.

Note: AT91SAM7X256 Revision C chip ID is 0x275B 0942. AT91SAM7X128 Revision C chip ID is 0x275A 0742.

### 41.7.1 Boundary Scan

### 41.7.1.1 BSDL: BSDL File for Rev. B Devices Not Compatible with Rev. C Devices

The BSDL file dedicated to Rev. C devices must be used. No other BSDL file is compatible with Rev. C devices.

### 41.7.2 Embedded Flash Controller (EFC)

### 41.7.2.1 EFC: Embedded Flash Access Time 2

The embedded Flash maximum access time is 20 MHz (instead of 30 MHz at zero Wait State (FWS = 0).

The maximum operating frequency with one Wait State (FWS = 1) is 48.1 MHz (instead of 55 MHz). Above 48.1 MHz and up to 55MHz, two Wait States (FWS = 2) are required.

Problem Fix/Workaround

Set the number of Wait States (FWS) according to the frequency requirements described in this errata.

### 41.7.3 Ethernet MAC (EMAC)

### 41.7.3.1 EMAC: Possible Event Loss when Reading EMAC\_ISR

If an event occurs within the same clock cycle in which the EMAC\_ISR is read, the corresponding bit might be cleared even though it has not been read at 1. This might lead to the loss of this event. Problem Fix/Workaround

Each time the software reads EMAC\_ISR, it has to check the contents of the Transmit Status Register (EMAC\_TSR), the Receive Status Register (EMAC\_RSR) and the Network Status Register (EMAC\_NSR), as the possible lost event is still notified in one of these registers.

### 41.7.3.2 EMAC: Possible Event Loss when Reading the Statistics Register Block

If an event occurs within the same clock cycle during which a statistics register is read, the corresponding counter might lose this event. This might lead to the loss of the incrementation of one for this counter. Problem Fix/Workaround

None

### 41.7.4 Peripheral Input/Output (PIO)

### 41.7.4.1 PIO: Electrical Characteristics on NRST, PA0-PA30 and PB0-PB26

When NRST or PA0 - PA30 or PB0 - PB26 are set as digital inputs with pull-up enabled, the voltage of the I/O stabilizes at VPull-up.

Vpull-up

| VPull-up Min   | VPull-up Max   |

|----------------|----------------|

| VDDIO - 0.65 V | VDDIO - 0.45 V |

| Version<br>6120F<br>(Continued) | Comments                                                                                                                                                                | Change<br>Request<br>Ref. |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|

|                                 | Section 34. "USB Device Port (UDP)" on page 441: Corrections, improvements, additions and deletions throughout section, new source document.                            |                           |  |  |  |

|                                 | Section 34.5.3.8 "Sending a Device Remote Wakeup" replaces title "Sending an External Resume.                                                                           |                           |  |  |  |

|                                 | WAKEUP bit shown in interruput registers: Section 34.6.4 on page 450 thru Section 34.6.8 on page 455                                                                    | 3288                      |  |  |  |

|                                 | RMWUPE, RSMINPR, ESR bits removed from Section 34.6.2 "UDP Global State Register"                                                                                       |                           |  |  |  |

|                                 | <b>NOTE:</b> pertinent to USB pullup effect on USB Reset added to Section 34.6.12 "UDP Transceiver Control Register".                                                   |                           |  |  |  |

|                                 | ADC: Section 35.2 "Block Diagram" on page 463 dedicated and I/O line multiplexed inputs differentiated.                                                                 | 3052                      |  |  |  |

|                                 | "ADC Timings" on page 486 typo corrected in warning                                                                                                                     | 2830                      |  |  |  |

|                                 | CAN: Update to message acceptance example in Section 36.6.2.1 "Message Acceptance Procedure" on page 484.                                                               | 2295, 2296                |  |  |  |

|                                 | New information on byte priority added to Section 36.8.17 "CAN Message Data Low Register" on page 531 and Section 36.8.18 "CAN Message Data High Register" on page 532. | 2476                      |  |  |  |

|                                 | Corrected MDL bit description in Section 36.8.17 "CAN Message Data Low Register" on page 531.                                                                           |                           |  |  |  |

|                                 | Update to specify allowed values for BRP field on Section 36.6.4 "CAN 2.0 Standard Features", page 489 and in Section 36.8.6 "CAN Baudrate Register" on page 518.       | 2597                      |  |  |  |

|                                 | EMAC: "Interrupt Enable Register" on page 559, access changed to Write-only.                                                                                            |                           |  |  |  |

|                                 | "Interrupt Disable Register" on page 560, access changed to Write-only.                                                                                                 | 1725                      |  |  |  |

|                                 | "Interrupt Mask Register" on page 561, access changed to Read-only.                                                                                                     |                           |  |  |  |

|                                 | Section 38. "SAM7X512/256/128 Electrical Characteristics"                                                                                                               |                           |  |  |  |

|                                 | "Absolute Maximum Ratings" on page 581 change to Maximum Operating Voltages                                                                                             | 3059                      |  |  |  |

|                                 | Changed conditions of parameters I <sub>PULLUP</sub> and I <sub>LEAK</sub> in Table 38-2, "DC Characteristics," on page 582.                                            |                           |  |  |  |

|                                 | Updated Table 38-5, "DC Flash Characteristics SAM7X512/256/128," on page 583 and Table 38-9, "Main Oscillator Characteristics," on page 587.                            |                           |  |  |  |

|                                 | Added Table 38-10, "Crystal Characteristics," on page 588.                                                                                                              |                           |  |  |  |

|                                 | Updated I <sub>DDBP</sub> in Table 38-11, "XIN Clock Electrical Characteristics," on page 588.                                                                          | rfo review                |  |  |  |

|                                 | Added information on data sampling in SPI master mode to Table 38-21, "SPI Timings," on page 595.                                                                       |                           |  |  |  |

|                                 | Updated Table 38-22, "EMAC Signals," on page 596                                                                                                                        |                           |  |  |  |

|                                 | Added Table 38-24, "EMAC RMII Specific Signals (Only for SAM7X512)," on page 598 and Figure 38-9, "EMAC RMII Mode" on page 598.                                         |                           |  |  |  |

|                                 | Errata updated:                                                                                                                                                         |                           |  |  |  |

|                                 | Added Section 41.1 "Marking" on page 607.                                                                                                                               |                           |  |  |  |

|                                 | Section 41.3.6.1 "RTT: Possible Event Loss when Reading RTT_SR"                                                                                                         |                           |  |  |  |

|                                 | Section 41.3.7.4 "SPI: Chip Select and Fixed Mode"                                                                                                                      |                           |  |  |  |

|                                 | Section 41.3.7.5 "SPI: Baudrate Set to 1"                                                                                                                               | #2871                     |  |  |  |

|                                 | TWI: Behavior of OVRE Bit (removed)                                                                                                                                     |                           |  |  |  |

|                                 | Section 41.3.9.5 "TWI: Software Reset"                                                                                                                                  |                           |  |  |  |

|                                 | Section 41.3.10.2 "USART: Hardware Handshaking – Two Characters Sent"                                                                                                   |                           |  |  |  |

|                                 | Section 41.3.10.3 "USART: RXBRK Flag Error in Asynchronous Mode"                                                                                                        |                           |  |  |  |

|                                 | PIO: Leakage on PB27 - PB 30"the leakage can be 25 μA in worst case"                                                                                                    | rfo review                |  |  |  |