Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Obsolete                                                                  |

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 55MHz                                                                     |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 62                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                             |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-TFBGA                                                                 |

| Supplier Device Package    | 100-TFBGA (9x9)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x256-cu |

## 7. Processor and Architecture

### 7.1 ARM7TDMI Processor

- RISC processor based on ARMv4T Von Neumann architecture

- Runs at up to 55 MHz, providing 0.9 MIPS/MHz

- Two instruction sets

- ARM high-performance 32-bit instruction set

- Thumb high code density 16-bit instruction set

- Three-stage pipeline architecture

- Instruction Fetch (F)

- Instruction Decode (D)

- Execute (E)

### 7.2 Debug and Test Features

- Integrated embedded in-circuit emulator

- Two watchpoint units

- Test access port accessible through a JTAG protocol

- Debug communication channel

- Debug Unit

- Two-pin UART

- Debug communication channel interrupt handling

- Chip ID Register

- IEEE1149.1 JTAG Boundary-scan on all digital pins

### 7.3 Memory Controller

- Programmable Bus Arbiter

- Handles requests from the ARM7TDMI, the Ethernet MAC and the Peripheral DMA Controller

- Address decoder provides selection signals for

- Three internal 1 Mbyte memory areas

- One 256 Mbyte embedded peripheral area

- Abort Status Registers

- Source, Type and all parameters of the access leading to an abort are saved

- Facilitates debug by detection of bad pointers

- Misalignment Detector

- Alignment checking of all data accesses

- Abort generation in case of misalignment

- Remap Command

- Remaps the SRAM in place of the embedded non-volatile memory

- Allows handling of dynamic exception vectors

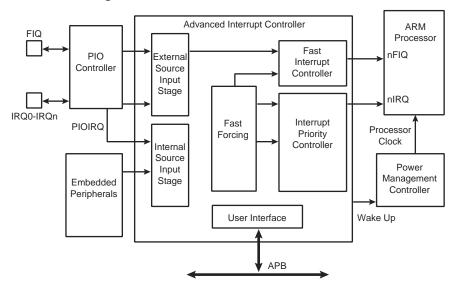

# 9. System Controller

The System Controller manages all vital blocks of the microcontroller: interrupts, clocks, power, time, debug and reset.

The System Controller peripherals are all mapped to the highest 4 Kbytes of address space, between addresses 0xFFFF F000 and 0xFFFF FFFF.

Figure 9-1 on page 24 shows the System Controller Block Diagram.

Figure 8-1 on page 18 shows the mapping of the User Interface of the System Controller peripherals. Note that the Memory Controller configuration user interface is also mapped within this address space.

# 15.4 Periodic Interval Timer (PIT) User Interface

Table 15-1. Register Mapping

| Offset | Register                         | Name     | Access     | Reset       |

|--------|----------------------------------|----------|------------|-------------|

| 0x00   | Mode Register                    | PIT_MR   | Read-write | 0x000F_FFFF |

| 0x04   | Status Register                  | PIT_SR   | Read-only  | 0x0000_0000 |

| 0x08   | Periodic Interval Value Register | PIT_PIVR | Read-only  | 0x0000_0000 |

| 0x0C   | Periodic Interval Image Register | PIT_PIIR | Read-only  | 0x0000_0000 |

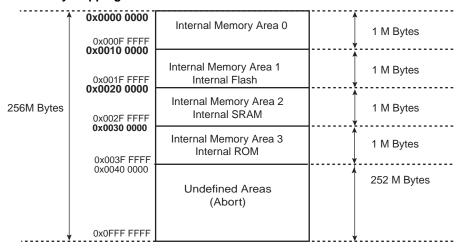

Figure 18-3. Internal Memory Mapping

#### 18.3.2.2 Internal Memory Area 0

The first 32 bytes of Internal Memory Area 0 contain the ARM processor exception vectors, in particular, the Reset Vector at address 0x0.

Before execution of the remap command, the on-chip Flash is mapped into Internal Memory Area 0, so that the ARM7TDMI reaches an executable instruction contained in Flash. After the remap command, the internal SRAM at address 0x0020 0000 is mapped into Internal Memory Area 0. The memory mapped into Internal Memory Area 0 is accessible in both its original location and at address 0x0.

#### 18.3.3 Remap Command

After execution, the Remap Command causes the Internal SRAM to be accessed through the Internal Memory Area 0.

As the ARM vectors (Reset, Abort, Data Abort, Prefetch Abort, Undefined Instruction, Interrupt, and Fast Interrupt) are mapped from address 0x0 to address 0x20, the Remap Command allows the user to redefine dynamically these vectors under software control.

The Remap Command is accessible through the Memory Controller User Interface by writing the MC\_RCR (Remap Control Register) RCB field to one.

The Remap Command can be cancelled by writing the MC\_RCR RCB field to one, which acts as a toggling command. This allows easy debug of the user-defined boot sequence by offering a simple way to put the chip in the same configuration as after a reset.

#### 18.3.4 Abort Status

There are two reasons for an abort to occur:

- access to an undefined address

- an access to a misaligned address.

When an abort occurs, a signal is sent back to all the masters, regardless of which one has generated the access. However, only the ARM7TDMI can take an abort signal into account, and only under the condition that it was generating an access. The Peripheral DMA Controller and the EMAC do not handle the abort input signal. Note that the connections are not represented in Figure 18-1.

To facilitate debug or for fault analysis by an operating system, the Memory Controller integrates an Abort Status register set.

The full 32-bit wide abort address is saved in MC\_AASR. Parameters of the access are saved in MC\_ASR and include:

the size of the request (field ABTSZ)

### 18.4.1 MC Remap Control Register

Register Name: MC\_RCR

Access Type: Write-only

Offset: 0x0

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24  |

|----|----|----|----|----|----|----|-----|

| _  | _  | _  | _  | -  | -  | _  | _   |

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  |

| _  | _  | _  | _  | _  | _  | _  | _   |

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8   |

| _  | _  | -  | -  | _  | _  | Ī  | _   |

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0   |

| _  | _  | _  | _  | _  | _  | _  | RCB |

### • RCB: Remap Command Bit

0: No effect.

<sup>1:</sup> This Command Bit acts on a toggle basis: writing a 1 alternatively cancels and restores the remapping of the page zero memory devices.

### MST\_PDC: PDC Abort Source

- 0: The last aborted access was not due to the PDC.

- 1: The last aborted access was due to the PDC.

#### MST ARM: ARM Abort Source

- 0: The last aborted access was not due to the ARM.

- 1: The last aborted access was due to the ARM.

#### SVMST EMAC: Saved EMAC Abort Source

- 0: No abort due to the EMAC occurred since the last read of MC\_ASR or it is notified in the bit MST\_EMAC.

- 1: At least one abort due to the EMAC occurred since the last read of MC\_ASR.

### • SVMST\_PDC: Saved PDC Abort Source

- 0: No abort due to the PDC occurred since the last read of MC\_ASR or it is notified in the bit MST\_PDC.

- 1: At least one abort due to the PDC occurred since the last read of MC\_ASR.

#### SVMST ARM: Saved ARM Abort Source

- 0: No abort due to the ARM occurred since the last read of MC\_ASR or it is notified in the bit MST\_ARM.

- 1: At least one abort due to the ARM occurred since the last read of MC\_ASR.

#### 20.2.5.2 Flash Write Command

This command is used to write the Flash contents.

The Flash memory plane is organized into several pages. Data to be written are stored in a load buffer that corresponds to a Flash memory page. The load buffer is automatically flushed to the Flash:

- before access to any page other than the current one

- when a new command is validated (MODE = CMDE)

The **Write Page** command **(WP)** is optimized for consecutive writes. Write handshaking can be chained; an internal address buffer is automatically increased.

Table 20-8. Write Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]               |

|------|--------------------|-----------|--------------------------|

| 1    | Write handshaking  | CMDE      | WP or WPL or EWP or EWPL |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB       |

| 3    | Write handshaking  | ADDR1     | Memory Address           |

| 4    | Write handshaking  | DATA      | *Memory Address++        |

| 5    | Write handshaking  | DATA      | *Memory Address++        |

|      |                    |           |                          |

| n    | Write handshaking  | ADDR0     | Memory Address LSB       |

| n+1  | Write handshaking  | ADDR1     | Memory Address           |

| n+2  | Write handshaking  | DATA      | *Memory Address++        |

| n+3  | Write handshaking  | DATA      | *Memory Address++        |

|      |                    |           |                          |

The Flash command **Write Page and Lock (WPL)** is equivalent to the Flash Write Command. However, the lock bit is automatically set at the end of the Flash write operation. As a lock region is composed of several pages, the programmer writes to the first pages of the lock region using Flash write commands and writes to the last page of the lock region using a Flash write and lock command.

The Flash command **Erase Page and Write (EWP)** is equivalent to the Flash Write Command. However, before programming the load buffer, the page is erased.

The Flash command Erase Page and Write the Lock (EWPL) combines EWP and WPL commands.

#### 20.2.5.3 Flash Full Erase Command

This command is used to erase the Flash memory planes.

All lock regions must be unlocked before the Full Erase command by using the CLB command. Otherwise, the erase command is aborted and no page is erased.

Table 20-9. Full Erase Command

| St | tep | Handshake Sequence | MODE[3:0] | DATA[15:0] |

|----|-----|--------------------|-----------|------------|

| 1  |     | Write handshaking  | CMDE      | EA         |

| 2  |     | Write handshaking  | DATA      | 0          |

#### 20.2.5.4 Flash Lock Commands

Lock bits can be set using WPL or EWPL commands. They can also be set by using the **Set Lock** command **(SLB)**. With this command, several lock bits can be activated. A Bit Mask is provided as argument to the command. When bit 0 of the bit mask is set, then the first lock bit is activated.

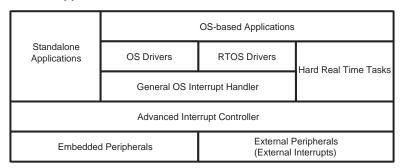

# 23.3 Application Block Diagram

Figure 23-2. Description of the Application Block

# 23.4 AIC Detailed Block Diagram

Figure 23-3. AIC Detailed Block Diagram

# 23.5 I/O Line Description

Table 23-1. I/O Line Description

| Pin Name    | Pin Description           | Туре  |

|-------------|---------------------------|-------|

| FIQ         | Fast Interrupt            | Input |

| IRQ0 - IRQn | Interrupt 0 - Interrupt n | Input |

### 23.8.10 AIC Core Interrupt Status Register

Register Name: AIC\_CISR

Access Type: Read-only

Reset Value: 0

| 31 | 30 | 29 | 28 | 27 | 26 | 25   | 24   |

|----|----|----|----|----|----|------|------|

| _  | _  | _  | _  | _  | _  | _    | _    |

| 23 | 22 | 21 | 20 | 19 | 18 | 17   | 16   |

| _  |    | _  |    |    |    | I    | _    |

| 15 | 14 | 13 | 12 | 11 | 10 | 9    | 8    |

| _  |    | _  |    |    |    | I    | _    |

| 7  | 6  | 5  | 4  | 3  | 2  | 1    | 0    |

| _  | _  | _  | _  | _  | _  | NIRQ | NIFQ |

### • NFIQ: NFIQ Status

0 = nFIQ line is deactivated.

1 = nFIQ line is active.

#### • NIRQ: NIRQ Status

0 = nIRQ line is deactivated.

1 = nIRQ line is active.

### 23.8.11 AIC Interrupt Enable Command Register

**Register Name:** AIC\_IECR Access Type: Write-only

| 31    | 30    | 29    | 28    | 27    | 26    | 25    | 24    |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PID31 | PID30 | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23    | 22    | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23 | PID22 | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15    | 14    | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15 | PID14 | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7  | PID6  | PID5  | PID4  | PID3  | PID2  | SYS   | FIQ   |

### • FIQ, SYS, PID2-PID3: Interrupt Enable

0 = No effect.

1 = Enables corresponding interrupt.

Master Clock cycle or more is accepted. For pulse durations between 1/2 Master Clock cycle and 1 Master Clock cycle the pulse may or may not be taken into account, depending on the precise timing of its occurrence. Thus for a pulse to be visible it must exceed 1 Master Clock cycle, whereas for a glitch to be reliably filtered out, its duration must not exceed 1/2 Master Clock cycle. The filter introduces one Master Clock cycle latency if the pin level change occurs before a rising edge. However, this latency does not appear if the pin level change occurs before a falling edge. This is illustrated in Figure 27-5.

The glitch filters are controlled by the register set; PIO\_IFER (Input Filter Enable Register), PIO\_IFDR (Input Filter Disable Register) and PIO\_IFSR (Input Filter Status Register). Writing PIO\_IFER and PIO\_IFDR respectively sets and clears bits in PIO\_IFSR. This last register enables the glitch filter on the I/O lines.

When the glitch filter is enabled, it does not modify the behavior of the inputs on the peripherals. It acts only on the value read in PIO\_PDSR and on the input change interrupt detection. The glitch filters require that the PIO Controller clock is enabled.

PIO\_PDSR if PIO\_IFSR = 1

Figure 27-5. Input Glitch Filter Timing

### 27.4.10 Input Change Interrupt

The PIO Controller can be programmed to generate an interrupt when it detects an input change on an I/O line. The Input Change Interrupt is controlled by writing PIO\_IER (Interrupt Enable Register) and PIO\_IDR (Interrupt Disable Register), which respectively enable and disable the input change interrupt by setting and clearing the corresponding bit in PIO\_IMR (Interrupt Mask Register). As Input change detection is possible only by comparing two successive samplings of the input of the I/O line, the PIO Controller clock must be enabled. The Input Change Interrupt is available, regardless of the configuration of the I/O line, i.e. configured as an input only, controlled by the PIO Controller or assigned to a peripheral function.

When an input change is detected on an I/O line, the corresponding bit in PIO\_ISR (Interrupt Status Register) is set. If the corresponding bit in PIO\_IMR is set, the PIO Controller interrupt line is asserted. The interrupt signals of the thirty-two channels are ORed-wired together to generate a single interrupt signal to the Advanced Interrupt Controller.

When the software reads PIO\_ISR, all the interrupts are automatically cleared. This signifies that all the interrupts that are pending when PIO\_ISR is read must be handled.

### 27.6.1 PIO Controller PIO Enable Register

Name: PIO\_PER

Access Type: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: PIO Enable

0 = No effect.

### 27.6.2 PIO Controller PIO Disable Register

Name: PIO\_PDR

Access Type: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: PIO Disable

0 = No effect.

<sup>1 =</sup> Enables the PIO to control the corresponding pin (disables peripheral control of the pin).

<sup>1 =</sup> Disables the PIO from controlling the corresponding pin (enables peripheral control of the pin).

### 27.6.27 PIO Output Write Enable Register

Name: PIO\_OWER

Access Type: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Output Write Enable.

0 = No effect.

### 27.6.28 PIO Output Write Disable Register

Name: PIO\_OWDR

Access Type: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: Output Write Disable.

0 = No effect.

<sup>1 =</sup> Enables writing PIO\_ODSR for the I/O line.

<sup>1 =</sup> Disables writing PIO\_ODSR for the I/O line.

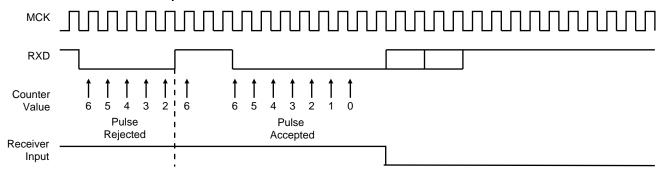

#### 30.6.5.3 IrDA Demodulator

The demodulator is based on the IrDA Receive filter comprised of an 8-bit down counter which is loaded with the value programmed in US\_IF. When a falling edge is detected on the RXD pin, the Filter Counter starts counting down at the Master Clock (MCK) speed. If a rising edge is detected on the RXD pin, the counter stops and is reloaded with US\_IF. If no rising edge is detected when the counter reaches 0, the input of the receiver is driven low during one bit time.

Figure 30-25 illustrates the operations of the IrDA demodulator.

Figure 30-25. IrDA Demodulator Operations

As the IrDA mode uses the same logic as the ISO7816, note that the FI\_DI\_RATIO field in US\_FIDI must be set to a value higher than 0 in order to assure IrDA communications operate correctly.

# 32.6.2 TC Block Mode Register

Register Name: TC\_BMR

Access Type: Read-write

| 31 | 30 | 29   | 28   | 27   | 26   | 25   | 24   |

|----|----|------|------|------|------|------|------|

| _  | _  | ı    | _    |      |      |      | _    |

| 23 | 22 | 21   | 20   | 19   | 18   | 17   | 16   |

| _  | _  | ı    | -    |      |      | ı    | -    |

| 15 | 14 | 13   | 12   | 11   | 10   | 9    | 8    |

| _  | _  | ı    | -    |      |      | ı    | -    |

| 7  | 6  | 5    | 4    | 3    | 2    | 1    | 0    |

| _  | _  | TC2X | KC2S | TC1> | (C1S | TC0> | KC0S |

# • TC0XC0S: External Clock Signal 0 Selection

| TC0) | (C0S | Signal Connected to XC0 |

|------|------|-------------------------|

| 0    | 0    | TCLK0                   |

| 0    | 1    | none                    |

| 1    | 0    | TIOA1                   |

| 1    | 1    | TIOA2                   |

# • TC1XC1S: External Clock Signal 1 Selection

| TC1) | (C1S | Signal Connected to XC1 |

|------|------|-------------------------|

| 0    | 0    | TCLK1                   |

| 0    | 1    | none                    |

| 1    | 0    | TIOA0                   |

| 1    | 1    | TIOA2                   |

# • TC2XC2S: External Clock Signal 2 Selection

| TC2) | C2S | Signal Connected to XC2 |

|------|-----|-------------------------|

| 0    | 0   | TCLK2                   |

| 0    | 1   | none                    |

| 1    | 0   | TIOA0                   |

| 1    | 1   | TIOA1                   |

### 33.6.10 PWM Channel Duty Cycle Register

**Register Name:** PWM\_CDTY[0..X-1]

Access Type: Read-write

| 31   | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|------|----|----|----|----|----|----|----|

|      |    |    | CD | TY |    |    |    |

| 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| CDTY |    |    |    |    |    |    |    |

| 15   | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|      |    |    | CD | TY |    |    |    |

| 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|      |    |    | CD | TY |    |    |    |

Only the first 16 bits (internal channel counter size) are significant.

### • CDTY: Channel Duty Cycle

Defines the waveform duty cycle. This value must be defined between 0 and CPRD (PWM\_CPRx).

### 34.6.11 UDP FIFO Data Register

**Register Name:** UDP\_ FDRx [x = 0..5]

Access Type: Read-write

| 31 | 30 | 29 | 28    | 27    | 26 | 25 | 24 |

|----|----|----|-------|-------|----|----|----|

| _  | _  | _  | _     | _     | 1  | ı  | _  |

| 23 | 22 | 21 | 20    | 19    | 18 | 17 | 16 |

| _  | _  | _  | _     | _     | -  | -  | _  |

| 15 | 14 | 13 | 12    | 11    | 10 | 9  | 8  |

| _  | _  | _  | _     | _     | 1  | -  | _  |

| 7  | 6  | 5  | 4     | 3     | 2  | 1  | 0  |

|    |    |    | FIFO_ | _DATA |    |    |    |

### • FIFO\_DATA[7:0]: FIFO Data Value

The microcontroller can push or pop values in the FIFO through this register.

RXBYTECNT in the corresponding UDP\_ CSRx register is the number of bytes to be read from the FIFO (sent by the host).

The maximum number of bytes to write is fixed by the Max Packet Size in the Standard Endpoint Descriptor. It can not be more than the physical memory size associated to the endpoint. Refer to the *Universal Serial Bus Specification, Rev. 2.0* for more information.

### 37.5.26.17Receive Jabbers Register

| Register Name:                                                                                                                                                                                                                                              | EMAC_F  | RJA  |    |    |    |    |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----|----|----|----|----|

| Access Type:                                                                                                                                                                                                                                                | Read-wr | rite |    |    |    |    |    |

| 31                                                                                                                                                                                                                                                          | 30      | 29   | 28 | 27 | 26 | 25 | 24 |

| _                                                                                                                                                                                                                                                           | _       | _    | _  | _  | _  | _  | -  |

| 23                                                                                                                                                                                                                                                          | 22      | 21   | 20 | 19 | 18 | 17 | 16 |

| _                                                                                                                                                                                                                                                           | _       | _    | _  | _  | _  |    | _  |

| 15                                                                                                                                                                                                                                                          | 14      | 13   | 12 | 11 | 10 | 9  | 8  |

| _                                                                                                                                                                                                                                                           | _       | _    | _  | _  | _  | 1  | _  |

| 7                                                                                                                                                                                                                                                           | 6       | 5    | 4  | 3  | 2  | 1  | 0  |

| -     -     -     -     -     -     -       23     22     21     20     19     18     17     16       -     -     -     -     -     -     -     -     -       15     14     13     12     11     10     9     8       -     -     -     -     -     -     - |         |      |    |    |    |    |    |

### • RJB: Receive Jabbers

An 8-bit register counting the number of frames received exceeding 1518 bytes (1536 if bit 8 set in network configuration register) in length and have either a CRC error, an alignment error or a receive symbol error.

### 37.5.26.18Undersize Frames Register

| Register Name: | EMAC_U  | JSF  |    |    |    |    |    |

|----------------|---------|------|----|----|----|----|----|

| Access Type:   | Read-wr | rite |    |    |    |    |    |

| 31             | 30      | 29   | 28 | 27 | 26 | 25 | 24 |

| -              | -       | _    | _  | _  | -  | -  | -  |

| 23             | 22      | 21   | 20 | 19 | 18 | 17 | 16 |

| _              | _       | _    | _  | _  | -  | _  | _  |

| 15             | 14      | 13   | 12 | 11 | 10 | 9  | 8  |

| _              | _       | _    | _  | _  | _  | _  | _  |

| 7              | 6       | 5    | 4  | 3  | 2  | 1  | 0  |

|                |         |      | U  | SF |    |    |    |

#### • USF: Undersize Frames

An 8-bit register counting the number of frames received less than 64 bytes in length but do not have either a CRC error, an alignment error or a receive symbol error.

### 38.4.3 Crystal Characteristics

Table 38-10. Crystal Characteristics

| Symbol                                                                                      | Parameter                     | Conditions          | Min      | Тур | Max | Unit |

|---------------------------------------------------------------------------------------------|-------------------------------|---------------------|----------|-----|-----|------|

| ESR Equivalent Series Resistor Rs Fundamental @3 MHz Fundamental @8 MHz Fundamental @16 MHz |                               | Fundamental @3 MHz  |          |     | 200 |      |

|                                                                                             |                               |                     | 100      |     |     |      |

|                                                                                             | Equivalent Series Resistor Rs | Fundamental @16 MHz |          |     | 80  | Ω    |

|                                                                                             |                               | Fundamental @20 MHz | 80<br>50 |     |     |      |

| C <sub>M</sub>                                                                              | Motional capacitance          |                     |          |     | 8   | fF   |

| C <sub>SHUNT</sub>                                                                          | Shunt capacitance             |                     |          |     | 7   | pF   |

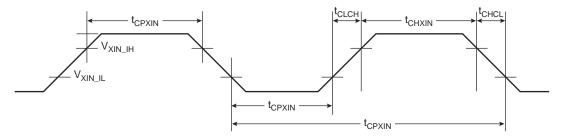

### 38.4.4 XIN Clock Characteristics

Table 38-11. XIN Clock Electrical Characteristics

| Symbol                  | Parameter                                 | Conditions | Min                      | Max                      | Units  |

|-------------------------|-------------------------------------------|------------|--------------------------|--------------------------|--------|

| 1/(t <sub>CPXIN</sub> ) | XIN Clock Frequency                       | (1)        |                          | 50.0                     | MHz    |

| t <sub>CPXIN</sub>      | XIN Clock Period                          | (1)        | 20.0                     |                          | ns     |

| t <sub>CHXIN</sub>      | XIN Clock High Half-period                | (1)        | 8.0                      |                          | ns     |

| t <sub>CLXIN</sub>      | XIN Clock Low Half-period                 | (1)        | 8.0                      |                          | ns     |

| t <sub>CLCH</sub>       | Rise Time                                 | (1)        |                          | 400                      |        |

| t <sub>CHCL</sub>       | Fall Time                                 | (1)        |                          | 400                      |        |

| C <sub>IN</sub>         | XIN Input Capacitance                     | (1)        |                          | 46                       | pF     |

| R <sub>IN</sub>         | XIN Pull-down Resistor                    | (1)        |                          | 500                      | kΩ     |

| $V_{XIN\_IL}$           | V <sub>XIN</sub> Input Low-level Voltage  | (1)        | -0.3                     | 0.2 x V <sub>DDPLL</sub> | V      |

| $V_{XIN\_IH}$           | V <sub>XIN</sub> Input High-level Voltage | (1)        | 0.8 x V <sub>DDPLL</sub> | 1.95                     | V      |

| I <sub>DDBP</sub>       | Bypass Current Consumption                | (1)        |                          | 15                       | μΩ/MHz |

Note: 1. These characteristics apply only when the Main Oscillator is in bypass mode (i.e., when MOSCEN = 0 and OSCBYPASS = 1 in the CKGR\_MOR register, see the Clock Generator Main Oscillator Register.

Figure 38-2. XIN CLock Timing

- DRDY already active,

- GOVRE inactive.

- previous data stored in LCDR being neither data from channel "y", nor data from channel "x".

GOVRE should be set but is not.

Problem Fix/Workaround

None

### 41.4.1.7 ADC: GOVRE Bit is not Set when Disabling a Channel

When disabling channel "y" at the same instant as an end of conversion on channel "x", EOC[x] and DRDY being already active, GOVRE does not rise.

Note: OVRE[x] rises as expected.

Problem Fix/Workaround

None

#### 41.4.1.8 ADC: OVRE Flag Behavior

When the OVRE flag (on channel i) has been set but the related EOC status (of channel i) has been cleared (by a read of CDRi or LCDR), reading the Status register at the same instant as an end of conversion (causing the set of EOC status on channel i), does not lead to a reset of the OVRE flag (on channel i) as expected.

Problem Fix/Workaround:

None

#### 41.4.1.9 ADC: EOC Set although Channel Disabled

If a channel is disabled while a conversion is running and if a read of CDR is performed at the same time as an end of conversion of any channel occurs, the EOC of the channel with the conversion running may rise (whereas it has been disabled).

Problem Fix/Workaround

Do not take into account the EOC of a disabled channel

#### 41.4.1.10 ADC: Spurious Clear of EOC Flag

If "x" and "y" are two successively converted channels and "z" is yet another enabled channel ("z" being neither "x" nor "y"), reading CDR on channel "z" at the same instant as an end of conversion on channel "y" automatically clears EOC[x] instead of EOC[z].

Problem Fix/Workaround

None.

#### 41.4.1.11 ADC: Sleep Mode

If Sleep mode is activated while there is no activity (no conversion is being performed), it will take effect only after a conversion occurs.

Problem Fix/Workaround

To activate sleep mode as soon as possible, it is recommended to write successively, ADC Mode Register (SLEEP) then ADC Control Register (START bit field); to start an analog-to-digital conversion, in order put ADC into sleep mode at the end of this conversion.

#### 41.4.10.5 TWI: Software Reset

when a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

Problem Fix/Workaround

None.

### 41.4.11 Universal Synchronous Asynchronous Receiver Transmitter (USART)

#### 41.4.11.1 USART: CTS in Hardware Handshaking

When Hardware Handshaking is used and if CTS goes low near the end of the start bit, a character can be lost.

CTS must not go high during a time slot occurring between 2 Master Clock periods before and 16 Master Clock periods after the rising edge of the start bit.

Problem Fix/Workaround

None.

#### 41.4.11.2 USART: Hardware Handshaking – Two Characters Sent

If CTS switches from 0 to 1 during the TX of a character and if the holding register (US\_THR) is not empty, the content of US\_THR will also be transmitted.

Problem Fix/Workaround

Don't use the PDC in transmit mode and do not fill US\_THR before TXEMPTY is set at 1.

### 41.4.11.3 USART: RXBRK Flag Error in Asynchronous Mode

In receiver mode, when there are two consecutive characters (without time guard in between), RXBRK is not taken into account. As a result, the RXBRK flag is not enabled correctly and the frame error flag is set

Problem Fix/Workaround

Constraints on the transmitter device connected to the SAM7X USART receiver side:

The transmitter may use the timeguard feature or send two STOP conditions. Only one STOP condition is taken into account by the receiver state machine. After this STOP condition, as there is no valid data, the receiver state machine will go in idle mode and enable the RXBRK flag.

#### 41.4.11.4 USART: DCD is Active High instead of Low.

The DCD signal is active at High level in the USART Modem Mode .

DCD should be active at Low level.

Problem Fix/Workaround

Add an inverter.