Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | ARM7®                                                           |

| Core Size                  | 16/32-Bit                                                       |

| Speed                      | 55MHz                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                      |

| Number of I/O              | 62                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 64K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                   |

| Data Converters            | A/D 8x10b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 100-TFBGA                                                       |

| Supplier Device Package    | 100-TFBGA (9x9)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at91sam7x256b-cu-999 |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

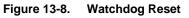

#### 13.2.4.5 Watchdog Reset

The Watchdog Reset is entered when a watchdog fault occurs. This state lasts 3 Slow Clock cycles.

When in Watchdog Reset, assertion of the reset signals depends on the WDRPROC bit in WDT\_MR:

- If WDRPROC is 0, the Processor Reset and the Peripheral Reset are asserted. The NRST line is also asserted, depending on the programming of the field ERSTL. However, the resulting low level on NRST does not result in a User Reset state.

- If WDRPROC = 1, only the processor reset is asserted.

The Watchdog Timer is reset by the proc\_nreset signal. As the watchdog fault always causes a processor reset if WDRSTEN is set, the Watchdog Timer is always reset after a Watchdog Reset, and the Watchdog is enabled by default and with a period set to a maximum.

When the WDRSTEN in WDT\_MR bit is reset, the watchdog fault has no impact on the reset controller.

# 16.3 Functional Description

The Watchdog Timer can be used to prevent system lock-up if the software becomes trapped in a deadlock. It is supplied with VDDCORE. It restarts with initial values on processor reset.

The Watchdog is built around a 12-bit down counter, which is loaded with the value defined in the field WV of the Mode Register (WDT\_MR). The Watchdog Timer uses the Slow Clock divided by 128 to establish the maximum Watchdog period to be 16 seconds (with a typical Slow Clock of 32.768 kHz).

After a Processor Reset, the value of WV is 0xFFF, corresponding to the maximum value of the counter with the external reset generation enabled (field WDRSTEN at 1 after a Backup Reset). This means that a default Watchdog is running at reset, i.e., at power-up. The user must either disable it (by setting the WDDIS bit in WDT\_MR) if he does not expect to use it or must reprogram it to meet the maximum Watchdog period the application requires.

The Watchdog Mode Register (WDT\_MR) can be written only once. Only a processor reset resets it. Writing the WDT\_MR register reloads the timer with the newly programmed mode parameters.

If the watchdog is restarted by writing into the WDT\_CR register, the WDT\_MR register must not be programmed during a period of time of 3 slow clock period following the WDT\_CR write access. In any case, programming a new value in WDT\_MR automatically initiates a restart instruction.

In normal operation, the user reloads the Watchdog at regular intervals before the timer underflow occurs, by writing the Control Register (WDT\_CR) with the bit WDRSTT to 1. The Watchdog counter is then immediately reloaded from WDT\_MR and restarted, and the Slow Clock 128 divider is reset and restarted. The WDT\_CR register is write-protected. As a result, writing WDT\_CR without the correct hard-coded key has no effect. If an underflow does occur, the "wdt\_fault" signal to the Reset Controller is asserted if the bit WDRSTEN is set in the Mode Register (WDT\_MR). Moreover, the bit WDUNF is set in the Watchdog Status Register (WDT\_SR).

To prevent a software deadlock that continuously triggers the Watchdog, the reload of the Watchdog must occur while the Watchdog counter is within a window between 0 and WDD, WDD is defined in the WatchDog Mode Register WDT\_MR.

Any attempt to restart the Watchdog while the Watchdog counter is between WDV and WDD results in a Watchdog error, even if the Watchdog is disabled. The bit WDERR is updated in the WDT\_SR and the "wdt\_fault" signal to the Reset Controller is asserted.

Note that this feature can be disabled by programming a WDD value greater than or equal to the WDV value. In such a configuration, restarting the Watchdog Timer is permitted in the whole range [0; WDV] and does not generate an error. This is the default configuration on reset (the WDD and WDV values are equal).

The status bits WDUNF (Watchdog Underflow) and WDERR (Watchdog Error) trigger an interrupt, provided the bit WDFIEN is set in the mode register. The signal "wdt\_fault" to the reset controller causes a Watchdog reset if the WDRSTEN bit is set as already explained in the reset controller programmer Datasheet. In that case, the processor and the Watchdog Timer are reset, and the WDERR and WDUNF flags are reset.

If a reset is generated or if WDT\_SR is read, the status bits are reset, the interrupt is cleared, and the "wdt\_fault" signal to the reset controller is deasserted.

Writing the WDT\_MR reloads and restarts the down counter.

While the processor is in debug state or in idle mode, the counter may be stopped depending on the value programmed for the bits WDIDLEHLT and WDDBGHLT in the WDT\_MR.

Atmel

The AT91SAM7X512 security bit is controlled by the EFC0. To use the Set Security Bit command, the EFC0 must be selected using the Select EFC command

#### Table 20-14. Set Security Bit Command

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0] |

|------|--------------------|-----------|------------|

| 1    | Write handshaking  | CMDE      | SSE        |

| 2    | Write handshaking  | DATA      | 0          |

Once the security bit is set, it is not possible to access FFPI. The only way to erase the security bit is to erase the Flash.

In order to erase the Flash, the user must perform the following:

- Power-off the chip

- Power-on the chip with TST = 0

- Assert Erase during a period of more than 220 ms

- Power-off the chip

Then it is possible to return to FFPI mode and check that Flash is erased.

#### 20.2.5.7 AT91SAM7X512 Select EFC Command

The commands WPx, EA, xLB, xFB are executed using the current EFC controller. The default EFC controller is EFC0. The **Select EFC** command (SEFC) allows selection of the current EFC controller.

| Table 20-15. | Select EFC | Command |

|--------------|------------|---------|

|--------------|------------|---------|

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]                         |

|------|--------------------|-----------|------------------------------------|

| 1    | Write handshaking  | CMDE      | SEFC                               |

| 2    | Write handshaking  | DATA      | 0 = Select EFC0<br>1 = Select EFC1 |

#### 20.2.5.8 Memory Write Command

This command is used to perform a write access to any memory location.

The **Memory Write** command **(WRAM)** is optimized for consecutive writes. Write handshaking can be chained; an internal address buffer is automatically increased.

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]         |

|------|--------------------|-----------|--------------------|

| 1    | Write handshaking  | CMDE      | WRAM               |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB |

| 3    | Write handshaking  | ADDR1     | Memory Address     |

| 4    | Write handshaking  | DATA      | *Memory Address++  |

| 5    | Write handshaking  | DATA      | *Memory Address++  |

|      |                    |           |                    |

| n    | Write handshaking  | ADDR0     | Memory Address LSB |

| n+1  | Write handshaking  | ADDR1     | Memory Address     |

| n+2  | Write handshaking  | DATA      | *Memory Address++  |

| n+3  | Write handshaking  | DATA      | *Memory Address++  |

|      |                    |           |                    |

#### Table 20-16. Write Command

Atmel

### 25.9.12 PMC Interrupt Enable Register

| Register Name:<br>Access Type: | PMC_IE<br>Write-on |    |    |        |         |         |         |

|--------------------------------|--------------------|----|----|--------|---------|---------|---------|

| 31                             | 30                 | 29 | 28 | 27     | 26      | 25      | 24      |

| -                              | _                  | _  | —  | -      | _       | _       | -       |

| 23                             | 22                 | 21 | 20 | 19     | 18      | 17      | 16      |

| -                              | _                  | —  | —  | -      | -       | _       | _       |

| 15                             | 14                 | 13 | 12 | 11     | 10      | 9       | 8       |

| -                              | _                  | —  | -  | -      | PCKRDY2 | PCKRDY1 | PCKRDY0 |

| 7                              | 6                  | 5  | 4  | 3      | 2       | 1       | 0       |

| _                              | _                  | _  | -  | MCKRDY | LOCK    | _       | MOSCS   |

- MOSCS: Main Oscillator Status Interrupt Enable

- LOCK: PLL Lock Interrupt Enable

- MCKRDY: Master Clock Ready Interrupt Enable

### • PCKRDYx: Programmable Clock Ready x Interrupt Enable

0 = No effect.

1 = Enables the corresponding interrupt.

# 26.5.8 Debug Unit Transmit Holding Register

|              | DBGU_THR   |    |    |    |    |    |  |  |  |

|--------------|------------|----|----|----|----|----|--|--|--|

| Access Type: | Write-only |    |    |    |    |    |  |  |  |

| 31 3         | 0 29       | 28 | 27 | 26 | 25 | 24 |  |  |  |

|              | - –        | -  | -  | _  | _  | -  |  |  |  |

| 232          | 2 21       | 20 | 19 | 18 | 17 | 16 |  |  |  |

|              | - –        | -  | -  | -  | -  | -  |  |  |  |

| 15 1         | 4 13       | 12 | 11 | 10 | 9  | 8  |  |  |  |

|              | - –        | _  | _  | _  | -  | -  |  |  |  |

| 7            | 6 5        | 4  | 3  | 2  | 1  | 0  |  |  |  |

|              | TXCHR      |    |    |    |    |    |  |  |  |

### • TXCHR: Character to be Transmitted

Next character to be transmitted after the current character if TXRDY is not set.

# 26.5.9 Debug Unit Baud Rate Generator Register

| Name:<br>Access Type: | DBGU_E<br>Read-wr |    |    |    |    |    |    |

|-----------------------|-------------------|----|----|----|----|----|----|

| 31                    | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

| _                     | -                 | _  | -  | —  | -  | _  | _  |

| 23                    | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

| -                     | _                 | —  | -  | —  | -  | _  | -  |

| 15                    | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

| CD                    |                   |    |    |    |    |    |    |

| 7                     | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                       |                   |    | C  | D  |    |    |    |

### • CD: Clock Divisor

| CD         | Baud Rate Clock |

|------------|-----------------|

| 0          | Disabled        |

| 1          | MCK             |

| 2 to 65535 | MCK / (CD x 16) |

• NVPSIZ2 Second Nonvolatile Program Memory Size

|   | NVP | SIZ2 |   | Size        |

|---|-----|------|---|-------------|

| 0 | 0   | 0    | 0 | None        |

| 0 | 0   | 0    | 1 | 8K bytes    |

| 0 | 0   | 1    | 0 | 16K bytes   |

| 0 | 0   | 1    | 1 | 32K bytes   |

| 0 | 1   | 0    | 0 | Reserved    |

| 0 | 1   | 0    | 1 | 64K bytes   |

| 0 | 1   | 1    | 0 | Reserved    |

| 0 | 1   | 1    | 1 | 128K bytes  |

| 1 | 0   | 0    | 0 | Reserved    |

| 1 | 0   | 0    | 1 | 256K bytes  |

| 1 | 0   | 1    | 0 | 512K bytes  |

| 1 | 0   | 1    | 1 | Reserved    |

| 1 | 1   | 0    | 0 | 1024K bytes |

| 1 | 1   | 0    | 1 | Reserved    |

| 1 | 1   | 1    | 0 | 2048K bytes |

| 1 | 1   | 1    | 1 | Reserved    |

### • SRAMSIZ: Internal SRAM Size

|   | SRA | MSIZ |   | Size       |

|---|-----|------|---|------------|

| 0 | 0   | 0    | 0 | Reserved   |

| 0 | 0   | 0    | 1 | 1K bytes   |

| 0 | 0   | 1    | 0 | 2K bytes   |

| 0 | 0   | 1    | 1 | 6K bytes   |

| 0 | 1   | 0    | 0 | 112K bytes |

| 0 | 1   | 0    | 1 | 4K bytes   |

| 0 | 1   | 1    | 0 | 80K bytes  |

| 0 | 1   | 1    | 1 | 160K bytes |

| 1 | 0   | 0    | 0 | 8K bytes   |

| 1 | 0   | 0    | 1 | 16K bytes  |

| 1 | 0   | 1    | 0 | 32K bytes  |

| 1 | 0   | 1    | 1 | 64K bytes  |

| 1 | 1   | 0    | 0 | 128K bytes |

| 1 | 1   | 0    | 1 | 256K bytes |

| 1 | 1   | 1    | 0 | 96K bytes  |

| 1 | 1   | 1    | 1 | 512K bytes |

### 27.6.1 PIO Controller PIO Enable Register

Name: Access Type: Write-only

```

PIO_PER

```

|   |     |     | •   |     |     |     |     |     |

|---|-----|-----|-----|-----|-----|-----|-----|-----|

| _ | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|   | P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| _ | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|   | P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| - | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|   | P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

|   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|   | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

|   |     |     |     |     |     |     |     |     |

### • P0-P31: PIO Enable

0 = No effect.

1 = Enables the PIO to control the corresponding pin (disables peripheral control of the pin).

### 27.6.2 PIO Controller PIO Disable Register

| Name: | PIO_PDR |

|-------|---------|

|       |         |

Access Type: Write-only

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

### • P0-P31: PIO Disable

0 = No effect.

1 = Disables the PIO from controlling the corresponding pin (enables peripheral control of the pin).

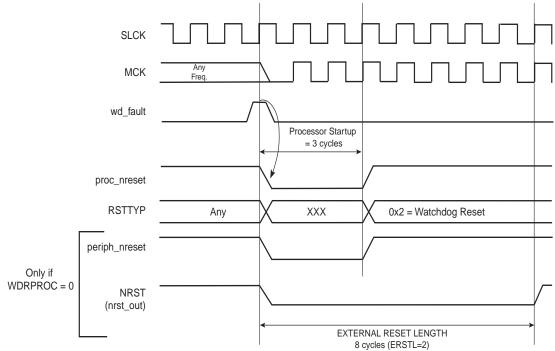

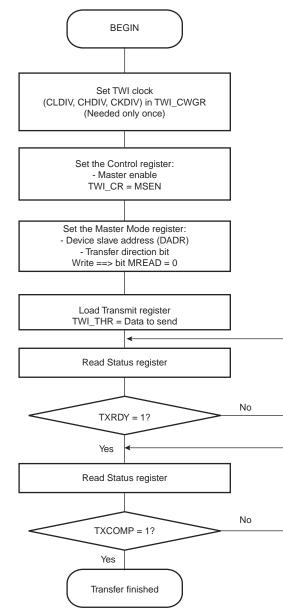

#### 29.5.6 Read/Write Flowcharts

The following flowcharts shown in Figure 29-13, Figure 29-14 on page 277, Figure 29-15 on page 278, Figure 29-16 on page 279, Figure 29-17 on page 280 and Figure 29-18 on page 281 give examples for read and write operations. A polling or interrupt method can be used to check the status bits. The interrupt method requires that the interrupt enable register (TWI\_IER) be configured first.

#### 30.6.3.6 Multidrop Mode

If the PAR field in the Mode Register (US\_MR) is programmed to the value 0x6 or 0x07, the USART runs in Multidrop Mode. This mode differentiates the data characters and the address characters. Data is transmitted with the parity bit at 0 and addresses are transmitted with the parity bit at 1.

If the USART is configured in multidrop mode, the receiver sets the PARE parity error bit when the parity bit is high and the transmitter is able to send a character with the parity bit high when the Control Register is written with the SENDA bit at 1.

To handle parity error, the PARE bit is cleared when the Control Register is written with the bit RSTSTA at 1.

The transmitter sends an address byte (parity bit set) when SENDA is written to US\_CR. In this case, the next byte written to US\_THR is transmitted as an address. Any character written in US\_THR without having written the command SENDA is transmitted normally with the parity at 0.

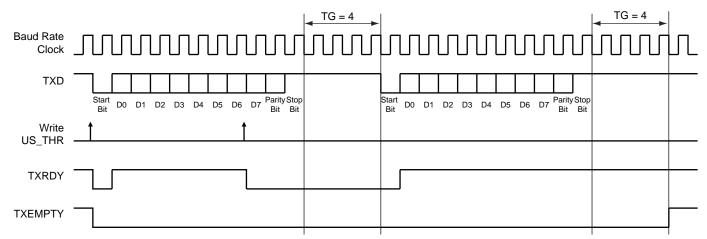

#### 30.6.3.7 Transmitter Timeguard

The timeguard feature enables the USART interface with slow remote devices.

The timeguard function enables the transmitter to insert an idle state on the TXD line between two characters. This idle state actually acts as a long stop bit.

The duration of the idle state is programmed in the TG field of the Transmitter Timeguard Register (US\_TTGR). When this field is programmed at zero no timeguard is generated. Otherwise, the transmitter holds a high level on TXD after each transmitted byte during the number of bit periods programmed in TG in addition to the number of stop bits.

As illustrated in Figure 30-13, the behavior of TXRDY and TXEMPTY status bits is modified by the programming of a timeguard. TXRDY rises only when the start bit of the next character is sent, and thus remains at 0 during the timeguard transmission if a character has been written in US\_THR. TXEMPTY remains low until the timeguard transmission is completed as the timeguard is part of the current character being transmitted.

#### Figure 30-13. Timeguard Operations

Table 30-7 indicates the maximum length of a timeguard period that the transmitter can handle in relation to the function of the Baud Rate.

| Baud Rate | Bit time | Timeguard |  |  |  |

|-----------|----------|-----------|--|--|--|

| Bit/sec   | μs       | ms        |  |  |  |

| 1 200     | 833      | 212.50    |  |  |  |

| 9 600     | 104      | 26.56     |  |  |  |

| 14400     | 69.4     | 17.71     |  |  |  |

Table 30-7.

Maximum Timeguard Length Depending on Baud Rate

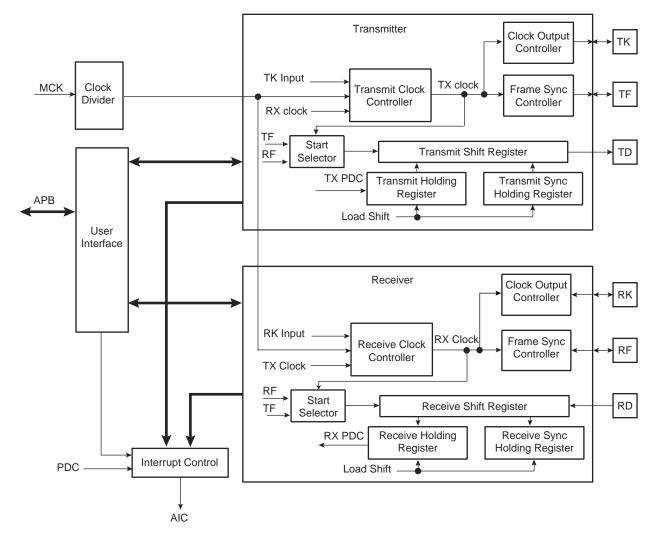

The receiver and transmitter operate separately. However, they can work synchronously by programming the receiver to use the transmit clock and/or to start a data transfer when transmission starts. Alternatively, this can be done by programming the transmitter to use the receive clock and/or to start a data transfer when reception starts. The transmitter and the receiver can be programmed to operate with the clock signals provided on either the TK or RK pins. This allows the SSC to support many slave-mode data transfers. The maximum clock speed allowed on the TK and RK pins is the master clock divided by 2.

#### 31.6.1 Clock Management

The transmitter clock can be generated by:

- an external clock received on the TK I/O pad

- the receiver clock

- the internal clock divider

The receiver clock can be generated by:

- an external clock received on the RK I/O pad

- the transmitter clock

- the internal clock divider

Atmel

# 31.8 Synchronous Serial Controller (SSC) User Interface

| Offset       | Register                                      | Name     | Access     | Reset      |

|--------------|-----------------------------------------------|----------|------------|------------|

| 0x0          | Control Register                              | SSC_CR   | Write      | _          |

| 0x4          | Clock Mode Register                           | SSC_CMR  | Read-write | 0x0        |

| 0x8          | Reserved                                      | -        | _          | -          |

| 0xC          | Reserved                                      | -        | _          | -          |

| 0x10         | Receive Clock Mode Register                   | SSC_RCMR | Read-write | 0x0        |

| 0x14         | Receive Frame Mode Register                   | SSC_RFMR | Read-write | 0x0        |

| 0x18         | Transmit Clock Mode Register                  | SSC_TCMR | Read-write | 0x0        |

| 0x1C         | Transmit Frame Mode Register                  | SSC_TFMR | Read-write | 0x0        |

| 0x20         | Receive Holding Register                      | SSC_RHR  | Read       | 0x0        |

| 0x24         | Transmit Holding Register                     | SSC_THR  | Write      | -          |

| 0x28         | Reserved                                      | _        | _          | _          |

| 0x2C         | Reserved                                      | -        | _          | -          |

| 0x30         | Receive Sync. Holding Register                | SSC_RSHR | Read       | 0x0        |

| 0x34         | Transmit Sync. Holding Register               | SSC_TSHR | Read-write | 0x0        |

| 0x38         | Receive Compare 0 Register                    | SSC_RC0R | Read-write | 0x0        |

| 0x3C         | Receive Compare 1 Register                    | SSC_RC1R | Read-write | 0x0        |

| 0x40         | Status Register                               | SSC_SR   | Read       | 0x000000CC |

| 0x44         | Interrupt Enable Register                     | SSC_IER  | Write      | _          |

| 0x48         | Interrupt Disable Register                    | SSC_IDR  | Write      | _          |

| 0x4C         | Interrupt Mask Register                       | SSC_IMR  | Read       | 0x0        |

| 0x50-0xFC    | Reserved                                      | -        | _          | _          |

| 0x100- 0x124 | Reserved for Peripheral Data Controller (PDC) | -        | -          | _          |

### Table 31-4.Register Mapping

#### 32.5.11.3 WAVSEL = 01

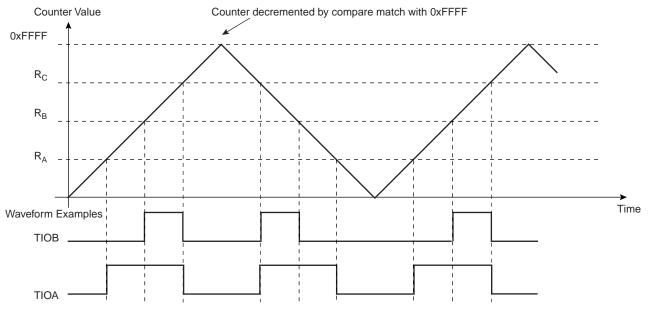

When WAVSEL = 01, the value of TC\_CV is incremented from 0 to 0xFFFF. Once 0xFFFF is reached, the value of TC\_CV is decremented to 0, then re-incremented to 0xFFFF and so on. See Figure 32-11.

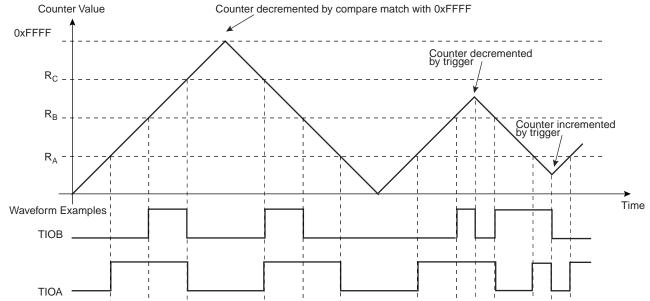

A trigger such as an external event or a software trigger can modify TC\_CV at any time. If a trigger occurs while TC\_CV is incrementing, TC\_CV then decrements. If a trigger is received while TC\_CV is decrementing, TC\_CV then increments. See Figure 32-12.

RC Compare cannot be programmed to generate a trigger in this configuration.

At the same time, RC Compare can stop the counter clock (CPCSTOP = 1) and/or disable the counter clock (CPCDIS = 1).

### Figure 32-11. WAVSEL = 01 Without Trigger

### 32.6.5 TC Channel Mode Register: Waveform Mode

Register Name:TC\_CMRx [x=0..2] (WAVE = 1)Access Type:Read-write

| 31     | 30      | 29            | 28   | 27     | 26 | 25      | 24     |  |

|--------|---------|---------------|------|--------|----|---------|--------|--|

| BSV    | /TRG    | BEEVT         |      | BCPC   |    | BCPB    |        |  |

| 23     | 22      | 21            | 20   | 19     | 18 | 17      | 16     |  |

| ASV    | /TRG    | A             | EEVT | T ACPC |    | ACPA    |        |  |

| 15     | 14      | 13            | 12   | 11     | 10 | 9       | 8      |  |

| WAVE   | WAW     | WAVSEL ENETRG |      | EEVT   |    | EEVTEDG |        |  |

| 7      | 6       | 5             | 4    | 3      | 2  | 1       | 0      |  |

| CPCDIS | CPCSTOP | BURST         |      | CLKI   |    | TCCLKS  | TCCLKS |  |

### • TCCLKS: Clock Selection

|   | TCCLKS |     |              |

|---|--------|-----|--------------|

| 0 | 0      | 0 0 |              |

| 0 | 0      | 1   | TIMER_CLOCK2 |

| 0 | 1      | 0   | TIMER_CLOCK3 |

| 0 | 1      | 1   | TIMER_CLOCK4 |

| 1 | 0      | 0   | TIMER_CLOCK5 |

| 1 | 0      | 1   | XC0          |

| 1 | 1      | 0   | XC1          |

| 1 | 1      | 1   | XC2          |

### • CLKI: Clock Invert

0 = Counter is incremented on rising edge of the clock.

1 = Counter is incremented on falling edge of the clock.

### • BURST: Burst Signal Selection

| BURST |   |                                               |  |

|-------|---|-----------------------------------------------|--|

| 0     | 0 | The clock is not gated by an external signal. |  |

| 0     | 1 | XC0 is ANDed with the selected clock.         |  |

| 1     | 0 | XC1 is ANDed with the selected clock.         |  |

| 1     | 1 | XC2 is ANDed with the selected clock.         |  |

### • CPCSTOP: Counter Clock Stopped with RC Compare

0 = Counter clock is not stopped when counter reaches RC.

1 = Counter clock is stopped when counter reaches RC.

### CPCDIS: Counter Clock Disable with RC Compare

0 = Counter clock is not disabled when counter reaches RC.

1 = Counter clock is disabled when counter reaches RC.

Atmel

### 34.6.5 UDP Interrupt Disable Register

| Register Name: | UDP_IC   | UDP_IDR |        |        |        |        |        |  |

|----------------|----------|---------|--------|--------|--------|--------|--------|--|

| Access Type:   | Write-on | lly     |        |        |        |        |        |  |

| 31             | 30       | 29      | 28     | 27     | 26     | 25     | 24     |  |

| -              | _        | -       | -      | -      | -      | -      | -      |  |

| 23             | 22       | 21      | 20     | 19     | 18     | 17     | 16     |  |

| -              | _        | _       | _      | _      | -      | _      | _      |  |

| 15             | 14       | 13      | 12     | 11     | 10     | 9      | 8      |  |

| -              | _        | WAKEUP  | —      | SOFINT | -      | RXRSM  | RXSUSP |  |

| 7              | 6        | 5       | 4      | 3      | 2      | 1      | 0      |  |

|                |          | EP5INT  | EP4INT | EP3INT | EP2INT | EP1INT | EP0INT |  |

- EP0INT: Disable Endpoint 0 Interrupt

- EP1INT: Disable Endpoint 1 Interrupt

- EP2INT: Disable Endpoint 2 Interrupt

- EP3INT: Disable Endpoint 3 Interrupt

- EP4INT: Disable Endpoint 4 Interrupt

- EP5INT: Disable Endpoint 5 Interrupt

- 0 = No effect.

- 1 = Disables corresponding Endpoint Interrupt.

- RXSUSP: Disable UDP Suspend Interrupt

- 0 = No effect.

- 1 = Disables UDP Suspend Interrupt.

### • RXRSM: Disable UDP Resume Interrupt

- 0 = No effect.

- 1 = Disables UDP Resume Interrupt.

### • SOFINT: Disable Start Of Frame Interrupt

- 0 = No effect.

- 1 = Disables Start Of Frame Interrupt

### • WAKEUP: Disable USB Bus Interrupt

- 0 = No effect.

- 1 = Disables USB Bus Wakeup Interrupt.

### 34.6.8 UDP Interrupt Clear Register

| Register Name: | : UDP_IC | R      |           |        |    |       |        |

|----------------|----------|--------|-----------|--------|----|-------|--------|

| Access Type:   | Write-on | ly     |           |        |    |       |        |

| 31             | 30       | 29     | 28        | 27     | 26 | 25    | 24     |

| -              | -        | —      | -         | -      | -  | -     | -      |

| 23             | 22       | 21     | 20        | 19     | 18 | 17    | 16     |

| -              | _        | _      | -         | _      | -  | _     | -      |

| 15             | 14       | 13     | 12        | 11     | 10 | 9     | 8      |

| -              | -        | WAKEUP | ENDBUSRES | SOFINT | -  | RXRSM | RXSUSP |

| 7              | 6        | 5      | 4         | 3      | 2  | 1     | 0      |

| _              | -        | _      | -         | _      | -  | -     | -      |

### RXSUSP: Clear UDP Suspend Interrupt

0 = No effect.

1 = Clears UDP Suspend Interrupt.

### • RXRSM: Clear UDP Resume Interrupt

0 = No effect.

1 = Clears UDP Resume Interrupt.

### • SOFINT: Clear Start Of Frame Interrupt

0 = No effect.

1 = Clears Start Of Frame Interrupt.

### • ENDBUSRES: Clear End of Bus Reset Interrupt

0 = No effect.

1 = Clears End of Bus Reset Interrupt.

### • WAKEUP: Clear Wakeup Interrupt

0 = No effect.

1 = Clears Wakeup Interrupt.

#### 36.7.3.5 Transmission Handling

A mailbox is in Transmit Mode once the MOT field in the CAN\_MMRx register has been configured. Message ID and Message Acceptance mask must be set before Receive Mode is enabled.

After Transmit Mode is enabled, the MRDY flag in the CAN\_MSR register is automatically set until the first command is sent. When the MRDY flag is set, the software application can prepare a message to be sent by writing to the CAN\_MDx registers. The message is sent once the software asks for a transfer command setting the MTCR bit and the message data length in the CAN\_MCRx register.

The MRDY flag remains at zero as long as the message has not been sent or aborted. It is important to note that no access to the mailbox data register is allowed while the MRDY flag is cleared. An interrupt is pending for the mailbox while the MRDY flag is set. This interrupt can be masked depending on the mailbox flag in the CAN\_IMR global register.

It is also possible to send a remote frame setting the MRTR bit instead of setting the MDLC field. The answer to the remote frame is handled by another reception mailbox. In this case, the device acts as a consumer but with the help of two mailboxes. It is possible to handle the remote frame emission and the answer reception using only one mailbox configured in Consumer Mode. Refer to the section "Remote Frame Handling" on page 501.

Several messages can try to win the bus arbitration in the same time. The message with the highest priority is sent first. Several transfer request commands can be generated at the same time by setting MBx bits in the CAN\_TCR register. The priority is set in the PRIOR field of the CAN\_MMRx register. Priority 0 is the highest priority, priority 15 is the lowest priority. Thus it is possible to use a part of the message ID to set the PRIOR field. If two mailboxes have the same priority, the message of the mailbox with the lowest number is sent first. Thus if mailbox 0 and mailbox 5 have the same priority and have a message to send at the same time, then the message of the mailbox 0 is sent first.

Setting the MACR bit in the CAN\_MCRx register aborts the transmission. Transmission for several mailboxes can be aborted by writing MBx fields in the CAN\_MACR register. If the message is being sent when the abort command is set, then the application is notified by the MRDY bit set and not the MABT in the CAN\_MSRx register. Otherwise, if the message has not been sent, then the MRDY and the MABT are set in the CAN\_MSR register.

When the bus arbitration is lost by a mailbox message, the CAN controller tries to win the next bus arbitration with the same message if this one still has the highest priority. Messages to be sent are re-tried automatically until they win the bus arbitration. This feature can be disabled by setting the bit DRPT in the CAN\_MR register. In this case if the message was not sent the first time it was transmitted to the CAN transceiver, it is automatically aborted. The MABT flag is set in the CAN\_MSRx register until the next transfer command.

Figure 36-15 shows three MBx message attempts being made (MRDY of MBx set to 0).

The first MBx message is sent, the second is aborted and the last one is trying to be aborted but too late because it has already been transmitted to the CAN transceiver.

### • MMI: Mailbox Message Ignored

0 = No message has been ignored during the previous transfer

1 = At least one message has been ignored during the previous transfer

Cleared by reading the CAN\_MSRx register.

| Mailbox Object Type    | Description                                                                                                                                                                                                                                  |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive                | Set when at least two messages intended for the mailbox have been sent. The first one is available in the mailbox data register. Others have been ignored. A mailbox with a lower priority may have accepted the message.                    |

| Receive with overwrite | Set when at least two messages intended for the mailbox have been sent. The last one is available in the mailbox data register. Previous ones have been lost.                                                                                |

| Transmit               | Reserved                                                                                                                                                                                                                                     |

| Consumer               | A remote frame has been sent by the mailbox but several messages have been received. The first one is available in the mailbox data register. Others have been ignored. Another mailbox with a lower priority may have accepted the message. |

| Producer               | A remote frame has been received, but no data are available to be sent.                                                                                                                                                                      |

# Table 37-6. Register Mapping (Continued)

| Offset      | Register                             | Name       | Access     | Reset       |

|-------------|--------------------------------------|------------|------------|-------------|

| 0x90        | Hash Register Bottom [31:0] Register | EMAC_HRB   | Read-write | 0x0000_0000 |

| 0x94        | Hash Register Top [63:32] Register   | EMAC_HRT   | Read-write | 0x0000_0000 |

| 0x98        | Specific Address 1 Bottom Register   | EMAC_SA1B  | Read-write | 0x0000_0000 |

| 0x9C        | Specific Address 1 Top Register      | EMAC_SA1T  | Read-write | 0x0000_0000 |

| 0xA0        | Specific Address 2 Bottom Register   | EMAC_SA2B  | Read-write | 0x0000_0000 |

| 0xA4        | Specific Address 2 Top Register      | EMAC_SA2T  | Read-write | 0x0000_0000 |

| 0xA8        | Specific Address 3 Bottom Register   | EMAC_SA3B  | Read-write | 0x0000_0000 |

| 0xAC        | Specific Address 3 Top Register      | EMAC_SA3T  | Read-write | 0x0000_0000 |

| 0xB0        | Specific Address 4 Bottom Register   | EMAC_SA4B  | Read-write | 0x0000_0000 |

| 0xB4        | Specific Address 4 Top Register      | EMAC_SA4T  | Read-write | 0x0000_0000 |

| 0xB8        | Type ID Checking Register            | EMAC_TID   | Read-write | 0x0000_0000 |

| 0xC0        | User Input/output Register           | EMAC_USRIO | Read-write | 0x0000_0000 |

| 0xC8-0xF8   | Reserved                             | -          | _          | -           |

| 0xC8 - 0xFC | Reserved                             | -          | _          | -           |

### 37.5.3 Network Status Register

| Register Name:<br>Access Type: | EMAC_N<br>Read-on |    |    |    |      |      |    |

|--------------------------------|-------------------|----|----|----|------|------|----|

| 31                             | 30                | 29 | 28 | 27 | 26   | 25   | 24 |

| -                              | _                 | —  | -  | -  | -    | —    | —  |

| 23                             | 22                | 21 | 20 | 19 | 18   | 17   | 16 |

| -                              | _                 | _  | -  | _  | _    | _    | _  |

| 15                             | 14                | 13 | 12 | 11 | 10   | 9    | 8  |

| -                              | _                 | _  | -  | _  | -    | -    | —  |

| 7                              | 6                 | 5  | 4  | 3  | 2    | 1    | 0  |

| -                              | _                 | _  | -  | -  | IDLE | MDIO | -  |

### • MDIO

Returns status of the MDIO pin. Use the PHY maintenance register for reading managed frames rather than this bit.

### • IDLE

0 = The PHY logic is running.

1 = The PHY management logic is idle (i.e., has completed).