Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                      |

|----------------------------|---------------------------------------------------------------|

| Core Processor             | ARM7®                                                         |

| Core Size                  | 16/32-Bit                                                     |

| Speed                      | 55MHz                                                         |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                    |

| Number of I/O              | 62                                                            |

| Program Memory Size        | 256KB (256K x 8)                                              |

| Program Memory Type        | FLASH                                                         |

| EEPROM Size                | -                                                             |

| RAM Size                   | 64K x 8                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                 |

| Data Converters            | A/D 8x10b                                                     |

| Oscillator Type            | Internal                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                             |

| Mounting Type              | Surface Mount                                                 |

| Package / Case             | 100-TFBGA                                                     |

| Supplier Device Package    | 100-TFBGA (9x9)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/at91sam7x256b-cu   |

|                            |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6.6 I/O Lines Current Drawing

The PIO lines PA0 to PA3 are high-drive current capable. Each of these I/O lines can drive up to 16 mA permanently. The remaining I/O lines can draw only 8 mA.

However, the total current drawn by all the I/O lines cannot exceed 200 mA.

- Embedded Flash Controller

- Embedded Flash interface, up to three programmable wait states

- Prefetch buffer, buffering and anticipating the 16-bit requests, reducing the required wait states

- Key-protected program, erase and lock/unlock sequencer

- Single command for erasing, programming and locking operations

- Interrupt generation in case of forbidden operation

## 7.4 Peripheral DMA Controller

- Handles data transfer between peripherals and memories

- Thirteen channels

- Two for each USART

- Two for the Debug Unit

- Two for the Serial Synchronous Controller

- Two for each Serial Peripheral Interface

- One for the Analog-to-digital Converter

- Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirements

- Peripheral DMA Controller (PDC) priority is as follows (from the highest priority to the lowest):

| Receive  | DBGU   |

|----------|--------|

| Receive  | USART0 |

| Receive  | USART1 |

| Receive  | SSC    |

| Receive  | ADC    |

| Receive  | SPI0   |

| Receive  | SPI1   |

| Transmit | DBGU   |

| Transmit | USART0 |

| Transmit | USART  |

| Transmit | SSC    |

| Transmit | SPI0   |

| Transmit | SPI1   |

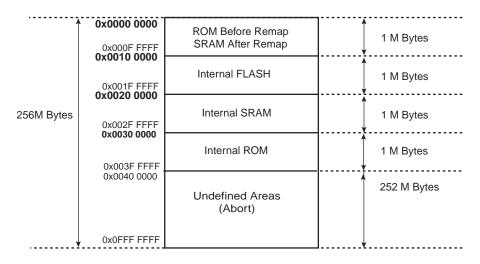

# 8.4 Memory Mapping

#### 8.4.1 Internal SRAM

- The SAM7X512 embeds a high-speed 128-Kbyte SRAM bank.

- The SAM7X256 embeds a high-speed 64-Kbyte SRAM bank.

- The SAM7X128 embeds a high-speed 32-Kbyte SRAM bank.

After reset and until the Remap Command is performed, the SRAM is only accessible at address 0x0020 0000. After Remap, the SRAM also becomes available at address 0x0.

#### 8.4.2 Internal ROM

The SAM7X512/256/128 embeds an Internal ROM. At any time, the ROM is mapped at address 0x30 0000. The ROM contains the FFPI and the SAM-BA program.

#### 8.4.3 Internal Flash

- The SAM7X512 features two banks (dual plane) of 256 Kbytes of Flash.

- The SAM7X256 features one bank (single plane) of 256 Kbytes of Flash.

- The SAM7X128 features one bank (single plane) of 128 Kbytes of Flash.

At any time, the Flash is mapped to address 0x0010 0000. It is also accessible at address 0x0 after the reset, if GPNVM bit 2 is set and before the Remap Command.

A general purpose NVM (GPNVM) bit is used to boot either on the ROM (default) or from the Flash.

This GPNVM bit can be cleared or set respectively through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EFC User Interface.

Setting the GPNVM Bit 2 selects the boot from the Flash. Asserting ERASE clears the GPNVM Bit 2 and thus selects the boot from the ROM by default.

#### Figure 8-2. Internal Memory Mapping with GPNVM Bit 2 = 0 (default)

# 10. Peripherals

## 10.1 User Interface

The User Peripherals are mapped in the 256 Mbytes of address space between 0xF000 0000 and 0xFFFF EFFF. Each peripheral is allocated 16 Kbytes of address space.

A complete memory map is provided in Figure 8-1 on page 18.

# 10.2 Peripheral Identifiers

The SAM7X512/256/128 embeds a wide range of peripherals. Table 10-1 defines the Peripheral Identifiers of the SAM7X512/256/128. Unique peripheral identifiers are defined for both the Advanced Interrupt Controller and the Power Management Controller.

| Peripheral ID | Peripheral Mnemonic | Peripheral Name                   | External<br>Interrupt |

|---------------|---------------------|-----------------------------------|-----------------------|

| 0             | AIC                 | Advanced Interrupt Controller     | FIQ                   |

| 1             | SYSC <sup>(1)</sup> | System Controller                 |                       |

| 2             | PIOA                | Parallel I/O Controller A         |                       |

| 3             | PIOB                | Parallel I/O Controller B         |                       |

| 4             | SPI0                | Serial Peripheral Interface 0     |                       |

| 5             | SPI1                | Serial Peripheral Interface 1     |                       |

| 6             | US0                 | USART 0                           |                       |

| 7             | US1                 | USART 1                           |                       |

| 8             | SSC                 | Synchronous Serial Controller     |                       |

| 9             | TWI                 | Two-wire Interface                |                       |

| 10            | PWMC                | Pulse Width Modulation Controller |                       |

| 11            | UDP                 | USB Device Port                   |                       |

| 12            | TC0                 | Timer/Counter 0                   |                       |

| 13            | TC1                 | Timer/Counter 1                   |                       |

| 14            | TC2                 | Timer/Counter 2                   |                       |

| 15            | CAN                 | CAN Controller                    |                       |

| 16            | EMAC                | Ethernet MAC                      |                       |

| 17            | ADC <sup>(1)</sup>  | Analog-to Digital Converter       |                       |

| 18 - 29       | Reserved            |                                   |                       |

| 30            | AIC                 | Advanced Interrupt Controller     | IRQ0                  |

| 31            | AIC                 | Advanced Interrupt Controller     | IRQ1                  |

Table 10-1.Peripheral Identifiers

Note: 1. Setting SYSC and ADC bits in the clock set/clear registers of the PMC has no effect. The System Controller and ADC are continuously clocked.

# 16.4 Watchdog Timer (WDT) User Interface

| Offset | Register         | Name   | Access          | Reset Value |

|--------|------------------|--------|-----------------|-------------|

| 0x00   | Control Register | WDT_CR | Write-only      | -           |

| 0x04   | Mode Register    | WDT_MR | Read-write Once | 0x3FFF_2FFF |

| 0x08   | Status Register  | WDT_SR | Read-only       | 0x0000_0000 |

#### Table 16-1.Register Mapping

# 16.4.1 Watchdog Timer Control Register

| Register Name | : WDT_CI | R   |    |    |    |    |        |

|---------------|----------|-----|----|----|----|----|--------|

| Access Type:  | Write-or | nly |    |    |    |    |        |

| 31            | 30       | 29  | 28 | 27 | 26 | 25 | 24     |

|               |          |     | K  | EY |    |    |        |

| 23            | 22       | 21  | 20 | 19 | 18 | 17 | 16     |

| _             | -        | -   | -  | -  | -  | -  | -      |

| 15            | 14       | 13  | 12 | 11 | 10 | 9  | 8      |

| _             | -        | _   | -  | _  | -  | -  | -      |

| 7             | 6        | 5   | 4  | 3  | 2  | 1  | 0      |

| _             | -        | _   | —  | _  | -  | _  | WDRSTT |

# • WDRSTT: Watchdog Restart

0: No effect.

1: Restarts the Watchdog.

#### • KEY: Password

Should be written at value 0xA5. Writing any other value in this field aborts the write operation.

# 18.4 Memory Controller (MC) User Interface

Base Address: 0xFFFFF00

#### Table 18-1.Register Mapping

| Offset    | Register                                    | Name       | Access                                    | Reset State |  |  |  |

|-----------|---------------------------------------------|------------|-------------------------------------------|-------------|--|--|--|

| 0x00      | MC Remap Control Register                   | MC_RCR     | Write-only                                |             |  |  |  |

| 0x04      | MC Abort Status Register                    | MC_ASR     | Read-only                                 | 0x0         |  |  |  |

| 0x08      | MC Abort Address Status Register            | MC_AASR    | Read-only                                 | 0x0         |  |  |  |

| 0x10-0x5C | Reserved                                    |            |                                           |             |  |  |  |

| 0x60      | EFC0 Configuration Registers                |            |                                           |             |  |  |  |

| 0x70      | EFC1 <sup>(1)</sup> Configuration Registers | See the Ei | See the Embedded Flash Controller Section |             |  |  |  |

Note: 1. EFC1 pertains to AT91SAM7X512 only.

The size of the buffer (number of transfers) is configured in an internal 16-bit transfer counter register, and it is possible, at any moment, to read the number of transfers left for each channel.

The memory base address is configured in a 32-bit memory pointer by defining the location of the first address to access in the memory. It is possible, at any moment, to read the location in memory of the next transfer and the number of remaining transfers. The PDC has dedicated status registers which indicate if the transfer is enabled or disabled for each channel. The status for each channel is located in the peripheral status register. Transfers can be enabled and/or disabled by setting TXTEN/TXTDIS and RXTEN/RXTDIS in PDC Transfer Control Register. These control bits enable reading the pointer and counter registers safely without any risk of their changing between both reads.

The PDC sends status flags to the peripheral visible in its status-register (ENDRX, ENDTX, RXBUFF, and TXBUFE).

ENDRX flag is set when the PERIPH\_RCR register reaches zero.

RXBUFF flag is set when both PERIPH\_RCR and PERIPH\_RNCR reach zero.

ENDTX flag is set when the PERIPH\_TCR register reaches zero.

TXBUFE flag is set when both PERIPH\_TCR and PERIPH\_TNCR reach zero.

These status flags are described in the peripheral status register.

#### 22.3.2 Memory Pointers

Each peripheral is connected to the PDC by a receiver data channel and a transmitter data channel. Each channel has an internal 32-bit memory pointer. Each memory pointer points to a location anywhere in the memory space (on-chip memory or external bus interface memory).

Depending on the type of transfer (byte, half-word or word), the memory pointer is incremented by 1, 2 or 4, respectively for peripheral transfers.

If a memory pointer is reprogrammed while the PDC is in operation, the transfer address is changed, and the PDC performs transfers using the new address.

#### 22.3.3 Transfer Counters

There is one internal 16-bit transfer counter for each channel used to count the size of the block already transferred by its associated channel. These counters are decremented after each data transfer. When the counter reaches zero, the transfer is complete and the PDC stops transferring data.

If the Next Counter Register is equal to zero, the PDC disables the trigger while activating the related peripheral end flag.

If the counter is reprogrammed while the PDC is operating, the number of transfers is updated and the PDC counts transfers from the new value.

Programming the Next Counter/Pointer registers chains the buffers. The counters are decremented after each data transfer as stated above, but when the transfer counter reaches zero, the values of the Next Counter/Pointer are loaded into the Counter/Pointer registers in order to re-enable the triggers.

For each channel, two status bits indicate the end of the current buffer (ENDRX, ENTX) and the end of both current and next buffer (RXBUFF, TXBUFE). These bits are directly mapped to the peripheral status register and can trigger an interrupt request to the AIC.

The peripheral end flag is automatically cleared when one of the counter-registers (Counter or Next Counter Register) is written.

Note: When the Next Counter Register is loaded into the Counter Register, it is set to zero.

#### 22.3.4 Data Transfers

The peripheral triggers PDC transfers using transmit (TXRDY) and receive (RXRDY) signals.

When the peripheral receives an external character, it sends a Receive Ready signal to the PDC which then requests access to the system bus. When access is granted, the PDC starts a read of the peripheral Receive Holding Register (RHR) and then triggers a write in the memory.

# Atmel

Moreover, like the PCK, a status bitin PMC\_SR indicates that the Programmable Clock is actually what has been programmed in the Programmable Clock registers.

As the Programmable Clock Controller does not manage with glitch prevention when switching clocks, it is strongly recommended to disable the Programmable Clock before any configuration change and to re-enable it after the change is actually performed.

# 25.7 Programming Sequence

1. Enabling the Main Oscillator:

The main oscillator is enabled by setting the MOSCEN field in the CKGR\_MOR register. In some cases it may be advantageous to define a start-up time. This can be achieved by writing a value in the OSCOUNT field in the CKGR\_MOR register.

Once this register has been correctly configured, the user must wait for MOSCS field in the PMC\_SR register to be set. This can be done either by polling the status register or by waiting the interrupt line to be raised if the associated interrupt to MOSCS has been enabled in the PMC\_IER register.

Code Example:

write\_register(CKGR\_MOR,0x0000701)

Start Up Time = 8 \* OSCOUNT / SLCK = 56 Slow Clock Cycles.

So, the main oscillator will be enabled (MOSCS bit set) after 56 Slow Clock Cycles.

2. Checking the Main Oscillator Frequency (Optional):

In some situations the user may need an accurate measure of the main oscillator frequency. This measure can be accomplished via the CKGR\_MCFR register.

Once the MAINRDY field is set in CKGR\_MCFR register, the user may read the MAINF field in CKGR\_MCFR register. This provides the number of main clock cycles within sixteen slow clock cycles.

3. Setting PLL and divider:

All parameters needed to configure PLL and the divider are located in the CKGR\_PLLR register.

The DIV field is used to control divider itself. A value between 0 and 255 can be programmed. Divider output is divider input divided by DIV parameter. By default DIV parameter is set to 0 which means that divider is turned off.

The OUT field is used to select the PLL B output frequency range.

The MUL field is the PLL multiplier factor. This parameter can be programmed between 0 and 2047. If MUL is set to 0, PLL will be turned off, otherwise the PLL output frequency is PLL input frequency multiplied by (MUL + 1).

The PLLCOUNT field specifies the number of slow clock cycles before LOCK bit is set in the PMC\_SR register after CKGR\_PLLR register has been written.

Once the PMC\_PLL register has been written, the user must wait for the LOCK bit to be set in the PMC\_SR register. This can be done either by polling the status register or by waiting the interrupt line to be raised if the associated interrupt to LOCK has been enabled in the PMC\_IER register. All parameters in CKGR\_PLLR can be programmed in a single write operation. If at some stage one of the following parameters, MUL, DIV is modified, LOCK bit will go low to indicate that PLL is not ready yet. When PLL is locked, LOCK will be set again. The user is constrained to wait for LOCK bit to be set before using the PLL output clock.

The USBDIV field is used to control the additional divider by 1, 2 or 4, which generates the USB clock(s).

Code Example:

## 25.9.7 PMC Clock Generator Main Oscillator Register

| Register Name: | CKGR_MOR |     |      |      |    |           |        |

|----------------|----------|-----|------|------|----|-----------|--------|

| Access Type:   | Read-wr  | ite |      |      |    |           |        |

| 31             | 30       | 29  | 28   | 27   | 26 | 25        | 24     |

| -              | _        | _   | _    | _    | _  | -         | _      |

| 23             | 22       | 21  | 20   | 19   | 18 | 17        | 16     |

| -              | _        | _   | _    | _    | _  | _         | -      |

| 15             | 14       | 13  | 12   | 11   | 10 | 9         | 8      |

|                |          |     | OSCO | JUNT |    |           |        |

| 7              | 6        | 5   | 4    | 3    | 2  | 1         | 0      |

| _              | -        | _   | _    | _    | _  | OSCBYPASS | MOSCEN |

#### • MOSCEN: Main Oscillator Enable

A crystal must be connected between XIN and XOUT.

0 = The Main Oscillator is disabled.

1 = The Main Oscillator is enabled. OSCBYPASS must be set to 0.

When MOSCEN is set, the MOSCS flag is set once the Main Oscillator startup time is achieved.

#### • OSCBYPASS: Oscillator Bypass

0 = No effect.

1 = The Main Oscillator is bypassed. MOSCEN must be set to 0. An external clock must be connected on XIN.

When OSCBYPASS is set, the MOSCS flag in PMC\_SR is automatically set.

Clearing MOSCEN and OSCBYPASS bits allows resetting the MOSCS flag.

#### • OSCOUNT: Main Oscillator Start-up Time

Specifies the number of Slow Clock cycles multiplied by 8 for the Main Oscillator start-up time.

### 26.5.5 Debug Unit Interrupt Mask Register

Nama

| Name:        | DBG0_I  | MR   |        |        |    |         |       |

|--------------|---------|------|--------|--------|----|---------|-------|

| Access Type: | Read-on | ly   |        |        |    |         |       |

| 31           | 30      | 29   | 28     | 27     | 26 | 25      | 24    |

| COMMRX       | COMMTX  | _    | _      | _      | _  | _       | _     |

| 23           | 22      | 21   | 20     | 19     | 18 | 17      | 16    |

| _            | _       | _    | _      | _      | _  | —       | _     |

| 15           | 14      | 13   | 12     | 11     | 10 | 9       | 8     |

| _            | _       | _    | RXBUFF | TXBUFE | —  | TXEMPTY | _     |

| 7            | 6       | 5    | 4      | 3      | 2  | 1       | 0     |

| PARE         | FRAME   | OVRE | ENDTX  | ENDRX  | _  | TXRDY   | RXRDY |

| -            |         |      | -      | •      | -  | -       | -     |

- RXRDY: Mask RXRDY Interrupt

- TXRDY: Disable TXRDY Interrupt

- ENDRX: Mask End of Receive Transfer Interrupt

- ENDTX: Mask End of Transmit Interrupt

- OVRE: Mask Overrun Error Interrupt

- FRAME: Mask Framing Error Interrupt

- PARE: Mask Parity Error Interrupt

- TXEMPTY: Mask TXEMPTY Interrupt

- TXBUFE: Mask TXBUFE Interrupt

- RXBUFF: Mask RXBUFF Interrupt

- COMMTX: Mask COMMTX Interrupt

#### • COMMRX: Mask COMMRX Interrupt

0 = The corresponding interrupt is disabled.

1 = The corresponding interrupt is enabled.

# Atmel

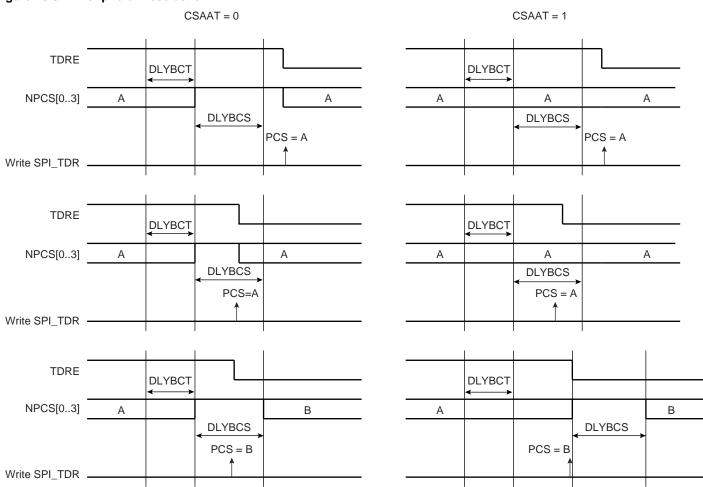

Figure 28-8. Peripheral Deselection

#### 28.6.3.8 Mode Fault Detection

A mode fault is detected when the SPI is programmed in Master Mode and a low level is driven by an external master on the NPCS0/NSS signal. NPCS0, MOSI, MISO and SPCK must be configured in open drain through the PIO controller, so that external pull up resistors are needed to guarantee high level.

When a mode fault is detected, the MODF bit in the SPI\_SR is set until the SPI\_SR is read and the SPI is automatically disabled until re-enabled by writing the SPIEN bit in the SPI\_CR (Control Register) at 1.

By default, the Mode Fault detection circuitry is enabled. The user can disable Mode Fault detection by setting the MODFDIS bit in the SPI Mode Register (SPI\_MR).

#### 28.6.4 SPI Slave Mode

When operating in Slave Mode, the SPI processes data bits on the clock provided on the SPI clock pin (SPCK).

The SPI waits for NSS to go active before receiving the serial clock from an external master. When NSS falls, the clock is validated on the serializer, which processes the number of bits defined by the BITS field of the Chip Select Register 0 (SPI\_CSR0). These bits are processed following a phase and a polarity defined respectively by the NCPHA and CPOL bits of the SPI\_CSR0. Note that BITS, CPOL and NCPHA of the other Chip Select Registers have no effect when the SPI is programmed in Slave Mode.

The bits are shifted out on the MISO line and sampled on the MOSI line.

When all the bits are processed, the received data is transferred in the Receive Data Register and the RDRF bit rises. If the SPI\_RDR (Receive Data Register) has not been read before new data is received, the Overrun Error bit (OVRES) in

# Atmel

#### 30.6.3.6 Multidrop Mode

If the PAR field in the Mode Register (US\_MR) is programmed to the value 0x6 or 0x07, the USART runs in Multidrop Mode. This mode differentiates the data characters and the address characters. Data is transmitted with the parity bit at 0 and addresses are transmitted with the parity bit at 1.

If the USART is configured in multidrop mode, the receiver sets the PARE parity error bit when the parity bit is high and the transmitter is able to send a character with the parity bit high when the Control Register is written with the SENDA bit at 1.

To handle parity error, the PARE bit is cleared when the Control Register is written with the bit RSTSTA at 1.

The transmitter sends an address byte (parity bit set) when SENDA is written to US\_CR. In this case, the next byte written to US\_THR is transmitted as an address. Any character written in US\_THR without having written the command SENDA is transmitted normally with the parity at 0.

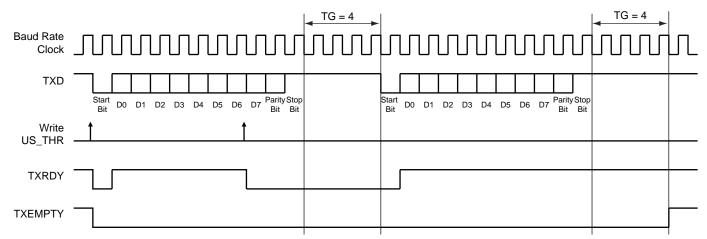

#### 30.6.3.7 Transmitter Timeguard

The timeguard feature enables the USART interface with slow remote devices.

The timeguard function enables the transmitter to insert an idle state on the TXD line between two characters. This idle state actually acts as a long stop bit.

The duration of the idle state is programmed in the TG field of the Transmitter Timeguard Register (US\_TTGR). When this field is programmed at zero no timeguard is generated. Otherwise, the transmitter holds a high level on TXD after each transmitted byte during the number of bit periods programmed in TG in addition to the number of stop bits.

As illustrated in Figure 30-13, the behavior of TXRDY and TXEMPTY status bits is modified by the programming of a timeguard. TXRDY rises only when the start bit of the next character is sent, and thus remains at 0 during the timeguard transmission if a character has been written in US\_THR. TXEMPTY remains low until the timeguard transmission is completed as the timeguard is part of the current character being transmitted.

#### Figure 30-13. Timeguard Operations

Table 30-7 indicates the maximum length of a timeguard period that the transmitter can handle in relation to the function of the Baud Rate.

| Baud Rate | Bit time | Timeguard |  |  |  |

|-----------|----------|-----------|--|--|--|

| Bit/sec   | μs       | ms        |  |  |  |

| 1 200     | 833      | 212.50    |  |  |  |

| 9 600     | 104      | 26.56     |  |  |  |

| 14400     | 69.4     | 17.71     |  |  |  |

Table 30-7.

Maximum Timeguard Length Depending on Baud Rate

#### • CP0: Compare 0 Interrupt Mask

0: The Compare 0 Interrupt is disabled.

1: The Compare 0 Interrupt is enabled.

#### • CP1: Compare 1 Interrupt Mask

0: The Compare 1 Interrupt is disabled.

1: The Compare 1 Interrupt is enabled.

## • TXSYN: Tx Sync Interrupt Mask

0: The Tx Sync Interrupt is disabled.

1: The Tx Sync Interrupt is enabled.

## • RXSYN: Rx Sync Interrupt Mask

0: The Rx Sync Interrupt is disabled.

1: The Rx Sync Interrupt is enabled.

# 33.3 I/O Lines Description

Each channel outputs one waveform on one external I/O line.

| Table 33-1. | I/O Line Description |

|-------------|----------------------|

|-------------|----------------------|

| Name | Description                       | Туре   |

|------|-----------------------------------|--------|

| PWMx | PWM Waveform Output for channel x | Output |

### 33.4 Product Dependencies

#### 33.4.1 I/O Lines

The pins used for interfacing the PWM may be multiplexed with PIO lines. The programmer must first program the PIO controller to assign the desired PWM pins to their peripheral function. If I/O lines of the PWM are not used by the application, they can be used for other purposes by the PIO controller.

All of the PWM outputs may or may not be enabled. If an application requires only four channels, then only four PIO lines will be assigned to PWM outputs.

#### 33.4.2 Power Management

The PWM is not continuously clocked. The programmer must first enable the PWM clock in the Power Management Controller (PMC) before using the PWM. However, if the application does not require PWM operations, the PWM clock can be stopped when not needed and be restarted later. In this case, the PWM will resume its operations where it left off.

Configuring the PWM does not require the PWM clock to be enabled.

#### 33.4.3 Interrupt Sources

The PWM interrupt line is connected on one of the internal sources of the Advanced Interrupt Controller. Using the PWM interrupt requires the AIC to be programmed first. Note that it is not recommended to use the PWM interrupt line in edge sensitive mode.

#### 33.5 Functional Description

The PWM macrocell is primarily composed of a clock generator module and 4 channels.

- Clocked by the system clock, MCK, the clock generator module provides 13 clocks.

- Each channel can independently choose one of the clock generator outputs.

- Each channel generates an output waveform with attributes that can be defined independently for each channel through the user interface registers.

## 33.6.13 PWM Channel Update Register

| Register Name: | PWM_CUPD[0X-1] |     |    |    |    |    |    |  |

|----------------|----------------|-----|----|----|----|----|----|--|

| Access Type:   | Write-or       | hly |    |    |    |    |    |  |

| 31             | 30             | 29  | 28 | 27 | 26 | 25 | 24 |  |

|                |                |     | CU | PD |    |    |    |  |

| 23             | 22             | 21  | 20 | 19 | 18 | 17 | 16 |  |

|                |                |     | CU | PD |    |    |    |  |

| 15             | 14             | 13  | 12 | 11 | 10 | 9  | 8  |  |

|                |                |     | CU | PD |    |    |    |  |

| 7              | 6              | 5   | 4  | 3  | 2  | 1  | 0  |  |

|                | CUPD           |     |    |    |    |    |    |  |

This register acts as a double buffer for the period or the duty cycle. This prevents an unexpected waveform when modifying the waveform period or duty-cycle.

Only the first 16 bits (internal channel counter size) are significant.

| CPD (PWM_CMRx Register) |                                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|

| 0                       | The duty-cycle (CDTY in the PWM_CDTYx register) is updated with the CUPD value at the beginning of the next period. |

| 1                       | The period (CPRD in the PWM_CPRDx register) is updated with the CUPD value at the beginning of the next period.     |

#### 37.3.11 PHY Maintenance

The register EMAC\_MAN enables the EMAC to communicate with a PHY by means of the MDIO interface. It is used during auto-negotiation to ensure that the EMAC and the PHY are configured for the same speed and duplex configuration.

The PHY maintenance register is implemented as a shift register. Writing to the register starts a shift operation which is signalled as complete when bit two is set in the network status register (about 2000 MCK cycles later when bit ten is set to zero, and bit eleven is set to one in the network configuration register). An interrupt is generated as this bit is set. During this time, the MSB of the register is output on the MDIO pin and the LSB updated from the MDIO pin with each MDC cycle. This causes transmission of a PHY management frame on MDIO.

Reading during the shift operation returns the current contents of the shift register. At the end of management operation, the bits have shifted back to their original locations. For a read operation, the data bits are updated with data read from the PHY. It is important to write the correct values to the register to ensure a valid PHY management frame is produced.

The MDIO interface can read IEEE 802.3 clause 45 PHYs as well as clause 22 PHYs. To read clause 45 PHYs, bits[31:28] should be written as 0x0011. For a description of MDC generation, see the network configuration register in the "Network Control Register" on page 550.

#### 37.3.12 Media Independent Interface

The Ethernet MAC is capable of interfacing to both RMII and MII Interfaces. The RMII bit in the EMAC\_USRIO register controls the interface that is selected. When this bit is set, the RMII interface is selected, else the MII interface is selected.

The MII and RMII interface are capable of both 10Mb/s and 100Mb/s data rates as described in the IEEE 802.3u standard. The signals used by the MII and RMII interfaces are described in Table 37-5.

| Pin Name     | MII                              | RMII                             |

|--------------|----------------------------------|----------------------------------|

| ETXCK_EREFCK | ETXCK: Transmit Clock            | EREFCK: Reference Clock          |

| ECRS         | ECRS: Carrier Sense              |                                  |

| ECOL         | ECOL: Collision Detect           |                                  |

| ERXDV        | ERXDV: Data Valid                | ECRSDV: Carrier Sense/Data Valid |

| ERX0 - ERX3  | ERX0 - ERX3: 4-bit Receive Data  | ERX0 - ERX1: 2-bit Receive Data  |

| ERXER        | ERXER: Receive Error             | ERXER: Receive Error             |

| ERXCK        | ERXCK: Receive Clock             |                                  |

| ETXEN        | ETXEN: Transmit Enable           | ETXEN: Transmit Enable           |

| ETX0-ETX3    | ETX0 - ETX3: 4-bit Transmit Data | ETX0 - ETX1: 2-bit Transmit Data |

| ETXER        | ETXER: Transmit Error            |                                  |

#### Table 37-5.Pin Configuration

The intent of the RMII is to provide a reduced pin count alternative to the IEEE 802.3u MII. It uses 2 bits for transmit (ETX0 and ETX1) and two bits for receive (ERX0 and ERX1). There is a Transmit Enable (ETXEN), a Receive Error (ERXER), a Carrier Sense (ECRS\_DV), and a 50 MHz Reference Clock (ETXCK\_EREFCK) for 100Mb/s data rate.

#### 37.3.12.1 RMII Transmit and Receive Operation

The same signals are used internally for both the RMII and the MII operations. The RMII maps these signals in a more pin-efficient manner. The transmit and receive bits are converted from a 4-bit parallel format to a 2-bit parallel scheme that is clocked at twice the rate. The carrier sense and data valid signals are combined into the ECRSDV signal. This signal contains information on carrier sense, FIFO status, and validity of the data. Transmit error bit (ETXER) and collision detect (ECOL) are not used in RMII mode.

#### 37.5.26 EMAC Statistic Registers

These registers reset to zero on a read and stick at all ones when they count to their maximum value. They should be read frequently enough to prevent loss of data. The receive statistics registers are only incremented when the receive enable bit is set in the network control register. To write to these registers, bit 7 must be set in the network control register. The statistics register block contains the following registers.

| Register Name<br>Access Type: | : EMAC_F<br>Read-wr |    |         |         |    |    |    |

|-------------------------------|---------------------|----|---------|---------|----|----|----|

| 31                            | 30                  | 29 | 28      | 27      | 26 | 25 | 24 |

| -                             | _                   | _  | -       | _       | _  | _  | _  |

| 23                            | 22                  | 21 | 20      | 19      | 18 | 17 | 16 |

| _                             | -                   | —  | -       | —       | _  | —  | _  |

| 15                            | 14                  | 13 | 12      | 11      | 10 | 9  | 8  |

| FROK                          |                     |    |         |         |    |    |    |

| 7                             | 6                   | 5  | 4<br>EP | 3<br>OK | 2  | 1  | 0  |

|                               |                     |    | FK      | UK      |    |    |    |

#### 37.5.26.1 Pause Frames Received Register

### • FROK: Pause Frames Received OK

A 16-bit register counting the number of good pause frames received. A good frame has a length of 64 to 1518 (1536 if bit 8 set in network configuration register) and has no FCS, alignment or receive symbol errors.

#### 37.5.26.2 Frames Transmitted OK Register

| Register Name:<br>Access Type: | EMAC_I<br>Read-wi |    |    |    |    |    |    |

|--------------------------------|-------------------|----|----|----|----|----|----|

| 31                             | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

| -                              | —                 | -  | -  | -  | -  | -  | -  |

| 23                             | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

|                                | FTOK              |    |    |    |    |    |    |

| 15                             | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

| FTOK                           |                   |    |    |    |    |    |    |

| 7                              | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                                | FTOK              |    |    |    |    |    |    |

#### • FTOK: Frames Transmitted OK

A 24-bit register counting the number of frames successfully transmitted, i.e., no underrun and not too many retries.

#### 41.3.4.2 PIO: Electrical Characteristics on NRST, PA0-PA30 and PB0-PB26

When NRST or PA0 - PA30 or PB0 - PB26 are set as digital inputs with pull-up enabled, the voltage of the I/O stabilizes at VPull-up.

#### Vpull-up

| VPull-up Min   | VPull-up Max   |

|----------------|----------------|

| VDDIO - 0.65 V | VDDIO - 0.45 V |

This condition causes a leakage through VDDIO. This leakage is 45  $\mu$ A per pad in worst case at 3.3 V.

| I | Leakage |

|---|---------|

|---|---------|

| Parameter         | Тур    | Max   |  |

|-------------------|--------|-------|--|

| I Leakage at 3,3V | 2.5 µA | 45 µA |  |

Problem Fix/Workaround

It is recommended to use an external pull-up if needed.

#### 41.3.4.3 PIO: Drive Low NRST, PA0-PA30 and PB0-PB26

When NRST or PA0 - PA30 or PB0 - PB26 are set as digital inputs with pull-up enabled, driving the I/O with an output impedance higher than 500 ohms may not drive the I/O to a logical zero. Problem Fix/Workaround

Output impedance must be lower than 500 ohms.

#### 41.3.5 Pulse Width Modulation Controller (PWM)

#### 41.3.5.1 PWM: Update when PWM\_CCNTx = 0 or 1

If the Channel Counter Register value is 0 or 1, the Channel Period Register or Channel Duty Cycle Register is directly modified when writing the Channel Update Register. Problem Fix/Workaround

Check the Channel Counter Register before writing the update register.

#### 41.3.5.2 PWM: Update when PWM\_CPRDx = 0

When Channel Period Register equals 0, the period update is not operational. Problem Fix/Workaround

Do not write 0 in the period register.

#### 41.3.5.3 PWM: Counter Start Value

In left aligned mode, the first start value of the counter is 0. For the other periods, the counter starts at 1. Problem Fix/Workaround

None.

#### 41.3.5.4 PWM: Behavior of CHIDx Status Bits in the PWM\_SR Register

Erratic behavior of the CHIDx status bit in the PWM\_SR Register. When a channel is disabled by writing in the PWM\_DIS Register just after enabling it (before completion of a Clock Period of the clock selected for the channel), the PWM line is internally disabled but the CHIDx status bit in the PWM\_SR stays at 1. Problem Fix/Workaround

Do not disable a channel before completion of one period of the selected clock.

#### 41.3.6 Real Time Timer (RTT)

#### 41.3.6.1 RTT: Possible Event Loss when Reading RTT\_SR

If an event (RTTINC or ALMS) occurs within the same slow clock cycle during which the RTT\_SR is read, the corresponding bit might be cleared. This can lead to the loss of this event. Problem Fix/Workaround:

The software must handle the RTT event as an interrupt and should not poll RTT\_SR.

#### 41.3.7 Serial Peripheral Interface (SPI)

#### 41.3.7.1 SPI: Bad tx\_ready Behavior when CSAAT = 1 and SCBR = 1

If the SPI2 is programmed with CSAAT = 1, SCBR(baudrate) = 1 and two transfers are performed consecutively on the same slave with an IDLE state between them, the tx\_ready signal does not rise after the second data has been transferred in the shifter. This can imply for example, that the second data is sent twice. Problem Fix/Workaround

Do not use the combination CSAAT = 1 and SCBR = 1.

#### 41.3.7.2 SPI: LASTXFER (Last Transfer) Behavior

In FIXED Mode, with CSAAT bit set, and in "PDC mode" the Chip Select can rise depending on the data written in the SPI\_TDR when the TX\_EMPTY flag is set. If for example, the PDC writes a "1" in the bit 24 (LASTXFER bit) of the SPI\_TDR, the chip select will rise as soon as the TXEMPTY flag is set.

Problem Fix/Workaround

Use the CS in PIO mode when PDC mode is required and CS has to be maintained between transfers.

#### 41.3.7.3 SPI: SPCK Behavior in Master Mode

SPCK pin can toggle out before the first transfer in Master Mode. Problem Fix/Workaround

In Master Mode, MSTR bit must be set (in SPI\_MR register) before configuring SPI\_CSRx registers.

#### 41.3.7.4 SPI: Chip Select and Fixed Mode

In fixed Mode, if a transfer is performed through a PDC on a Chip select different from the Chip select 0, the output spi\_size sampled by the PDC will depend on the field, BITS (Bits per Transfer) of SPI\_CSR0 register, whatever the selected Chip select is. For example, if SPI\_CSR0 is configured for a 10-bit transfer whereas SPI\_CSR1 is configured for an 8-bit transfer, when a transfer is performed in Fixed mode through the PDC, on Chip select 1, the transfer will be considered as a HalfWord transfer.

Problem Fix/Workaround

If a PDC transfer has to be performed in 8 bits, on a Chip select y (y as different from 0), the BITS field of the SPI\_CSR0 must be configured in 8 bits, in the same way as the BITS field of the CSRy Register.

#### 41.3.7.5 SPI: Baudrate Set to 1

When Baudrate is set at 1 (i.e. when serial clock frequency equals the system clock frequency) and when the BITS field of the SPI\_CSR register (number of bits to be transmitted) equals an ODD value (in this case 9,11,13 or 15), an additional pulse will be generated on output SPCK.

Everything is OK if the BITS field equals 8,10,12,14 or 16 and Baudrate = 1. Problem Fix/Workaround

# Atmel

#### 41.6.2 Controller Area Network (CAN)

#### 41.6.2.1 CAN: Low Power Mode and Error Frame

If the Low Power Mode is activated while the CAN is generating an error frame, this error frame may be shortened. Problem Fix/Workaround

None

#### 41.6.2.2 CAN: Low Power Mode and Pending Transmit Messages

No pending transmit messages may be sent once the CAN Controller enters Low-power Mode. Problem Fix/Workaround

Check that all messages have been sent by reading the related Flags before entering Low-power Mode.

#### 41.6.3 Embedded Flash Controller (EFC)

#### 41.6.3.1 EFC: Embedded Flash Access Time

The embedded Flash maximum access time (FWS) is shown in Table 41-2:

#### Table 41-2. Embedded Flash Access Time

| Flash Wait State (FWS) | Read Operations | Maximum Operating Frequency (MHz) |

|------------------------|-----------------|-----------------------------------|

| 0                      | 1 cycle         | 16                                |

| 1                      | 2 cycles        | 32                                |

| 2                      | 3 cycels        | 48                                |

| 3                      | 4 cycles        | 55                                |

#### Problem Fix/Workaround

Set the number of wait states (FWS) depending on frequency as specified in Table 41-2.

#### 41.6.4 Ethernet MAC (EMAC)

#### 41.6.4.1 EMAC: Possible Event Loss when Reading EMAC\_ISR

If an event occurs within the same clock cycle in which the EMAC\_ISR is read, the corresponding bit might be cleared even though it has not been read at 1. This might lead to the loss of this event. Problem Fix/Workaround

Each time the software reads EMAC\_ISR, it has to check the contents of the Transmit Status Register (EMAC\_TSR), the Receive Status Register (EMAC\_RSR) and the Network Status Register (EMAC\_NSR), as the possible lost event is still notified in one of these registers.

#### 41.6.4.2 EMAC: Possible Event Loss when Reading the Statistics Register Block

If an event occurs within the same clock cycle during which a statistics register is read, the corresponding counter might lose this event. This might lead to the loss of the incrementation of one for this counter. Problem Fix/Workaround

None