#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                         |

| Core Size                  | 16/32-Bit                                                                     |

| Speed                      | 55MHz                                                                         |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                    |

| Number of I/O              | 62                                                                            |

| Program Memory Size        | 512KB (512K x 8)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 128K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                                 |

| Data Converters            | A/D 8x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 100-LQFP                                                                      |

| Supplier Device Package    | 100-LQFP (14x14)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x512-au-999 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 14.4.1 Real-time Timer Mode Register

| Register Name:<br>Access Type: | RTT_M<br>Read-wr |    |     |     |        |           |        |  |  |

|--------------------------------|------------------|----|-----|-----|--------|-----------|--------|--|--|

| 31                             | 30               | 29 | 28  | 27  | 26     | 25        | 24     |  |  |

| -                              | -                | _  | _   | _   | _      | _         | _      |  |  |

| 23                             | 22               | 21 | 20  | 19  | 18     | 17        | 16     |  |  |

| -                              | -                | _  | -   | _   | RTTRST | RTTINCIEN | ALMIEN |  |  |

| 15                             | 14               | 13 | 12  | 11  | 10     | 9         | 8      |  |  |

|                                | RTPRES           |    |     |     |        |           |        |  |  |

| 7                              | 6                | 5  | 4   | 3   | 2      | 1         | 0      |  |  |

|                                |                  |    | RTF | RES |        |           |        |  |  |

### • RTPRES: Real-time Timer Prescaler Value

Defines the number of SLCK periods required to increment the real-time timer. RTPRES is defined as follows:

RTPRES = 0: The Prescaler Period is equal to  $2^{16}$

RTPRES  $\neq$  0: The Prescaler Period is equal to RTPRES.

### • ALMIEN: Alarm Interrupt Enable

0 = The bit ALMS in RTT\_SR has no effect on interrupt.

1 = The bit ALMS in RTT\_SR asserts interrupt.

### • RTTINCIEN: Real-time Timer Increment Interrupt Enable

0 = The bit RTTINC in RTT\_SR has no effect on interrupt.

1 = The bit RTTINC in RTT\_SR asserts interrupt.

### • RTTRST: Real-time Timer Restart

1 = Reloads and restarts the clock divider with the new programmed value. This also resets the 32-bit counter.

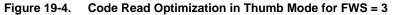

Note: When FWS is equal to 2 or 3, in case of sequential reads, the first access takes FWS cycles, the second access one cycle, the third access FWS cycles, the fourth access one cycle, etc.

### 19.2.3 Write Operations

The internal memory area reserved for the embedded Flash can also be written through a write-only latch buffer. Write operations take into account only the 8 lowest address bits and thus wrap around within the internal memory area address space and appear to be repeated 1024 times within it.

Write operations can be prevented by programming the Memory Protection Unit of the product.

Writing 8-bit and 16-bit data is not allowed and may lead to unpredictable data corruption.

Write operations are performed in the number of wait states equal to the number of wait states for read operations + 1, except for FWS = 3 (see "MC Flash Mode Register" on page 108).

#### 19.2.4 Flash Commands

The EFC offers a command set to manage programming the memory flash, locking and unlocking lock sectors, consecutive programming and locking, and full Flash erasing.

| Command                       | Value | Mnemonic |

|-------------------------------|-------|----------|

| Write page                    | 0x01  | WP       |

| Set Lock Bit                  | 0x02  | SLB      |

| Write Page and Lock           | 0x03  | WPL      |

| Clear Lock Bit                | 0x04  | CLB      |

| Erase all                     | 0x08  | EA       |

| Set General-purpose NVM Bit   | 0x0B  | SGPB     |

| Clear General-purpose NVM Bit | 0x0D  | CGPB     |

| Set Security Bit              | 0x0F  | SSB      |

Table 19-2. Set of Commands

To run one of these commands, the field FCMD of the MC\_FCR register has to be written with the command number. As soon as the MC\_FCR register is written, the FRDY flag is automatically cleared. Once the current command is achieved, then the FRDY flag is automatically set. If an interrupt has been enabled by setting the bit FRDY in MC\_FMR, the interrupt line of the Memory Controller is activated.

# 22.4.9 PDC Transfer Control Register

| Register Name: | PERIPH_PTCR |

|----------------|-------------|

| Access Type:   | Write-only  |

| 31 | 30 | 29 | 28 | 27 | 26 | 25     | 24    |

|----|----|----|----|----|----|--------|-------|

| _  | -  | -  | _  | -  | _  | -      | _     |

| 23 | 22 | 21 | 20 | 19 | 18 | 17     | 16    |

| _  | _  | _  | _  | _  | _  | _      | _     |

| 15 | 14 | 13 | 12 | 11 | 10 | 9      | 8     |

| _  | -  | Ι  | -  |    | -  | TXTDIS | TXTEN |

| 7  | 6  | 5  | 4  | 3  | 2  | 1      | 0     |

| _  | _  | _  | _  | _  | _  | RXTDIS | RXTEN |

# • RXTEN: Receiver Transfer Enable

0 = No effect.

1 = Enables the receiver PDC transfer requests if RXTDIS is not set.

### • RXTDIS: Receiver Transfer Disable

0 = No effect.

1 = Disables the receiver PDC transfer requests.

### • TXTEN: Transmitter Transfer Enable

0 = No effect.

1 = Enables the transmitter PDC transfer requests.

# • TXTDIS: Transmitter Transfer Disable

0 = No effect.

1 = Disables the transmitter PDC transfer requests

### 25.9.14 PMC Status Register

| Register Name: | PMC_SR  |    |    |        |         |         |         |

|----------------|---------|----|----|--------|---------|---------|---------|

| Access Type:   | Read-on | ly |    |        |         |         |         |

| 31             | 30      | 29 | 28 | 27     | 26      | 25      | 24      |

| _              | _       | _  | -  | -      | _       | -       | _       |

| 23             | 22      | 21 | 20 | 19     | 18      | 17      | 16      |

| -              | _       | _  | -  | -      | _       | -       | -       |

| 15             | 14      | 13 | 12 | 11     | 10      | 9       | 8       |

| -              | -       | -  | -  | —      | PCKRDY2 | PCKRDY1 | PCKRDY0 |

| 7              | 6       | 5  | 4  | 3      | 2       | 1       | 0       |

| -              | _       | -  | -  | MCKRDY | LOCK    | _       | MOSCS   |

# • MOSCS: MOSCS Flag Status

0 = Main oscillator is not stabilized.

1 = Main oscillator is stabilized.

### • LOCK: PLL Lock Status

0 = PLL is not locked

1 = PLL is locked.

### MCKRDY: Master Clock Status

0 = Master Clock is not ready.

1 = Master Clock is ready.

### • PCKRDYx: Programmable Clock Ready Status

0 = Programmable Clock x is not ready.

1 = Programmable Clock x is ready.

# 26.5.3 Debug Unit Interrupt Enable Register

Nama

| Name: DBGU_IER |          | ER   |        |        |    |         |       |

|----------------|----------|------|--------|--------|----|---------|-------|

| Access Type:   | Write-on | lly  |        |        |    |         |       |

| 31             | 30       | 29   | 28     | 27     | 26 | 25      | 24    |

| COMMRX         | COMMTX   | _    | -      | _      | _  | _       | _     |

| 23             | 22       | 21   | 20     | 19     | 18 | 17      | 16    |

| _              | _        | _    | -      | _      | _  | _       | _     |

| 15             | 14       | 13   | 12     | 11     | 10 | 9       | 8     |

| _              | _        | _    | RXBUFF | TXBUFE | —  | TXEMPTY | _     |

| 7              | 6        | 5    | 4      | 3      | 2  | 1       | 0     |

| PARE           | FRAME    | OVRE | ENDTX  | ENDRX  | -  | TXRDY   | RXRDY |

| FARE           | FRANIE   | OVRE | ENDIX  | ENDRA  | _  | IARDI   | RARDI |

- RXRDY: Enable RXRDY Interrupt

- TXRDY: Enable TXRDY Interrupt

- ENDRX: Enable End of Receive Transfer Interrupt

- ENDTX: Enable End of Transmit Interrupt

- OVRE: Enable Overrun Error Interrupt

- FRAME: Enable Framing Error Interrupt

- PARE: Enable Parity Error Interrupt

- TXEMPTY: Enable TXEMPTY Interrupt

- TXBUFE: Enable Buffer Empty Interrupt

- RXBUFF: Enable Buffer Full Interrupt

- COMMTX: Enable COMMTX (from ARM) Interrupt

- COMMRX: Enable COMMRX (from ARM) Interrupt

0 = No effect.

1 = Enables the corresponding interrupt.

# 28.7.8 SPI Interrupt Mask Register

| Name:        | e: SPI_IMR |       |       |       |      |         |      |

|--------------|------------|-------|-------|-------|------|---------|------|

| Access Type: | Read-on    | lly   |       |       |      |         |      |

| 31           | 30         | 29    | 28    | 27    | 26   | 25      | 24   |

| _            | _          | _     | -     | -     | _    | _       | _    |

| 23           | 22         | 21    | 20    | 19    | 18   | 17      | 16   |

| _            | _          | _     | _     | _     | _    | _       | _    |

| 15           | 14         | 13    | 12    | 11    | 10   | 9       | 8    |

| _            | _          | _     | _     | _     | -    | TXEMPTY | NSSR |

| 7            | 6          | 5     | 4     | 3     | 2    | 1       | 0    |

| TXBUFE       | RXBUFF     | ENDTX | ENDRX | OVRES | MODF | TDRE    | RDRF |

|              |            |       |       |       |      |         |      |

- RDRF: Receive Data Register Full Interrupt Mask

- TDRE: SPI Transmit Data Register Empty Interrupt Mask

- MODF: Mode Fault Error Interrupt Mask

- OVRES: Overrun Error Interrupt Mask

- ENDRX: End of Receive Buffer Interrupt Mask

- ENDTX: End of Transmit Buffer Interrupt Mask

- RXBUFF: Receive Buffer Full Interrupt Mask

- TXBUFE: Transmit Buffer Empty Interrupt Mask

- TXEMPTY: Transmission Registers Empty Mask

# • NSSR: NSS Rising Interrupt Mask

- 0 = The corresponding interrupt is not enabled.

- 1 = The corresponding interrupt is enabled.

### 30.6.7 Modem Mode

The USART features modem mode, which enables control of the signals: DTR (Data Terminal Ready), DSR (Data Set Ready), RTS (Request to Send), CTS (Clear to Send), DCD (Data Carrier Detect) and RI (Ring Indicator). While operating in modem mode, the USART behaves as a DTE (Data Terminal Equipment) as it drives DTR and RTS and can detect level change on DSR, DCD, CTS and RI.

Setting the USART in modem mode is performed by writing the USART\_MODE field in the Mode Register (US\_MR) to the value 0x3. While operating in modem mode the USART behaves as though in asynchronous mode and all the parameter configurations are available.

Table 30-11 gives the correspondence of the USART signals with modem connection standards.

| USART Pin | V24 | CCITT | Direction              |  |  |

|-----------|-----|-------|------------------------|--|--|

| TXD       | 2   | 103   | From terminal to modem |  |  |

| RTS       | 4   | 105   | From terminal to modem |  |  |

| DTR       | 20  | 108.2 | From terminal to modem |  |  |

| RXD       | 3   | 104   | From modem to terminal |  |  |

| CTS       | 5   | 106   | From terminal to modem |  |  |

| DSR       | 6   | 107   | From terminal to modem |  |  |

| DCD       | 8   | 109   | From terminal to modem |  |  |

| RI        | 22  | 125   | From terminal to modem |  |  |

Table 30-11. Circuit References

The control of the DTR output pin is performed by writing the Control Register (US\_CR) with the DTRDIS and DTREN bits respectively at 1. The disable command forces the corresponding pin to its inactive level, i.e. high. The enable command forces the corresponding pin to its active level, i.e. low. RTS output pin is automatically controlled in this mode

The level changes are detected on the RI, DSR, DCD and CTS pins. If an input change is detected, the RIIC, DSRIC, DCDIC and CTSIC bits in the Channel Status Register (US\_CSR) are set respectively and can trigger an interrupt. The status is automatically cleared when US\_CSR is read. Furthermore, the CTS automatically disables the transmitter when it is detected at its inactive state. If a character is being transmitted when the CTS rises, the character transmission is completed before the transmitter is actually disabled.

# 30.6.8 Test Modes

The USART can be programmed to operate in three different test modes. The internal loopback capability allows onboard diagnostics. In the loopback mode the USART interface pins are disconnected or not and reconfigured for loopback internally or externally.

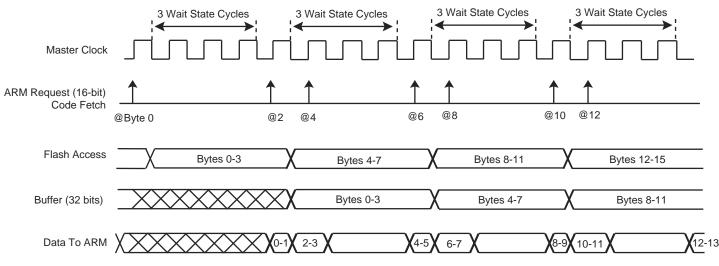

### 30.6.8.1 Normal Mode

Normal mode connects the RXD pin on the receiver input and the transmitter output on the TXD pin.

# Figure 30-28. Normal Mode Configuration

# • FSOS: Transmit Frame Sync Output Selection

| FSOS    | Selected Transmit Frame Sync Signal         | TF Pin     |  |  |  |

|---------|---------------------------------------------|------------|--|--|--|

| 0x0     | None                                        | Input-only |  |  |  |

| 0x1     | Negative Pulse Ou                           |            |  |  |  |

| 0x2     | 0x2 Positive Pulse                          |            |  |  |  |

| 0x3     | Driven Low during data transfer             | Output     |  |  |  |

| 0x4     | Driven High during data transfer            | Output     |  |  |  |

| 0x5     | 0x5 Toggling at each start of data transfer |            |  |  |  |

| 0x6-0x7 | Reserved                                    | Undefined  |  |  |  |

# • FSDEN: Frame Sync Data Enable

0: The TD line is driven with the default value during the Transmit Frame Sync signal.

1: SSC\_TSHR value is shifted out during the transmission of the Transmit Frame Sync signal.

# • FSEDGE: Frame Sync Edge Detection

Determines which edge on frame sync will generate the interrupt TXSYN (Status Register).

|                             | FSEDGE | Frame Sync Edge Detection |  |

|-----------------------------|--------|---------------------------|--|

| 0x0 Positive Edge Detection |        | Positive Edge Detection   |  |

|                             | 0x1    | Negative Edge Detection   |  |

# 31.8.16 SSC Interrupt Mask Register

| Name:        | SSC_IMR |       |       |        |       |         |       |

|--------------|---------|-------|-------|--------|-------|---------|-------|

| Access Type: | Read-on | lly   |       |        |       |         |       |

| 31           | 30      | 29    | 28    | 27     | 26    | 25      | 24    |

| -            | _       | -     | -     | -      | -     | -       | -     |

| 23           | 22      | 21    | 20    | 19     | 18    | 17      | 16    |

| -            | _       | _     | _     | _      | _     | _       | _     |

| 15           | 14      | 13    | 12    | 11     | 10    | 9       | 8     |

| -            | -       | -     | -     | RXSYN  | TXSYN | CP1     | CP0   |

| 7            | 6       | 5     | 4     | 3      | 2     | 1       | 0     |

| RXBUFF       | ENDRX   | OVRUN | RXRDY | TXBUFE | ENDTX | TXEMPTY | TXRDY |

### • TXRDY: Transmit Ready Interrupt Mask

0: The Transmit Ready Interrupt is disabled.

1: The Transmit Ready Interrupt is enabled.

# • TXEMPTY: Transmit Empty Interrupt Mask

0: The Transmit Empty Interrupt is disabled.

1: The Transmit Empty Interrupt is enabled.

### • ENDTX: End of Transmission Interrupt Mask

0: The End of Transmission Interrupt is disabled.

1: The End of Transmission Interrupt is enabled.

# • TXBUFE: Transmit Buffer Empty Interrupt Mask

0: The Transmit Buffer Empty Interrupt is disabled.

1: The Transmit Buffer Empty Interrupt is enabled.

### • RXRDY: Receive Ready Interrupt Mask

0: The Receive Ready Interrupt is disabled.

1: The Receive Ready Interrupt is enabled.

# OVRUN: Receive Overrun Interrupt Mask

0: The Receive Overrun Interrupt is disabled.

1: The Receive Overrun Interrupt is enabled.

# • ENDRX: End of Reception Interrupt Mask

0: The End of Reception Interrupt is disabled.

1: The End of Reception Interrupt is enabled.

### • RXBUFF: Receive Buffer Full Interrupt Mask

0: The Receive Buffer Full Interrupt is disabled.

1: The Receive Buffer Full Interrupt is enabled.

# 34.6.4 UDP Interrupt Enable Register

| Register Name: | UDP_IE   | R      |        |        |        |        |        |

|----------------|----------|--------|--------|--------|--------|--------|--------|

| Access Type:   | Write-on | ly     |        |        |        |        |        |

| 31             | 30       | 29     | 28     | 27     | 26     | 25     | 24     |

| -              | _        | -      | -      | -      | -      | -      | -      |

| 23             | 22       | 21     | 20     | 19     | 18     | 17     | 16     |

| _              | _        | -      | -      | -      | -      | _      | -      |

| 15             | 14       | 13     | 12     | 11     | 10     | 9      | 8      |

| -              | —        | WAKEUP | -      | SOFINT | —      | RXRSM  | RXSUSP |

| 7              | 6        | 5      | 4      | 3      | 2      | 1      | 0      |

|                |          | EP5INT | EP4INT | EP3INT | EP2INT | EP1INT | EP0INT |

- EP0INT: Enable Endpoint 0 Interrupt

- EP1INT: Enable Endpoint 1 Interrupt

- EP2INT: Enable Endpoint 2Interrupt

- EP3INT: Enable Endpoint 3 Interrupt

- EP4INT: Enable Endpoint 4 Interrupt

- EP5INT: Enable Endpoint 5 Interrupt

- 0 = No effect.

1 = Enables corresponding Endpoint Interrupt.

- RXSUSP: Enable UDP Suspend Interrupt

- 0 = No effect.

- 1 = Enables UDP Suspend Interrupt.

# • RXRSM: Enable UDP Resume Interrupt

0 = No effect.

1 = Enables UDP Resume Interrupt.

# • SOFINT: Enable Start Of Frame Interrupt

0 = No effect.

1 = Enables Start Of Frame Interrupt.

# • WAKEUP: Enable UDP bus Wakeup Interrupt

0 = No effect.

1 = Enables USB bus Interrupt.

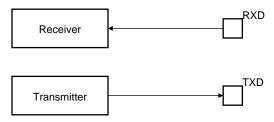

# 35. Analog-to-Digital Converter (ADC)

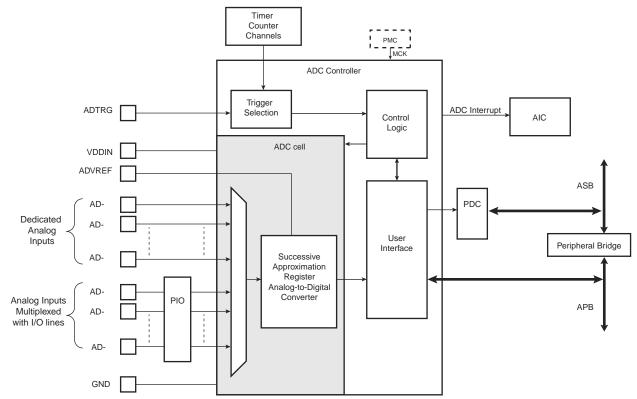

# 35.1 Overview

The ADC is based on a Successive Approximation Register (SAR) 10-bit Analog-to-Digital Converter (ADC). It also integrates an 8-to-1 analog multiplexer, making possible the analog-to-digital conversions of 8 analog lines. The conversions extend from 0V to ADVREF.

The ADC supports an 8-bit or 10-bit resolution mode, and conversion results are reported in a common register for all channels, as well as in a channel-dedicated register. Software trigger, external trigger on rising edge of the ADTRG pin or internal triggers from Timer Counter output(s) are configurable.

The ADC also integrates a Sleep Mode and a conversion sequencer and connects with a PDC channel. These features reduce both power consumption and processor intervention.

Finally, the user can configure ADC timings, such as Startup Time and Sample & Hold Time.

# 35.2 Block Diagram

# 36.8.12 CAN Message Mode Register

| Name:        | CAN_M       | MRx         |             |             |             |            |            |

|--------------|-------------|-------------|-------------|-------------|-------------|------------|------------|

| Access Type: | Read-wr     | ite         |             |             |             |            |            |

| 31           | 30          | 29          | 28          | 27          | 26          | 25         | 24         |

| -            | -           | -           | —           | —           |             | MOT        |            |

| 23           | 22          | 21          | 20          | 19          | 18          | 17         | 16         |

| _            | -           | -           | -           |             | PRI         | OR         |            |

| 15           | 14          | 13          | 12          | 11          | 10          | 9          | 8          |

| MTIMEMARK15  | MTIMEMARK14 | MTIMEMARK13 | MTIMEMARK12 | MTIMEMARK11 | MTIMEMARK10 | MTIMEMARK9 | MTIMEMARK8 |

| 7            | 6           | 5           | 4           | 3           | 2           | 1          | 0          |

| MTIMEMARK7   | MTIMEMARK6  | MTIMEMARK5  | MTIMEMARK4  | MTIMEMARK3  | MTIMEMARK2  | MTIMEMARK1 | MTIMEMARK0 |

# • MTIMEMARK: Mailbox Timemark

This field is active in Time Triggered Mode. Transmit operations are allowed when the internal timer counter reaches the Mailbox Timemark. See "Transmitting within a Time Window" on page 504.

In Timestamp Mode, MTIMEMARK is set to 0.

### • PRIOR: Mailbox Priority

This field has no effect in receive and receive with overwrite modes. In these modes, the mailbox with the lowest number is serviced first.

When several mailboxes try to transmit a message at the same time, the mailbox with the highest priority is serviced first. If several mailboxes have the same priority, the mailbox with the lowest number is serviced first (i.e., MBx0 is serviced before MBx 15 if they have the same priority).

# • MOT: Mailbox Object Type

This field allows the user to define the type of the mailbox. All mailboxes are independently configurable. Five different types are possible for each mailbox:

|   | МОТ |   | Mailbox Object Type                                                                                                                                                      |

|---|-----|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | 0   | 0 | Mailbox is disabled. This prevents receiving or transmitting any messages with this mailbox.                                                                             |

| 0 | 0   | 1 | Reception Mailbox. Mailbox is configured for reception. If a message is received while the mailbox data register is full, it is discarded.                               |

| 0 | 1   | 0 | Reception mailbox with overwrite. Mailbox is configured for reception. If a message is received while the mailbox is full, it overwrites the previous message.           |

| 0 | 1   | 1 | Transmit mailbox. Mailbox is configured for transmission.                                                                                                                |

| 1 | 0   | 0 | Consumer Mailbox. Mailbox is configured in reception but behaves as a Transmit Mailbox, i.e., it sends a remote frame and waits for an answer.                           |

| 1 | 0   | 1 | Producer Mailbox. Mailbox is configured in transmission but also behaves like a reception mailbox, i.e., it waits to receive a Remote Frame before sending its contents. |

| 1 | 1   | Х | Reserved                                                                                                                                                                 |

# 36.8.18 CAN Message Data High Register

| Name:<br>Access Type: | CAN_MI<br>Read-wi |    |    |    |    |    |    |

|-----------------------|-------------------|----|----|----|----|----|----|

| 31                    | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

|                       |                   |    | M  | DH |    |    |    |

| 23                    | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

|                       |                   |    | M  | DH |    |    |    |

| 15                    | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

|                       |                   |    | M  | DH |    |    |    |

| 7                     | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                       |                   |    | M  | DH |    |    |    |

# • MDH: Message Data High Value

When MRDY field is set in the CAN\_MSRx register, the upper 32 bits of a received message are read or written by the software application. Otherwise, the MDH value is locked by the CAN controller to send/receive a new message.

In Receive with overwrite, the CAN controller may modify MDH value while the software application reads MDH and MDL registers. To check that MDH and MDL do not belong to different messages, the application has to check the MMI field in the CAN\_MSRx register. In this mode, the software application must re-read CAN\_MDH and CAN\_MDL, while the MMI bit in the CAN\_MSRx register is set.

Bytes are received/sent on the bus in the following order:

- 1. CAN\_MDL[7:0]

- 2. CAN\_MDL[15:8]

- 3. CAN\_MDL[23:16]

- 4. CAN\_MDL[31:24]

- 5. CAN\_MDH[7:0]

- 6. CAN\_MDH[15:8]

- 7. CAN\_MDH[23:16]

- 8. CAN\_MDH[31:24]

# 37.5.18 Specific Address 2 Bottom Register

| Register Name: | EMAC_S  | SA2B |    |    |    |    |    |

|----------------|---------|------|----|----|----|----|----|

| Access Type:   | Read-wi | rite |    |    |    |    |    |

| 31             | 30      | 29   | 28 | 27 | 26 | 25 | 24 |

|                |         |      | AD | DR |    |    |    |

| 23             | 22      | 21   | 20 | 19 | 18 | 17 | 16 |

|                |         |      | AD | DR |    |    |    |

| 15             | 14      | 13   | 12 | 11 | 10 | 9  | 8  |

|                |         |      | AD | DR |    |    |    |

| 7              | 6       | 5    | 4  | 3  | 2  | 1  | 0  |

|                |         |      | AD | DR |    |    |    |

# • ADDR

Least significant bits of the destination address. Bit zero indicates whether the address is multicast or unicast and corresponds to the least significant bit of the first byte received.

|                |        | op negister |    |     |    |    |    |

|----------------|--------|-------------|----|-----|----|----|----|

| Register Name: | EMAC_  | SA2T        |    |     |    |    |    |

| Access Type:   | Read-w | rite        |    |     |    |    |    |

| 31             | 30     | 29          | 28 | 27  | 26 | 25 | 24 |

| -              | _      | -           | -  | -   | -  | -  | -  |

| 23             | 22     | 21          | 20 | 19  | 18 | 17 | 16 |

| -              | —      | -           | -  | -   | —  | —  | -  |

| 15             | 14     | 13          | 12 | 11  | 10 | 9  | 8  |

|                |        |             | A  | DDR |    |    |    |

| 7              | 6      | 5           | 4  | 3   | 2  | 1  | 0  |

|                |        |             | A  | DDR |    |    |    |

# 37.5.19 Specific Address 2 Top Register

# • ADDR

The most significant bits of the destination address, that is bits 47 to 32.

# 37.5.26.3 Single Collision Frames Register

| Register Name: | EMAC_  | SCF  |    |    |    |    |    |

|----------------|--------|------|----|----|----|----|----|

| Access Type:   | Read-w | rite |    |    |    |    |    |

| 31             | 30     | 29   | 28 | 27 | 26 | 25 | 24 |

| -              | -      | -    | -  | -  | —  | -  | -  |

| 23             | 22     | 21   | 20 | 19 | 18 | 17 | 16 |

| -              | _      | -    | -  | -  | -  | -  | -  |

| 15             | 14     | 13   | 12 | 11 | 10 | 9  | 8  |

|                |        |      | S  | CF |    |    |    |

| 7              | 6      | 5    | 4  | 3  | 2  | 1  | 0  |

|                |        |      | S  | CF |    |    |    |

### • SCF: Single Collision Frames

A 16-bit register counting the number of frames experiencing a single collision before being successfully transmitted, i.e., no underrun.

# 37.5.26.4 Multicollision Frames Register

| Register Name:<br>Access Type: | EMAC_N<br>Read-wr |    |    |    |    |    |    |

|--------------------------------|-------------------|----|----|----|----|----|----|

| 31                             | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

| -                              | _                 | _  | _  | _  | _  | _  | —  |

| 23                             | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

| -                              | _                 | —  | -  | —  | -  | —  | —  |

| 15                             | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

|                                |                   |    | M  | CF |    |    |    |

| 7                              | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                                |                   |    | M  | CF |    |    |    |

### • MCF: Multicollision Frames

A 16-bit register counting the number of frames experiencing between two and fifteen collisions prior to being successfully transmitted, i.e., no underrun and not too many retries.

# 38.7 ADC Characteristics

| Table 38-15. | Channel Conversion Time and ADC Clock |

|--------------|---------------------------------------|

|              |                                       |

| Parameter                       | Conditions             | Min | Тур | Max                | Units |

|---------------------------------|------------------------|-----|-----|--------------------|-------|

| ADC Clock Frequency             | 10-bit resolution mode |     |     | 5                  | MHz   |

| ADC Clock Frequency             | 8-bit resolution mode  |     |     | 8                  | MHz   |

| Startup Time                    | Return from Idle Mode  |     |     | 20                 | μs    |

| Track and Hold Acquisition Time |                        | 600 |     |                    | ns    |

| Conversion Time                 | ADC Clock = 5 MHz      |     |     | 2                  | μs    |

| Conversion Time                 | ADC Clock = 8 MHz      |     |     | 1.25               | μs    |

| Throughput Rate                 | ADC Clock = 5 MHz      |     |     | 384 <sup>(1)</sup> | kSPS  |

| Throughput Rate                 | ADC Clock = 8 MHz      |     |     | 533 <sup>(2)</sup> | kSPS  |

Notes: 1. Corresponds to 13 clock cycles at 5 MHz: 3 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

2. Corresponds to 15 clock cycles at 8 MHz: 5 clock cycles for track and hold acquisition time and 10 clock cycles for conversion.

Table 38-16. External Voltage Reference Input

| Parameter                    | Conditions                           | Min | Тур  | Max               | Units |

|------------------------------|--------------------------------------|-----|------|-------------------|-------|

| ADVREF Input Voltage Range   |                                      | 2.6 |      | V <sub>DDIN</sub> | V     |

| ADVREF Input Voltage Range   | 8-bit resolution mode                | 2.5 |      | V <sub>DDIN</sub> | V     |

| ADVREF Average Current       | On 13 samples with ADC Clock = 5 MHz |     | 200  | 250               | μA    |

| Current Consumption on VDDIN |                                      |     | 0.55 | 1                 | mA    |

### Table 38-17. Analog Inputs

| Parameter             | Min | Тур | Мах                 | Units |

|-----------------------|-----|-----|---------------------|-------|

| Input Voltage Range   | 0   |     | V <sub>ADVREF</sub> |       |

| Input Leakage Current |     | 1   |                     | μA    |

| Input Capacitance     |     | 12  | 14                  | pF    |

The user can drive ADC input with impedance up to:

- $Z_{OUT} \leq$  (SHTIM -470) x 10 in 8-bit resolution mode

- $Z_{OUT} \leq$  (SHTIM -589) x 7.69 in 10-bit resolution mode

with SHTIM (Sample and Hold Time register) expressed in ns and  $Z_{OUT}$  expressed in ohms.

### Table 38-18. Transfer Characteristics

| Parameter                  | Conditions      | Min | Тур | Max | Units |

|----------------------------|-----------------|-----|-----|-----|-------|

| Resolution                 |                 |     | 10  |     | Bit   |

| Integral Non-linearity     |                 |     |     | ±2  | LSB   |

| Differential Non-linearity | No missing code |     |     | ±1  | LSB   |

| Offset Error               |                 |     |     | ±2  | LSB   |

| Gain Error                 |                 |     |     | ±2  | LSB   |

| Absolute Accuracy          |                 |     |     | ±4  | LSB   |

For more information on data converter terminology, please refer to the application note: Data Converter Terminology, Atmel lit<sup>o</sup> 6022.

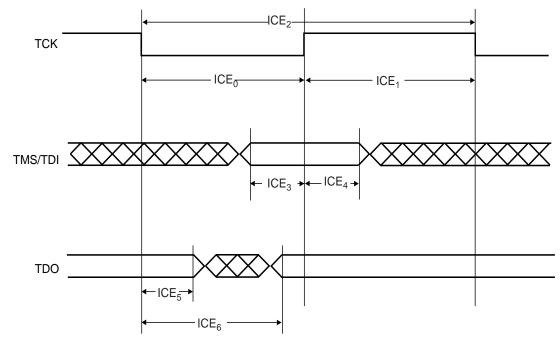

### 38.8.6 JTAG/ICE Timings

38.8.6.1 ICE Interface Signals

| Symbol           | Parameter                       | Conditions | Min | Max | Units |

|------------------|---------------------------------|------------|-----|-----|-------|

| ICE <sub>0</sub> | TCK Low Half-period             | (1)        | 51  |     | ns    |

| ICE <sub>1</sub> | TCK High Half-period            | (1)        | 51  |     | ns    |

| ICE <sub>2</sub> | TCK Period                      | (1)        | 102 |     | ns    |

| ICE <sub>3</sub> | TDI, TMS, Setup before TCK High | (1)        | 0   |     | ns    |

| ICE <sub>4</sub> | TDI, TMS, Hold after TCK High   | (1)        | 3   |     | ns    |

| ICE <sub>5</sub> | TDO Hold Time                   | (1)        | 13  |     | ns    |

| ICE <sub>6</sub> | TCK Low to TDO Valid            | (1)        |     | 20  | ns    |

Note: 1.  $V_{VDDIO}$  from 3.0V to 3.6V, maximum external capacitor = 40pF

### Figure 38-10. ICE Interface Signals

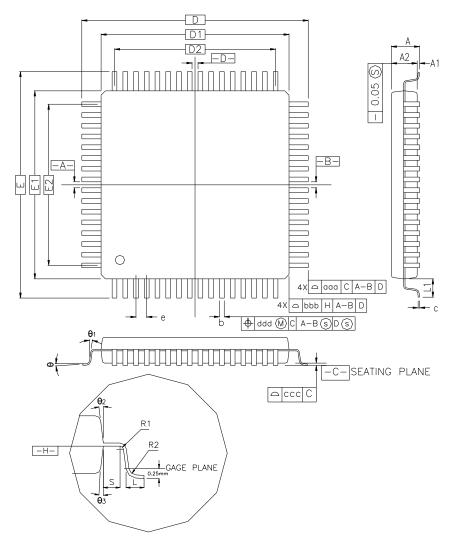

# 39. SAM7X512/256/128 Mechanical Characteristics

# 39.1 Package Drawings

Figure 39-1. LQFP Package Drawing

### 41.3.9.5 TWI: Software Reset

when a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

Problem Fix/Workaround

None.

### 41.3.10 Universal Synchronous Asynchronous Receiver Transmitter (USART)

### 41.3.10.1 USART: CTS in Hardware Handshaking

When Hardware Handshaking is used and if CTS goes low near the end of the start bit, a character can be lost.

CTS must not go high during a time slot occurring between 2 Master Clock periods before and 16 Master Clock periods after the rising edge of the start bit.

Problem Fix/Workaround

None.

### 41.3.10.2 USART: Hardware Handshaking – Two Characters Sent

If CTS switches from 0 to 1 during the TX of a character and if the holding register (US\_THR) is not empty, the content of US\_THR will also be transmitted.

Problem Fix/Workaround

Don't use the PDC in transmit mode and do not fill US\_THR before TXEMPTY is set at 1.

### 41.3.10.3 USART: RXBRK Flag Error in Asynchronous Mode

In receiver mode, when there are two consecutive characters (without time guard in between), RXBRK is not taken into account. As a result, the RXBRK flag is not enabled correctly and the frame error flag is set Problem Fix/Workaround

Constraints on the transmitter device connected to the SAM7X USART receiver side:

The transmitter may use the timeguard feature or send two STOP conditions. Only one STOP condition is taken into account by the receiver state machine. After this STOP condition, as there is no valid data, the receiver state machine will go in idle mode and enable the RXBRK flag.

### 41.3.10.4 USART: DCD is Active High instead of Low.

The DCD signal is active at High level in the USART Modem Mode .

DCD should be active at Low level.

Problem Fix/Workaround

Add an inverter.

The user must be sure that received data is read before transmitting any new data.

### 41.5.9.5 TWI: Software Reset

when a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

Problem Fix/Workaround

None.

### 41.5.10 Universal Synchronous Asynchronous Receiver Transmitter (USART)

### 41.5.10.1 USART: CTS in Hardware Handshaking

When Hardware Handshaking is used and if CTS goes low near the end of the start bit, a character can be lost.

CTS must not go high during a time slot occurring between 2 Master Clock periods before and 16 Master Clock periods after the rising edge of the start bit.

Problem Fix/Workaround

None.

### 41.5.10.2 USART: Hardware Handshaking – Two Characters Sent

If CTS switches from 0 to 1 during the TX of a character and if the holding register (US\_THR) is not empty, the content of US\_THR will also be transmitted.

Problem Fix/Workaround

Don't use the PDC in transmit mode and do not fill US\_THR before TXEMPTY is set at 1.

### 41.5.10.3 USART: RXBRK Flag Error in Asynchronous Mode

In receiver mode, when there are two consecutive characters (without time guard in between), RXBRK is not taken into account. As a result, the RXBRK flag is not enabled correctly and the frame error flag is set Problem Fix/Workaround

Constraints on the transmitter device connected to the SAM7X USART receiver side:

The transmitter may use the timeguard feature or send two STOP conditions. Only one STOP condition is taken into account by the receiver state machine. After this STOP condition, as there is no valid data, the receiver state machine will go in idle mode and enable the RXBRK flag.

### 41.5.10.4 USART: DCD is Active High instead of Low

The DCD signal is active at High level in the USART Modem Mode.

DCD should be active at Low level. Problem Fix/Workaround

Add an inverter.

DCD should be active at Low level. Problem Fix/Workaround

Add an inverter.