# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 55MHz                                                                     |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 62                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                             |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x512-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Configuration Summary of the SAM7X512/256/128

The SAM7X512, SAM7X256 and SAM7X128 differ only in memory sizes. Table 1-1 summarizes the configurations of the three devices.

| Table 1-1. | Configuration Summary |

|------------|-----------------------|

|------------|-----------------------|

| Device   | Flash      | Flash Organization | SRAM       |

|----------|------------|--------------------|------------|

| SAM7X512 | 512 Kbytes | Dual-plane         | 128 Kbytes |

| SAM7X256 | 256 Kbytes | Single-plane       | 64 Kbytes  |

| SAM7X128 | 128 Kbytes | Single-plane       | 32 Kbytes  |

- Half a clock period glitch filter

- Multi-drive option enables driving in open drain

- Programmable pull-up on each I/O line

- Pin data status register, supplies visibility of the level on the pin at any time

- Synchronous output, provides Set and Clear of several I/O lines in a single write

## 9.10 Voltage Regulator Controller

The purpose of this controller is to select the Power Mode of the Voltage Regulator between Normal Mode (bit 0 is cleared) or Standby Mode (bit 0 is set).

### 12.5.5 ID Code Register

Access: Read-only

| 31          | 30                    | 29 | 28 | 27 | 26         | 25           | 24 |

|-------------|-----------------------|----|----|----|------------|--------------|----|

|             | VERSION               |    |    |    | PART N     | UMBER        |    |

| 23          | 22                    | 21 | 20 | 19 | 18         | 17           | 16 |

|             | PART NUMBER           |    |    |    |            |              |    |

| 15          | 14                    | 13 | 12 | 11 | 10         | 9            | 8  |

| PART NUMBER |                       |    |    |    | MANUFACTUF | RER IDENTITY |    |

| 7           | 6                     | 5  | 4  | 3  | 2          | 1            | 0  |

|             | MANUFACTURER IDENTITY |    |    |    |            |              | 1  |

|             |                       |    |    |    |            |              |    |

• VERSION[31:28]: Product Version Number

Set to 0x0.

### • PART NUMBER[27:12]: Product Part Number

AT91SAM7X512: 0x5B18 AT91SAM7X256: 0x5B17 AT91SAM7X128: 0x5B16

### • MANUFACTURER IDENTITY[11:1]

Set to 0x01F.

Bit[0] Required by IEEE Std. 1149.1.

Set to 0x1.

AT91SAM7X512: JTAG ID Code value is 05B1\_803F

AT91SAM7X256: JTAG ID Code value is 05B1\_703F

AT91SAM7X128: JTAG ID Code value is 05B1\_603F

### 16.4.3 Watchdog Timer Status Register

| Register Name: | WDT_S   | R   |    |    |    |       |       |

|----------------|---------|-----|----|----|----|-------|-------|

| Access Type:   | Read-or | nly |    |    |    |       |       |

| 31             | 30      | 29  | 28 | 27 | 26 | 25    | 24    |

| -              | _       | -   | -  | -  | -  | -     | -     |

| 23             | 22      | 21  | 20 | 19 | 18 | 17    | 16    |

| -              | _       | -   | -  | -  | -  | _     | _     |

| 15             | 14      | 13  | 12 | 11 | 10 | 9     | 8     |

| _              | _       | -   | -  | -  | -  | -     | -     |

| 7              | 6       | 5   | 4  | 3  | 2  | 1     | 0     |

| -              | _       | _   | _  | _  | -  | WDERR | WDUNF |

### • WDUNF: Watchdog Underflow

0: No Watchdog underflow occurred since the last read of WDT\_SR.

1: At least one Watchdog underflow occurred since the last read of WDT\_SR.

### • WDERR: Watchdog Error

0: No Watchdog error occurred since the last read of WDT\_SR.

1: At least one Watchdog error occurred since the last read of WDT\_SR.

### 19.2.2 Read Operations

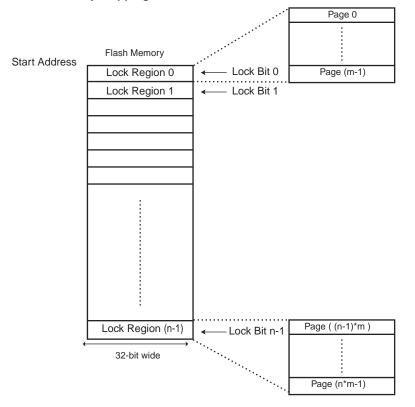

An optimized controller manages embedded Flash reads. A system of 2 x 32-bit buffers is added in order to start access at following address during the second read, thus increasing performance when the processor is running in Thumb mode (16-bit instruction set). See Figure 19-2, Figure 19-3 and Figure 19-4.

This optimization concerns only Code Fetch and not Data.

The read operations can be performed with or without wait state. Up to 3 wait states can be programmed in the field FWS (Flash Wait State) in the Flash Mode Register MC\_FMR (see "MC Flash Mode Register" on page 108). Defining FWS to be 0 enables the single-cycle access of the embedded Flash.

The Flash memory is accessible through 8-, 16- and 32-bit reads.

As the Flash block size is smaller than the address space reserved for the internal memory area, the embedded Flash wraps around the address space and appears to be repeated within it.

### • PAGEN: Page Number

| Command                                   | PAGEN Description                                                           |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Write Page Command                        | PAGEN defines the page number to be written.                                |  |  |  |  |

| Write Page and Lock Command               | PAGEN defines the page number to be written and its associated lock region. |  |  |  |  |

| Erase All Command                         | This field is meaningless                                                   |  |  |  |  |

| Set/Clear Lock Bit Command                | PAGEN defines one page number of the lock region to be locked or unlocked.  |  |  |  |  |

| Set/Clear General Purpose NVM Bit Command | PAGEN defines the general-purpose bit number.                               |  |  |  |  |

| Set Security Bit Command                  | This field is meaningless                                                   |  |  |  |  |

Note: Depending on the command, all the possible unused bits of PAGEN are meaningless.

### • KEY: Write Protection Key

This field should be written with the value 0x5A to enable the command defined by the bits of the register. If the field is written with a different value, the write is not performed and no action is started.

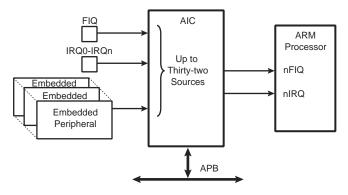

## 23. Advanced Interrupt Controller (AIC)

## 23.1 Overview

The Advanced Interrupt Controller (AIC) is an 8-level priority, individually maskable, vectored interrupt controller, providing handling of up to thirty-two interrupt sources. It is designed to substantially reduce the software and real-time overhead in handling internal and external interrupts.

The AIC drives the nFIQ (fast interrupt request) and the nIRQ (standard interrupt request) inputs of an ARM processor. Inputs of the AIC are either internal peripheral interrupts or external interrupts coming from the product's pins.

The 8-level Priority Controller allows the user to define the priority for each interrupt source, thus permitting higher priority interrupts to be serviced even if a lower priority interrupt is being treated.

Internal interrupt sources can be programmed to be level sensitive or edge triggered. External interrupt sources can be programmed to be positive-edge or negative-edge triggered or high-level or low-level sensitive.

The fast forcing feature redirects any internal or external interrupt source to provide a fast interrupt rather than a normal interrupt.

## 23.2 Block Diagram

Figure 23-1. Block Diagram

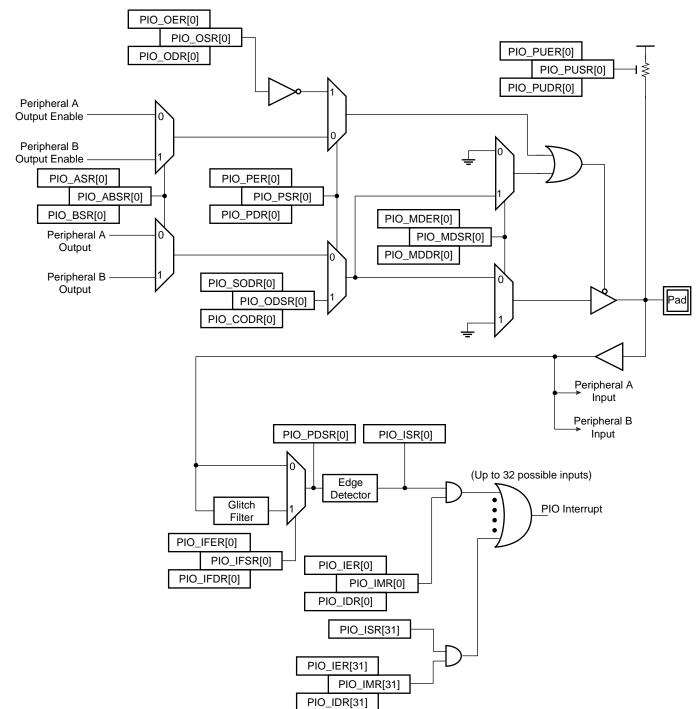

## 27.4 Functional Description

The PIO Controller features up to 32 fully-programmable I/O lines. Most of the control logic associated to each I/O is represented in Figure 27-3. In this description each signal shown represents but one of up to 32 possible indexes.

### Figure 27-3. I/O Line Control Logic

### 27.4.1 Pull-up Resistor Control

Each I/O line is designed with an embedded pull-up resistor. The pull-up resistor can be enabled or disabled by writing respectively PIO\_PUER (Pull-up Enable Register) and PIO\_PUDR (Pull-up Disable Resistor). Writing in these registers

# Atmel

## 27.5 I/O Lines Programming Example

The programing example as shown in Table 27-1 below is used to define the following configuration.

- 4-bit output port on I/O lines 0 to 3, (should be written in a single write operation), open-drain, with pull-up resistor

- Four output signals on I/O lines 4 to 7 (to drive LEDs for example), driven high and low, no pull-up resistor

- Four input signals on I/O lines 8 to 11 (to read push-button states for example), with pull-up resistors, glitch filters and input change interrupts

- Four input signals on I/O line 12 to 15 to read an external device status (polled, thus no input change interrupt), no pull-up resistor, no glitch filter

- I/O lines 16 to 19 assigned to peripheral A functions with pull-up resistor

- I/O lines 20 to 23 assigned to peripheral B functions, no pull-up resistor

- I/O line 24 to 27 assigned to peripheral A with Input Change Interrupt and pull-up resistor

| Register | Value to be Written |

|----------|---------------------|

| PIO_PER  | 0x0000 FFFF         |

| PIO_PDR  | 0x0FFF 0000         |

| PIO_OER  | 0x0000 00FF         |

| PIO_ODR  | 0x0FFF FF00         |

| PIO_IFER | 0x0000 0F00         |

| PIO_IFDR | 0x0FFF F0FF         |

| PIO_SODR | 0x0000 0000         |

| PIO_CODR | 0x0FFF FFFF         |

| PIO_IER  | 0x0F00 0F00         |

| PIO_IDR  | 0x00FF F0FF         |

| PIO_MDER | 0x0000 000F         |

| PIO_MDDR | 0x0FFF FFF0         |

| PIO_PUDR | 0x00F0 00F0         |

| PIO_PUER | 0x0F0F FF0F         |

| PIO_ASR  | 0x0F0F 0000         |

| PIO_BSR  | 0x00F0 0000         |

| PIO_OWER | 0x0000 000F         |

| PIO_OWDR | 0x0FFF FFF0         |

### Table 27-1. Programming Example

## 31.8.11 SSC Receive Compare 0 Register

| Name:        | SSC_RC  | COR  |    |    |    |    |    |

|--------------|---------|------|----|----|----|----|----|

| Access Type: | Read-wr | rite |    |    |    |    |    |

| 31           | 30      | 29   | 28 | 27 | 26 | 25 | 24 |

| -            | _       | _    | -  | -  | _  | -  | -  |

| 23           | 22      | 21   | 20 | 19 | 18 | 17 | 16 |

| -            | _       | _    | -  | -  | _  | -  | -  |

| 15           | 14      | 13   | 12 | 11 | 10 | 9  | 8  |

|              |         |      | C  | P0 |    |    |    |

| 7            | 6       | 5    | 4  | 3  | 2  | 1  | 0  |

|              |         |      | C  | P0 |    |    |    |

• CP0: Receive Compare Data 0

### • BEEVT: External Event Effect on TIOB

| BEI | EVT | Effect |

|-----|-----|--------|

| 0   | 0   | none   |

| 0   | 1   | set    |

| 1   | 0   | clear  |

| 1   | 1   | toggle |

## • BSWTRG: Software Trigger Effect on TIOB

| BSW | /TRG | Effect |

|-----|------|--------|

| 0   | 0    | none   |

| 0   | 1    | set    |

| 1   | 0    | clear  |

| 1   | 1    | toggle |

## 32.6.8 TC Register B

| Register Name:<br>Access Type: |    | TC_RB [x=02]<br>Read-only if WAVE = 0, Read-write if WAVE = 1 |    |    |    |  |  |

|--------------------------------|----|---------------------------------------------------------------|----|----|----|--|--|

| 31                             | 30 | 29                                                            | 28 | 27 | 26 |  |  |

| -                              | -  | -                                                             | -  | -  | -  |  |  |

| 23                             | 22 | 21                                                            | 20 | 19 | 18 |  |  |

| -                              | -  | -                                                             | -  | -  | -  |  |  |

| 15                             | 14 | 13                                                            | 12 | 11 | 10 |  |  |

|                                |    |                                                               | F  | RB |    |  |  |

| 7                              | 6  | 5                                                             | 4  | 3  | 2  |  |  |

|                                |    |                                                               | F  | RB |    |  |  |

# • RB: Register B

RB contains the Register B value in real time.

25

\_

17

-

9

1

24

\_

16

\_

8

0

## 33.6.4 PWM Status Register

| Register Name: | PWM_S   | R   |    |       |       |       |       |

|----------------|---------|-----|----|-------|-------|-------|-------|

| Access Type:   | Read-or | nly |    |       |       |       |       |

| 31             | 30      | 29  | 28 | 27    | 26    | 25    | 24    |

| -              | _       | _   | -  | -     | -     | -     | -     |

| 23             | 22      | 21  | 20 | 19    | 18    | 17    | 16    |

| -              | _       | _   | -  | _     | _     | _     | -     |

| 15             | 14      | 13  | 12 | 11    | 10    | 9     | 8     |

| -              | _       | _   | -  | -     | -     | _     | -     |

| 7              | 6       | 5   | 4  | 3     | 2     | 1     | 0     |

| -              | _       | _   | _  | CHID3 | CHID2 | CHID1 | CHID0 |

### • CHIDx: Channel ID

0 = PWM output for channel x is disabled.

1 = PWM output for channel x is enabled.

### 33.6.8 PWM Interrupt Status Register

| Register Name: | PWM_IS  | SR        |    |       |       |       |       |  |  |  |

|----------------|---------|-----------|----|-------|-------|-------|-------|--|--|--|

| Access Type:   | Read-on | Read-only |    |       |       |       |       |  |  |  |

| 31             | 30      | 29        | 28 | 27    | 26    | 25    | 24    |  |  |  |

| -              | _       | -         | -  | -     | -     | -     | -     |  |  |  |

| 23             | 22      | 21        | 20 | 19    | 18    | 17    | 16    |  |  |  |

| _              | _       | _         | -  | -     | _     | -     | _     |  |  |  |

| 15             | 14      | 13        | 12 | 11    | 10    | 9     | 8     |  |  |  |

| _              | _       | —         | -  | -     | -     | -     | -     |  |  |  |

| 7              | 6       | 5         | 4  | 3     | 2     | 1     | 0     |  |  |  |

| _              | _       | _         | _  | CHID3 | CHID2 | CHID1 | CHID0 |  |  |  |

### • CHIDx: Channel ID

0 = No new channel period has been achieved since the last read of the PWM\_ISR register.

1 = At least one new channel period has been achieved since the last read of the PWM\_ISR register.

Note: Reading PWM\_ISR automatically clears CHIDx flags.

Once the resume is detected on the bus, the WAKEUP signal in the UDP\_ISR is set. It may generate an interrupt if the corresponding bit in the UDP\_IMR register is set. This interrupt may be used to wake up the core, enable PLL and main oscillators and configure clocks.

**Warning**: Read, write operations to the UDP registers are allowed only if MCK is enabled for the UDP peripheral. MCK for the UDP must be enabled before clearing the WAKEUP bit in the UDP\_ICR register and clearing TXVDIS in the UDP\_TXVC register.

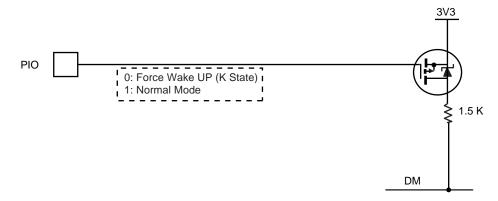

### 34.5.3.8 Sending a Device Remote Wakeup

In Suspend state it is possible to wake up the host sending an external resume.

- The device must wait at least 5 ms after being entered in suspend before sending an external resume.

- The device has 10 ms from the moment it starts to drain current and it forces a K state to resume the host.

- The device must force a K state from 1 to 15 ms to resume the host

To force a K state to the bus (DM at 3.3V and DP tied to GND), it is possible to use a transistor to connect a pullup on DM. The K state is obtained by disabling the pullup on DP and enabling the pullup on DM. This should be under the control of the application.

### Figure 34-15. Board Schematic to Drive a K State

### 36.7.3.6 Remote Frame Handling

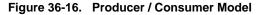

Producer/consumer model is an efficient means of handling broadcasted messages. The push model allows a producer to broadcast messages; the pull model allows a customer to ask for messages.

In Pull Mode, a consumer transmits a remote frame to the producer. When the producer receives a remote frame, it sends the answer accepted by one or many consumers. Using transmit and receive mailboxes, a consumer must dedicate two mailboxes, one in Transmit Mode to send remote frames, and at least one in Receive Mode to capture the producer's answer. The same structure is applicable to a producer: one reception mailbox is required to get the remote frame and one transmit mailbox to answer.

Mailboxes can be configured in Producer or Consumer Mode. A lonely mailbox can handle the remote frame and the answer. With 8 mailboxes, the CAN controller can handle 8 independent producers/consumers.

# Atmel

At 100 Mbit/s, it takes 960 ns to transmit or receive 12 bytes of data. In addition, six master clock cycles should be allowed for data to be loaded from the bus and to propagate through the FIFOs. For a 60 MHz master clock this takes 100 ns, making the bus latency requirement 860 ns.

### 37.3.1.2 Receive Buffers

Received frames, including CRC/FCS optionally, are written to receive buffers stored in memory. Each receive buffer is 128 bytes long. The start location for each receive buffer is stored in memory in a list of receive buffer descriptors at a location pointed to by the receive buffer queue pointer register. The receive buffer start location is a word address. For the first buffer of a frame, the start location can be offset by up to three bytes depending on the value written to bits 14 and 15 of the network configuration register. If the start location of the buffer is offset the available length of the first buffer of a frame is reduced by the corresponding number of bytes.

Each list entry consists of two words, the first being the address of the receive buffer and the second being the receive status. If the length of a receive frame exceeds the buffer length, the status word for the used buffer is written with zeroes except for the "start of frame" bit and the offset bits, if appropriate. Bit zero of the address field is written to one to show the buffer has been used. The receive buffer manager then reads the location of the next receive buffer and fills that with receive frame data. The final buffer descriptor status word contains the complete frame status. Refer to Table 37-1 for details of the receive buffer descriptor list.

| Bit   | Function                                                                                                                                                     |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Word 0                                                                                                                                                       |

| 31:2  | Address of beginning of buffer                                                                                                                               |

| 1     | Wrap - marks last descriptor in receive buffer descriptor list.                                                                                              |

| 0     | Ownership - needs to be zero for the EMAC to write data to the receive buffer. The EMAC sets this to one once it has successfully written a frame to memory. |

|       | Software has to clear this bit before the buffer can be used again.                                                                                          |

|       | Word 1                                                                                                                                                       |

| 31    | Global all ones broadcast address detected                                                                                                                   |

| 30    | Multicast hash match                                                                                                                                         |

| 29    | Unicast hash match                                                                                                                                           |

| 28    | External address match                                                                                                                                       |

| 27    | Reserved for future use                                                                                                                                      |

| 26    | Specific address register 1 match                                                                                                                            |

| 25    | Specific address register 2 match                                                                                                                            |

| 24    | Specific address register 3 match                                                                                                                            |

| 23    | Specific address register 4 match                                                                                                                            |

| 22    | Type ID match                                                                                                                                                |

| 21    | VLAN tag detected (i.e., type id of 0x8100)                                                                                                                  |

| 20    | Priority tag detected (i.e., type id of 0x8100 and null VLAN identifier)                                                                                     |

| 19:17 | VLAN priority (only valid if bit 21 is set)                                                                                                                  |

| 16    | Concatenation format indicator (CFI) bit (only valid if bit 21 is set)                                                                                       |

| 15    | End of frame - when set the buffer contains the end of a frame. If end of frame is not set, then the only other valid status are bits 12, 13 and 14.         |

### Table 37-1. Receive Buffer Descriptor Entry

### 37.5.26 EMAC Statistic Registers

These registers reset to zero on a read and stick at all ones when they count to their maximum value. They should be read frequently enough to prevent loss of data. The receive statistics registers are only incremented when the receive enable bit is set in the network control register. To write to these registers, bit 7 must be set in the network control register. The statistics register block contains the following registers.

| Register Name<br>Access Type: | : EMAC_F<br>Read-wr |    |         |    |    |    |    |

|-------------------------------|---------------------|----|---------|----|----|----|----|

| 31                            | 30                  | 29 | 28      | 27 | 26 | 25 | 24 |

| -                             | _                   | _  | -       | _  | _  | _  | _  |

| 23                            | 22                  | 21 | 20      | 19 | 18 | 17 | 16 |

| _                             | -                   | —  | -       | —  | _  | —  | _  |

| 15                            | 14                  | 13 | 12      | 11 | 10 | 9  | 8  |

|                               |                     |    | FR      | OK |    |    |    |

| 7                             | 6                   | 5  | 4<br>EP | 3  | 2  | 1  | 0  |

| FROK                          |                     |    |         |    |    |    |    |

### 37.5.26.1 Pause Frames Received Register

### • FROK: Pause Frames Received OK

A 16-bit register counting the number of good pause frames received. A good frame has a length of 64 to 1518 (1536 if bit 8 set in network configuration register) and has no FCS, alignment or receive symbol errors.

### 37.5.26.2 Frames Transmitted OK Register

| Register Name:<br>Access Type: | EMAC_I<br>Read-wi |      |    |    |    |    |    |  |  |

|--------------------------------|-------------------|------|----|----|----|----|----|--|--|

| 31                             | 30                | 29   | 28 | 27 | 26 | 25 | 24 |  |  |

| -                              | —                 | -    | -  | -  | -  | -  | -  |  |  |

| 23                             | 22                | 21   | 20 | 19 | 18 | 17 | 16 |  |  |

|                                |                   | FTOK |    |    |    |    |    |  |  |

| 15                             | 14                | 13   | 12 | 11 | 10 | 9  | 8  |  |  |

|                                |                   |      | FT | OK |    |    |    |  |  |

| 7                              | 6                 | 5    | 4  | 3  | 2  | 1  | 0  |  |  |

|                                | FTOK              |      |    |    |    |    |    |  |  |

### • FTOK: Frames Transmitted OK

A 24-bit register counting the number of frames successfully transmitted, i.e., no underrun and not too many retries.

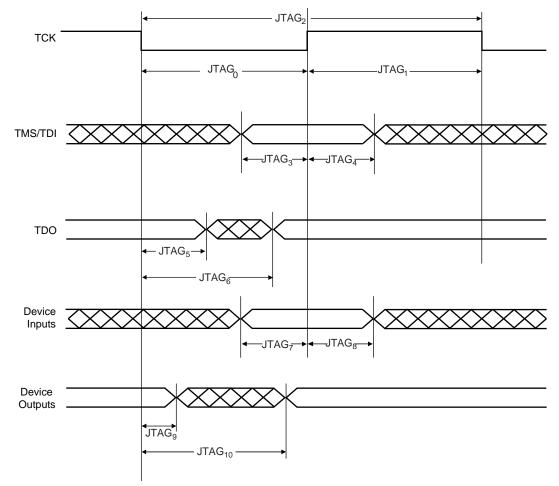

| Symbol             | Parameter                      | Conditions | Min | Max | Units |

|--------------------|--------------------------------|------------|-----|-----|-------|

| JTAG <sub>0</sub>  | TCK Low Half-period            | (1)        | 6.5 |     | ns    |

| JTAG <sub>1</sub>  | TCK High Half-period           | (1)        | 5.5 |     | ns    |

| JTAG <sub>2</sub>  | TCK Period                     | (1)        | 12  |     | ns    |

| JTAG <sub>3</sub>  | TDI, TMS Setup before TCK High | (1)        | 2   |     | ns    |

| JTAG <sub>4</sub>  | TDI, TMS Hold after TCK High   | (1)        | 3   |     | ns    |

| JTAG <sub>5</sub>  | TDO Hold Time                  | (1)        | 4   |     | ns    |

| JTAG <sub>6</sub>  | TCK Low to TDO Valid           | (1)        |     | 16  | ns    |

| JTAG <sub>7</sub>  | Device Inputs Setup Time       | (1)        | 0   |     | ns    |

| JTAG <sub>8</sub>  | Device Inputs Hold Time        | (1)        | 3   |     | ns    |

| JTAG <sub>9</sub>  | Device Outputs Hold Time       | (1)        | 6   |     | ns    |

| JTAG <sub>10</sub> | TCK to Device Outputs Valid    | (1)        |     | 18  | ns    |

### Table 38-28. JTAG Interface Timing specification

Note: 1. V<sub>VDDIO</sub> from 3.0V to 3.6V, maximum external capacitor = 40pF

### Figure 38-11. JTAG Interface Signals

## Atmel

None.

### 41.4.8.6 SPI: Bad Serial Clock Generation on 2nd Chip Select

Bad Serial clock generation on the 2nd chip select when SCBR = 1, CPOL = 1 and NCPHA = 0.

This occurs using SPI with the following conditions:

- Master mode

- CPOL = 1 and NCPHA = 0

- Multiple chip selects are used with one transfer with Baud rate (SCBR) equal to 1 (i.e., when serial clock frequency equals the system clock frequency) and the other transfers set with SCBR are not equal to 1

- Transmitting with the slowest chip select and then with the fastest one, then an additional pulse is generated on output SPCK during the second transfer.

Problem Fix/Workaround

Do not use a multiple Chip Select configuration where at least one SCRx register is configured with SCBR = 1 and the others differ from 1 if NCPHA = 0 and CPOL = 1.

If all chip selects are configured with Baudrate = 1, the issue does not appear

### 41.4.8.7 SPI: Software Reset must be Written Twice

If a software reset (SWRST in the SPI Control Register) is performed, the SPI may not work properly (the clock is enabled before the chip select.)

Problem Fix/Workaround

The SPI Control Register field, SWRST (Software Reset) needs to be written twice to be correctly set.

### 41.4.9 Synchronous Serial Controller (SSC)

41.4.9.1 SSC: Periodic Transmission Limitations in Master Mode

If the Least Significant Bit is sent first (MSBF = 0), the first TAG during the frame synchro is not sent. Problem Fix/Workaround

None.

### 41.4.9.2 SSC: Transmitter Limitations in Slave Mode

If TK is programmed as output and TF is programmed as input, it is impossible to emit data when the start of edge (rising or falling) of synchro has a Start Delay equal to zero. Problem Fix/Workaround

None.

### 41.4.9.3 SSC: Transmitter Limitations in Slave Mode

If TK is programmed as an input and TF is programmed as an output and requested to be set to low/high during data emission, the Frame Synchro signal is generated one bit clock period after the data start and one data bit is lost. This problem does not exist when generating a periodic synchro.

Problem Fix/Workaround

The data need to be delayed for one bit clock period with an external assembly. In the following schematic, TD, TK and NRST are AT91SAM7X signals, TXD is the delayed data to connect to the device.