#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                     |

| Core Size                  | 16/32-Bit                                                                 |

| Speed                      | 55MHz                                                                     |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, SPI, SSC, UART/USART, USB             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 62                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                             |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-TFBGA                                                                 |

| Supplier Device Package    | 100-TFBGA (9x9)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7x512-cu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 11.2.4.3 Exception Types

The ARM7TDMI supports five types of exception and a privileged processing mode for each type. The types of exceptions are:

- fast interrupt (FIQ)

- normal interrupt (IRQ)

- memory aborts (used to implement memory protection or virtual memory)

- attempted execution of an undefined instruction

- software interrupts (SWIs)

Exceptions are generated by internal and external sources.

More than one exception can occur in the same time.

When an exception occurs, the banked version of R14 and the SPSR for the exception mode are used to save state.

To return after handling the exception, the SPSR is moved to the CPSR, and R14 is moved to the PC. This can be done in two ways:

- by using a data-processing instruction with the S-bit set, and the PC as the destination

- by using the Load Multiple with Restore CPSR instruction (LDM)

## 11.2.5 ARM Instruction Set Overview

The ARM instruction set is divided into:

- Branch instructions

- Data processing instructions

- Status register transfer instructions

- Load and Store instructions

- Coprocessor instructions

- Exception-generating instructions

ARM instructions can be executed conditionally. Every instruction contains a 4-bit condition code field (bit[31:28]). Table 11-2 gives the ARM instruction mnemonic list.

| Mnemonic | Operation                       | Mner |

|----------|---------------------------------|------|

| MOV      | Move                            | CDP  |

| ADD      | Add                             | MVN  |

| SUB      | Subtract                        | ADC  |

| RSB      | Reverse Subtract                | SBC  |

| CMP      | Compare                         | RSC  |

| TST      | Test                            | CMN  |

| AND      | Logical AND                     | TEQ  |

| EOR      | Logical Exclusive OR            | BIC  |

| MUL      | Multiply                        | ORR  |

| SMULL    | Sign Long Multiply              | MLA  |

| SMLAL    | Signed Long Multiply Accumulate | UMUL |

| MSR      | Move to Status Register         | UMLA |

| В        | Branch                          | MRS  |

| вх       | Branch and Exchange             | BL   |

Table 11-2.

ARM Instruction Mnemonic List

| Mnemonic | Operation                         |

|----------|-----------------------------------|

| CDP      | Coprocessor Data Processing       |

| MVN      | Move Not                          |

| ADC      | Add with Carry                    |

| SBC      | Subtract with Carry               |

| RSC      | Reverse Subtract with Carry       |

| CMN      | Compare Negated                   |

| TEQ      | Test Equivalence                  |

| BIC      | Bit Clear                         |

| ORR      | Logical (inclusive) OR            |

| MLA      | Multiply Accumulate               |

| UMULL    | Unsigned Long Multiply            |

| UMLAL    | Unsigned Long Multiply Accumulate |

| MRS      | Move From Status Register         |

| BL       | Branch and Link                   |

| Bit<br>Number | Pin Name              | Pin Type                  | Associated BSR<br>Cells |  |

|---------------|-----------------------|---------------------------|-------------------------|--|

| 117           |                       |                           | INPUT                   |  |

| 116           | PA18/SPI0_SPCK        | IN/OUT                    | OUTPUT                  |  |

| 115           |                       |                           | CONTROL                 |  |

| 114           |                       |                           | INPUT                   |  |

| 113           | PB9/EMDIO             | IN/OUT                    | OUTPUT                  |  |

| 112           |                       |                           | CONTROL                 |  |

| 111           |                       |                           | INPUT                   |  |

| 110           | PB8/EMDC              | IN/OUT                    | OUTPUT                  |  |

| 109           |                       |                           | CONTROL                 |  |

| 108           |                       |                           | INPUT                   |  |

| 107           | PB14/ERX3/SPI0_NPCS2  | IN/OUT                    | OUTPUT                  |  |

| 106           |                       |                           | CONTROL                 |  |

| 105           |                       |                           |                         |  |

| 104           | PB13/ERX2/SPI0_NPCS1  | IN/OUT                    | OUTPUT                  |  |

| 103           | CONTRO                |                           |                         |  |

| 102           |                       |                           | INPUT                   |  |

| 101           | PB6/ERX1              | IN/OUT                    | OUTPUT                  |  |

| 100           |                       |                           | CONTROL                 |  |

| 99            |                       |                           | INPUT                   |  |

| 98            | PB5/ERX0              | IN/OUT                    | OUTPUT                  |  |

| 97            |                       |                           | CONTROL                 |  |

| 96            |                       |                           | INPUT                   |  |

| 95            | PB15/ERXDV/ECRSDV     | IN/OUT                    | OUTPUT                  |  |

| 94            |                       |                           | CONTROL                 |  |

| 93            |                       |                           | INPUT                   |  |

| 92            | PB17/ERXCK/SPI0_NPCS3 | IN/OUT                    | OUTPUT                  |  |

| 91            |                       |                           | CONTROL                 |  |

| 90            |                       |                           | INPUT                   |  |

| 89            | PB7/ERXER             | IN/OUT                    | OUTPUT                  |  |

| 88            |                       |                           | CONTROL                 |  |

| 87            |                       |                           | INPUT                   |  |

| 86            | PB12/ETXER/TCLK0      | IN/OUT                    | OUTPUT                  |  |

| 85            |                       | [                         | CONTROL                 |  |

| 84            |                       |                           | INPUT                   |  |

| 83            | PB0/ETXCK/EREFCK/PCK0 | PB0/ETXCK/ERE<br>FCK/PCK0 | OUTPUT                  |  |

| 82            |                       |                           | CONTROL                 |  |

Table 12-2. SAM7X JTAG Boundary Scan Register (Continued)

Atmel

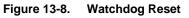

#### 13.2.4.5 Watchdog Reset

The Watchdog Reset is entered when a watchdog fault occurs. This state lasts 3 Slow Clock cycles.

When in Watchdog Reset, assertion of the reset signals depends on the WDRPROC bit in WDT\_MR:

- If WDRPROC is 0, the Processor Reset and the Peripheral Reset are asserted. The NRST line is also asserted, depending on the programming of the field ERSTL. However, the resulting low level on NRST does not result in a User Reset state.

- If WDRPROC = 1, only the processor reset is asserted.

The Watchdog Timer is reset by the proc\_nreset signal. As the watchdog fault always causes a processor reset if WDRSTEN is set, the Watchdog Timer is always reset after a Watchdog Reset, and the Watchdog is enabled by default and with a period set to a maximum.

When the WDRSTEN in WDT\_MR bit is reset, the watchdog fault has no impact on the reset controller.

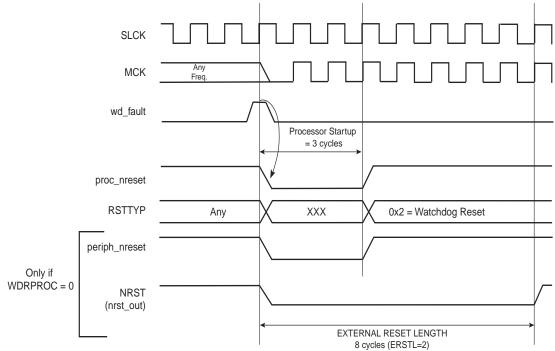

# 15. Periodic Interval Timer (PIT)

# 15.1 Overview

The Periodic Interval Timer (PIT) provides the operating system's scheduler interrupt. It is designed to offer maximum accuracy and efficient management, even for systems with long response time.

# 15.2 Block Diagram

# Figure 15-1. Periodic Interval Timer

#### Figure 18-3. Internal Memory Mapping

| Î          | 0x0000 0000   | Internal Memory Area 0                   |   | 1 M Bytes   |

|------------|---------------|------------------------------------------|---|-------------|

|            | 0x0010 0000   | Internal Memory Area 1<br>Internal Flash |   | 1 M Bytes   |

| 256M Bytes | 0x0020 0000   | Internal Memory Area 2<br>Internal SRAM  |   | 1 M Bytes   |

|            | 0x0030 0000   | Internal Memory Area 3<br>Internal ROM   | , | 1 M Bytes   |

|            | 0x0040 0000   | Undefined Areas<br>(Abort)               |   | 252 M Bytes |

|            | , 0x0FFF FFFF |                                          |   | ۲           |

#### 18.3.2.2 Internal Memory Area 0

The first 32 bytes of Internal Memory Area 0 contain the ARM processor exception vectors, in particular, the Reset Vector at address 0x0.

Before execution of the remap command, the on-chip Flash is mapped into Internal Memory Area 0, so that the ARM7TDMI reaches an executable instruction contained in Flash. After the remap command, the internal SRAM at address 0x0020 0000 is mapped into Internal Memory Area 0. The memory mapped into Internal Memory Area 0 is accessible in both its original location and at address 0x0.

#### 18.3.3 Remap Command

After execution, the Remap Command causes the Internal SRAM to be accessed through the Internal Memory Area 0.

As the ARM vectors (Reset, Abort, Data Abort, Prefetch Abort, Undefined Instruction, Interrupt, and Fast Interrupt) are mapped from address 0x0 to address 0x20, the Remap Command allows the user to redefine dynamically these vectors under software control.

The Remap Command is accessible through the Memory Controller User Interface by writing the MC\_RCR (Remap Control Register) RCB field to one.

The Remap Command can be cancelled by writing the MC\_RCR RCB field to one, which acts as a toggling command. This allows easy debug of the user-defined boot sequence by offering a simple way to put the chip in the same configuration as after a reset.

#### 18.3.4 Abort Status

There are two reasons for an abort to occur:

- access to an undefined address

- an access to a misaligned address.

When an abort occurs, a signal is sent back to all the masters, regardless of which one has generated the access. However, only the ARM7TDMI can take an abort signal into account, and only under the condition that it was generating an access. The Peripheral DMA Controller and the EMAC do not handle the abort input signal. Note that the connections are not represented in Figure 18-1.

To facilitate debug or for fault analysis by an operating system, the Memory Controller integrates an Abort Status register set.

The full 32-bit wide abort address is saved in MC\_AASR. Parameters of the access are saved in MC\_ASR and include:

• the size of the request (field ABTSZ)

# 19.3.1 MC Flash Mode Register

| Register Name<br>Access Type:<br>Offset: (EFC0)<br>Offset: (EFC1) | : MC_FMI<br>Read-wr<br>0x60<br>0x70 |    |    |       |       |    |      |

|-------------------------------------------------------------------|-------------------------------------|----|----|-------|-------|----|------|

| 31                                                                | 30                                  | 29 | 28 | 27    | 26    | 25 | 24   |

| -                                                                 | -                                   | -  | -  | -     | -     | -  | -    |

| 23                                                                | 22                                  | 21 | 20 | 19    | 18    | 17 | 16   |

|                                                                   |                                     |    | FN | 1CN   |       |    |      |

| 15                                                                | 14                                  | 13 | 12 | 11    | 10    | 9  | 8    |

| _                                                                 | _                                   | _  | -  | _     | _     | F۷ | VS   |

| 7                                                                 | 6                                   | 5  | 4  | 3     | 2     | 1  | 0    |

| NEBP                                                              | _                                   | -  | -  | PROGE | LOCKE | _  | FRDY |

#### • FRDY: Flash Ready Interrupt Enable

0: Flash Ready does not generate an interrupt.

1: Flash Ready generates an interrupt.

## • LOCKE: Lock Error Interrupt Enable

0: Lock Error does not generate an interrupt.

1: Lock Error generates an interrupt.

#### • PROGE: Programming Error Interrupt Enable

0: Programming Error does not generate an interrupt.

1: Programming Error generates an interrupt.

#### • NEBP: No Erase Before Programming

0: A page erase is performed before programming.

1: No erase is performed before programming.

## • FWS: Flash Wait State

This field defines the number of wait states for read and write operations:

| FWS | Read Operations | Write Operations |

|-----|-----------------|------------------|

| 0   | 1 cycle         | 2 cycles         |

| 1   | 2 cycles        | 3 cycles         |

| 2   | 3 cycles        | 4 cycles         |

| 3   | 4 cycles        | 4 cycles         |

#### Figure 23-10. Fast Forcing

The Variable Peripheral Selection allows buffer transfers with multiple peripherals without reprogramming the Mode Register. Data written in SPI\_TDR is 32 bits wide and defines the real data to be transmitted and the peripheral it is destined to. Using the PDC in this mode requires 32-bit wide buffers, with the data in the LSBs and the PCS and LASTXFER fields in the MSBs, however the SPI still controls the number of bits (8 to16) to be transferred through MISO and MOSI lines with the chip select configuration registers. This is not the optimal means in term of memory size for the buffers, but it provides a very effective means to exchange data with several peripherals without any intervention of the processor.

#### 28.6.3.6 Peripheral Chip Select Decoding

The user can program the SPI to operate with up to 15 peripherals by decoding the four Chip Select lines, NPCS0 to NPCS3 with an external logic. This can be enabled by writing the PCSDEC bit at 1 in the Mode Register (SPI\_MR).

When operating without decoding, the SPI makes sure that in any case only one chip select line is activated, i.e. driven low at a time. If two bits are defined low in a PCS field, only the lowest numbered chip select is driven low.

When operating with decoding, the SPI directly outputs the value defined by the PCS field of either the Mode Register or the Transmit Data Register (depending on PS).

As the SPI sets a default value of 0xF on the chip select lines (i.e. all chip select lines at 1) when not processing any transfer, only 15 peripherals can be decoded.

The SPI has only four Chip Select Registers, not 15. As a result, when decoding is activated, each chip select defines the characteristics of up to four peripherals. As an example, SPI\_CRS0 defines the characteristics of the externally decoded peripherals 0 to 3, corresponding to the PCS values 0x0 to 0x3. Thus, the user has to make sure to connect compatible peripherals on the decoded chip select lines 0 to 3, 4 to 7, 8 to 11 and 12 to 14.

## 28.6.3.7 Peripheral Deselection

When operating normally, as soon as the transfer of the last data written in SPI\_TDR is completed, the NPCS lines all rise. This might lead to runtime error if the processor is too long in responding to an interrupt, and thus might lead to difficulties for interfacing with some serial peripherals requiring the chip select line to remain active during a full set of transfers.

To facilitate interfacing with such devices, the Chip Select Register can be programmed with the CSAAT bit (Chip Select Active After Transfer) at 1. This allows the chip select lines to remain in their current state (low = active) until transfer to another peripheral is required.

Figure 28-8 shows different peripheral deselection cases and the effect of the CSAAT bit.

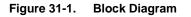

# 31. Synchronous Serial Controller (SSC)

# 31.1 Overview

The Atmel Synchronous Serial Controller (SSC) provides a synchronous communication link with external devices. It supports many serial synchronous communication protocols generally used in audio and telecom applications such as I2S, Short Frame Sync, Long Frame Sync, etc.

The SSC contains an independent receiver and transmitter and a common clock divider. The receiver and the transmitter each interface with three signals: the TD/RD signal for data, the TK/RK signal for the clock and the TF/RF signal for the Frame Sync. The transfers can be programmed to start automatically or on different events detected on the Frame Sync signal.

The SSC's high-level of programmability and its two dedicated PDC channels of up to 32 bits permit a continuous high bit rate data transfer without processor intervention.

Featuring connection to two PDC channels, the SSC permits interfacing with low processor overhead to the following:

- CODEC's in master or slave mode

- DAC through dedicated serial interface, particularly I2S

- Magnetic card reader

# 31.2 Block Diagram

# 31.8.2 SSC Clock Mode Register

| Name:<br>Access Type: | SSC_CM<br>Read-wr |    |    |    |    |    |    |

|-----------------------|-------------------|----|----|----|----|----|----|

| 31                    | 30                | 29 | 28 | 27 | 26 | 25 | 24 |

| -                     | _                 | _  | _  | _  | _  | _  | —  |

| 23                    | 22                | 21 | 20 | 19 | 18 | 17 | 16 |

| -                     | _                 | _  | -  | -  | _  | _  | _  |

| 15                    | 14                | 13 | 12 | 11 | 10 | 9  | 8  |

| -                     | _                 | —  | -  |    | D  | IV |    |

| 7                     | 6                 | 5  | 4  | 3  | 2  | 1  | 0  |

|                       |                   |    | D  | IV |    |    |    |

## • DIV: Clock Divider

0: The Clock Divider is not active.

Any Other Value: The Divided Clock equals the Master Clock divided by 2 times DIV. The maximum bit rate is MCK/2. The minimum bit rate is  $MCK/2 \times 4095 = MCK/8190$ .

# 31.8.14 SSC Interrupt Enable Register

| Name:        | SSC_IEI  | R     |       |        |       |         |       |

|--------------|----------|-------|-------|--------|-------|---------|-------|

| Access Type: | Write-on | ly    |       |        |       |         |       |

| 31           | 30       | 29    | 28    | 27     | 26    | 25      | 24    |

| -            | -        | -     | -     | -      | -     | -       | -     |

| 23           | 22       | 21    | 20    | 19     | 18    | 17      | 16    |

| _            | _        | _     | _     | _      | _     | _       | _     |

| 15           | 14       | 13    | 12    | 11     | 10    | 9       | 8     |

| -            | -        | -     | -     | RXSYN  | TXSYN | CP1     | CP0   |

| 7            | 6        | 5     | 4     | 3      | 2     | 1       | 0     |

| RXBUFF       | ENDRX    | OVRUN | RXRDY | TXBUFE | ENDTX | TXEMPTY | TXRDY |

# • TXRDY: Transmit Ready Interrupt Enable

- 0: No effect.

- 1: Enables the Transmit Ready Interrupt.

# • TXEMPTY: Transmit Empty Interrupt Enable

- 0: No effect.

- 1: Enables the Transmit Empty Interrupt.

## • ENDTX: End of Transmission Interrupt Enable

- 0: No effect.

- 1: Enables the End of Transmission Interrupt.

# • TXBUFE: Transmit Buffer Empty Interrupt Enable

- 0: No effect.

- 1: Enables the Transmit Buffer Empty Interrupt

# • RXRDY: Receive Ready Interrupt Enable

- 0: No effect.

- 1: Enables the Receive Ready Interrupt.

# • OVRUN: Receive Overrun Interrupt Enable

- 0: No effect.

- 1: Enables the Receive Overrun Interrupt.

#### • ENDRX: End of Reception Interrupt Enable

- 0: No effect.

- 1: Enables the End of Reception Interrupt.

# • RXBUFF: Receive Buffer Full Interrupt Enable

- 0: No effect.

- 1: Enables the Receive Buffer Full Interrupt.

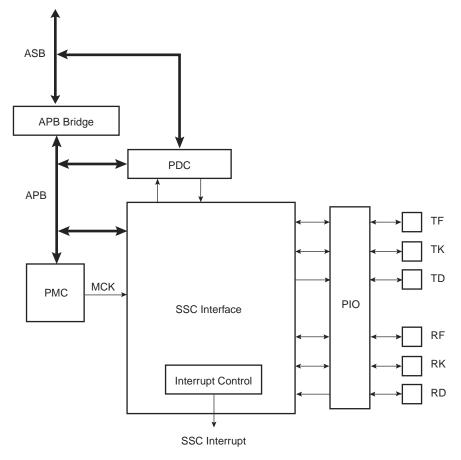

Figure 32-5. Capture Mode

Atmel

# 32.5.12 External Event/Trigger Conditions

An external event can be programmed to be detected on one of the clock sources (XC0, XC1, XC2) or TIOB. The external event selected can then be used as a trigger.

The EEVT parameter in TC\_CMR selects the external trigger. The EEVTEDG parameter defines the trigger edge for each of the possible external triggers (rising, falling or both). If EEVTEDG is cleared (none), no external event is defined.

If TIOB is defined as an external event signal (EEVT = 0), TIOB is no longer used as an output and the compare register B is not used to generate waveforms and subsequently no IRQs. In this case the TC channel can only generate a waveform on TIOA.

When an external event is defined, it can be used as a trigger by setting bit ENETRG in TC\_CMR.

As in Capture Mode, the SYNC signal and the software trigger are also available as triggers. RC Compare can also be used as a trigger depending on the parameter WAVSEL.

#### 32.5.13 Output Controller

The output controller defines the output level changes on TIOA and TIOB following an event. TIOB control is used only if TIOB is defined as output (not as an external event).

The following events control TIOA and TIOB: software trigger, external event and RC compare. RA compare controls TIOA and RB compare controls TIOB. Each of these events can be programmed to set, clear or toggle the output as defined in the corresponding parameter in TC\_CMR.

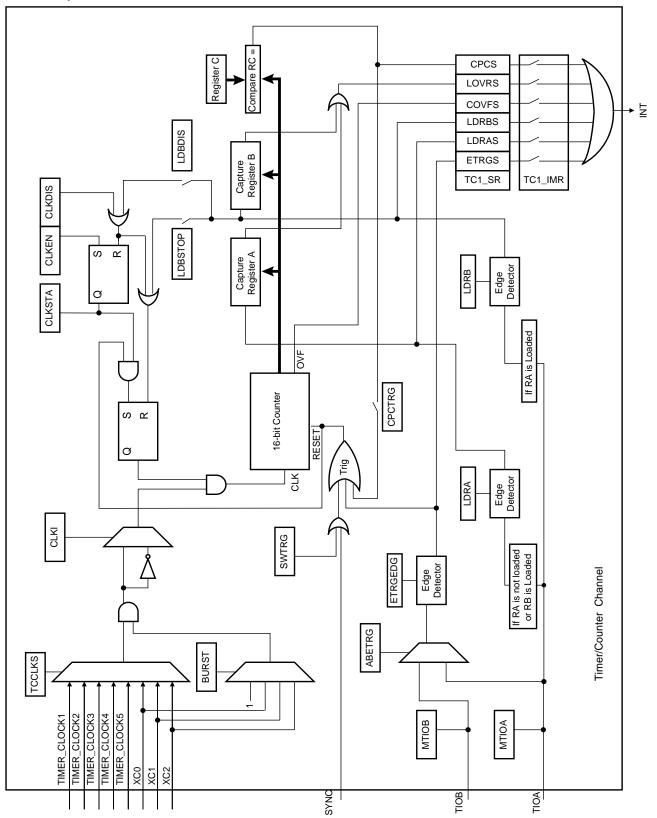

To prevent overwriting the PWM\_CUPDx by software, the user can use status events in order to synchronize his software. Two methods are possible. In both, the user must enable the dedicated interrupt in PWM\_IER at PWM Controller level.

The first method (polling method) consists of reading the relevant status bit in PWM\_ISR Register according to the enabled channel(s). See Figure 33-7.

The second method uses an Interrupt Service Routine associated with the PWM channel.

Note: Reading the PWM\_ISR register automatically clears CHIDx flags.

#### Figure 33-7. Polling Method

Note: Polarity and alignment can be modified only when the channel is disabled.

#### 33.5.3.4 Interrupts

Depending on the interrupt mask in the PWM\_IMR register, an interrupt is generated at the end of the corresponding channel period. The interrupt remains active until a read operation in the PWM\_ISR register occurs.

A channel interrupt is enabled by setting the corresponding bit in the PWM\_IER register. A channel interrupt is disabled by setting the corresponding bit in the PWM\_IDR register.

#### 34.5.3.2 Entering Attached State

When no device is connected, the USB DP and DM signals are tied to GND by 15 K $\Omega$  pull-down resistors integrated in the hub downstream ports. When a device is attached to a hub downstream port, the device connects a 1.5 K $\Omega$  pull-up resistor on DP. The USB bus line goes into IDLE state, DP is pulled up by the device 1.5 K $\Omega$  resistor to 3.3V and DM is pulled down by the 15 K $\Omega$  resistor of the host.

After pullup connection, the device enters the powered state. In this state, the UDPCK and MCK must be enabled in the Power Management Controller. The transceiver can remain disabled.

#### 34.5.3.3 From Powered State to Default State

After its connection to a USB host, the USB device waits for an end-of-bus reset. The unmaskable flag ENDBUSRES is set in the register UDP\_ISR and an interrupt is triggered.

Once the ENDBUSRES interrupt has been triggered, the device enters Default State. In this state, the UDP software must:

- Enable the default endpoint, setting the EPEDS flag in the UDP\_CSR[0] register and, optionally, enabling the interrupt for endpoint 0 by writing 1 to the UDP\_IER register. The enumeration then begins by a control transfer.

- Configure the interrupt mask register which has been reset by the USB reset detection

- Enable the transceiver clearing the TXVDIS flag in the UDP\_TXVC register.

In this state UDPCK and MCK must be enabled.

**Warning**: Each time an ENDBUSRES interrupt is triggered, the Interrupt Mask Register and UDP\_CSR registers have been reset.

#### 34.5.3.4 From Default State to Address State

After a set address standard device request, the USB host peripheral enters the address state.

**Warning**: Before the device enters in address state, it must achieve the Status IN transaction of the control transfer, i.e., the UDP device sets its new address once the TXCOMP flag in the UDP\_CSR[0] register has been received and cleared.

To move to address state, the driver software sets the FADDEN flag in the UDP\_GLB\_STAT register, sets its new address, and sets the FEN bit in the UDP\_FADDR register.

#### 34.5.3.5 From Address State to Configured State

Once a valid Set Configuration standard request has been received and acknowledged, the device enables endpoints corresponding to the current configuration. This is done by setting the EPEDS and EPTYPE fields in the UDP\_CSRx registers and, optionally, enabling corresponding interrupts in the UDP\_IER register.

#### 34.5.3.6 Entering in Suspend State

When a Suspend (no bus activity on the USB bus) is detected, the RXSUSP signal in the UDP\_ISR register is set. This triggers an interrupt if the corresponding bit is set in the UDP\_IMR register. This flag is cleared by writing to the UDP\_ICR register. Then the device enters Suspend Mode.

In this state bus powered devices must drain less than 500uA from the 5V VBUS. As an example, the microcontroller switches to slow clock, disables the PLL and main oscillator, and goes into Idle Mode. It may also switch off other devices on the board.

The USB device peripheral clocks can be switched off. Resume event is asynchronously detected. MCK and UDPCK can be switched off in the Power Management controller and the USB transceiver can be disabled by setting the TXVDIS field in the UDP\_TXVC register.

**Warning**: Read, write operations to the UDP registers are allowed only if MCK is enabled for the UDP peripheral. Switching off MCK for the UDP peripheral must be one of the last operations after writing to the UDP\_TXVC and acknowledging the RXSUSP.

#### 34.5.3.7 Receiving a Host Resume

In suspend mode, a resume event on the USB bus line is detected asynchronously, transceiver and clocks are disabled (however the pullup shall not be removed).

# 34.6.12 UDP Transceiver Control Register

| Register Name: | UDP_T   | XVC |    |    |    |    |        |

|----------------|---------|-----|----|----|----|----|--------|

| Access Type:   | Read-wr | ite |    |    |    |    |        |

| 31             | 30      | 29  | 28 | 27 | 26 | 25 | 24     |

| -              | _       | -   | -  | -  | -  | -  | -      |

| 23             | 22      | 21  | 20 | 19 | 18 | 17 | 16     |

| -              | _       | _   | -  | _  | _  | _  | -      |

| 15             | 14      | 13  | 12 | 11 | 10 | 9  | 8      |

| -              | —       | —   | -  | -  | -  | -  | TXVDIS |

| 7              | 6       | 5   | 4  | 3  | 2  | 1  | 0      |

| -              | -       | -   | -  | _  | _  | _  | _      |

**WARNING:** The UDP peripheral clock in the Power Management Controller (PMC) must be enabled before any read/write operations to the UDP registers including the UDP\_TXCV register.

# • TXVDIS: Transceiver Disable

When UDP is disabled, power consumption can be reduced significantly by disabling the embedded transceiver. This can be done by setting TXVDIS field.

To enable the transceiver, TXVDIS must be cleared.

**NOTE**: If the USB pullup is not connected on DP, the user should not write in any UDP register other than the UDP\_TXVC register. This is because if DP and DM are floating at 0, or pulled down, then SE0 is received by the device with the consequence of a USB Reset.

# 36.6 CAN Controller Features

## 36.6.1 CAN Protocol Overview

The Controller Area Network (CAN) is a multi-master serial communication protocol that efficiently supports real-time control with a very high level of security with bit rates up to 1 Mbit/s.

The CAN protocol supports four different frame types:

- Data frames: They carry data from a transmitter node to the receiver nodes. The overall maximum data frame length is 108 bits for a standard frame and 128 bits for an extended frame.

- Remote frames: A destination node can request data from the source by sending a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node then sends a data frame as a response to this node request.

- Error frames: An error frame is generated by any node that detects a bus error.

- Overload frames: They provide an extra delay between the preceding and the successive data frames or remote frames.

The Atmel CAN controller provides the CPU with full functionality of the CAN protocol V2.0 Part A and V2.0 Part B. It minimizes the CPU load in communication overhead. The Data Link Layer and part of the physical layer are automatically handled by the CAN controller itself.

The CPU reads or writes data or messages via the CAN controller mailboxes. An identifier is assigned to each mailbox. The CAN controller encapsulates or decodes data messages to build or to decode bus data frames. Remote frames, error frames and overload frames are automatically handled by the CAN controller under supervision of the software application.

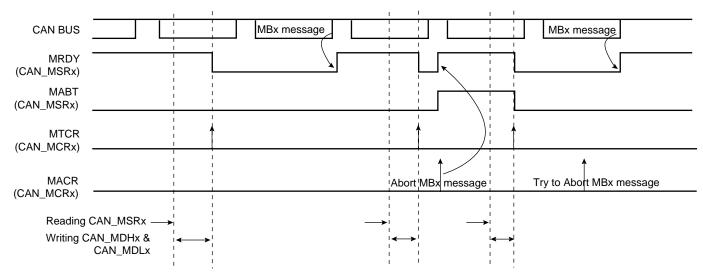

## 36.6.2 Mailbox Organization

The CAN module has 8 buffers, also called channels or mailboxes. An identifier that corresponds to the CAN identifier is defined for each active mailbox. Message identifiers can match the standard frame identifier or the extended frame identifier. This identifier is defined for the first time during the CAN initialization, but can be dynamically reconfigured later so that the mailbox can handle a new message family. Several mailboxes can be configured with the same ID.

Each mailbox can be configured in receive or in transmit mode independently. The mailbox object type is defined in the MOT field of the CAN\_MMRx register.

#### 36.6.2.1 Message Acceptance Procedure

If the MIDE field in the CAN\_MIDx register is set, the mailbox can handle the extended format identifier; otherwise, the mailbox handles the standard format identifier. Once a new message is received, its ID is masked with the CAN\_MAMx value and compared with the CAN\_MIDx value. If accepted, the message ID is copied to the CAN\_MIDx register.

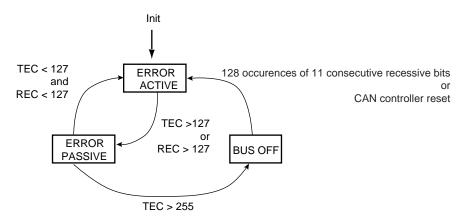

#### 36.6.4.5 Fault Confinement

To distinguish between temporary and permanent failures, every CAN controller has two error counters: REC (Receive Error Counter) and TEC (Transmit Error Counter). The two counters are incremented upon detected errors and are decremented upon correct transmissions or receptions, respectively. Depending on the counter values, the state of the node changes: the initial state of the CAN controller is Error Active, meaning that the controller can send Error Active flags. The controller changes to the Error Passive state if there is an accumulation of errors. If the CAN controller fails or if there is an extreme accumulation of errors, there is a state transition to Bus Off.

#### Figure 36-7. Line Error Mode

An error active unit takes part in bus communication and sends an active error frame when the CAN controller detects an error.

An error passive unit cannot send an active error frame. It takes part in bus communication, but when an error is detected, a passive error frame is sent. Also, after a transmission, an error passive unit waits before initiating further transmission.

A bus off unit is not allowed to have any influence on the bus.

For fault confinement, two errors counters (TEC and REC) are implemented. These counters are accessible via the CAN\_ECR register. The state of the CAN controller is automatically updated according to these counter values. If the CAN controller is in Error Active state, then the ERRA bit is set in the CAN\_SR register. The corresponding interrupt is pending while the interrupt is not masked in the CAN\_IMR register. If the CAN controller is in Error Passive Mode, then the ERRP bit is set in the CAN\_SR register and an interrupt remains pending while the ERRP bit is set in the CAN\_IMR register. If the CAN is in Bus Off Mode, then the BOFF bit is set in the CAN\_SR register. As for ERRP and ERRA, an interrupt is pending while the BOFF bit is set in the CAN\_IMR register.

When one of the error counters values exceeds 96, an increased error rate is indicated to the controller through the WARN bit in CAN\_SR register, but the node remains error active. The corresponding interrupt is pending while the interrupt is set in the CAN\_IMR register.

Refer to the Bosch CAN specification v2.0 for details on fault confinement.

#### 36.6.4.6 Error Interrupt Handler

WARN, BOFF, ERRA and ERRP (CAN\_SR) represent the current status of the CAN bus and are not latched. They reflect the current TEC and REC (CAN\_ECR) values as described in Section 36.6.4.5 "Fault Confinement" on page 492.

Based on that, if these bits are used as an interrupt, the user can enter into an interrupt and not see the corresponding status register if the TEC and REC counter have changed their state. When entering Bus Off Mode, the only way to exit from this state is 128 occurrences of 11 consecutive recessive bits or a CAN controller reset.

In Error Active Mode, the user reads:

• ERRA =1

#### 36.7.3.6 Remote Frame Handling

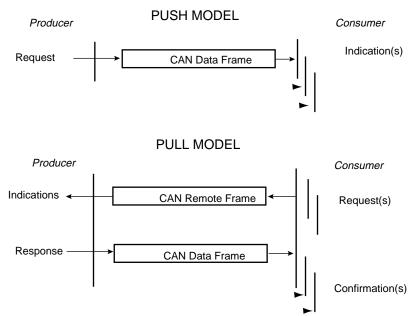

Producer/consumer model is an efficient means of handling broadcasted messages. The push model allows a producer to broadcast messages; the pull model allows a customer to ask for messages.

In Pull Mode, a consumer transmits a remote frame to the producer. When the producer receives a remote frame, it sends the answer accepted by one or many consumers. Using transmit and receive mailboxes, a consumer must dedicate two mailboxes, one in Transmit Mode to send remote frames, and at least one in Receive Mode to capture the producer's answer. The same structure is applicable to a producer: one reception mailbox is required to get the remote frame and one transmit mailbox to answer.

Mailboxes can be configured in Producer or Consumer Mode. A lonely mailbox can handle the remote frame and the answer. With 8 mailboxes, the CAN controller can handle 8 independent producers/consumers.

# Atmel

|                   | 9.6                                                                                                                                                                          | Periodic Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                   | 9.7                                                                                                                                                                          | Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

|                   | 9.8                                                                                                                                                                          | Real-time Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

|                   | 9.9                                                                                                                                                                          | PIO Controllers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

|                   | 9.10                                                                                                                                                                         | Voltage Regulator Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                 |

| 10.               | Perio                                                                                                                                                                        | herals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30                                                                                                 |

|                   | 10.1                                                                                                                                                                         | User Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

|                   | 10.2                                                                                                                                                                         | Peripheral Identifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                    |

|                   | 10.3                                                                                                                                                                         | Peripheral Multiplexing on PIO Lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                    |

|                   | 10.4                                                                                                                                                                         | PIO Controller A Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

|                   | 10.5                                                                                                                                                                         | PIO Controller B Multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

|                   | 10.6                                                                                                                                                                         | Ethernet MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

|                   | 10.7                                                                                                                                                                         | Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                    |

|                   | 10.8                                                                                                                                                                         | Two-wire Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |

|                   | 10.9                                                                                                                                                                         | USART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

|                   |                                                                                                                                                                              | Serial Synchronous Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |

|                   |                                                                                                                                                                              | Timer Counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

|                   |                                                                                                                                                                              | Pulse Width Modulation Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

|                   |                                                                                                                                                                              | USB Device Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                    |

|                   |                                                                                                                                                                              | CAN Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

|                   |                                                                                                                                                                              | Analog-to-Digital Converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                    |

|                   |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

| 11.               | ARM                                                                                                                                                                          | 7TDMI Processor Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

|                   | 11.1                                                                                                                                                                         | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

|                   | 11.2                                                                                                                                                                         | ARM7TDMI Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39                                                                                                 |

|                   |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

| 12.               | Debu                                                                                                                                                                         | ig and Test Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                 |

| 12.               | Debu<br>12.1                                                                                                                                                                 | ig and Test Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                    |

| 12.               |                                                                                                                                                                              | Ig and Test Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44                                                                                                 |

| 12.               | 12.1                                                                                                                                                                         | Description<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44<br>44                                                                                           |

| 12.               | 12.1<br>12.2                                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>44<br>45                                                                                     |

| 12.               | 12.1<br>12.2<br>12.3                                                                                                                                                         | Description<br>Block Diagram<br>Application Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44<br>44<br>45<br>46                                                                               |

|                   | 12.1<br>12.2<br>12.3<br>12.4<br>12.5                                                                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>45<br>46<br>46                                                                               |

|                   | 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>Rese                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>45<br>46<br>46                                                                               |

|                   | 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br><b>Rese</b><br>13.1                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>45<br>46<br>46<br>55                                                                         |

|                   | 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br><b>Rese</b><br>13.1<br>13.2                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44<br>45<br>46<br>46<br>55<br>55<br>56                                                             |