Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 4MHz                                                                     |

| Connectivity               | I <sup>2</sup> C                                                         |

| Peripherals                | POR, Temp Sensor, WDT                                                    |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | Slope A/D                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 28-SSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic14000-04-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains the various enable and flag bits for the Timer0 overflow and peripheral interrupts. Figure 4-5 shows the bits for the INTCON register.

Note: The TOIF will be set by the specified condition even if the corresponding Interrupt Enable Bit is cleared (interrupt disabled) or the GIE bit is cleared (all interrupts disabled). Before enabling interrupt, clear the interrupt flag, to ensure that the program does not immediately branch to the peripheral interrupt service routine

| R/W  | R/W  | R/W  | R/W | R/W | R/W  | R/W | R/W  | Register: INTCON W: Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|------|------|-----|-----|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE  | PEIE | TOIE | r   | r   | TOIF | r   | r    | Address: 0Bh or 8Bh R: Readable<br>POR value: 0000 000xb U: Unimplemented,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit7 |      |      |     |     |      |     | bit0 | read as '0'     Reserved. This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.     Reserved. This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.     TOIF: TMR0 overflow interrupt flag     1 = The TMR0 has overflowed Must be cleared by software     0 = TMR0 did not overflow     Reserved. This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products. |

|      |      |      |     |     |      |     |      | <b>Reserved.</b> This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |      |      |     |     |      |     |      | <b>TOIE:</b> TMR0 interrupt enable bit<br>1 = Enables TOIF interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |      |      |     |     |      |     |      | 0 = Disables T0IF interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | L    |      |     |     |      |     |      | PEIE: Peripheral interrupt enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |      |      |     |     |      |     |      | <ul><li>1 = Enables all un-masked peripheral interrupts</li><li>0 = Disables all peripheral interrupts</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |      |      |     |     |      |     |      | GIE: Global interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |      |      |     |     |      |     |      | 1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# FIGURE 4-5: INTCON REGISTER

### 4.2.2.6 PCON REGISTER

The Power Control (PCON) register status contains 2 flag bits to allow differentiation between a Power-on Reset, an external MCLR reset, WDT reset, or low-voltage condition (Figure 4-8).

These bits are cleared on POR. The user must set these bits following POR. On a subsequent reset if POR is cleared, this is an indication that the reset was due to a power-on reset condition.

**Note:**  $\overline{\text{LVD}}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{\text{LVD}}$  is cleared, indicating a low voltage condition has occurred.

#### R/W R/W R/W U U U U U W: Writable Register: PCON POR LVD r Readable Address: 8Eh R: Unimplemented, bit7 bit0 POR value: U: read as '0' 0000\_000xb **LVD:** Low Voltage Detect Flag 1 = A low-voltage detect condition has not occurred. 0 = A low-voltage detect condition has occurred. Software must set this bit after a power-on-reset condition has occurred. **POR:** Power on Reset Flag 1 = A power on reset condition has not occurred. Reset must be due to some other source (WDT, MCLR). 0 = A power on reset condition has occurred. Software must set this bit after a power-on-reset condition has occurred. Unimplemented. Read as '0' Reserved. Bit 7 is reserved. This bit should be programmed as '0'.

# FIGURE 4-8: PCON REGISTER

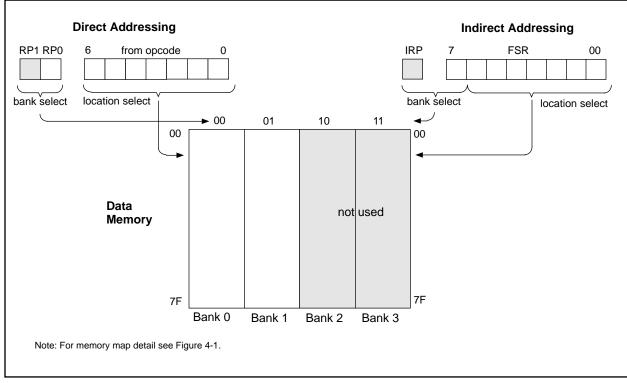

### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-10. However, IRP is not used in the PIC14000.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-2.

# EXAMPLE 4-2: INDIRECT ADDRESSING

|      | movlw | 0x20  | ;initialize pointer  |

|------|-------|-------|----------------------|

|      | movf  | FSR   | ;to RAM              |

| NEXT | clrf  | INDF  | ;clear INDF register |

|      | incf  | FSR   | ;inc pointer         |

|      | btfss | FSR,4 | ;all done?           |

|      | goto  | NEXT  | ;no clear next       |

|      |       |       | ;yes continue        |

CONTINUE:

# FIGURE 4-10: INDIRECT/INDIRECT ADDRESSING

# TABLE 5-1: PORT RC0 PIN CONFIGURATION SUMMARY

| RC0 Pin<br>Configuration     | TRISC<0> | RCPU<br>OPTION<7> | CMAOE<br>CMCON<1> | Comment                                                               |

|------------------------------|----------|-------------------|-------------------|-----------------------------------------------------------------------|

| Digital Input (weak pull-up) | 1        | 0                 | 0                 |                                                                       |

| Digital Input (no pull-up)   | 1        | 1                 | 0                 |                                                                       |

| Digital Output               | 0        | Х                 | 0                 |                                                                       |

| Analog Output                | 0        | Х                 | 1                 | Must clear TRISC<0> to disable pull-up when used as an analog output. |

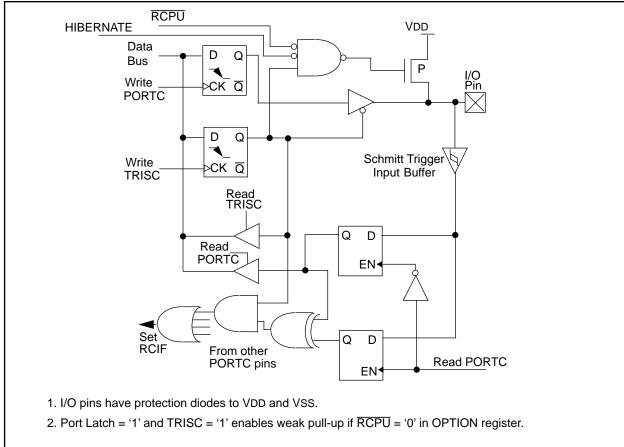

# FIGURE 5-4: BLOCK DIAGRAM OF PORTC<5:4> PINS

If the CMBOE bit (CMCON<5>) is set, the RD3/REFB pin becomes the programmable reference B output and pin RD2/CMPB becomes the comparator B output.

| Note: | Setting CMBOE changes the definition of |

|-------|-----------------------------------------|

|       | RD3/REFB and RD2/CMPB, bypassing        |

|       | the PORTD data and TRISD register set-  |

|       | tings.                                  |

PORTD<1:0> also serve multiple functions. These pins act as the  $I^2C$  data and clock lines when the  $I^2C$  module is enabled.

The TRISD register controls the direction of the Port D pins. A '1' in each location configures the corresponding port pin as an input. Upon reset, this register sets to FFh, meaning all PORTD pins are initially inputs. The data register should be initialized prior to configuring the port as outputs.

Unused inputs should not be left floating to avoid leakage currents. All pins have input protection diodes to VDD and VSS.

| EXAN  | IPLE 5-3:   | INITIALIZING PORTD         |  |  |  |

|-------|-------------|----------------------------|--|--|--|

| CLRF  | PORTD       | ; Initialize PORTD data    |  |  |  |

|       |             | ; latches before setting   |  |  |  |

|       |             | ; the data direction       |  |  |  |

|       |             | ; register                 |  |  |  |

| BSF   | STATUS, RPO | ;Select Bankl              |  |  |  |

| MOVLW | 0xFF        | ; Value used to initialize |  |  |  |

|       |             | ;data direction            |  |  |  |

| MOVWF | TRISD       | ;Set RD<7:0> as inputs     |  |  |  |

# 5.4 <u>I/O Programming Considerations</u>

# 5.4.1 BI-DIRECTIONAL I/O PORTS

Reading the port register reads the values of the port pins. Writing to the port register writes the value to the port latch. Some instructions operate internally as read-modify-write. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation, and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTC will cause all eight bits of PORTC to be read into the CPU. Then the BSF operation takes place on bit5 and PORTC is written to the output latches. If another bit of PORTC is used as a bi-directional I/O pin (say bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

A pin actively outputting a LOW or HIGH should not be driven from external devices at the same time in order to change the level on this pin ("wire-or", "wire-and"). The resulting high output currents may damage the chip.

Example 5-4 shows the effect of two sequential read modify write instructions (ex.  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O Port.

### EXAMPLE 5-4: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT

| ; Initial PORT settings:  | PORTC<7:4> Inputs     |

|---------------------------|-----------------------|

| ;<br>;                    | PORTC<3:0> Outputs    |

| ; PORTC<7:6> have externa | l pull-up and are not |

| ; connected to other circ | uitry                 |

| ;                         |                       |

| ;                         | PORT latch PORT pins  |

| ;                         |                       |

|                           |                       |

| BCF PORTC, 7              | ;01pp pppp 11pp pppp  |

| BCF PORTC, 6              | ;10pp pppp 11pp pppp  |

| BSF STATUS, RPO           | ;                     |

| BCF TRISC, 7              | ;10pp pppp 11pp pppp  |

| BCF TRISC, 6              | ;10pp pppp 10pp pppp  |

| ;                         |                       |

| ;Note that the user may   | have expected the pin |

| ; values to be 00pp pppp. | The 2nd BCF caused    |

| ;RC7 to be latched as th  | e pin value (High).   |

© 1996 Microchip Technology Inc.

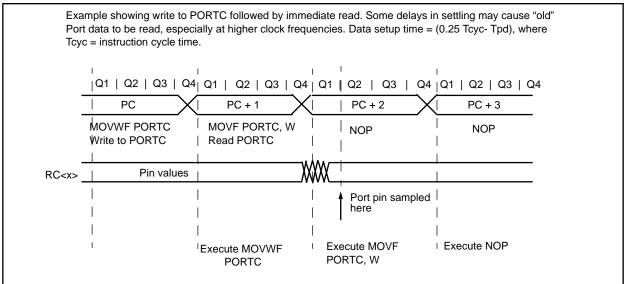

# 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle. Therefore, care must be exercised if a write operation is followed by a read operation on the same I/O port.

The sequence of instructions should be such to allow the pin voltage to stabilize before the next instruction which causes that port to be read into the CPU is executed. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

### FIGURE 5-13: SUCCESSIVE I/O OPERATION

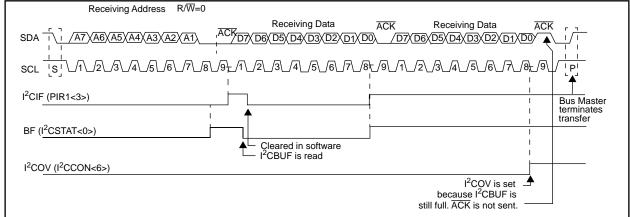

### 7.5.1.1 ADDRESSING

Once the I<sup>2</sup>C module has been enabled, the I<sup>2</sup>C waits for a START to occur. Following the START, the 8-bits are shifted into the I<sup>2</sup>CSR. All incoming bits are sampled with the rising edge of the clock (SCL) line. The I<sup>2</sup>CSR<7:1> is compared to the I<sup>2</sup>CADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and I<sup>2</sup>COV bits are clear, the following things happen:

- I<sup>2</sup>CSR loaded into I<sup>2</sup>CBUF

- Buffer Full (BF) bit is set

- ACK pulse is generated

- I<sup>2</sup>C Interrupt Flag (I<sup>2</sup>CIF) is set (interrupt is generated if enabled (I<sup>2</sup>CIE set) on falling edge of ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 7-5). The five most significant bits (MSbs) of the first address byte specify if this is a 10-bit address. The R/W bit (bit 0) must specify a write, so the slave device will received the second address byte. For a 10-bit address the first byte would equal '1 1 1 1 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address are as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (I<sup>2</sup>CIF, BF and UA are set).

- Update I<sup>2</sup>CADD with second (low) byte of address (clears UA and releases SCL line).

- 3. Read I<sup>2</sup>CBUF (clears BF) and clear I<sup>2</sup>CIF.

- 4. Receive second (low) byte of address (I<sup>2</sup>CIF, BF and UA are set).

- Update I<sup>2</sup>CADD with first (high) byte of address (clears UA, if match releases SCL line).

- 6. Read I<sup>2</sup>CBUF (clears BF) and clear I<sup>2</sup>CIF

- 7. Receive Repeated START.

- 8. Receive first (high) byte of address (I<sup>2</sup>CIF and BF are set).

- 9. Read I<sup>2</sup>CBUF (clears BF) and clear I<sup>2</sup>CIF.

### 7.5.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the I<sup>2</sup>CSTAT register is cleared. The received address is loaded into the I<sup>2</sup>CBUF.

When the address byte overflow condition exists then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either the BF bit (I<sup>2</sup>CSTAT<0>) is set or the I<sup>2</sup>COV bit (I<sup>2</sup>CCON<6>) is set (Figure 7-14).

An  $I^2CIF$  interrupt is generated for each data transfer byte. The  $I^2CIF$  bit must be cleared in software, and the  $I^2CSTAT$  register is used to determine the status of the byte. In master mode with slave enabled, three interrupt sources are possible. Reading BF, P and S will indicate the source of the interrupt.

**Caution:** BF is set after receipt of eight bits and automatically cleared after the I<sup>2</sup>CBUF is read. However, the flag is not actually cleared until receipt of the acknowledge pulse. Otherwise extra reads appear to be valid.

# FIGURE 7-14: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

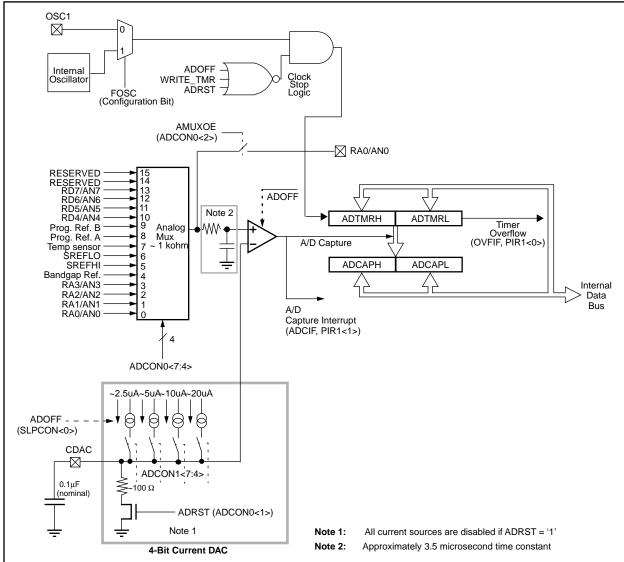

**Caution:** Reading or writing the ADTMR register during an A/D conversion cycle can produce unpredictable results and is not recommended.

| Note: | The correct sequence for writing the        |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | ADTMR register is HI byte followed by LO    |  |  |  |  |  |  |  |

|       | byte. Reversing this order will prevent the |  |  |  |  |  |  |  |

|       | A/D timer from running.                     |  |  |  |  |  |  |  |

During conversion one or both of the following events will occur:

- 1. capture event

- 2. timer overflow

In a capture event, the comparator trips when the slope voltage on the CDAC output exceeds the input voltage, causing the comparator output to transition from high to low. This causes a transfer of the current timer count to the capture register and sets the ADCIF flag (PIR1<1>).

A CPU interrupt will be generated if bit ADCIE (PIE1<1>) is set to '1' (interrupt enabled). In addition, the Global Interrupt Enable and Peripheral Interrupt Enables (INTCON<7,6>) must also be set. Software is responsible for clearing the ADCIF flag prior to the next conversion cycle. Note that this interrupt can only occur once per conversion cycle.

In a timer overflow condition, the timer rolls over from FFFFh to 0000h, and a capture overflow flag (OVFIF) is asserted (PIR1<0>). The timer continues to increment following a timer overflow. A CPU interrupt can be generated if bit OVFIE (PIE1<0>) is set (interrupt enabled). In addition, the Global Interrupt Enable and Peripheral Interrupt Enables (INTCON<7,6>) must also be set. Software is responsible for clearing the OVFIF flag prior to the next conversion cycle.

### FIGURE 8-1: A/D BLOCK DIAGRAM

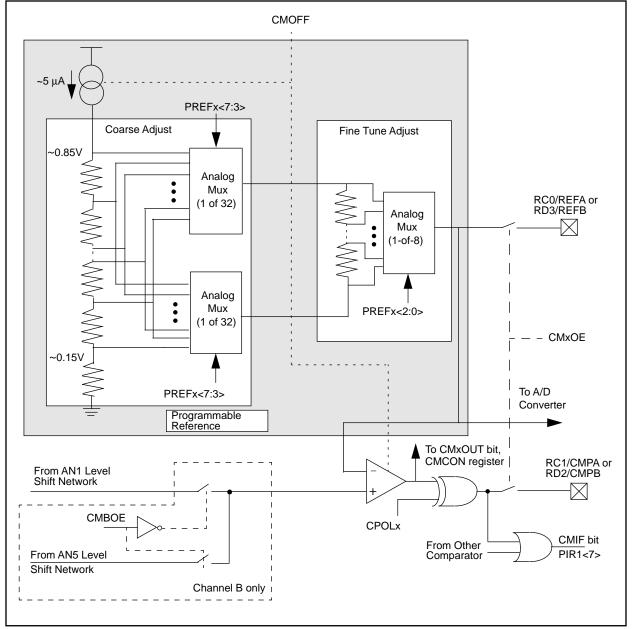

Two registers PREFA (9Bh) and PREFB (9Ch) are used to select the reference output voltages. The PREFx<7:3> bits select the output from the coarse ladder, while PREFx<2:0> bits are for the fine-tune adjustment. Table 9-1 and Table 9-2 show the reference decoding.

These voltages are visible at either RC0/REFA or RD3/REFB pins by setting the CMAOE (CMCON<1>) or CMBOE (CMCON<5>) bits. Setting CMxOE does not affect the reference voltages. It only enables the pin function regardless of the port TRIS register setting. These outputs are not buffered, so they cannot directly drive any DC loads.

The reference outputs are also connected to two independent comparators, COMPA and COMPB. Thus, the references can be used to set the comparator trippoints. The A/D converter can also monitor the reference outputs via A/D channels 8 and 9. Refer to Section 8 for the description of the A/D operation.

The programmable reference output is designed to track the output from the level shift network. However, there will always be some mismatch due to component drift. For best accuracy, the A/D should be used to periodically calibrate the references to the desired set-point.

## FIGURE 9-3: COMPARATOR AND PROGRAMMABLE REFERENCE BLOCK DIAGRAM (ONE OF TWO SHOWN)

| TABLE 10-3. STATUS BITS AND THEIR SIGNIFICANCE | TABLE 10-3: | STATUS BITS AND THEIR SIGNIFICANCE |

|------------------------------------------------|-------------|------------------------------------|

|------------------------------------------------|-------------|------------------------------------|

| POR | TO | PD | Meaning                                                                             |  |  |  |

|-----|----|----|-------------------------------------------------------------------------------------|--|--|--|

| 0   | 1  | 1  | Power-On Reset                                                                      |  |  |  |

| 0   | 0  | Х  | Illegal, TO is set on POR                                                           |  |  |  |

| 0   | Х  | 0  | Illegal, PD is set on POR                                                           |  |  |  |

| 1   | 0  | 1  | WDT reset during normal operation                                                   |  |  |  |

| 1   | 0  | 0  | WDT time-out wakeup from sleep                                                      |  |  |  |

| 1   | 1  | 1  | MCLR reset during normal operation                                                  |  |  |  |

| 1   | 1  | 0  | MCLR reset during SLEEP or HIBERNATE, or interrupt wake-up from SLEEP or HIBERNATE. |  |  |  |

### 10.4 Low-Voltage Detector

The PIC14000 contains an integrated low-voltage detector. The supply voltage is divided and compared to the bandgap reference output. If the supply voltage (VDD) falls below VTRIP-, then the low-voltage detector will cause  $\overline{LVD}$  (PCON<0>) to be reset. This bit can be read by software to determine if a low voltage condition occurred. This bit must be set by software.

The nominal values of the low-voltage detector trip points are as follows:

- VTRIP- = 2.55V

- VTRIP+ = 2.60V

- Hysteresis (VTRIP+ VTRIP-) = 55 mV

# 10.5 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT) and Oscillator Start-up</u> <u>Timer (OST)</u>

#### 10.5.1 POWER-ON RESET (POR)

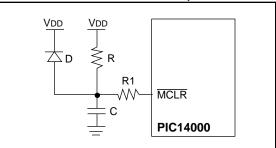

A Power-on Reset pulse is generated on-chip when VDD rise is detected (in the range of 1.5V - 2.1V). To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create a Power-on Reset. A maximum rise time for VDD is specified. See Electrical Specifications for details.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, ...) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*."

#### 10.5.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from  $\overrightarrow{POR}$ . The power-up timer operates from a local internal oscillator. The chip is kept in reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit,  $\overrightarrow{PWRTE}$ , can disable (if set, or unprogrammed) or enable (if cleared, or programmed) the power-up timer.

The power-up timer delay will vary from chip to chip and due to VDD and temperature.

10.5.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides 1024 oscillator cycles (from OSC1 input) delay after the PWRT delay is over. This guarantees that the crystal oscillator or resonator has started and stabilized.

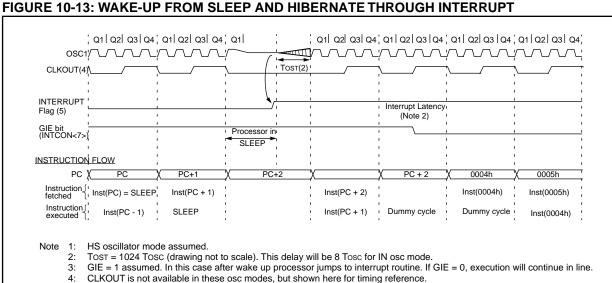

10.5.4 IN OSCILLATOR START-UP

There is an 8-cycle delay in IN mode to ensure stability only after a Power-on Reset (POR) or wake-up from SLEEP.

#### 10.5.5 TIMEOUT SEQUENCE

On power-up the time-out sequence is as follows: First the PWRT time-out is invoked after POR has expired. The OST is activated only in HS (crystal oscillator) mode. The total time-out will vary based on the oscillator configuration and PWRTE status. For example, in IN mode, with PWRTE unprogrammed (PWRT disabled), there will be no time-out delay at all. Figure 13-4 depicts the power-on reset time-out sequences.

Table 10-4 shows the reset conditions for some special registers, while Table 10-5 shows the reset conditions for all registers.

#### FIGURE 10-8: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- External power-on reset circuit is required only if VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2. R < 40 K $\Omega$  is recommended to make sure that voltage drop across R does not exceed 0.2V (max leakage current spec on MCLR pin is 5  $\mu$ A). A larger voltage drop will degrade VIH level on MCLR pin.

- 3. R1 = 100  $\Omega$  to 1 K $\Omega$  will limit any current flowing into  $\overline{\text{MCLR}}$  from external capacitor C in the event of  $\overline{\text{MCLR}}$  pin breakdown due to ESD or EOS.

# TABLE 10-4: RESET CONDITION FOR SPECIAL REGISTERS

| Condition                          | PCL<br>Addr: 02h      | STATUS<br>Addr: 03h | PCON<br>Addr: 8Eh |  |

|------------------------------------|-----------------------|---------------------|-------------------|--|

| Power-on Reset                     | 000h                  | 0001 1xxx           | 00x               |  |

| MCLR reset during normal operation | 000h                  | 0001 luuu           | uux               |  |

| MCLR reset during SLEEP            | 000h                  | 0001 Ouuu           | uux               |  |

| WDT reset during normal operation  | 000h                  | 0000 luuu           | uux               |  |

| WDT during SLEEP                   | PC + 1                | นนน0 0นนน           | uux               |  |

| Interrupt wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuul Ouuu           | uux               |  |

Legend: u = unchanged

x = unknown

- = unimplemented, read as '0'

Note 1: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

CLKOUT is not available in these osc modes

Refer to Section 10.8 for sources.

### 10.9 Code Protection

The code in the program memory can be protected by programming the code protect bits. When code protected, the contents of the program memory cannot be read out. In code-protected mode, the configuration word (2007h) will not be scrambled, allowing reading of all configuration bits.

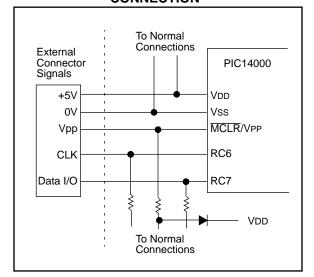

#### 10.10 In-Circuit Serial Programming

PIC14000 can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RC6/SCL and RC7/SDA pins low while raising the  $\overline{\text{MCLR}}$  (VPP) pin from VIL to VIH. RC6 then becomes the programming clock and RC7 becomes the programmed data. Both RC6 and RC7 are Schmitt trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device. For complete details about serial programming, please refer to the *PIC16C6X/7X Programming Specifications* (Literature #DS30228).

A typical in-system serial programming connection is shown in Figure 10-14.

#### FIGURE 10-14: TYPICAL IN-SYSTEM SERIAL PROGRAMMING CONNECTION

# 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                 |      |      |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|------|------|------|--|--|--|

| Syntax:          | [label] ADDLW k                                                                                                   |      |      |      |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                 |      |      |      |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                 |      |      |      |  |  |  |

| Status Affected: | C, DC, Z                                                                                                          |      |      |      |  |  |  |

| Encoding:        | 11                                                                                                                | 111x | kkkk | kkkk |  |  |  |

| Description:     | The contents of the W register are added to the eight bit literal 'k' and the result is placed in the W register. |      |      |      |  |  |  |

| Words:           | 1                                                                                                                 |      |      |      |  |  |  |

| Cycles:          | 1                                                                                                                 |      |      |      |  |  |  |

| Example          | ADDLW                                                                                                             | 0x15 |      |      |  |  |  |

|                  | Before Instruction<br>W = 0x10<br>After Instruction<br>W = 0x25                                                   |      |      |      |  |  |  |

| ANDLW            | And Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                   |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                   |

| Cycles:          | 1                                                                                                                   |

| Example          | ANDLW 0x5F                                                                                                          |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction                                                                 |

W = 0x03

| ADDWF            | Add W and f                                                                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[ 0,1 \right] \end{array}$                                                                                              |

| Operation:       | (W) + (f) $\rightarrow$ (dest)                                                                                                                                            |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                         |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0 the result is<br>stored in the W register. If 'd' is 1 the<br>result is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                                         |

| Cycles:          | 1                                                                                                                                                                         |

| Example          | ADDWF FSR, 0                                                                                                                                                              |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                               |

| ANDWF            | AND W with f                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                         |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                        |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                        |

| Status Affected: | Z                                                                                                                                                         |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                         |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0 the result is stored in the W<br>register. If 'd' is 1 the result is stored<br>back in register 'f'. |

| Words:           | 1                                                                                                                                                         |

| Cycles:          | 1                                                                                                                                                         |

| Example          | ANDWF FSR, 1                                                                                                                                              |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                               |

MPASM allows full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

# 12.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 12.12 <u>C Compiler (MPLAB-C)</u>

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of microcontrollers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

# 12.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

# 12.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

# 12.15 <u>SEEVAL<sup>®</sup> Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 12.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

# 12.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

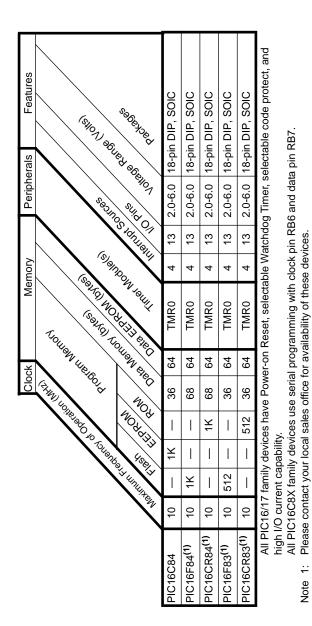

# A.6 PIC16C8X Family of Devices

DS40122B-page 138

|                                                                                                                                                                                                                                                                |                            |                             |                                                                                   | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             | Memory                               |                             |                                 | Peripherals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | erals                       |                 |               |                                    |                        |             | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Γ |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|-----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|---------------|------------------------------------|------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                                                                                                                                |                            |                             |                                                                                   | FOOTBAN CONST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TIOLUS                      | $\mathbb{N}$                         |                             | all de la                       | (Hans)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                             | Sloute          |               | $\mathbb{N}$                       | $\left  \right\rangle$ | $\setminus$ | GUILLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |

|                                                                                                                                                                                                                                                                |                            |                             | TO TOUS                                                                           | 50101<br>50100<br>10<br>10<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ڔ                           | (s)                                  | ALL DE                      |                                 | 100 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |                 | 583)<br>11    |                                    |                        | SHON        | 1950 - 1010<br>1950 - 1010<br>1911                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                                                                                                                                                                                                                                                |                            | THE MELT                    |                                                                                   | THE STATES OF A ST | IDOW J                      | 1001 COI PONE SAN PONE               | E LOC                       |                                 | Sile of the Star of the Source |                             |                 |               | $\langle \dot{\mathbf{v}} \rangle$ | Ins Reality Services   | S III I     | Solution out the second |   |