Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

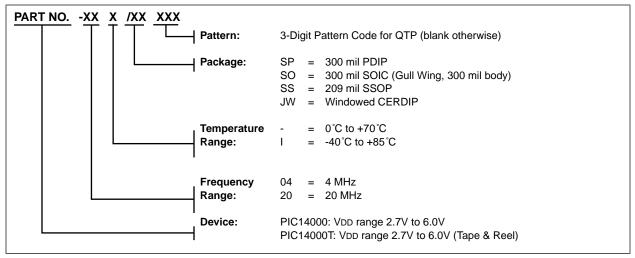

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | I <sup>2</sup> C                                                          |

| Peripherals                | POR, Temp Sensor, WDT                                                     |

| Number of I/O              | 20                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                 |

| Data Converters            | Slope A/D                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic14000-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC14000 features include medium to high resolution A/D conversion (10 to 16 bits), temperature sensing, closed loop charge control, serial communication, and low power operation.

The PIC14000 uses a RISC Harvard architecture CPU with separate 14-bit instruction and 8-bit data buses. A two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches, which require two cycles. A total of 35 instructions are available. Additionally, a large register set is included.

PIC16/17 microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers.

### Features:

The PIC14000 is a 28-pin device with these features:

- 4K of EPROM

- 192 bytes of RAM

- 22 I/O pins

#### The analog peripherals include:

- 8 external analog input channels, two with level shift inputs

- 6 internal analog input channels

- 2 comparators with programmable references

- A bandgap reference

- An internal temperature sensor

- A programmable current source

In addition, the  $I^2C$  serial port through a multiplexer supports two separate  $I^2C$  channels.

A special oscillator option allows either an internal 4 MHz oscillator or an external crystal oscillator. Using the internal 4 MHz oscillator requires no external components.

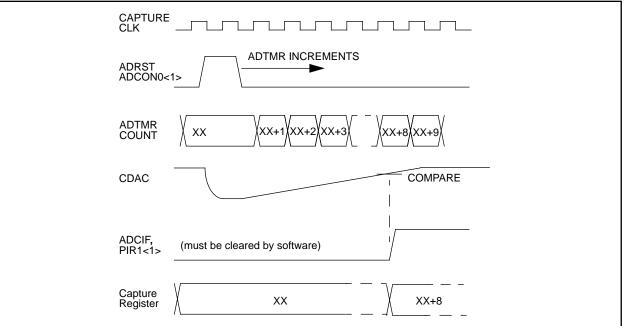

The PIC14000 contains three timers, the Watchdog Timer (WDT), Timer0 (TMR0), and A/D Timer (ADTMR). The Watchdog Timer includes its own on-chip RC oscillator providing protection against software lock-up. TMR0 is a general purpose 8-bit timer/counter with an 8-bit prescaler. It may be clocked externally using the RC3/T0CKI pin. The ADTMR is intended for use with the slope A/D converter, but can also be used as a general purpose timer. It has an associated capture register which can be used to measure the time between events.

An internal low-voltage detect circuit allows for tracking of voltage levels. Upon detecting the low voltage condition, the PIC14000 can be instructed to save its operating state then enter an idle state. The internal band-gap reference is used for calibrating the measurements of the analog peripherals. The calibration factors are stored in EPROM and can be used to achieve high measurement accuracy.

Power savings modes are available for portable applications. The SLEEP and HIBERNATE modes offer different levels of power savings. The PIC14000 can wake up from these modes through interrupts or reset.

A UV erasable CERDIP packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC14000 fits perfectly in applications for battery charging, capacity monitoring, and data logging. The EPROM technology makes customization of application programs (battery characteristics, feature sets, etc.) extremely fast and convenient. The small footprint packages make this microcontroller based mixed signal device perfect for all applications with space limitations. Low-cost, low-power, high performance, ease of use and I/O flexibility make the PIC14000 very versatile in other applications such as temperature monitors/controllers.

## 1.1 Family and Upward Compatibility

Code written for PIC16C6X/7X can be easily ported to the PIC14000 (see Appendix A).

## 1.2 Development Support

The PIC14000 is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler and fuzzy logic support tools are also available.

#### 4.2.2.2 OPTION REGISTER

The OPTION register (Address 81h) is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, TMR0, and the weak pull-ups on PORTC<5:0>. Bit 6 is reserved.

## FIGURE 4-4: OPTION REGISTER

| R/W<br>RCPU | 1 | R/W<br>r | R/W | R/W<br>TOSE | R/W<br>PSA | PS2 | R/W<br>PS1 | R/W<br>PS0<br>bit0                                                       | Regi:<br>Addr<br>POR                                                                                     |                                                                                        | OPTION<br>81h<br>FFh                                                        |                                                                              |                                                  |

|-------------|---|----------|-----|-------------|------------|-----|------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|

|             |   |          |     |             |            |     |            | PS2:PS0                                                                  | PRES<br>PS2                                                                                              | CALER<br><b>PS1</b>                                                                    | VALUE                                                                       | TMR0 RATE                                                                    | WDT RATE                                         |

|             |   |          |     |             |            |     |            |                                                                          | 0                                                                                                        | 0                                                                                      | 0                                                                           | 1:2                                                                          | 1:1                                              |

|             |   |          |     |             |            |     |            |                                                                          | 0                                                                                                        | 0                                                                                      | 1                                                                           | 1:4                                                                          | 1:2                                              |

|             |   |          |     |             |            |     |            |                                                                          | 0                                                                                                        | 1                                                                                      | 0                                                                           | 1:8                                                                          | 1:4                                              |

|             |   |          |     |             |            |     |            |                                                                          | 0                                                                                                        | 1                                                                                      | 1                                                                           | 1 : 16                                                                       | 1:8                                              |

|             |   |          |     |             |            |     |            |                                                                          | 1                                                                                                        | 0                                                                                      | 0                                                                           | 1:32                                                                         | 1 : 16                                           |

|             |   |          |     |             |            |     |            |                                                                          | 1                                                                                                        | 0                                                                                      | 1                                                                           | 1:64                                                                         | 1 : 32                                           |

|             |   |          |     |             |            |     |            |                                                                          | 1                                                                                                        | 1                                                                                      | 0                                                                           | 1:128                                                                        | 1 : 64                                           |

|             |   |          |     |             |            |     |            | PSA: Preso                                                               | 1                                                                                                        | 1                                                                                      | 1                                                                           | 1 : 256                                                                      | 1 : 128                                          |

|             |   |          |     |             |            |     |            | 0 = Increme<br>TOCS: TMR<br>1 = Transitio<br>0 = Internal<br>Reserved. 1 | er assigr<br>0 source<br>ent on hig<br>ent on lov<br>0 clock so<br>on on RC<br>instruction<br>This bit s | hed to T<br>e edge<br>gh-to-low<br>w-to-hig<br>source<br>3/T0Ck<br>on cycle<br>hould b | MR0<br>w transition<br>h transition<br>(I pin<br>e clock (CLk<br>e programn | on RC3/T0CKI<br>on RC3/T0CKI<br>(OUT)<br>ned as a '1'. Use<br>mended since t | pin<br>e of this bit as                          |

|             |   |          |     |             |            |     |            | RCPU: POI<br>1 = PORTC                                                   | patibility<br>RTC pull<br>; pull-up:                                                                     | with fut<br>-up ena<br>s are dis                                                       | ture product<br>ble<br>sabled over                                          | ts.<br>riding any port la                                                    | atch value (RC<5:0> only)<br>ch values (RC<5:0>) |

Note: To achieve a 1:1 prescaler assignment, assign the prescaler to the WDT (PSA=1)

# PIC14000

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bits for the Peripheral interrupts including A/D capture event,  $I^2C$  serial port, PORTC change and A/D capture timer overflow, and external push button.

# FIGURE 4-6: PIE1 REGISTER

#### R/W R R R/W R/W R/W R/W R/W Register: PIE1 W: Writable CMIE PBIE I<sup>2</sup>CIE RCIE ADCIE OVFIE Address: 8Ch R: Readable 00h bit0 POR value: U: Unimplemented, bit7 read as '0' OVFIE: A/D Counter Overflow Interrupt Enable 1 = Enables A/D counter overflow interrupt 0 = Disables A/D counter overflow interrupt ADCIE: A/D Capture Interrupt Enable 1 = A/D capture interrupt is enabled 0 = A/D capture interrupt is disabled PORTC Interrupt on change Enable RCIE: 1 = Enables RCIF interrupt on pins, RC<7:4> 0 = Disables RCIF interrupt I<sup>2</sup>CIE: I<sup>2</sup>C Port Interrupt Enable 1 = Enables I<sup>2</sup>CIF interrupt 0 = Disables I<sup>2</sup>CIF interrupt PBIE: External Pushbutton Interrupt Enable 1 = Enable PBTN (pushbutton) interrupt on OSC1/PBTN. (Note this interrupt not available in HS mode). 0 = Disable PBTN interrupt on OSC1/PBTN Unimplemented. Read as '0' Unimplemented. Read as '0' CMIE: Programmable Reference Comparator Interrupt Enable 1 = Enable programmable reference comparator trip 0 = Disable programmable reference comparator trip

**Note:** INTCON<6> must be enabled to enable any interrupt in PIE1.

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bits for the Peripheral interrupts (Figure 4-7).

Note: These bits will be set by the specified condition, even if the corresponding Interrupt Enable bit is cleared (interrupt disabled) or the GIE bit is cleared (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the corresponding interrupt flag, to ensure that the program does not immediately branch to the Peripheral Interrupt service routine.

## FIGURE 4-7: PIR1 REGISTER

| R/W  |   | R | R | R/W  | R/W                | R/W  | R/W   | R/W   |                                                                                                                                                                                                                                                                                                                                |

|------|---|---|---|------|--------------------|------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMIF | - | - |   | PBIF | I <sup>2</sup> CIF | RCIF | ADCIF | OVFIF | Register:PIR1W:WritableAddress:0ChR:Readable                                                                                                                                                                                                                                                                                   |

| bit7 |   |   |   |      |                    |      |       | bitO  | POR value: 00h U: Unimplemented,<br>read as '0'                                                                                                                                                                                                                                                                                |

|      |   |   |   |      |                    |      |       |       | <ul> <li>OVFIF: A/D counter Overflow Interrupt Flag</li> <li>1 = An A/D counter overflow has occurred.<br/>Must be cleared in software.</li> <li>0 = An A/D counter overflow has not occurred</li> <li>ADCIF: A/D Capture Interrupt Flag</li> <li>1 = An A/D capture has occurred.<br/>Must be cleared in software.</li> </ul> |

|      |   |   |   |      |                    |      |       |       | <ul> <li>0 = An A/D capture has not occurred</li> <li>RCIF: PORTC Interrupt on Change Flag</li> <li>1 = At least one RC&lt;7:4&gt; input changed.<br/>Must be cleared in software.</li> <li>0 =None of the RC&lt;7:4&gt; inputs have changed</li> </ul>                                                                        |

|      |   |   |   |      |                    |      |       |       | <ul> <li>I<sup>2</sup>CIF: I<sup>2</sup>C Port Interrupt Flag</li> <li>1 = A transmission/reception is completed.<br/>Must be cleared in software.</li> <li>0 = Waiting to transmit/receive</li> </ul>                                                                                                                         |

|      |   |   |   |      |                    |      |       |       | <ul> <li>PBIF: External Pushbutton Interrupt Flag</li> <li>1 = The external pushbutton interrupt has occurred<br/>on OSC1/PBTN. Note: This interrupt is not available<br/>in HS mode.</li> <li>0 =The external pushbutton interrupt did not occur</li> </ul>                                                                   |

|      |   |   |   |      |                    |      |       |       | Unimplemented. Read as '0'                                                                                                                                                                                                                                                                                                     |

|      |   |   |   |      |                    |      |       |       | Unimplemented. Read as '0'                                                                                                                                                                                                                                                                                                     |

|      |   |   |   |      |                    |      |       |       | <ul> <li>CMIF: Programmable Reference Comparator Interrupt Flag</li> <li>1 = The comparator output has tripped. This is a level-sensitive interrupt.</li> <li>0 = The interrupt did not occur</li> </ul>                                                                                                                       |

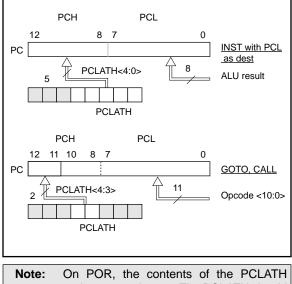

## 4.3 PCL and PCLATH

The program counter (PC) is 13-bits wide. The low byte, PCL, is a readable and writable register. The high byte of the PC (PCH) is not directly readable or writable. PCLATH is a holding register for PC<12:8> where contents are transferred to the upper byte of the program counter. When PC is loaded with a new value during a CALL, GOTO or a write to PCL, the high bits of PC are loaded from PCLATH as shown in Figure 4-9.

## FIGURE 4-9: LOADING OF PC IN DIFFERENT SITUATIONS

Note: On POR, the contents of the PCLATH register are unknown. The PCLATH should be initialized before a CALL, GOTO, or any instruction that modifies the PCL register is executed.

### 4.3.1 COMPUTED GOTO

When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note "Table Read Using the PIC16CXX" (AN556).

### 4.3.2 STACK

The PIC14000 has an 8 deep x 13-bit wide hardware stack (Figure 4-1). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed in the stack when a CALL instruction is executed or an interrupt is acknowledged. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a "PUSH" or a "POP" operation.

The stack operates as a circular buffer. This means that after the stack has been "PUSHed" eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instruction mnemonics called PUSH nor POP. These are actions that occur from the execution of the CALL, RETURN, RETLW, or RETFIE instructions, or the vectoring to an interrupt address

## 4.3.3 PROGRAM MEMORY PAGING

The PIC14000 has 4K of program memory, but the CALL and GOTO instructions only have a 11-bit address range. This 11-bit address range allows a branch within a 2K program memory page size. To allow CALL and GOTO instructions to address the entire 4K program memory address range, there must be another bit to specify the program memory page. This paging bit comes from the PCLATH<3> bit (Figure 4-9). When doing a CALL or GOTO instruction, the user must ensure that this page bit (PCLATH<3>) is programmed to the desired program memory page. If a CALL instruction (or interrupt) is executed, the entire 13-bit PC is pushed onto the stack. Therefore, manipulation of the PCLATH<3> is not required for the return instructions (which pops the PC from the stack).

Note: The PIC14000 ignores the PCLATH<4> bit, which is used for program memory pages 2 and 3 (1000h-1FFFh). The use of PCLATH<4> as a general purpose read/write bit is not recommended since this may affect upward compatibility with future products.

Example 4-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that the PCLATH is saved and restored by the interrupt service routine (if interrupts are used).

#### EXAMPLE 4-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

| ORG 0X5 | 00      |   |   |                           |

|---------|---------|---|---|---------------------------|

| BSF     | PCLATH, | 3 | ; | Select page 1 (800h-FFFh) |

| CALL    | SUB1_P1 |   | ; | Call subroutine in        |

|         | :       |   | ; | page 1 (800h-FFFh)        |

|         | :       |   |   |                           |

|         | :       |   |   |                           |

| ORG 0X9 | 00      |   |   |                           |

| SUB1 P1 | :       |   | ; | called subroutine         |

|         | :       |   | ; | page 1 (800h-FFFh)        |

|         | :       |   |   |                           |

| RETURN  |         |   | ; | return to page 0          |

|         |         |   | ; | (000h-7FFh)               |

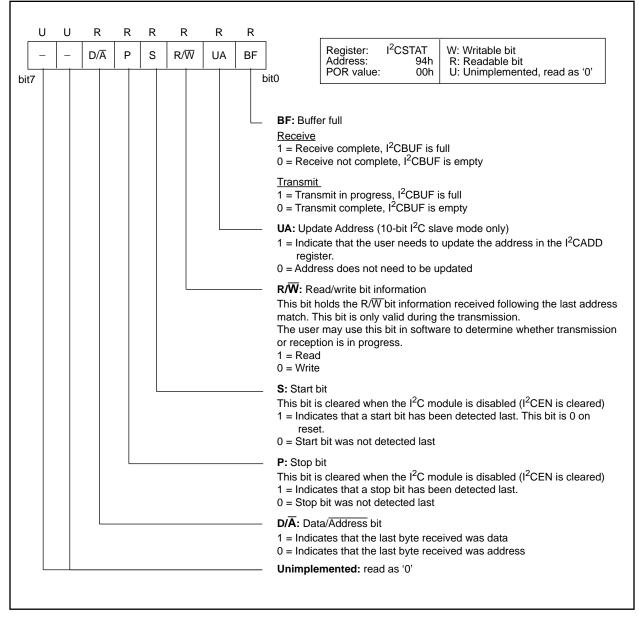

## FIGURE 7-2: I<sup>2</sup>CSTAT: I<sup>2</sup>C PORT STATUS REGISTER

# PIC14000

# FIGURE 7-3: I<sup>2</sup>CCON: I<sup>2</sup>C PORT CONTROL REGISTER

| R/   | W R/ | N R/                | WR/ | W R/W                 | R/W                | R/W                | R/W                |                                                       |                                                                                                                                                                                                                                                                        |                                                                                                                                                   |                                                                                                                                                    |

|------|------|---------------------|-----|-----------------------|--------------------|--------------------|--------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| WC   |      | DV I <sup>2</sup> C |     | KP I <sup>2</sup> CM3 | I <sup>2</sup> CM2 | I <sup>2</sup> CM1 | I <sup>2</sup> CM0 |                                                       | Register:<br>Address:<br>POR value:                                                                                                                                                                                                                                    | l <sup>2</sup> CCON<br>14h<br>00h                                                                                                                 | W: Writable bit<br>R: Readable bit<br>U: Unimplemented, read as '0'                                                                                |

| bit7 |      |                     |     |                       |                    |                    | b                  | 0110<br>0111<br>1011<br>1110<br>1111<br>Any<br>are il | <3:0>: I <sup>2</sup> C mo<br>= I <sup>2</sup> C slave I<br>= I <sup>2</sup> C slave<br>= I <sup>2</sup> C firmwa<br>= I <sup>2</sup> C slave<br>enabled<br>= I <sup>2</sup> C slave<br>enabled<br>other combin<br>llegal and sho<br>: Clock polarity<br>release contr | ode select<br>mode, 7-bit ac<br>mode, 10-bit a<br>rre controlled<br>mode, 7-bit a<br>mode, 10-bit a<br>ations of I <sup>2</sup> CI<br>uld NEVER b | ddress<br>address<br>master mode (slave idle)<br>ddress with start and stop bit interrupts<br>address with start and stop bit interrupts<br>M<3:0> |

|      |      |                     |     |                       |                    |                    |                    | 0 =<br><b>I<sup>2</sup>CEN</b><br>1 = E<br>pro-<br>or | ort pins. Wher<br>r output.                                                                                                                                                                                                                                            | o ensure data<br>rial port and c<br>n enabled, the                                                                                                |                                                                                                                                                    |

|      |      |                     |     |                       |                    |                    |                    | 1 = A<br>b<br>  <sup>2</sup>                          | <b>/:</b> Receive ove<br>byte is receive<br>yte. I <sup>2</sup> COV is<br>COV must be<br>lo overflow                                                                                                                                                                   | ved while the la don't care ir                                                                                                                    | I <sup>2</sup> CBUF is still holding the previous<br>n transmit mode.<br>oftware.                                                                  |

|      |      |                     |     |                       |                    |                    |                    | 1 = t<br>c<br>N                                       | L: Write collisi<br>he I <sup>2</sup> CBUF re-<br>bus word.<br>Aust be cleare<br>No collision                                                                                                                                                                          | gister is writte                                                                                                                                  | n while it is still transmitting the previ-                                                                                                        |

## 7.5.1.3 TRANSMISSION

When the  $R/\overline{W}$  bit of the address byte is set and an address match occurs, the  $R/\overline{W}$  bit of the  $I^2CSTAT$  register is set. The received address is loaded into the  $I^2CBUF$  The  $\overline{ACK}$  pulse will be sent on the ninth bit, and the SCL pin is held low. The transmit data must be loaded into the  $I^2CBUF$  register, which also loads the  $I^2CSR$  register. Then the SCL pin should be enabled by setting the CKP bit ( $I^2CCON<4>$ ). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 7-15).

A l<sup>2</sup>CIF interrupt is generated for each data transfer byte. The l<sup>2</sup>CIF bit must be cleared in software, and the l<sup>2</sup>CSTAT register is used to determine the status of the byte. The l<sup>2</sup>CIF bit is set on the falling edge of the ninth clock pulse.

As a slave-transmitter, the  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line was high (not  $\overline{ACK}$ ), then the data transfer is complete. The slave then monitors for another occurrence of the START bit. If the SDA line was low ( $\overline{ACK}$ ), the transmit data must be loaded into the I<sup>2</sup>CBUF register, which also loads the I<sup>2</sup>CSR register. Then the SCL pin should be enabled by setting the CKP bit (I<sup>2</sup>CCON<4>).

### FIGURE 7-15: I<sup>2</sup>C WAVEFORMS FOR TRANSMISSION (7-BIT ADDRESS)

## FIGURE 8-3: A/D CAPTURE TIMER (LOW BYTE)

| 0Eh           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| ADTMRL        | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

| Read/Write    | R/W   |

| POR value 00h | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### FIGURE 8-4: A/D CAPTURE TIMER (HIGH BYTE)

| 0Fh           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| ADTMRH        | b15   | b14   | b13   | b12   | b11   | b10   | b9    | b8    |

| Read/Write    | R/W   |

| POR value 00h | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

## FIGURE 8-5: A/D CAPTURE REGISTER (LOW BYTE)

| 15h           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCAPL        | b7    | b6    | b5    | b4    | b3    | b2    | b1    | b0    |

| Read/Write    | R/W   |

| POR value 00h | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

## FIGURE 8-6: A/D CAPTURE REGISTER (HIGH BYTE)

| 16h           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| ADCAPH        | b15   | b14   | b13   | b12   | b11   | b10   | b9    | b8    |

| Read/Write    | R/W   |

| POR value 00h | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Legend: U= unimplemented, X = unknown.

## 8.4 <u>A/D Comparator</u>

The PIC14000 includes a high gain comparator for A/D conversions. The positive input terminal of the A/D comparator is connected to the output of an analog mux through an RC low-pass filter. The nominal time-constant for the RC filter is  $3.5 \ \mu$ s. The negative input terminal is connected to the external 0.1  $\mu$ F (nominal) ramp capacitor.

|   | ADCO | N0(7:4) |   | A/D Channel                     |

|---|------|---------|---|---------------------------------|

| 0 | 0    | 0       | 0 | RA0/AN0 pin                     |

| 0 | 0    | 0       | 1 | RA1/AN1 pin                     |

| 0 | 0    | 1       | 0 | RA2/AN2 pin                     |

| 0 | 0    | 1       | 1 | RA3/AN3 pin                     |

| 0 | 1    | 0       | 0 | Bandgap reference voltage       |

| 0 | 1    | 0       | 1 | Slope reference SREFHI          |

| 0 | 1    | 1       | 0 | Slope reference SREFLO          |

| 0 | 1    | 1       | 1 | Internal temperature sensor     |

| 1 | 0    | 0       | 0 | Programmable reference A output |

| 1 | 0    | 0       | 1 | Programmable reference B output |

| 1 | 0    | 1       | 0 | RD4/AN4 pin                     |

| 1 | 0    | 1       | 1 | RD5/AN5 pin                     |

| 1 | 1    | 0       | 0 | RD6/AN6 pin                     |

| 1 | 1    | 0       | 1 | RD7/AN7 pin                     |

| 1 | 1    | 1       | 0 | Reserved                        |

| 1 | 1    | 1       | 1 | Reserved                        |

## TABLE 8-1: A/D CHANNEL ASSIGNMENT

## 8.5 <u>Analog Mux</u>

A total of 16 channels are internally multiplexed to the single A/D comparator positive input. Four configuration bits (ADCON0<7:4>) select the channel to be converted. Refer to Table 8-1 for channel assignments.

## TABLE 8-4: A/D CONTROL AND STATUS REGISTER 1

| 9Fh           | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|--------|--------|--------|--------|-------|-------|-------|-------|

| ADCON1        | ADDAC3 | ADDAC2 | ADDAC1 | ADDAC0 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R/W   | R/W   | R/W   | R/W   |

| POR value 00h | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     |

| Bit   | Name                                 | Function                                        |

|-------|--------------------------------------|-------------------------------------------------|

| B7-B4 | ADDAC3<br>ADDAC2<br>ADDAC1<br>ADDAC0 | A/D Current Source Selects. Refer to Table 8-2. |

| B3-B2 | PCFG3<br>PCFG2                       | PORTD Configuration Selects<br>(See Table 8-5)  |

| B1-B0 | PCFG1<br>PCFG0                       | PORTA Configuration Selects<br>(See Table 8-5)  |

## TABLE 8-5:PORTA AND PORTD CONFIGURATION

| ADCON1<1:0> | RA0/AN0 | RA1/AN1 | RA2/AN2 | RA3/AN3 |

|-------------|---------|---------|---------|---------|

| ADCON1<3:2> | RD4/AN4 | RD5/AN5 | RD6/AN6 | RD7/AN7 |

| 0 0         | A       | A       | A       | A       |

| 0 1         | A       | A       | A       | D       |

| 10          | A       | A       | D       | D       |

| 11          | D       | D       | D       | D       |

Legend: A = Analog input, D = Digital I/O

# FIGURE 9-6: PREFA REGISTER

| 9Bh           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PREFA         | PRA7  | PRA6  | PRA5  | PRA4  | PRA3  | PRA2  | PRA1  | PRA0  |

| Read/Write    | R/W   |

| POR value 00h | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Bit   | Name                                                         | Function                                                                                   |

|-------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| B7-B0 | PRA7<br>PRA6<br>PRA5<br>PRA4<br>PRA3<br>PRA2<br>PRA1<br>PRA0 | Programmable Reference A Voltage Select Bits.<br>See Table 9-1 and Table 9-2 for decoding. |

## FIGURE 9-7: PREFB REGISTER

| 9Ch           | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PREFB         | PRB7  | PRB6  | PRB5  | PRB4  | PRB3  | PRB2  | PRB1  | PRB0  |

| Read/Write    | R/W   |

| POR value 00h | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Bit   | Name                                                         | Function                                                                                   |

|-------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| B7-B0 | PRB7<br>PRB6<br>PRB5<br>PRB4<br>PRB3<br>PRB2<br>PRB1<br>PRB0 | Programmable Reference B Voltage Select Bits.<br>See Table 9-1 and Table 9-2 for decoding. |

#### 10.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION registers. Thus, time-out periods up to 2.3 seconds can be realized. The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the status register will be cleared upon a watchdog timer time-out. The WDT time-out period (no prescaler) is measured and stored in calibration space at location 0FD2h.

#### 10.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst-case conditions (minimum VDD, maximum temperature, maximum WDT prescaler) it may take several seconds before a WDT time-out occurs. Refer to Section 6.3 for prescaler switching considerations.

#### 10.8 <u>Power Management Options</u>

The PIC14000 has several power management options to prolong battery lifetime. The SLEEP instruction halts the CPU and can turn off the on-chip oscillators. The CPU can be in SLEEP mode, yet the A/D converter can continue to run. Several bits are included in the SLPCON register (8Fh) to control power to analog modules.

| Function                                  | Summary                                                                      |

|-------------------------------------------|------------------------------------------------------------------------------|

| CPU Clock                                 | OFF during SLEEP/HIBERNATE mode, ON otherwise                                |

| Main Oscillator                           | ON if NOT in SLEEP mode. In SLEEP mode, controlled by OSCOFF bit, SLPCON<3>. |

| Watchdog Timer                            | Controlled by WDTE, 2007h<2> and HIBEN, SLPCON<7>                            |

| Temperature Sensor                        | Controlled by TEMPOFF, SLPCON<1>                                             |

| Low-voltage Detector                      | Controlled by REFOFF, SLPCON<5>                                              |

| Comparator and<br>Programmable References | Controlled by CMOFF, SLPCON<2>                                               |

| A/D Comparator                            | Controlled by ADOFF, SLPCON<0>                                               |

| Programmable Current Source               | Controlled by ADOFF, SLPCON<0> and ADCON1<7:4>                               |

| Slope Reference Voltage Divider           | Controlled by ADOFF, SLPCON<0>                                               |

| Level Shift Networks                      | Controlled by LSOFF, SLPCON<4>                                               |

| Bandgap Reference                         | Controlled by REFOFF, SLPCON<5>                                              |

| Voltage Regulator Control                 | Always ON. Does not consume power if unconnected.                            |

| Power On Reset                            | Always ON, except in SLEEP/HIBERNATE mode                                    |

## TABLE 10-6: SUMMARY OF POWER MANAGEMENT OPTIONS

**Note:** Refer to analog specs for individual peripheral operating currents.

# PIC14000

| CLRWDT           | Clear Watchdog Timer                                                                                                                               |         |                  |                          |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|--------------------------|--|--|

| Syntax:          | [ label ] CLRWDT                                                                                                                                   |         |                  |                          |  |  |

| Operands:        | None                                                                                                                                               |         |                  |                          |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |         |                  |                          |  |  |

| Status Affected: | TO, PD                                                                                                                                             |         |                  |                          |  |  |

| Encoding:        | 00                                                                                                                                                 | 0000    | 0110             | 0100                     |  |  |

| Description:     | CLRWDT instruction resets the Watch-<br>dog Timer. It also resets the prescaler<br>of the WDT. Status bits TO and PD<br>are set.                   |         |                  |                          |  |  |

| Words:           | 1                                                                                                                                                  |         |                  |                          |  |  |

| Cycles:          | 1                                                                                                                                                  |         |                  |                          |  |  |

| Example          | CLRWDT                                                                                                                                             |         |                  |                          |  |  |

|                  | After Inst                                                                                                                                         | WDT cou | nter =<br>nter = | ?<br>0x00<br>0<br>1<br>1 |  |  |

| DECF             | Decreme                                                          | ent f                                     |                         |                              |                                 |

|------------------|------------------------------------------------------------------|-------------------------------------------|-------------------------|------------------------------|---------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                        |                                           |                         |                              |                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ d \in \ [0,1] \end{array}$ | 27                                        |                         |                              |                                 |

| Operation:       | (f) - 1 $ ightarrow$                                             | (dest)                                    |                         |                              |                                 |

| Status Affected: | Z                                                                |                                           |                         |                              |                                 |

| Encoding:        | 00                                                               | 0011                                      | df                      | ff                           | ffff                            |

| Description:     | Decremen<br>result is st<br>is 1 the res<br>'f'.                 | it register<br>ored in th<br>sult is stor | 'f'. If<br>e W<br>ed ba | 'd' is (<br>regist<br>ack in | ) the<br>er. If 'd'<br>register |

| Words:           | 1                                                                |                                           |                         |                              |                                 |

| Cycles:          | 1                                                                |                                           |                         |                              |                                 |

| Example          | DECF                                                             | CNT,                                      | 1                       |                              |                                 |

|                  | After Inst                                                       | CNT<br>Z                                  | )<br>=<br>=<br>=        | 0x01<br>0<br>0x00<br>1       |                                 |

| COMF             | Complen                                                                                                                                                 | nent f |              |                   |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|-------------------|--|

| Syntax:          | [label] COMF f,d                                                                                                                                        |        |              |                   |  |

| Operands:        | 0 ≤ f ≤ 127<br>d ∈ [0,1]                                                                                                                                |        |              |                   |  |

| Operation:       | $(\bar{\mathrm{f}})  ightarrow (\mathrm{des}$                                                                                                           | st)    |              |                   |  |

| Status Affected: | Z                                                                                                                                                       |        |              |                   |  |

| Encoding:        | 00                                                                                                                                                      | 1001   | dfff         | ffff              |  |

| Description:     | The contents of register 'f' are comple-<br>mented. If 'd' is 0 the result is stored in<br>W. If 'd' is 1 the result is stored back in<br>register 'f'. |        |              |                   |  |

| Words:           | 1                                                                                                                                                       |        |              |                   |  |

| Cycles:          | 1                                                                                                                                                       |        |              |                   |  |

| Example          | COMF                                                                                                                                                    | REC    | G1,0         |                   |  |

|                  | After Inst                                                                                                                                              | REG1   | = 0x<br>= 0x | x13<br>x13<br>xEC |  |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                               |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is 0 the result is placed in<br>the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded. A<br>NOP is executed instead making it a two<br>cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Example          | HERE DECFSZ CNT, 1                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                  | $\begin{array}{rcl} PC &=& address \ {\rm HERE} \\ \mbox{After Instruction} \\ CNT &=& CNT - 1 \\ \mbox{if CNT} &=& 0, \\ PC &=& address \ {\rm CONTINUE} \\ \mbox{if CNT} \neq& 0, \\ PC &=& address \ {\rm HERE} + 1 \end{array}$                                                                                            |  |  |  |  |

# PIC14000

| SWAPF            | Swap Nibbles in f                                                                    | XORLW            | Exclusive OR Literal with W                                               |

|------------------|--------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                    | Syntax:          | [ <i>label</i> ] XORLW k                                                  |

| Operands:        | $0 \le f \le 127$                                                                    | Operands:        | 0 ≤ k ≤ 255                                                               |

|                  | d ∈ [0,1]                                                                            | Operation:       | (W) .XOR. $k \rightarrow (W)$                                             |

| Operation:       | (f<3:0>) → (dest<7:4>),<br>(f<7:4>) → (dest<3:0>)                                    | Status Affected: | Z                                                                         |

| Status Affected: | None                                                                                 | Encoding:        | 11 1010 kkkk kkkk                                                         |

| Encoding:        | 00 1110 dfff ffff                                                                    | Description:     | The contents of the W register are XOR'ed with the eight bit literal 'k'. |

| Description:     | The upper and lower nibbles of regis-<br>ter 'f' are exchanged. If 'd' is 0 the      |                  | The result is placed in the W register.                                   |

|                  | result is placed in W register. If 'd' is 1<br>the result is placed in register 'f'. | Words:           | 1                                                                         |

| Words:           | 1                                                                                    | Cycles:          | 1                                                                         |

| Cycles:          | 1                                                                                    | Example:         | XORLW 0xAF                                                                |

| Example          | SWAPF REG, 0                                                                         |                  | Before Instruction                                                        |

| ·                | Before Instruction                                                                   |                  | W = 0xB5                                                                  |

|                  | REG1 = 0xA5                                                                          |                  | After Instruction                                                         |

|                  | After Instruction                                                                    |                  | W = 0x1A                                                                  |

|                  | REG1 = 0xA5<br>W = 0x5A                                                              |                  |                                                                           |

| TRIS             | Load TRIS Register                                                                                                                                                                  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                                                                                             |  |  |  |

| Operands:        | $5 \le f \le 7$                                                                                                                                                                     |  |  |  |

| Operation:       | (W) $\rightarrow$ TRIS register f;                                                                                                                                                  |  |  |  |

| Status Affected: | None                                                                                                                                                                                |  |  |  |

| Encoding:        | 00 0000 0110 0fff                                                                                                                                                                   |  |  |  |

| Description:     | The instruction is supported for code<br>compatibility with the PIC16C5X prod-<br>ucts. Since TRIS registers are read-<br>able and writable, the user can directly<br>address them. |  |  |  |

| Words:           | 1                                                                                                                                                                                   |  |  |  |

| Cycles:          | 1                                                                                                                                                                                   |  |  |  |

| Example          |                                                                                                                                                                                     |  |  |  |

|                  | To maintain upward compatibility<br>with future PIC16CXX products, do<br>not use this instruction.                                                                                  |  |  |  |

|                  |                                                                                                                                                                                     |  |  |  |

| XORWF            | Exclusiv                                                                                                                                                                              | e OR W   | with f | :            |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--------------|--|

| Syntax:          | [ label ]                                                                                                                                                                             | XORWF    | f,d    |              |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                    |          |        |              |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                                                                                    |          |        |              |  |

| Status Affected: | Z                                                                                                                                                                                     |          |        |              |  |

| Encoding:        | 00                                                                                                                                                                                    | 0110     | dfff   | ffff         |  |

| Description:     | Exclusive OR the contents of the W<br>register with register 'f'. If 'd' is 0 the<br>result is stored in the W register. If 'd'<br>is 1 the result is stored back in register<br>'f'. |          |        |              |  |

| Words:           | 1                                                                                                                                                                                     |          |        |              |  |

| Cycles:          | 1                                                                                                                                                                                     |          |        |              |  |

| Example          | XORWF                                                                                                                                                                                 | REG      | 1      |              |  |

|                  | Before Instruction                                                                                                                                                                    |          |        |              |  |

|                  |                                                                                                                                                                                       | REG<br>W | =      | 0xAF<br>0xB5 |  |

|                  | After Instruction                                                                                                                                                                     |          |        |              |  |

|                  |                                                                                                                                                                                       | REG<br>W | =      | 0x1A<br>0xB5 |  |

# 13.0 ELECTRICAL CHARACTERISTICS FOR PIC14000 ABSOLUTE MAXIMUM RATINGS †

| Ambient temperature under bigg 55°C to 1.12                                                                                 | ۶°℃  |

|-----------------------------------------------------------------------------------------------------------------------------|------|

| Ambient temperature under bias55°C to+ 125                                                                                  | 50   |

| Storage Temperature65°C to +150                                                                                             | 0°C  |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                | .6V  |

| Voltage on VDD with respect to Vss 0 to +6.                                                                                 |      |

| Voltage on MCLR with respect to Vss (Note 2)0 to +1                                                                         | 4 V  |

| Total power Dissipation (Note 1)                                                                                            | 0 W  |

| Maximum Current out of Vss pin                                                                                              | mA   |

| Maximum Current into VDD pin                                                                                                | mA   |

| Input clamp current, Iικ (VI <0 or VI> VDD)±20                                                                              | mA   |

| Output clamp current, loк (Vo <0 or Vo>VDD)±20                                                                              | mA   |

| Output clamp current, Iok (VO <0 or VO>VDD)                                                                                 | δmA  |

|                                                                                                                             | δmA  |

| Maximum Current sunk by PORTA, PORTC, and PORTD(combined)                                                                   |      |

| Maximum Current sourced by PORTA, PORTC, and PORTE (combined)                                                               | mA   |

| Maximum Current sunk by PORTC and PORTD (combined)                                                                          | mA   |

| Maximum Current sourced by PORTC and PORTD (combined)                                                                       | )mA  |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = $VDDx \{Ipp - \SigmaIOH\}$ $X = VDDx \{Ipp - \SigmaIOH\}$ | OL)  |

| Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80mA, may cause latch-up. Th               | nus, |

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**†** NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

© 1996 Microchip Technology Inc.

## 13.2 DC Characteristics:

PIC14000

| DC CHARACTERISTICS                                |            | Operating                     | temp             | erature                                                                    | -40<br>( | Processing the second state of the second st |

|---------------------------------------------------|------------|-------------------------------|------------------|----------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characteristic                                    | Sym        | Min                           | Typ†             | ~                                                                          | Units    | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Input Low Voltage                                 |            |                               |                  |                                                                            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I/O ports                                         | VIL        |                               |                  |                                                                            |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |