Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C                                                         |

| Peripherals                | POR, Temp Sensor, WDT                                                    |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | Slope A/D                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                           |

| Supplier Device Package    | 28-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic14000-20-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The special function registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-3). These registers are static RAM.

The special registers are classified into two sets. Special registers associated with the "core" functions are described in this section. Those registers related to the operation of the peripheral features are described in the section specific to that peripheral.

#### **TABLE 4-3**: SPECIAL FUNCTION REGISTERS FOR THE PIC14000

| Address | Name                          | Bit 7                   | Bit 6                                                                                        | Bit 5              | Bit 4         | Bit 3              | Bit 2              | Bit 1              | Bit 0              |

|---------|-------------------------------|-------------------------|----------------------------------------------------------------------------------------------|--------------------|---------------|--------------------|--------------------|--------------------|--------------------|

| Bank0   |                               |                         | -                                                                                            |                    |               |                    | -                  | -                  |                    |

| 00h*    | INDF<br>(Indirect<br>Address) | Addressing register).   | Addressing this location uses contents of the FSR to address data memory (not a p register). |                    |               |                    |                    |                    |                    |

| 01h     | TMR0                          | Timer0 data             | а                                                                                            |                    |               |                    |                    |                    |                    |

| 02h*    | PCL                           | Program C               | ounter's (P                                                                                  | C's) least si      | gnificant by  | te                 |                    |                    |                    |

| 03h*    | STATUS                        | IRP                     | RP1                                                                                          | RP0                | TO            | PD                 | Z                  | DC                 | С                  |

| 04h*    | FSR                           | Indirect dat            | a memory a                                                                                   | address poi        | nter          |                    |                    |                    |                    |

| 05h     | PORTA                         | PORTA dat               | ta latch.                                                                                    |                    |               |                    |                    |                    |                    |

| 06h     | Reserved                      | Reserved f              | or emulatio                                                                                  | n.                 |               |                    |                    |                    |                    |

| 07h     | PORTC                         | PORTC da                | ta latch                                                                                     |                    |               |                    |                    |                    |                    |

| 08h     | PORTD                         | PORTD da                | ta latch                                                                                     |                    |               |                    |                    |                    |                    |

| 09h     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 0Ah*    | PCLATH                        | Buffered re             | gister for th                                                                                | ne upper 5 b       | its of the Pr | ogram Cou          | inter (PC)         |                    |                    |

| 0Bh*    | INTCON                        | GIE                     | PEIE                                                                                         | TOIE               | r             | r                  | T0IF               | r                  | r                  |

| 0Ch     | PIR1                          | CMIF                    | _                                                                                            | _                  | PBIF          | I <sup>2</sup> CIF | RCIF               | ADCIF              | OVFIF              |

| 0Dh     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 0Eh     | ADTMRL                        | A/D capture             | e timer data                                                                                 | a least signi      | ficant byte   |                    |                    |                    |                    |

| 0Fh     | ADTMRH                        | A/D capture             | e timer data                                                                                 | a most signi       | ficant byte   |                    |                    |                    |                    |

| 10h     | Reserved                      |                         |                                                                                              | -                  |               |                    |                    |                    |                    |

| 11h     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 12h     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 13h     | I <sup>2</sup> CBUF           | I <sup>2</sup> C Serial | Port Receiv                                                                                  | /e Buffer/Tr       | ansmit Regi   | ster               |                    |                    |                    |

| 14h     | I <sup>2</sup> CCON           | WCOL                    | I <sup>2</sup> COV                                                                           | I <sup>2</sup> CEN | CKP           | I <sup>2</sup> CM3 | I <sup>2</sup> CM2 | I <sup>2</sup> CM1 | I <sup>2</sup> CM0 |

| 15h     | ADCAPL                        | A/D capture             | e latch leas                                                                                 | t significant      | byte          |                    |                    |                    |                    |

| 16h     | ADCAPH                        | A/D capture             | e latch mos                                                                                  | t significant      | byte          |                    |                    |                    |                    |

| 17h     | Reserved                      |                         |                                                                                              | -                  | -             |                    |                    |                    |                    |

| 18h     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 19h     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 1Ah     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 1Bh     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 1Ch     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 1Dh     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 1Eh     | Reserved                      |                         |                                                                                              |                    |               |                    |                    |                    |                    |

| 1Fh     | ADCON0                        | ADCS3                   | ADCS2                                                                                        | ADCS1              | ADCS0         |                    | AMUXOE             | ADRST              | ADZER              |

- = unimplemented bits, read as '0' but cannot be overwritten

a full preference bits, default is POR value and should not be overwritten with any value

Reserved indicates reserved register and should not be overwritten with any value

\* indicates registers that can be addressed from either bank

### 4.2.2.3 INTCON REGISTER

The INTCON Register is a readable and writable register which contains the various enable and flag bits for the Timer0 overflow and peripheral interrupts. Figure 4-5 shows the bits for the INTCON register.

Note: The TOIF will be set by the specified condition even if the corresponding Interrupt Enable Bit is cleared (interrupt disabled) or the GIE bit is cleared (all interrupts disabled). Before enabling interrupt, clear the interrupt flag, to ensure that the program does not immediately branch to the peripheral interrupt service routine

| R/W  | R/W  | R/W  | R/W | R/W | R/W  | R/W | R/W  | Register: INTCON W: Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|------|------|-----|-----|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GIE  | PEIE | TOIE | r   | r   | TOIF | r   | r    | Address: 0Bh or 8Bh R: Readable<br>POR value: 0000 000xb U: Unimplemented,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| bit7 |      |      |     |     |      |     | bit0 | read as '0'         Reserved. This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.         Reserved. This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.         TOIF: TMR0 overflow interrupt flag         1 = The TMR0 has overflowed Must be cleared by software         0 = TMR0 did not overflow         Reserved. This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products. |

|      |      |      |     |     |      |     |      | <b>Reserved.</b> This bit should be programmed as '0'. Use of this bit as a general purpose read/write bit is not recommended, since this may affect upward compatibility with future products.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      |      |      |     |     |      |     |      | <b>TOIE:</b> TMR0 interrupt enable bit<br>1 = Enables TOIF interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |      |      |     |     |      |     |      | 0 = Disables T0IF interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | L    |      |     |     |      |     |      | PEIE: Peripheral interrupt enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      |      |      |     |     |      |     |      | <ul><li>1 = Enables all un-masked peripheral interrupts</li><li>0 = Disables all peripheral interrupts</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |      |      |     |     |      |     |      | GIE: Global interrupt enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |      |      |     |     |      |     |      | 1 = Enables all un-masked interrupts<br>0 = Disables all interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## FIGURE 4-5: INTCON REGISTER

This interrupt can wake the device up from SLEEP. The user, in the interrupt service routine, can clear the interrupt in one of two ways:

- Disable the interrupt by clearing the RCIE (PIE1<2>) bit

- Read PORTC. This will end mismatch condition. Then, clear the RCIF (PIR1<2>) bit.

A mismatch condition will continue to set the RCIF bit. Reading PORTC will end the mismatch condition, and allow the RCIF bit to be cleared.

If bit CMAOE (CMCON<1>) is set, the RC0/REFA pin becomes the programmable reference A and analog output. Pin RC1/CMPA becomes the comparator A output.

| Note: | Setting CMAOE changes the definition of |

|-------|-----------------------------------------|

|       | RC0/REFA and RC1/CMPA, bypassing        |

|       | the PORTC data and TRISC register set-  |

|       | tings.                                  |

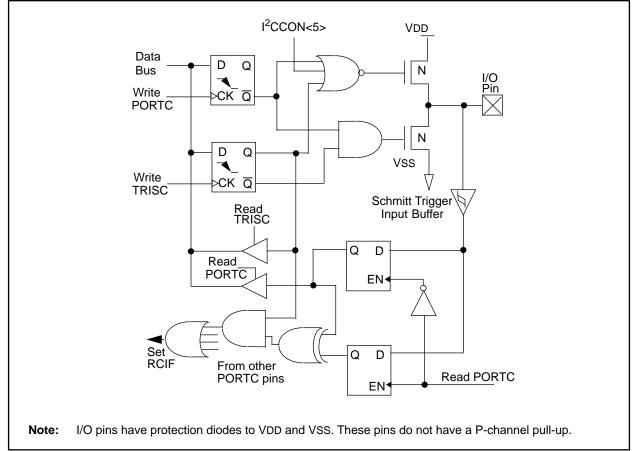

PORTC<7:6> also serves multiple functions. These pins act as the  $I^2C$  data and clock lines when the  $I^2C$  module is enabled. They also serve as the serial programming interface data and clock line for in-circuit programming of the EPROM.

The TRISC register controls the direction of the PORTC pin. A '1' in each location configures the corresponding port pin as an input. Upon reset, this register sets to FFh, meaning all PORTC pins are initially inputs. The data register should be initialized prior to configuring the port as outputs.

Unused inputs should not be left floating to avoid leakage currents. All pins have input protection diodes to VDD and VSS.

| EXAM  | IPLE 5-2:   | INITIALIZING PORTC         |

|-------|-------------|----------------------------|

| CLRF  | PORTC       | ; Initialize PORTC data    |

|       |             | ; latches before setting   |

|       |             | ; the data direction       |

|       |             | ; register                 |

| BSF   | STATUS, RPO | ;Select Bankl              |

| MOVLW | 0xCF        | ; Value used to initialize |

|       |             | ;data direction            |

| MOVWF | TRISC       | ;Set RC<3:0> as inputs     |

|       |             | ; RC<5:4> as outputs       |

|       |             | ; RC<7:6> as inputs        |

|       |             |                            |

## FIGURE 5-3: BLOCK DIAGRAM OF PORTC<7:6> PINS

© 1996 Microchip Technology Inc.

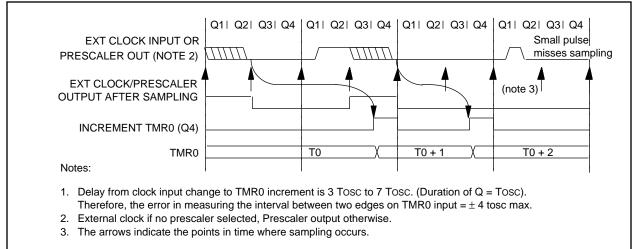

## 6.2 Using Timer0 with External Clock

When the external clock input (pin RC3/T0CKI) is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR0 after synchronization.

### 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns).

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns.

### 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

## 6.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a post-scaler for the Watchdog Timer (Figure 6-1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

Bit PSA and PS2:PS0 (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the Timer0 module (e.g., CLRF 1, MOVWF 1, BSF 1, x) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

## FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

### 6.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control, i.e., it can be changed "on the fly" during program execution. To avoid an unintended device RESET, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

## EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| 1.BCF    | STATUS, RPO  | ;Skip if already in     |

|----------|--------------|-------------------------|

|          |              | ; Bank 0                |

| 2.CLRWD1 | C            | ;Clear WDT              |

| 3.CLRF   | TMR0         | ;Clear TMR0 & Prescaler |

| 4.BSF    | STATUS, RPO  | ;Bank 1                 |

| 5.MOVLW  | '00101111'b; | These 3 lines (5, 6, 7) |

| 6.MOVWF  | OPTION       | ; are required only     |

|          |              | ; if desired PS<2:0>    |

| 7.CLRWD1 | C            | ; are 000 or 001        |

| 8.MOVLW  | '00101xxx'b  | ;Set Postscaler to      |

| 9.MOVWF  | OPTION       | ; desired WDT rate      |

| 10.BCF   | STATUS, RPO  | ;Return to Bank 0       |

To change prescaler from the WDT to the Timer0 module use the sequence shown in Example 6-2. This precaution must be taken even if the WDT is disabled.

### EXAMPLE 6-2: CHANGING PRESCALER (WDT→TIMER0)

|        | •           | ,                   |

|--------|-------------|---------------------|

| CLRWDT |             | ;Clear WDT and      |

|        |             | ;prescaler          |

| BSF    | STATUS, RPO |                     |

| MOVLW  | B'xxxx0xxx' | ;Select TMR0, new   |

|        |             | ;prescale value and |

|        |             | ;clock source       |

| MOVWF  | OPTION      |                     |

| BCF    | STATUS, RPO |                     |

|        |             |                     |

## TABLE 6-1: SUMMARY OF TIMER0 REGISTERS

| Register Name | Function                                                   | Address | Power-on Reset Value |

|---------------|------------------------------------------------------------|---------|----------------------|

| TMR0          | Timer/counter register                                     | 01h     | XXXX XXXX            |

| OPTION        | Configuration and prescaler assign-<br>ment bits for TMR0. | 81h     | 1111 1111            |

| INTCON        | TMR0 overflow interrupt flag and mask bits.                | 0Bh     | 0000 000x            |

Legend: x = unknown,

Note 1: For reset values of registers in other reset situations refer to Table 10-4.

## TABLE 6-2: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7                | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|--------|----------------------|--------|--------|--------|--------|--------|--------|--------|

| 01h     | TMR0   | TIMER0 TIMER/COUNTER |        |        |        |        |        |        |        |

| 0Bh/8Bh | INTCON | GIE                  | PEIE   | TOIE   | r      | r      | TOIF   | r      | r      |

| 81h     | OPTION | RCPU                 | r      | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    |

| 87h     | TRISC  | TRISC7               | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

Legend: r = Reserved locations

Shaded boxes are not used by Timer0 module

## FIGURE 7-16: MISC REGISTER

| 9Eh           |      | Bit 7                                                                                                                          | ,                              | Bit 6  | Bit 5  | Bit 4                                                                                                                                                          | Bit 3 | Bit 2   | Bit 1 | Bit 0 |  |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|-------|--|

| MISC          |      | SMHC                                                                                                                           | G                              | SPGNDB | SPGNDA | I <sup>2</sup> CSEL                                                                                                                                            | SMBUS | INCLKEN | OSC2  | OSC1  |  |

| Read/Write    | )    | R/W                                                                                                                            |                                | R/W    | R/W    | R/W                                                                                                                                                            | R/W   | R/W     | R/W   | R     |  |

| POR value 00h |      | 0                                                                                                                              |                                | 0      | 0      | 0                                                                                                                                                              | 0     | 0       | 0     | Х     |  |

| Bit           | N    | ame                                                                                                                            |                                |        |        | Function                                                                                                                                                       |       |         |       |       |  |

| B7            | SMHC | DG                                                                                                                             | G Section 7.5.4). conversions. |        |        | Stretch $I^2C$ CLK signal (hold low) when receive data buffer is full (refer to ion 7.5.4). For pausing $I^2C$ transfers while preventing interruptions of A/D |       |         |       |       |  |

| B6            | SPGN | Serial Port Ground Select<br>NDB 1 = PORTD<1:0> ground reference is the RD5/AN5 pin.<br>0 = PORTD<1:0> ground reference is VSS |                                |        |        |                                                                                                                                                                |       |         |       |       |  |

| B6 | SPGNDB              | <ul><li>1 = PORTD&lt;1:0&gt; ground reference is the RD5/AN5 pin.</li><li>0 = PORTD&lt;1:0&gt; ground reference is Vss.</li></ul>                                                                                                                         |

|----|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B5 | SPGNDA              | Serial Port Ground Select<br>1 = PORTC<7:6> ground reference is the RA1/AN1 pin.<br>0 = PORTC<7:6> ground reference is Vss.                                                                                                                               |

| B4 | I <sup>2</sup> CSEL | I <sup>2</sup> C Port select Bit.<br>1 = PORTD<1:0> are used as the I <sup>2</sup> C clock and data lines.<br>0 = PORTC<7:6> are used as the I <sup>2</sup> C clock and data lines.                                                                       |

| В3 | SMBus               | SMBus-Compatibility Select<br>1 = SMBus compatibility mode is enabled. PORTC<7:6> and PORTD<1:0> have<br>SMBus-compatible input thresholds.<br>0 = SMBus-compatibility is disabled. PORTC<7:6> and PORTD<1:0> have Schmitt Trig-<br>ger input thresholds. |

| B2 | INCLKEN             | Oscillator Output Select (available in IN mode only).<br>1 = Output IN oscillator signal divided by four on OSC2 pin.<br>0 = Disconnect IN oscillator signal from OSC2 pin.                                                                               |

| B1 | OSC2                | OSC2 output port bit (available in IN mode only).<br>Writes to this location affect the OSC2 pin in IN mode. Reads return the value of the output latch.                                                                                                  |

| В0 | OSC1                | OSC1 input port bit (available in IN mode only).<br>Reads from this location return the status of the OSC1 pin in IN mode. Writes have no<br>effect.                                                                                                      |

© 1996 Microchip Technology Inc.

## 9.0 OTHER ANALOG MODULES

The PIC14000 has additional analog modules for mixed signal applications. These include:

- bandgap voltage reference

- comparators with programmable references

- internal temperature sensor

- voltage regulator control

## 9.1 Bandgap Voltage Reference

The bandgap reference circuit is used to generate a 1.2V nominal stable voltage reference for the A/D and the low-voltage detector. The bandgap reference is channel 4 of the analog mux. The bandgap reference voltage is stored in the calibration space EPROM (See Table 4-2). To enable the bandgap reference REFOFF (SLPCON<5>) must be cleared.

### 9.2 Level-Shift Networks

The RA1/AN1 and RA5/AN5 pins have an internal level-shift network. A current source and resistor are used to bias the pin voltage by about +0.5V into a range usable by the A/D converter. The nominal value of bias current source is  $5 \ \mu$ A and the resistor is 100 kohms.

The level-shift function can be turned on by clearing the LSOFF bit (SLPCON<4>) to '0'.

**Note:** The minimum voltage permissible at the RA1/AN1 and RA5/AN5 pins is -0.3V. The input protection diodes will begin to turn on beyond -0.3V, introducing significant errors in the A/D readings. Under no conditions should the pin voltage fall below -0.5V.

### 9.2.1 ZEROING/FILTERING SWITCHES

The RA1/AN1 and RA5/AN5 inputs also have a matched pair of pass gates useful for current-measurement applications. One gate is connected between the pin and the level-shift network. The second pass gate is connected to ground as shown in Figure 9-1. By setting the ADZERO bit (ADCON0<0>), a zero-current condition is simulated. Subsequent A/D readings are calculated relative to this zero count from the A/D. This zeroing of the current provides very high accuracies at low current values where it is most needed.

For additional noise filtering or for capturing short duration periodic pulses, an optional filter capacitor may be connected from the SUM pin to ground (this feature is available for RA1/AN1 only). This forms an RC network with the internal 100 kohm (nominal) bias resistor to act as a low pass filter. The capacitor size can be adjusted for the desired time constant.

A switch is included between the output from the RA1/AN1 level-shift network and the SUM pin. This switch is closed during A/D sampling periods and is automatically opened during a zeroing operation (if ADZERO = '1'). If not required in the system, this pin should be left floating (not connected).

Setting the LSOFF bit (SLPCON<4>) disables the level-shift networks, so the RA1/AN1 and RA5/AN5 pins can continue to be used as general-purpose analog inputs.

NOTES:

# **PIC14000**

### 10.6.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in Timer0 will set the T0IF (INTCON<2>) flag. Setting T0IE (INTCON<5>) enables the interrupt.

### 10.6.3 PORTC INTERRUPT ON CHANGE

An input change on PORTC<7:4> sets RCIF (PIR1<2>). Setting RCIE (PIE1<2>) enables the interrupt. For operation of PORTC, refer to Section 5.2.

**Note:** If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RCIF interrupt flag may not be set.

## 10.6.4 CONTEXT SWITCHING DURING INTERRUPTS

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt, for example, W register and Status register. Example 10-1 is an example that shows saving registers in RAM.

## EXAMPLE 10-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF<br>BCF<br>BCF | W_TEMP<br>STATUS,W<br>STATUS,RP1<br>STATUS,RP0 | ;Copy W to TEMP register, could be any bank<br>;Swap status to be saved into W<br>;Change to bank zero, regardless of current bank |

|------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                | 1                                                                                                                                  |

| MOVWF                        | STATUS_TEMP                                    | ;Save status to bank zero STATUS_TEMP register                                                                                     |

| :                            |                                                |                                                                                                                                    |

| :(ISR)                       |                                                |                                                                                                                                    |

| :                            |                                                |                                                                                                                                    |

| SWAPF                        | STATUS_TEMP,W                                  | ;Swap STATUS_TEMP register into W                                                                                                  |

|                              |                                                | ;(sets bank to original state)                                                                                                     |

| MOVWF                        | STATUS                                         | ;Move W into STATUS register                                                                                                       |

| SWAPF                        | W_TEMP,F                                       | ;Swap W_TEMP                                                                                                                       |

| SWAPF                        | W_TEMP,W                                       | ;Swap W_TEMP into W                                                                                                                |

## FIGURE 10-12: SLPCON REGISTER

| 8Fh         |      | Bit 7 | Bit 6                  | Bit 5                                                                                                                                                                                  | Bit 4                                                          | Bit 3                                        | Bit 2       | Bit 1                           | Bit 0 |  |  |

|-------------|------|-------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------|-------------|---------------------------------|-------|--|--|

| SLPCON      |      | HIBEN |                        | REFOFF                                                                                                                                                                                 | LSOFF                                                          | OSCOFF                                       | CMOFF       | TEMPOFF                         | ADOFF |  |  |

| Read/Write  |      | R/W   | U                      | R/W                                                                                                                                                                                    | R/W                                                            | R/W                                          | R/W         | R/W                             | R/W   |  |  |

| POR value 3 | Fh   | 0     | 0                      | 1                                                                                                                                                                                      | 1                                                              | 1                                            | 1           | 1                               | 1     |  |  |

| Bit         |      | Name  |                        |                                                                                                                                                                                        |                                                                | Function                                     | ו           |                                 |       |  |  |

| В7          | ніві | EN    | 1 = Hi                 | nate Mode So<br>bernate mod<br>ormal operati                                                                                                                                           | e enable                                                       |                                              |             |                                 |       |  |  |

| B6          | -    |       | Unimp                  | emented. R                                                                                                                                                                             | ead as '0'                                                     |                                              |             |                                 |       |  |  |

| В5          | REF  | OFF   | bias g<br>1 = Th       | References Power Control (bandgap reference, low voltage detector,<br>bias generator)<br>1 = The references are off<br>0 = The references are on                                       |                                                                |                                              |             |                                 |       |  |  |

| B4          | LSC  | )FF   | 1 = Th<br>fu<br>0 = Th | ne level shift<br>nction as eith<br>ne level shift i                                                                                                                                   | ner analog or                                                  | f. The RA1/AN<br>digital.<br>. The signals a |             | inputs can cor<br>N1, RD5/AN5 i |       |  |  |

| В3          | oso  | COFF  | 1 = Tr<br>0 = Tr       |                                                                                                                                                                                        | lator is disab                                                 | led during SLI<br>ng during SLE              |             | A/D conversio                   | ns to |  |  |

| B2          | СМО  | OFF   | 1 = Th                 | Programmable Reference and Comparator Power Control<br>1 = The programmable reference and comparator circuits are off<br>0 = The programmable reference and comparator circuits are on |                                                                |                                              |             |                                 |       |  |  |

| B1          | TEN  | 1POFF | 1 = Th                 | ie temperatu                                                                                                                                                                           | ire Sensor P<br>re sensor is o<br>re sensor is o               |                                              |             |                                 |       |  |  |

| В0          | ADC  | DFF   | slope<br>1 = Tł        | reference vo<br>ne A/D modul                                                                                                                                                           | Control (cor<br>ltage divider)<br>e power is o<br>e power is o | ff                                           | rammable cu | rrent source,                   |       |  |  |

| Droduct                                                                                                                                               | ** MDI A DTM                         |                                   | MD-Drive/Max      |                              | *** DICMACTED®/                                                                                                                                                                       |                                                                |                                                                                                                                                                            |                                                                                                                                                                                                                                    | DIC CTADT® DI         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------|-------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

|                                                                                                                                                       | Integrated                           | Compiler                          | Applications      | Explorer/Edition             | PICMASTER-CE                                                                                                                                                                          | Low-Cost                                                       | II Universal                                                                                                                                                               | Ultra Low-Cost                                                                                                                                                                                                                     | Low-Cost              |

|                                                                                                                                                       | Development<br>Environment           |                                   | Code<br>Generator | Fuzzy Logic<br>Dev. Tool     | In-Circuit<br>Emulator                                                                                                                                                                | In-Circuit<br>Emulator                                         | Microchip<br>Programmer                                                                                                                                                    | Dev. Kit                                                                                                                                                                                                                           | Universal<br>Dev. Kit |

| PIC12C508, 509                                                                                                                                        | SW007002                             | SW006005                          |                   | I                            | EM167015/<br>EM167101                                                                                                                                                                 | 1                                                              | DV007003                                                                                                                                                                   | Ι                                                                                                                                                                                                                                  | DV003001              |

| PIC14000                                                                                                                                              | SW007002                             | SW006005                          |                   | Ι                            | EM147001/<br>EM147101                                                                                                                                                                 | 1                                                              | DV007003                                                                                                                                                                   | Ι                                                                                                                                                                                                                                  | DV003001              |

| PIC16C52, 54, 54A,<br>55, 56, 57, 58A                                                                                                                 | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167015/<br>EM167101                                                                                                                                                                 | EM167201                                                       | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C554, 556, 558                                                                                                                                   | SW007002                             | SW006005                          | I                 | DV005001/<br>DV005002        | EM167033/<br>EM167113                                                                                                                                                                 | 1                                                              | DV007003                                                                                                                                                                   | Ι                                                                                                                                                                                                                                  | DV003001              |

| PIC16C61                                                                                                                                              | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167021/<br>N/A                                                                                                                                                                      | EM167205                                                       | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C62, 62A,<br>64, 64A                                                                                                                             | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167025/<br>EM167103                                                                                                                                                                 | EM167203                                                       | DV007003                                                                                                                                                                   | DV162002                                                                                                                                                                                                                           | DV003001              |

| PIC16C620, 621, 622                                                                                                                                   | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167023/<br>EM167109                                                                                                                                                                 | EM167202                                                       | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C63, 65, 65A,<br>73, 73A, 74, 74A                                                                                                                | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167025/<br>EM167103                                                                                                                                                                 | EM167204                                                       | DV007003                                                                                                                                                                   | DV162002                                                                                                                                                                                                                           | DV003001              |

| PIC16C642, 662*                                                                                                                                       | SW007002                             | SW006005                          |                   | I                            | EM167035/<br>EM167105                                                                                                                                                                 | 1                                                              | DV007003                                                                                                                                                                   | DV162002                                                                                                                                                                                                                           | DV003001              |

| PIC16C71                                                                                                                                              | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167027/<br>EM167105                                                                                                                                                                 | EM167205                                                       | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C710, 711                                                                                                                                        | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167027/<br>EM167105                                                                                                                                                                 |                                                                | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C72                                                                                                                                              | SW007002                             | SW006005                          | SW006006          | I                            | EM167025/<br>EM167103                                                                                                                                                                 |                                                                | DV007003                                                                                                                                                                   | DV162002                                                                                                                                                                                                                           | DV003001              |

| PIC16F83                                                                                                                                              | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167029/<br>EM167107                                                                                                                                                                 | 1                                                              | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C84                                                                                                                                              | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167029/<br>EM167107                                                                                                                                                                 | EM167206                                                       | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16F84                                                                                                                                              | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167029/<br>EM167107                                                                                                                                                                 |                                                                | DV007003                                                                                                                                                                   | DV162003                                                                                                                                                                                                                           | DV003001              |

| PIC16C923, 924*                                                                                                                                       | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM167031/<br>EM167111                                                                                                                                                                 |                                                                | DV007003                                                                                                                                                                   | 1                                                                                                                                                                                                                                  | DV003001              |

| PIC17C42,<br>42A, 43, 44                                                                                                                              | SW007002                             | SW006005                          | SW006006          | DV005001/<br>DV005002        | EM177007/<br>EM177107                                                                                                                                                                 |                                                                | DV007003                                                                                                                                                                   | I                                                                                                                                                                                                                                  | DV003001              |

| *Contact Microchip Technology for availability date<br>**MPLAB Integrated Development Environment includes MPLAB-SIM Simulator and<br>MPASM Assembler | chnology for avai<br>velopment Envir | llability date<br>onment include: | s MPLAB-SIM Si    | mulator and                  | ***All PICMASTER and PICMASTER-CE ordering part<br>PRO MATE II programmer<br>****PRO MATE socket modules are ordered separately.<br>ordering guide for specific ordering part numbers | and PICMAST<br>rogrammer<br>et modules are<br>or specific orde | II PICMASTER and PICMASTER-CE ordering par<br>PRO MATE II programmer<br>RO MATE socket modules are ordered separately<br>ordering guide for specific ordering part numbers | ***All PICMASTER and PICMASTER-CE ordering part numbers above include<br>PRO MATE II programmer<br>***PRO MATE socket modules are ordered separately. See development systems<br>ordering guide for specific ordering part numbers | stems                 |

| Product                                                                                                                                               | TRUEGAUG                             | <b>TRUEGAUGE® Development Kit</b> |                   | <b>SEEVAL® Designers Kit</b> | Hopping Code Security Programmer Kit                                                                                                                                                  | Security Prog                                                  |                                                                                                                                                                            | Hopping Code Security Eval/Demo Kit                                                                                                                                                                                                | ty Eval/Demo Kit      |

| All 2 wire and 3 wire<br>Serial EEPROM's                                                                                                              |                                      | N/A                               |                   | DV243001                     |                                                                                                                                                                                       | N/A                                                            |                                                                                                                                                                            | N/A                                                                                                                                                                                                                                |                       |

| MTA11200B                                                                                                                                             |                                      | DV114001                          |                   | N/A                          |                                                                                                                                                                                       | N/A                                                            |                                                                                                                                                                            | N/A                                                                                                                                                                                                                                |                       |

| HCS200, 300, 301 *                                                                                                                                    |                                      | N/A                               |                   | N/A                          |                                                                                                                                                                                       | PG306001                                                       |                                                                                                                                                                            | DM303001                                                                                                                                                                                                                           | 001                   |

## TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

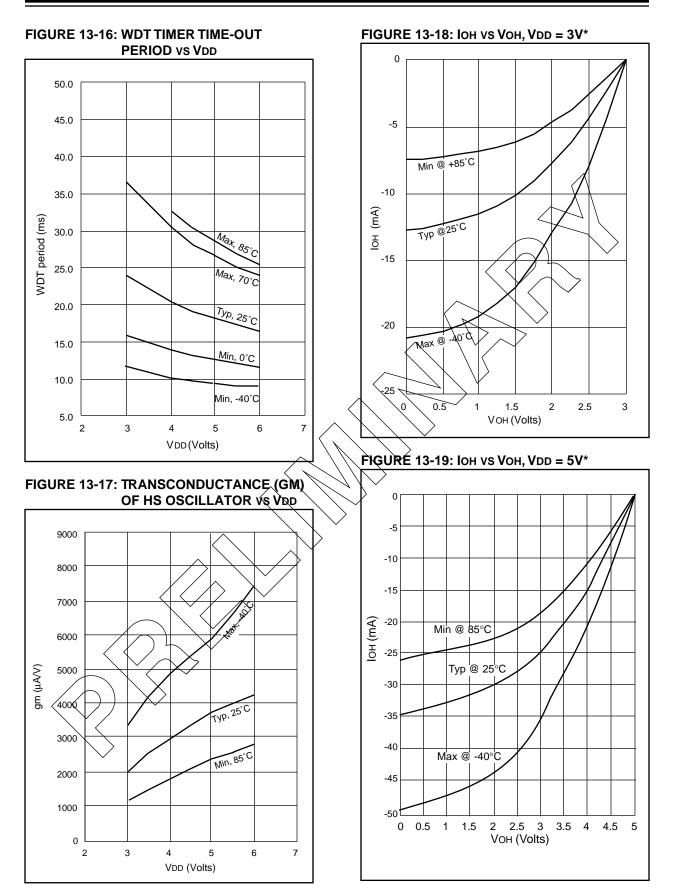

### 13.1 DC Characteristics:

#### **PIC14000**

| DC CHARACTERISTICS                                                        |                 | <b>Standa</b><br>Operati |                  |                          | re -40         | tions (unless otherwise stated)<br>$P^{\circ}C \leq TA \leq + 85^{\circ}C$ for industrial and<br>$P^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |  |

|---------------------------------------------------------------------------|-----------------|--------------------------|------------------|--------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                           |                 | Operati                  | ng volta         | age V                    | DD = 2.7       | 7V to 6.0V                                                                                                                                             |  |

| Characteristic                                                            | Sym             | Min                      | Typ†             | Max                      | Units          | Conditions                                                                                                                                             |  |

| Supply Voltage                                                            | Vdd             | 2.7                      | _                | 6.0                      | V              | IN or HS at Fosc ≤ 4 MHz                                                                                                                               |  |

|                                                                           |                 | 4.5                      | _                | 5.5                      | v              | HS at Fosc > 4 MHz                                                                                                                                     |  |

| RAM Data Retention<br>Voltage (Note 1)                                    | Vdr             | —                        | 1.5              | -                        | V              | Device in SLEEP mode                                                                                                                                   |  |

| VDD start voltage to guarantee Power-On Reset                             | VPOR            | _                        | Vss              | -                        | V              | See section on power-on reset for details                                                                                                              |  |

| VDD rise rate to guarantee<br>Power-On Reset                              | SVDD            | 0.05*                    | _                | -                        | V/ms           | See section on power-on reset for details                                                                                                              |  |

| Operating Current in SLEEP Mod                                            | le (Note 2      | )                        |                  |                          |                | $\sim$                                                                                                                                                 |  |

| During A/D conversion:<br>all analog on and internal<br>oscillator active | IPD1<br>IPD1    | _                        | TBD<br>TBD       | 900<br>1250              | μΑ<br>μΑ       | VDD = 3.0V<br>VDD = 4.0V                                                                                                                               |  |

| Comparator interrupt enabled:<br>level-shift, programmable                | IPD2            | _                        | 75               | 100                      | μA             | $V_{DD} = 3.0V, CMOFF = 0, LSOFF = 0, REFOFF = 0$                                                                                                      |  |

| reference, and comparator active                                          | IPD2            | -                        | 95               | 125                      | μΑ             | V = 7.0 , CMOFF = 0,  LSOFF = 0,  REFOFF = 0                                                                                                           |  |

| All analog off, WDT on (Note 5)                                           | IPD3<br>IPD3    | _                        | 7.5<br>10.5      | 20<br>28                 | μΑ<br>γιΑ      | $\begin{array}{l} V_{\text{DD}} = 3.0V\\ V_{\text{DD}} = 4.0V \end{array}$                                                                             |  |