Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

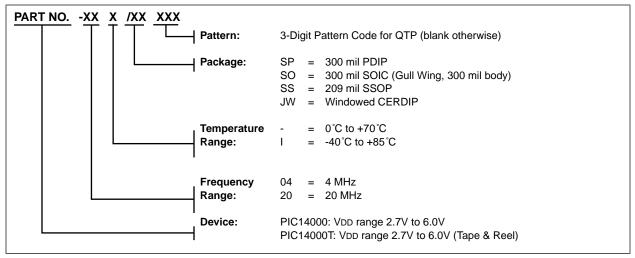

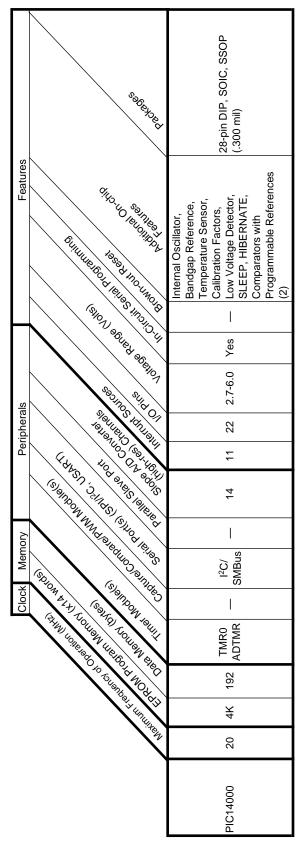

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | I <sup>2</sup> C                                                         |

| Peripherals                | POR, Temp Sensor, WDT                                                    |

| Number of I/O              | 20                                                                       |

| Program Memory Size        | 7KB (4K x 14)                                                            |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                |                                                                          |

| RAM Size                   | 192 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 6V                                                                |

| Data Converters            | Slope A/D                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                          |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 28-SPDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic14000-20-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Address | Name                            | Bit 7                   | Bit 6         | Bit 5         | Bit 4               | Bit 3              | Bit 2     | Bit 1         | Bit 0      |

|---------|---------------------------------|-------------------------|---------------|---------------|---------------------|--------------------|-----------|---------------|------------|

| Bank1   |                                 |                         |               | ·             |                     |                    |           |               |            |

| 80h*    | INDF<br>(Indirect Ad-<br>dress) | ter).                   | this locatio  | on uses cont  | ents of FSF         | R to address       | ata memo  | ry (not a phy | sical regi |

| 81h     | OPTION                          | RCPU                    | r             | TOCS          | TOSE                | PSA                | PS2       | PS1           | PS0        |

| 82h*    | PCL                             | Program C               | ounter's (P   | C's) least si | gnificant by        | te                 |           |               |            |

| 83h*    | STATUS                          | IRP                     | RP1           | RP0           | TO                  | PD                 | Z         | DC            | С          |

| 84h*    | FSR                             | Indirect dat            | a memory a    | address poir  | nter                |                    |           |               |            |

| 85h     | TRISA                           | PORTA Da                | ta Directior  | n Register    |                     |                    |           |               |            |

| 86h     | Reserved                        | Reserved f              | or emulatio   | n             |                     |                    |           |               |            |

| 87h     | TRISC                           | PORTC Da                | ta Directior  | n Register    |                     |                    |           |               |            |

| 88h     | TRISD                           | PORTD Da                | ta Directior  | n Register    |                     |                    |           |               |            |

| 89h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 8Ah*    | PCLATH                          | Buffered re             | gister for th | e upper 5 b   | its of the Pi       | rogram Cou         | nter (PC) |               |            |

| 8Bh*    | INTCON                          | GIE                     | PEIE          | TOIE          | r                   | r                  | TOIF      | r             | r          |

| 8Ch     | PIE1                            | CMIE                    | _             | _             | PBIE                | I <sup>2</sup> CIE | RCIE      | ADCIE         | OVFIE      |

| 8Dh     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 8Eh     | PCON                            | r                       | _             | _             | _                   | _                  |           | POR           | LVD        |

| 8Fh     | SLPCON                          | HIBEN                   | _             | REFOFF        | LSOFF               | OSCOFF             | CMOFF     | TEMPOFF       | ADOFF      |

| 90h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 91h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 92h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 93h     | I <sup>2</sup> CADD             | I <sup>2</sup> C Synchi | ronous Seri   | al Port Add   | ress Regist         | er                 |           |               |            |

| 94h     | I <sup>2</sup> CSTAT            | _                       | _             | D/Ā           | P                   | S                  | R/W       | UA            | BF         |

| 95h     | Reserved                        |                         |               | 1             |                     | 11                 |           | 11            |            |

| 96h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 97h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 98h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 99h     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 9Ah     | Reserved                        |                         |               |               |                     |                    |           |               |            |

| 9Bh     | PREFA                           | PRA7                    | PRA6          | PRA5          | PRA4                | PRA3               | PRA2      | PRA1          | PRA0       |

| 9Ch     | PREFB                           | PRB7                    | PRB6          | PRB5          | PRB4                | PRB3               | PRB2      | PRB1          | PRB0       |

| 9Dh     | CMCON                           |                         | CMBOUT        | CMBOE         | CPOLB               |                    | CMAOUT    | CMAOE         | CPOLA      |

| 9Eh     | MISC                            | SMHOG                   | SPGNDB        | SPGNDA        | I <sup>2</sup> CSEL | SMBUS              | INCLKEN   | OSC2          | OSC1       |

| 9Fh     | ADCON1                          | ADDAC3                  | ADDAC2        | ADDAC1        | ADDAC0              | PCFG3              | PCFG2     | PCFG1         | PCFG       |

#### SPECIAL FUNCTION REGISTERS FOR THE PIC14000 (CONTINUED) **TABLE 4-3:**

Legend

= unimplemented bits, read as '0' but cannot be overwritten

r = reserved bits, default is POR value and should not be overwritten with any value

Reserved indicates reserved register and should not be overwritten with any value

\* indicates registers that can be addressed from either bank

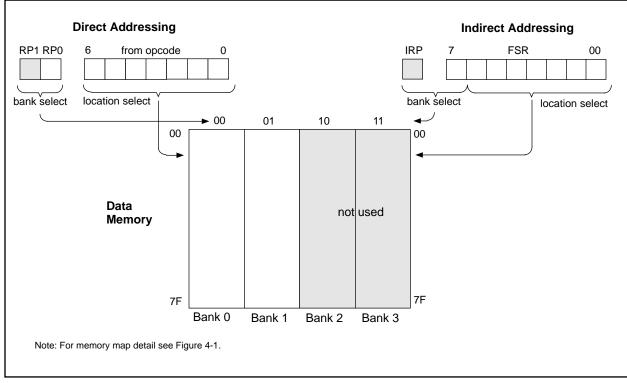

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the file select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-10. However, IRP is not used in the PIC14000.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-2.

# EXAMPLE 4-2: INDIRECT ADDRESSING

|      | movlw | 0x20  | ;initialize pointer  |

|------|-------|-------|----------------------|

|      | movf  | FSR   | ;to RAM              |

| NEXT | clrf  | INDF  | ;clear INDF register |

|      | incf  | FSR   | ;inc pointer         |

|      | btfss | FSR,4 | ;all done?           |

|      | goto  | NEXT  | ;no clear next       |

|      |       |       | ;yes continue        |

CONTINUE:

# FIGURE 4-10: INDIRECT/INDIRECT ADDRESSING

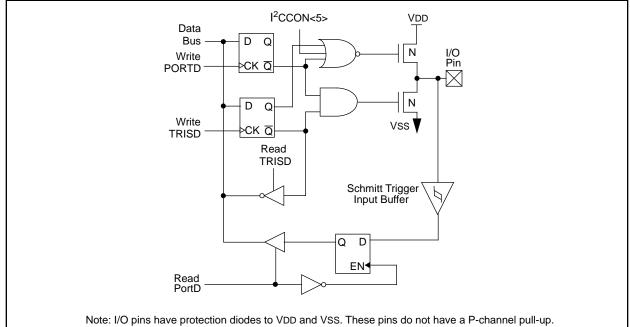

# FIGURE 5-10: BLOCK DIAGRAM OF PORTD<1:0> PINS

| 08h           | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    |

|---------------|---------|---------|---------|---------|----------|----------|----------|----------|

| PORTD         | RD7/AN7 | RD6/AN6 | RD5/AN5 | RD4/AN4 | RD3/REFB | RD2/CMPB | RD1/SDAB | RD0/SCLB |

| Read/Write    | R/W     | R/W     | R/W     | R/W     | R/W      | R/W      | R/W      | R/W      |

| POR value xxh | Х       | Х       | Х       | Х       | Х        | Х        | Х        | Х        |

| Bit | Name     | Function                                                                                                                                                                                                                                                                         |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В7  | RD7/AN7  | GPIO or analog input. Returns value on pin RD7/AN7 when used as a digital input. When configured as an analog input, reads as '0'.                                                                                                                                               |

| B6  | RD6/AN6  | GPIO or analog input. Returns value on pin RD6/AN6 when used as a digital input. When configured as an analog input, reads as '0'.                                                                                                                                               |

| B5  | RD5/AN5  | GPIO or analog input. This pin can connect to a level shift network. If enabled, a +0.5V offset is added to the input voltage. When configured as an analog input, reads as '0'.                                                                                                 |

| B4  | RD4/AN4  | GPIO or analog input. Returns value on pin RD4/AN4 when used as a digital input. When configured as an analog input, reads as '0'.                                                                                                                                               |

| B3  | RD3/REFB | This pin can serve as a GPIO, or programmable reference B output.                                                                                                                                                                                                                |

| B2  | RD2/CMPB | This pin can serve as a GPIO, or comparator B output.                                                                                                                                                                                                                            |

| B1  | RD1/SDAB | Alternate synchronous serial data I/O for I <sup>2</sup> C interface enabled by setting the I <sup>2</sup> CSEL bit in the MISC register. This pin can also serve as a general purpose I/O. This pin has an N-channel pull-up to VDD which is disabled in I <sup>2</sup> C mode. |

| во  | RD0/SCLB | Alternate synchronous serial clock for I <sup>2</sup> C interface, enabled by setting the I <sup>2</sup> CSEL bit in the MISC register. This pin can also serve as a general purpose I/O. This pin has an N-Channel pull-up to VDD which is disabled in I <sup>2</sup> C mode.   |

Legend: U = unimplemented, read as '0', x = unknown.

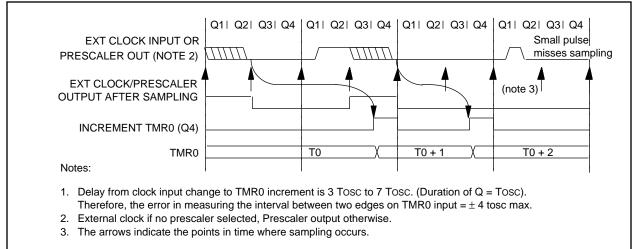

# 6.2 Using Timer0 with External Clock

When the external clock input (pin RC3/T0CKI) is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of TMR0 after synchronization.

# 6.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns).

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for T0CKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on T0CKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns.

## 6.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-5 shows the delay from the external clock edge to the timer incrementing.

# 6.3 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a post-scaler for the Watchdog Timer (Figure 6-1). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer, and vice-versa.

Bit PSA and PS2:PS0 (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the Timer0 module (e.g., CLRF 1, MOVWF 1, BSF 1, x) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

# FIGURE 6-5: TIMER0 TIMING WITH EXTERNAL CLOCK

# 7.5.1.1 ADDRESSING

Once the I<sup>2</sup>C module has been enabled, the I<sup>2</sup>C waits for a START to occur. Following the START, the 8-bits are shifted into the I<sup>2</sup>CSR. All incoming bits are sampled with the rising edge of the clock (SCL) line. The I<sup>2</sup>CSR<7:1> is compared to the I<sup>2</sup>CADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match, and the BF and I<sup>2</sup>COV bits are clear, the following things happen:

- I<sup>2</sup>CSR loaded into I<sup>2</sup>CBUF

- Buffer Full (BF) bit is set

- ACK pulse is generated

- I<sup>2</sup>C Interrupt Flag (I<sup>2</sup>CIF) is set (interrupt is generated if enabled (I<sup>2</sup>CIE set) on falling edge of ninth SCL pulse.

In 10-bit address mode, two address bytes need to be received by the slave (Figure 7-5). The five most significant bits (MSbs) of the first address byte specify if this is a 10-bit address. The R/W bit (bit 0) must specify a write, so the slave device will received the second address byte. For a 10-bit address the first byte would equal '1 1 1 1 0 A9 A8 0', where A9 and A8 are the two MSbs of the address. The sequence of events for 10-bit address are as follows, with steps 7-9 for slave-transmitter:

- 1. Receive first (high) byte of address (I<sup>2</sup>CIF, BF and UA are set).

- Update I<sup>2</sup>CADD with second (low) byte of address (clears UA and releases SCL line).

- 3. Read I<sup>2</sup>CBUF (clears BF) and clear I<sup>2</sup>CIF.

- 4. Receive second (low) byte of address (I<sup>2</sup>CIF, BF and UA are set).

- Update I<sup>2</sup>CADD with first (high) byte of address (clears UA, if match releases SCL line).

- 6. Read I<sup>2</sup>CBUF (clears BF) and clear I<sup>2</sup>CIF

- 7. Receive Repeated START.

- 8. Receive first (high) byte of address (I<sup>2</sup>CIF and BF are set).

- 9. Read I<sup>2</sup>CBUF (clears BF) and clear I<sup>2</sup>CIF.

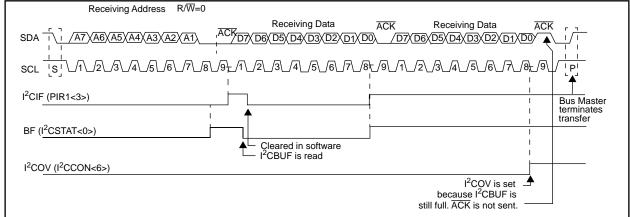

#### 7.5.1.2 RECEPTION

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the I<sup>2</sup>CSTAT register is cleared. The received address is loaded into the I<sup>2</sup>CBUF.

When the address byte overflow condition exists then no acknowledge ( $\overline{ACK}$ ) pulse is given. An overflow condition is defined as either the BF bit (I<sup>2</sup>CSTAT<0>) is set or the I<sup>2</sup>COV bit (I<sup>2</sup>CCON<6>) is set (Figure 7-14).

An  $I^2CIF$  interrupt is generated for each data transfer byte. The  $I^2CIF$  bit must be cleared in software, and the  $I^2CSTAT$  register is used to determine the status of the byte. In master mode with slave enabled, three interrupt sources are possible. Reading BF, P and S will indicate the source of the interrupt.

**Caution:** BF is set after receipt of eight bits and automatically cleared after the I<sup>2</sup>CBUF is read. However, the flag is not actually cleared until receipt of the acknowledge pulse. Otherwise extra reads appear to be valid.

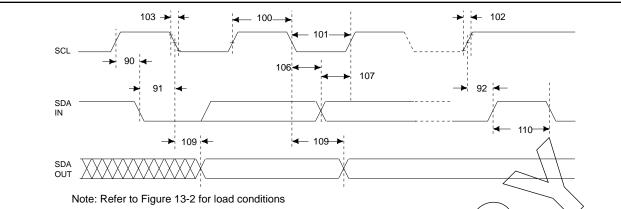

# FIGURE 7-14: I<sup>2</sup>C WAVEFORMS FOR RECEPTION (7-BIT ADDRESS)

#### 7.5.2 MASTER MODE

Master mode operation is supported by interrupt generation on the detection of the START and STOP. The STOP(P) and START(S) bits are cleared from a reset or when the  $l^2C$  module is disabled. Control of the  $l^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are cleared.

In master mode, the SCL and SDA lines are manipulated by changing the corresponding TRISC<7:6> or TRISD<1:0> bits to an output (cleared). The output level is always low, regardless of the value(s) in PORTC<7:6> or PORTD<1:0>. So when transmitting data, a "1" data bit must have the TRISC<7> or TRISD<1> bit set (input) and a "0" data bit must have the TRISC<7> or TRISD<1> bit set (input) and a "0" data bit must have the TRISC<7> or TRISD<1> bit set (input) and a "0" data bit must have the TRISC<7> or TRISD<1> bit cleared (output). The same scenario is true for the SCL line with the TRISC<6> or TRISD<0> bit.

The following events will cause the  $I^2C$  interrupt Flag ( $I^2CIF$ ) to be set ( $I^2C$  interrupt if enabled):

- START

- STOP

- Data transfer byte transmitted/received

Master mode of operation can be done with either the slave mode idle ( $l^2CM3...l^2CM0 = 1011b$ ) or with the slave active. When both master and slave modes are enabled, the software needs to differentiate the source(s) of the interrupt.

#### 7.5.3 MULTI-MASTER MODE

In multi-master mode, the interrupt generation on the detection of the START and STOP allows the determination of when the bus is free. The STOP (P) and START (S) bits are cleared from a reset or when the  $I^2C$  module is disabled. Control of the  $I^2C$  bus may be taken when the P bit is set, or the bus is idle and both the S and P bits are cleared. When the bus is busy, enabling the  $I^2C$  interrupt will generate the interrupt when the STOP occurs.

In multi-master operation, the SDA line must be monitored to see if the signal level is the expected output level. This check only needs to be done when a high level is output. If a high level is expected and low level is present, the device needs to release the SDA and SCL lines (set TRISC<7:6>). There are two stages where this arbitration can be lost, these are:

- Address Transfer

- Data Transfer

When the slave logic is enabled, the slave continues to receive. If arbitration was lost during the address transfer stage, the device may being addressed. If addressed an  $\overrightarrow{ACK}$  pulse will be generated. If arbitration was lost during the data transfer stage, the device will need to re-transfer the data at a later time.

# TABLE 7-3:REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Address | Name                 | Bit 7                     | Bit 6              | Bit 5              | Bit 4                  | Bit 3              | Bit 2              | Bit 1              | Bit 0              |

|---------|----------------------|---------------------------|--------------------|--------------------|------------------------|--------------------|--------------------|--------------------|--------------------|

| 0B/8Bh  | INTCON               | GIE                       | PEIE               | TOIE               | r                      | r                  | T0IF               | r                  | r                  |

| 0Ch     | PIR1                 | CMIF                      | _                  | _                  | PBIF                   | I <sup>2</sup> CIF | RCIF               | ADCIF              | OVFIF              |

| 8Ch     | PIE1                 | CMIE                      | _                  | _                  | PBIE                   | I <sup>2</sup> CIE | RCIE               | ADCIE              | OVFIE              |

| 13h     | I <sup>2</sup> CBUF  | I <sup>2</sup> C Serial F | Port Receive       | Buffer/Transr      | nit Registe            | r                  |                    |                    |                    |

| 93h     | I <sup>2</sup> CADD  | I <sup>2</sup> C mode S   | Synchronous        | Serial Port (l     | <sup>2</sup> C mode) A | ddress Reg         | gister             |                    |                    |

| 14h     | I <sup>2</sup> CCON  | WCOL                      | I <sup>2</sup> CON | I <sup>2</sup> CEN | CKP                    | I <sup>2</sup> CM3 | I <sup>2</sup> CM2 | I <sup>2</sup> CM1 | I <sup>2</sup> CM0 |

| 94h     | I <sup>2</sup> CSTAT | —                         | _                  | D/Ā                | Р                      | S                  | R/W                | UA                 | BF                 |

| 9Eh     | MISC                 | SMHOG                     | SPGNDB             | SPGNDA             | I <sup>2</sup> CSEL    | SMBUS              | INCLKEN            | OSC2               | OSC1               |

| 87h     | TRISC                | TRISC7                    | TRISC6             | TRISC5             | TRISC4                 | TRISC3             | TRISC2             | TRISC1             | TRISC0             |

| 88h     | TRISD                | TRISD7                    | TRISD6             | TRISD5             | TRISD4                 | TRISD3             | TRISD2             | TRISD1             | TRISD0             |

Legend: — = Unimplemented location, read as '0'

r = reserved locations, default is POR value and should not be overwritten with any value

Note: Shaded boxes are not used by the I<sup>2</sup>C module.

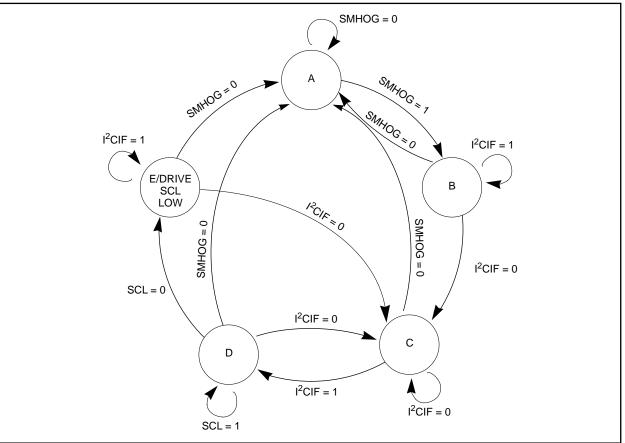

## 7.5.4 SMBus™ AND ACCESS.bus™ CONSIDERATIONS

PIC14000 is compliant with the SMBus specification published by Intel. Some key points to note regarding the bus specifications and how it pertains to the PIC14000 hardware are listed below:

- SMBus has fixed input voltage thresholds. PIC14000 I/O buffers have programmable levels that can be selected to be compatible with both SMBus threshold levels via the SMBus and SPGND bits in the MISC register.

- A mechanism to stretch the I<sup>2</sup>C clock time has been implemented to support SMBus slave transactions. The SMHOG bit (MISC<7>) allows hardware to automatically force and hold the I<sup>2</sup>C clock line low when a data byte has been received. This prevents the SMBus master from overflowing the receive buffer in instances where the microcontroller may be to busy servicing higher priority tasks to respond to a I<sup>2</sup>C module interrupt. Or, if the microcontroller is in SLEEP mode and needs time to wake-up and respond to the I<sup>2</sup>C interrupt.

# FIGURE 7-18: SMHOG STATE MACHINE

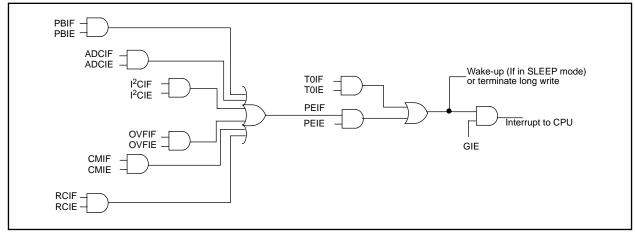

# 10.6 Interrupts

The PIC14000 has several sources of interrupt:

- External interrupt from OSC1/PBTN pin

- I<sup>2</sup>C port interrupt

- PORTC interrupt on change (pins RC<7:4> only)

- Timer0 overflow

- A/D timer overflow

- A/D converter capture event

- Programmable reference comparator interrupt

This section addresses the external and Timer0 interrupts only. Refer to the appropriate sections for description of the serial port, programmable reference and A/D interrupts.

INTCON records individual interrupt requests in flag bits. It also has individual and global enable bits. The peripheral interrupt flags reside in the PIR1 register. Peripheral interrupt enable interrupts are contained in the PIE1 register.

Global interrupt masking is controlled by GIE (INTCON<7>). Individual interrupts can be disabled through their corresponding mask bit in the INTCON register. GIE is cleared on reset to mask interrupts.

When an interrupt is serviced, the GIE is cleared to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with 0004h, the interrupt vector. For external interrupt events, such as the I<sup>2</sup>C interrupt, the interrupt latency will be 3 or 4 instruction cycles. The exact latency depends when the interrupt event occurs. The latency is the same for 1 or 2 cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests. Individual interrupt flag bits are set regardless of the status of their corresponding mask bit or the GIE bit to allow polling.

The return from interrupt instruction, RETFIE, exits the interrupt routine as well as sets the GIE bit to re-enable interrupts.

- Note 1: The individual interrupt flags will be set by the specified condition even though the corresponding interrupt enable bit is cleared (interrupt disabled) or the GIE bit is cleared (all interrupts disabled).

- Note 2: If an interrupt occurs while the Global Interrupt Enable (GIE) bit is being cleared, the GIE bit may unintentionally be re-enabled by the user's Interrupt Service Routine (the RETFIE instruction). The events that would cause this to occur are:

- 1. An instruction clears the GIE bit while an interrupt is acknowledged.

- 2. The program branches to the interrupt vector and executes the Interrupt Service Routine.

- 3. The interrupt service routine completes with the execution of the RETFIE instruction. This causes the GIE bit to be set (enables interrupts), and the program returns to the instruction after the one which was meant to disable interrupts.

The method to ensure that interrupts are globally disabled is:

1. Ensure that the GIE bit was cleared by the instruction, as shown in the following code:

| LOOP: | BCF   | INTCON, GIE | ; | Disable Global Interrupts   |

|-------|-------|-------------|---|-----------------------------|

|       | BTFSC | INTCON, GIE | ; | Global Interrupts Disabled? |

|       | GOTO  | LOOP        | ; | No, try again               |

|       | :     |             | ; | Yes, continue with program  |

|       |       |             | ; | flow                        |

## FIGURE 10-9: INTERRUPT LOGIC SCHEMATIC

#### 10.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION registers. Thus, time-out periods up to 2.3 seconds can be realized. The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the status register will be cleared upon a watchdog timer time-out. The WDT time-out period (no prescaler) is measured and stored in calibration space at location 0FD2h.

#### 10.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken into account that under worst-case conditions (minimum VDD, maximum temperature, maximum WDT prescaler) it may take several seconds before a WDT time-out occurs. Refer to Section 6.3 for prescaler switching considerations.

#### 10.8 <u>Power Management Options</u>

The PIC14000 has several power management options to prolong battery lifetime. The SLEEP instruction halts the CPU and can turn off the on-chip oscillators. The CPU can be in SLEEP mode, yet the A/D converter can continue to run. Several bits are included in the SLPCON register (8Fh) to control power to analog modules.

| Function                                  | Summary                                                                      |

|-------------------------------------------|------------------------------------------------------------------------------|

| CPU Clock                                 | OFF during SLEEP/HIBERNATE mode, ON otherwise                                |

| Main Oscillator                           | ON if NOT in SLEEP mode. In SLEEP mode, controlled by OSCOFF bit, SLPCON<3>. |

| Watchdog Timer                            | Controlled by WDTE, 2007h<2> and HIBEN, SLPCON<7>                            |

| Temperature Sensor                        | Controlled by TEMPOFF, SLPCON<1>                                             |

| Low-voltage Detector                      | Controlled by REFOFF, SLPCON<5>                                              |

| Comparator and<br>Programmable References | Controlled by CMOFF, SLPCON<2>                                               |

| A/D Comparator                            | Controlled by ADOFF, SLPCON<0>                                               |

| Programmable Current Source               | Controlled by ADOFF, SLPCON<0> and ADCON1<7:4>                               |

| Slope Reference Voltage Divider           | Controlled by ADOFF, SLPCON<0>                                               |

| Level Shift Networks                      | Controlled by LSOFF, SLPCON<4>                                               |

| Bandgap Reference                         | Controlled by REFOFF, SLPCON<5>                                              |

| Voltage Regulator Control                 | Always ON. Does not consume power if unconnected.                            |

| Power On Reset                            | Always ON, except in SLEEP/HIBERNATE mode                                    |

# TABLE 10-6: SUMMARY OF POWER MANAGEMENT OPTIONS

**Note:** Refer to analog specs for individual peripheral operating currents.

# 11.0 INSTRUCTION SET SUMMARY

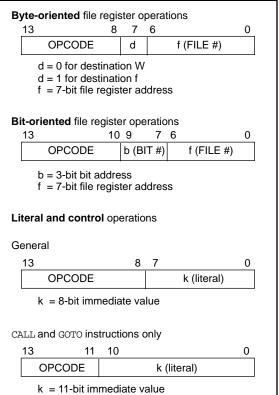

The PIC14000's instruction set is the same as PIC16CXX. Each instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The instruction set summary in Table 11-2 lists byte-oriented, bit-oriented, and literal and control operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

#### TABLE 11-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$                                                              |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| E             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 11-2 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the three general formats that the instructions can have.

Note: To maintain upward compatibility with future PIC16CXX products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

| GOTO                   | Unconditional Branch                                                                                                                                                                          | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                               |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                | [ <i>label</i> ] GOTO k                                                                                                                                                                       | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                          |  |  |  |

| Operands:              | $0 \le k \le 2047$                                                                                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                    |  |  |  |

| Operation:             | $k \rightarrow PC < 10:0>$                                                                                                                                                                    |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                            |  |  |  |

|                        | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                           | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                     |  |  |  |

| Status Affected:       | None                                                                                                                                                                                          | Status Affected: | None                                                                                                                                                                                                                                                                                                 |  |  |  |

| Encoding:              | 10 1kkk kkkk kkkk                                                                                                                                                                             | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                    |  |  |  |

| Description:<br>Words: | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two cycle instruction. | Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a |  |  |  |

| Cycles:                | 2                                                                                                                                                                                             | 147              | two cycle instruction.                                                                                                                                                                                                                                                                               |  |  |  |

| Example                | GOTO THERE                                                                                                                                                                                    | Words:           | 1                                                                                                                                                                                                                                                                                                    |  |  |  |

| ·                      | After Instruction                                                                                                                                                                             | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                 |  |  |  |

|                        | PC = Address THERE                                                                                                                                                                            | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                      |  |  |  |

|                        |                                                                                                                                                                                               |                  | CONTINUE •                                                                                                                                                                                                                                                                                           |  |  |  |

|                        |                                                                                                                                                                                               |                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                                              |  |  |  |

| INCF             | Increment f                                                                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                                            |

| Status Affected: | Z                                                                                                                                                                                       |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                                       |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is 0 the result is placed<br>in the W register. If 'd' is 1 the result is<br>placed back in register 'f'.                     |

| Words:           | 1                                                                                                                                                                                       |

| Cycles:          | 1                                                                                                                                                                                       |

| Example          | INCF CNT, 1                                                                                                                                                                             |

|                  | $\begin{array}{rrrr} \text{Before Instruction} \\ & \text{CNT} &= & 0 \text{xFF} \\ & Z &= & 0 \\ \text{After Instruction} \\ & \text{CNT} &= & 0 \text{x00} \\ & Z &= & 1 \end{array}$ |

| IORLW            | Inclusive OR Literal with W                                                                                           |  |  |  |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                              |  |  |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                          |  |  |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Description:     | The contents of the W register is<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                            |  |  |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                              |  |  |  |  |  |  |  |  |  |  |

After Instruction CNT = CN

if CNT=

PC =

if CNT≠

PC =

CNT + 1

address CONTINUE

address HERE +1

0,

0,

# PIC14000

# 13.3 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS            | 8                                                                                                                    | 3. Tcc:st                    | (I <sup>2</sup> C specifications only) |

|------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------|

| 2. TppS                |                                                                                                                      | 4. Ts                        | (I <sup>2</sup> C specifications only) |

| т                      |                                                                                                                      |                              |                                        |

| F                      | Frequency                                                                                                            | Т                            | Time                                   |

| Lowercas               | e subscripts (pp) and their meanings:                                                                                |                              | A                                      |

| рр                     |                                                                                                                      |                              | $\langle \rangle$                      |

| ck                     | CLKOUT                                                                                                               | osc                          | OSC1                                   |

| di                     | SDI                                                                                                                  | tO                           | тоскі                                  |

| io                     | I/O port                                                                                                             |                              |                                        |

| mc                     | MCLR                                                                                                                 |                              |                                        |

| Uppercas               | e letters and their meanings:                                                                                        |                              |                                        |

| S                      |                                                                                                                      |                              |                                        |

| F                      | Fall                                                                                                                 | Р                            | Periód                                 |

| н                      | High                                                                                                                 | R                            | Rise                                   |

| 1                      | Invalid (Hi-impedance)                                                                                               | v <                          | Valid                                  |

| L                      | Low                                                                                                                  | z </td <td>Hi-impedance</td> | Hi-impedance                           |

| I <sup>2</sup> C only  |                                                                                                                      |                              | $\searrow$                             |

| AA                     | output access                                                                                                        | High                         | High                                   |

| BUF                    | Bus free                                                                                                             | Law                          | > Low                                  |

| TCC:ST (I <sup>2</sup> | C specifications only)                                                                                               | $\langle \rangle \rangle$    |                                        |

| СС                     |                                                                                                                      | $\left \right\rangle$        |                                        |

| HD                     | Hold                                                                                                                 | su                           | Setup                                  |

| ST                     | $\land \land $ |                              |                                        |

| DAT                    | DATA input hold                                                                                                      | STO                          | STOP condition                         |

| STA                    | START condition                                                                                                      |                              |                                        |

| L                      |                                                                                                                      |                              |                                        |

|                        | $\langle \rangle \rangle$                                                                                            |                              |                                        |

|                        |                                                                                                                      |                              |                                        |

|                        | $\langle \rangle \rangle >$                                                                                          |                              |                                        |

|                        | $\sim$                                                                                                               |                              |                                        |

|                        |                                                                                                                      |                              |                                        |

# TABLE 13-8: I<sup>2</sup>C BUS DATA REQUIREMENTS

| Parameter Sym<br>No. |         | Characteristic         | Min                     | Мах                                          | Units                         | Conditions           |                                                  |

|----------------------|---------|------------------------|-------------------------|----------------------------------------------|-------------------------------|----------------------|--------------------------------------------------|

| 100                  | Тнідн   | Clock high time        | 100 kHz mode            | 4.0                                          |                               | ₩S                   | PIC14900 must operate at a minimum of 1.5 MHz    |

|                      |         |                        | 400 kHz mode            | 0.6                                          |                               | μs                   | PIC14000 must operate at a<br>minimum of 10 MHz  |

|                      |         |                        | I <sup>2</sup> C Module | 1.5 ICY                                      | $\langle \mathcal{A} \rangle$ | $\backslash \rangle$ |                                                  |

| 101                  | TLOW    | Clock low time         | 100 kHz mode            | 4:7                                          | $\rightarrow$                 | μs                   | PIC14000 must operate at a<br>minimum of 1.5 MHz |

|                      |         |                        | 400 kHz mode            | 1.3                                          | > -                           | μs                   | PIC14000 must operate at a<br>minimum of 10 MHz  |

|                      |         |                        | I <sup>2</sup> C Module | 1.5 Ter                                      | —                             |                      |                                                  |

| 102                  | TR      | SDA and SCL rise       | 100 kHz mode            | <u>\                                    </u> | 1000                          | ns                   |                                                  |

|                      |         | time                   | 400 kHz mode            | 20+0.1 C <sub>b</sub>                        | 300                           | ns                   | C <sub>b</sub> is specified to be from 10-400 pF |

| 103                  | TF      | SDA and SCL fall       | 100 kHz mode            | _                                            | 300                           | ns                   |                                                  |

|                      |         | time                   | 400 kHz mode            | 20+0.1 C <sub>b</sub>                        | 300                           | ns                   | C <sub>b</sub> is specified to be from 10-400 pF |

| 90                   | TSU:STA | START condition        | 100 kHz mode            | 4.7                                          | —                             | μs                   | Only relevant for repeated                       |

|                      |         | setup time             | 400 kHz mode            | 0.6                                          | _                             | μs                   | START condition                                  |

| 91                   | THD:STA | START condition hold   | 100 kHz mode            | 4.0                                          | _                             | μs                   | After this period the first cloc                 |

|                      |         | time                   | 400 kHz mode            | 0.6                                          | —                             | μs                   | pulse is generated                               |

| 106                  | THD:DAT | Data input hold time   | 100 kHz mode            | 0                                            |                               | ns                   |                                                  |

|                      |         | $ \leq \vee $          | 400 kHz mode            | 0                                            | 0.9                           | μs                   |                                                  |

| 107                  | TSU:DAT | Rata input setup time  | 100 kHz mode            | 250                                          | —                             | ns                   | Note 2                                           |

|                      |         | 400 kHz mode           | 100                     | _                                            | ns                            |                      |                                                  |

| Ø2                   | TSU:STQ | STOP condition setup   | 100 kHz mode            | 4.7                                          |                               | μs                   |                                                  |

| $\leq$               |         | time                   | 400 kHz mode            | 0.6                                          | —                             | μs                   |                                                  |

| 109 <                | ΤΑΑ     | Output valid from      | 100 kHz mode            | —                                            | 3500                          | ns                   | Note 1                                           |

|                      | $\geq$  | clock                  | 400 kHz mode            |                                              |                               | ns                   |                                                  |

| 110                  | TBUF    | Bus free time          | 100 kHz mode            | 4.7                                          |                               | μs                   | Time the bus must be free                        |

|                      |         |                        | 400 kHz mode            | 1.3                                          |                               | μs                   | before a new transmission<br>can start           |

|                      | Cb      | Bus capacitive loading |                         |                                              | 400                           | pF                   |                                                  |

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of STARTs or STOPs.

2: A fast-mode l<sup>2</sup>C-bus device can be used in a standard-mode l<sup>2</sup>C-bus system, but the requirement

2: A fast-mode I<sup>2</sup>C-bus device can be used in a standard-mode I<sup>2</sup>C-bus system, but the requirement ts∪:DAT≥250ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+ts∪:DAT=1000+250=1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

| Standard Operating Condition          | ns (unless o              | therwise st         | ated)    |                      |        |                                                |        |

|---------------------------------------|---------------------------|---------------------|----------|----------------------|--------|------------------------------------------------|--------|

|                                       | $^{\circ}C \le TA \le +8$ |                     |          |                      |        |                                                |        |

|                                       | $^{\circ}C \le TA \le +7$ |                     |          | l                    |        |                                                |        |

| VDD range: 2.7V (min) to 6.0V (       | (max) unless              | otherwise s         | stated.  |                      |        |                                                |        |

| Characteristic                        | Sym.                      | Min.                | Тур.     | Max.                 | Units  | Conditions                                     | Notes  |

| Temperature Sensor (continue          | od)                       |                     | 1        |                      |        |                                                | 1      |

| Output Linearity                      | lin(temp)                 |                     | TBD      | _                    |        |                                                | 1      |

| Operating Current (sensor on)         | idd(temp)                 |                     | 150      | 250                  | μA     | TEMPOFF = 0                                    | 2      |

| Operating Current (sensor off)        | idd(temp)                 |                     | 0        |                      | μΑ     |                                                | 2      |

|                                       |                           |                     |          |                      | 10.1   |                                                |        |

| Slope Reference Voltage Divid         | ler                       |                     | -        |                      |        | $\sim$                                         | $\geq$ |

| Output Voltage (SREFHI)               | voh(sref)                 | 1.14                | 1.19     | 1.24                 | V      |                                                |        |

| Output Voltage (SREFLO)               | vol(sref)                 | 0.10                | 0.13     | 0.16                 | V      |                                                |        |

| Slope Reference Calibration<br>Factor | Kref                      | 0.09                | 0.126    | 0.16                 |        | TA = 25°C, VDD = 5V                            |        |

| KREF Supply Sensitivity               | ss(Kref)                  |                     | 0.02     | _                    | %/V    | From VDDmin to VDDmax                          | 1      |

| KREF Temperature Coefficient          | tc(KREF)                  | —                   | 20       | —                    | ppm/%C | From Tmin to Tmax                              | 1      |

| Operating Current (A/D on)            | idd(sref)                 | —                   | 55       | 85 ~                 | μÀ     | AQOFF = 0                                      | 2      |

| Operating Current (A/D off)           | idd(sref)                 | —                   | 0        |                      | 144    | ADOFF = 1                                      | 2      |

| A/D Comparator                        |                           |                     | $\wedge$ | $\overline{\langle}$ |        | ><br>>                                         |        |

| Input Offset Voltage                  | ioff(adc)                 | -10                 | 2        | 10                   | mV     | Measured over common-mode range                |        |

| Input Common Mode Voltage<br>Range    | cmr(adc)                  | 0                   |          | VPR-1.4              | V      |                                                |        |

| Differential Voltage Gain             | gain(adc)                 | $\langle - \rangle$ | 100      | <u> </u>             | dB     |                                                | 1      |

| Common Mode Rejection Ratio           | - · ·                     |                     | 80       |                      | dB     | VDD = 5V, TA = 25°C, over<br>common-mode range | 1      |

| Power Supply Rejection Ratio          | psrr(adc)                 |                     | 70       |                      | dB     | TA = $25^{\circ}$ C, VDDmin to VDDmax          | 1      |

| Operating Current (A/D on)            | idd(adc)                  | $\searrow$          | 40       | 65                   | μΑ     | ADOFF = 0                                      | 2      |

| Operating Current (A/D off)           |                           | ×                   | 0        |                      | μΑ     | ADOFF = 1                                      | 2      |

|                                       |                           |                     | Ū        |                      | μπ     |                                                | 2      |

| Programmable Reference(s)             | $\searrow$                |                     |          |                      |        |                                                |        |

| Upper Range<br>Output Voltage         | vo(pref)                  | 0.627               | 0.792    | 0.957                | V      | TA = 25°C<br>PREFx<7:0> = 7Fh                  |        |

| ()                                    |                           | 0.418               | 0.528    | 0.638                | V      | (127 decimal), max<br>PREFx<7:0> = 50h         |        |

| Coarse Resolution                     | resc(pref)                | 38.0                | 48.0     | 58.0                 | mV     | (80 decimal), min<br>PREFx<2:0> = constant     |        |

| Fine Resolution                       | resf(pref)                | 4.0                 | 5.0      | 6.0                  | mV     | PREFx<7:3> = constant                          |        |

| Middle Range                          |                           |                     |          |                      |        | TA = 25°C                                      |        |

| Output Voltage                        | vo(pref)                  | 0.414               | 0.523    | 0.632                | V      | PREFx<7:0> = 4F<br>(79 decimal), max           |        |

|                                       |                           | 0.380               | 0.480    | 0.580                | V      | PREFx<7:0> = 00h                               |        |

|                                       |                           | 0.240               | 0 400    | 0 500                |        | (default), mid-point                           |        |

|                                       |                           | 0.342               | 0.432    | 0.522                | V      | PREFx<7:0> = C8h<br>(200 decimal), min         |        |

| Coarse Resolution                     | resc(pref)                | 3.8                 | 4.8      | 5.8                  | mV     | PREFx<2:0> = constant                          |        |

| Fine Resolution                       | resf(pref)                | 0.38                | 0.46     | 0.54                 | mV     | PREFx<7:3> = constant                          | 1      |

#### Standard Operating Conditions (unless otherwise stated)

| Operating Temperature:   | $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |

|--------------------------|-------------------------------------------------------|

|                          | $0^{\circ}C \le TA \le +70^{\circ}C$ for commercial   |

| VDD range: 2.7V (min) to | 6.0V (max) unless otherwise stated.                   |

| Characteristic                          | Sym.   | Min.       | Тур.     | Max.   | Units                                                          | Conditions                  | Notes |

|-----------------------------------------|--------|------------|----------|--------|----------------------------------------------------------------|-----------------------------|-------|

| Calibration Accuracy                    |        | :          |          |        | All parameters calibrated at VDD = 5V, TA = 25°C unless noted. | 3, 5                        |       |

|                                         |        |            | Accuracy |        |                                                                |                             |       |

| Parameter                               | Sym.   | Resolution | Units    | Тур    | Max                                                            | Conditions                  | Notes |

| Slope Reference Ratio                   | Kref   | 0.015%     | —        | .02%   | _                                                              |                             |       |

| Bandgap Reference Voltage               | KBG    | 10         | μV       | .01%   | _                                                              |                             |       |

| Temperature Sensor Output<br>Voltage    | VTHERM | 20         | μV       | .02%   | _                                                              |                             |       |

| Temperature Sensor Slope<br>Coefficient | Ктс    | 0.33       | μV/°C    | 6.7%   | _                                                              | Calibrated at 25°C and Tmax |       |